# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### High Efficiency 800mA Synchronous Buck Regulator

Ideal for portable designs powered with Li lon battery

#### FEATURES

- Ultra-low 20µA Quiescent Current

- 98% Efficiency Possible

- 800mA Output Current

- 2.7V to 5.5V Input Voltage Range

- Output Adjustable Down to 1.0V

- No External FET's Required

- 1.25A Inductor Peak Current Limit

- 100% Duty Ratio Low Dropout Operation

- 80µA Light Load Quiescent Current in Dropout

- Logic Shutdown Control

- Programmable UVLO

- Small 10 pin MSOP Package

- Power Good Indicator

- Industry Standard 10 Pin MSOP and and Small DFN Package

Now Available in Lead Free Packaging

#### APPLICATIONS

- PDA's

- DSC's

- MP3 Players

- USB Devices

- Point of Use Power

#### DESCRIPTION

The SP6654 is a 800mA synchronous buck regulator which is ideal for portable applications that use a Li-Ion or 3 cell alkaline/NiCD/NiMH input. The SP6654's proprietary control loop,  $20\mu$ A light load quiescent current, and  $0.3\Omega$  power switches provide excellent efficiency across a wide range of output currents. As the input battery supply decreases towards the output voltage the SP6654 seamlessly transitions into 100% duty ratio operation further extending useful battery life. The SP6654 is protected against overload and short circuit conditions with a precise inductor peak current limit. Other features include programmable under voltage lockout, externally programmed output voltage down to 1.0V, logic level shutdown control, and an open drain power good indicator when V<sub>OUT</sub> is above 94% of its programmed value.

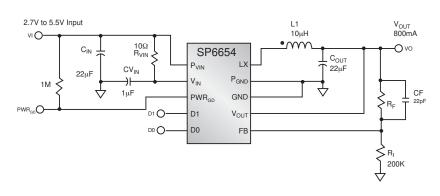

#### **TYPICAL APPLICATION SCHEMATIC**

#### **ABSOLUTE MAXIMUM RATINGS**

| PV <sub>IN</sub> ,V <sub>IN</sub>                |                 |

|--------------------------------------------------|-----------------|

| All other pins                                   |                 |

| PV <sub>IN</sub> , P <sub>GND</sub> , LX current |                 |

| Storage Temperature                              | 65 °C to 150 °C |

| Operating Temperature                            |                 |

| Junction Temperature                             | 125°C           |

| Theta JA (10 Pin MSOP)                           |                 |

| Theta JA (10 Pin DFN)                            | 48.7°C/w        |

|                                                  |                 |

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN}=PV_{IN}=V_{SDN}=3.6V$ ,  $V_{OUT}=V_{FB}$ ,  $I_{O} = 0mA$ ,  $T_{AMB} = -40^{\circ}C$  to  $+85^{\circ}C$ . The  $\blacklozenge$  denotes the specifications which apply over the full operating temperature range, unless otherwise specified.

| PARAMETER                                                                                          | MIN   | ТҮР   | МАХ   | UNITS |   | CONDITIONS                                                                 |

|----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|---|----------------------------------------------------------------------------|

| Input Voltage Operating                                                                            | UVLO  |       | 5.5   | V     | • | Result of $I_{Q}$ measurement at $V_{IN} = PV_{IN} = 5.5V$                 |

| Minimum Output Voltage                                                                             | 1.0   |       |       | V     | • | FB Set Voltage, Vr                                                         |

| FB Set Voltage, Vr                                                                                 | 0.784 | 0.800 | 0.816 | V     |   | 25° C, IO = 200mA Close Loop. LI = $10\mu$ H,                              |

|                                                                                                    |       |       | ±4    | 0/    |   | Measured at $V_{IN} = 5.5V$ , no<br>load, $T_{AMB} = 0^{\circ}$ C to 70° C |

| Overall Accuracy                                                                                   |       |       | ±5    | %     | • | Measured at $V_{IN} = 3.6V$ , 200mA load, Close Loop                       |

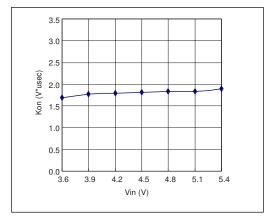

| On-Time Constant - KON Min,<br>$T_{ON} = KON/(V_{IN}-V_{OUT})$                                     | 1.5   | 2.25  | 3.0   | V*µs  | • | Close Loop, LI = $10\mu$ H, C <sub>OUT</sub> = $22\mu$ F                   |

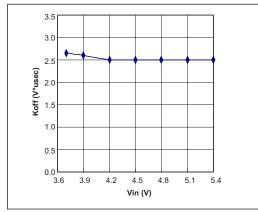

| Off-Time Min, T <sub>OFF</sub> = K <sub>OFF</sub> /V <sub>OUT</sub><br>Constant - K <sub>OFF</sub> | 1.6   | 2.4   | 3.2   | V*µs  | • | Inductor current limit tripped,<br>$V_{FB} = 0.5V$ Measured at V, = 2V     |

| Off-Time Blanking                                                                                  |       | 100   |       | ns    |   | T <sub>AMB</sub> =27° C                                                    |

| PMOS Switch Resistance                                                                             |       | 0.3   | 0.6   |       | • | IPMOS = 200mA                                                              |

| NMOS Switch Resistance                                                                             |       | 0.3   | 0.6   |       | • | INMOS = 200mA                                                              |

| Inductor Current Limit                                                                             | 1.0   | 1.25  | 1.50  | А     | • | V <sub>FB</sub> = 0.5V                                                     |

| LX Leakage Current                                                                                 |       | 0.01  | 3     | μA    | • | D0 = D1 = 0                                                                |

| Power Efficiency                                                                                   |       | 96    |       | %     |   | $V_{OUT} = 2.5V, IO = 200mA$<br>$T_{AMB} = 27^{\circ} C$                   |

|                                                                                                    |       | 92    |       |       |   | $V_{_{OUT}}$ = 3.3V, IO = 800mA<br>T_{_{AMB}}=27° C                        |

| Minimum Guaranteed Load Current                                                                    | 800   | 900   |       | mA    | • |                                                                            |

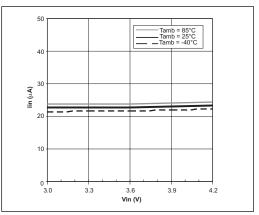

| V <sub>IN</sub> Quiescent Current                                                                  |       | 20    | 30    | μA    | • | $V_{_{\rm OUT}}$ = 3.3V, $V_{_{\rm IN}}$ = 3.6V and $V_{_{\rm IN}}$ = 5.5V |

| V <sub>IN</sub> Shutdown Current                                                                   |       | 1     | 500   | nA    | • | D1 = D0 = 0V                                                               |

| V <sub>out</sub> Quiescent Current                                                                 |       | 2     | 5     | μA    | • | $V_{OUT} = 3.3V$                                                           |

| V <sub>out</sub> Shutdown Current                                                                  |       | 1     | 500   | nA    | • | D1 = D0 = 0V                                                               |

#### **ELECTRICAL CHARACTERISTICS**

$V_{IN}=PV_{IN}=V_{SDN}=3.6V$ ,  $V_{OUT}=V_{FB}$ ,  $I_O = 0mA$ ,  $T_{AMB} = -40^{\circ}C$  to  $+85^{\circ}C$ . The  $\blacklozenge$  denotes the specifications wich apply over the full operating temperature range, unless otherwise specified.

| PARAMETER                                             | MIN  | ТҮР  | МАХ  | UNITS |   | CONDITIONS                                     |

|-------------------------------------------------------|------|------|------|-------|---|------------------------------------------------|

|                                                       | 2.55 | 2.70 | 2.85 |       | • | D1 = 0V, D0 = V <sub>IN</sub>                  |

| UVLO Undervoltage Lockout Threshold, $V_{IN}$ falling | 2.70 | 2.85 | 3.00 | V     | • | D1 = V <sub>IN</sub> , D0 = 0V                 |

|                                                       | 2.85 | 3.00 | 3.15 |       | • | D1 = V <sub>IN</sub> , D0 = V <sub>IN</sub>    |

| UVLO hysteresis                                       |      | 40   |      | mV    |   | T <sub>AMB</sub> = 27° C                       |

| PWRGD Low Output Voltage                              |      |      | 0.4  | V     | • | $V_{IN} = 3.3V, I_{SINK} = 1mA$                |

| PWRGD Leakage Current                                 |      |      | 1    | μA    | ٠ | VPWRGD =3.6V                                   |

| PWRGD Rising Threshold                                |      | -6   |      | %     |   | FB Set Voltage -6%,<br>T <sub>AMB</sub> =27° C |

| PWRGD Hysterisis                                      |      | 80   |      | mV    |   | T <sub>AMB</sub> =27° C                        |

| D1,D0 Leakage Current                                 |      | 1    | 500  | nA    | • |                                                |

| D1,D0 Input Threshold Voltage                         | 0.60 | 0.90 |      | v     | • | High to Low Transition                         |

| The should voltage                                    |      | 1.25 | 1.8  |       | * | Low to High Transition                         |

| FB Leakage Current                                    |      | 1    | 100  | nA    |   | FB = 1V                                        |

| D1 | D0 |                                                                                 |

|----|----|---------------------------------------------------------------------------------|

| 0  | 0  | Shutdown. All internal circuitry is disabled and the power switches are opened. |

| 0  | 1  | Device enabled, falling UVLO threshold =2.70V                                   |

| 1  | 0  | Device enabled, falling UVLO threshold =2.85V                                   |

| 1  | 1  | Device enabled, falling UVLO threshold =3.00V                                   |

Table 1. Operating Mode Definition

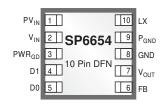

| PIN NUMBER | PIN NAME          | DESCRIPTION                                                                                                                                                                                                                                                  |

|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | PV <sub>IN</sub>  | Input voltage power pin. Inductor charging current passes through this pin.                                                                                                                                                                                  |

| 2          | V <sub>IN</sub>   | Internal supply voltage. Control circuitry powered from this pin.                                                                                                                                                                                            |

| 3          | PWR <sub>GD</sub> | Open drain Power Good indicator. If V <sub>FB</sub> is less than 750mV this pin is pulled to ground. When V <sub>FB</sub> is above 750mV this pin is open. Connect a resistor from this pin to V <sub>IN</sub> or V <sub>OUT</sub> to create a logic signal. |

| 4          | D1                | Digital mode control input. See table I for definition.                                                                                                                                                                                                      |

| 5          | D0                | Digital mode control input. See table I for definition.                                                                                                                                                                                                      |

| 6          | FB                | External feedback network input connection. Connect a resistor from FB to ground and FB to $V_{OUT}$ to set the output voltage. This pin regulates to the internal bandgap reference voltage of 0.8V.                                                        |

| 7          | V <sub>OUT</sub>  | Output voltage sense pin. Used by the timing circuit to set minimum on and off times.                                                                                                                                                                        |

| 8          | GND               | Internal ground pin. Control circuitry returns current to this pin.                                                                                                                                                                                          |

| 9          | P <sub>GND</sub>  | Power ground pin. Synchronous rectifier current returns through this pin.                                                                                                                                                                                    |

| 10         | LX                | Inductor switching node. Inductor tied between this pin and the output capacitor to create regulated output voltage.                                                                                                                                         |

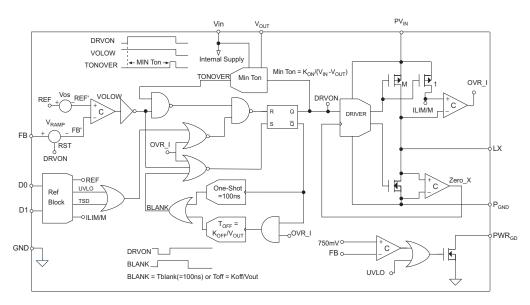

#### FUNCTIONAL DIAGRAM

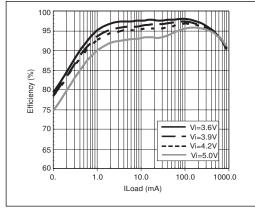

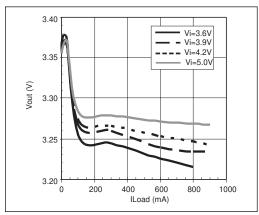

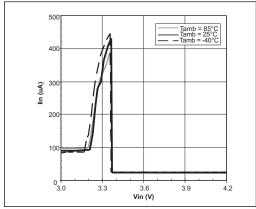

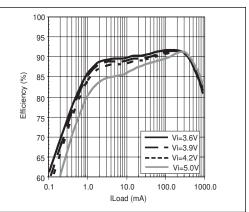

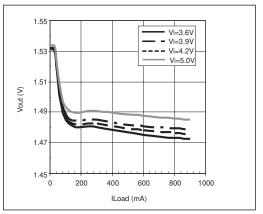

Refer to the typical application schematic,  $T_{AMB}$ = +27°C

Figure 1. Efficiency vs Load,  $V_{OUT} = 3.3V$

Figure 3. Line/Load Rejection,  $V_{OUT} = 3.3V$

Figure 5. No Load Battery Current, V<sub>OUT</sub>=3.3V

Figure 2. Efficiency vs Load,  $V_{OUT} = 1.5V$

Figure 4. Line/Load Rejection,  $V_{OUT} = 1.5V$

Figure 6. No Load Battery Current,  $V_{out}$ =1.5V

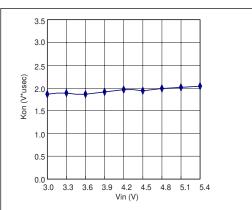

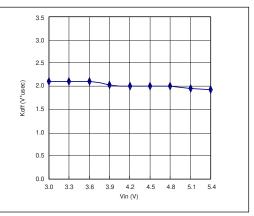

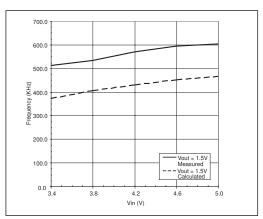

#### Refer to the typical application schematic, $T_{AMB}$ = +27°C

Figure 7. K<sub>on</sub> vs V<sub>IN</sub>, V<sub>out</sub>=3.3V

Figure 9. K<sub>OFF</sub> vs V<sub>IN</sub>, V<sub>OUT</sub>=3.3V

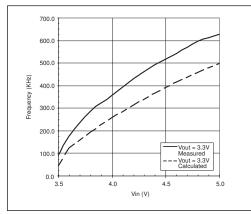

Figure 11. Ripple Frequency vs.  $V_{IN}$ ,  $I_{OUT}$ =600mA,  $V_{OUT}$ =3.3V

Figure 8. K<sub>on</sub> vs V<sub>IN</sub>, V<sub>out</sub>=1.5V

Figure 10.  $K_{OFF}$  vs  $V_{IN}$ ,  $V_{OUT}$ =1.5V

Figure 12. Ripple Frequency vs.  $V_{IN}$ ,  $I_{OUT}$ =600mA,  $V_{OUT}$ =1.5V

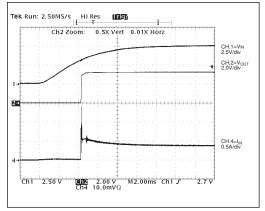

#### **TYPICAL PERFORMANCE CHARATERISTICS**

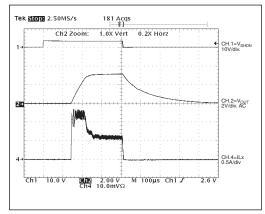

Refer to the typical application schematic,  $T_{AMB}$  = +27°C

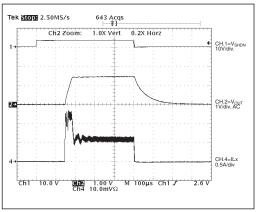

Figure 13. V<sub>IN</sub> Start up, I<sub>OUT</sub>=0.6A, V<sub>OUT</sub>=3.3V

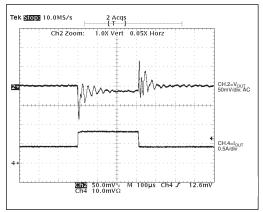

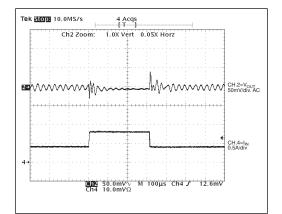

Figure 15. Load Step,  $I_{OUT}$ =0.4A to 0.8A,  $V_{OUT}$ =3.3V

Figure 17. Start up from SHDN, I<sub>out</sub>=0.6A, V<sub>out</sub>=3.3V

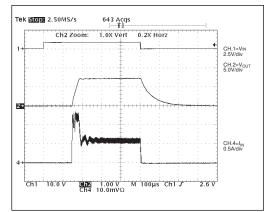

Figure 14. V<sub>IN</sub> Start up, I<sub>OUT</sub>=0.6A, V<sub>OUT</sub>=1.5V

Figure 16. Load Step, I<sub>OUT</sub>=0.4A to 0.8A, V<sub>OUT</sub>=1.5V

The SP6654 is a high efficiency synchronous buck regulator with an input voltage range of +2.7V to +5.5V and an output that is adjustable between +1.0V and  $V_{IN}$ . The SP6654 features a unique on-time control loop that runs in discontinuous conduction mode (DCM) or continuous conduction mode (CCM) using synchronous rectification. Other features include, over-current protection, digitally controlled enable and under-voltage lockout, an external feedback pin, and a power good indicator.

The SP6654 operates with a light load quiescent current of  $20\mu A$  using a  $0.3\Omega$  PMOS main switch and a  $0.3\Omega$  NMOS synchronous switch. It operates with excellent efficiency across the entire load range, making it an ideal solution for battery powered applications and low current step-down conversions. The part smoothly transitions into a 100% duty cycle under heavy load/ low input voltage conditions.

#### **On-Time Control - Charge Phase**

The SP6654 uses a precision comparator and a minimum on-time to regulate the output voltage and control the inductor current under normal load conditions. As the feedback pin drops below the regulation point, the loop comparator output goes high and closes the main switch. The minimum on-timer is triggered, setting a logic high for the duration defined by:

$$T_{\rm ON} = \frac{K_{\rm ON}}{V_{\rm IN} - V_{\rm OUT}}$$

where:

$K_{ON} = 2.25 V^* \mu sec \text{ constant}$  $V_{IN} = V_{IN} \text{ pin voltage}$

$$V_{OUT} = V_{OUT}$$

pin voltage

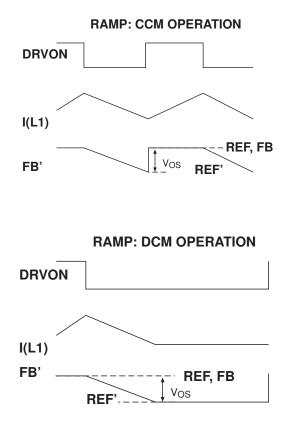

To accommodate the use of ceramic and other low ESR capacitors, an open loop ramp is added to the feedback signal to mimic the inductor current ripple. The following waveforms describe the ideal ramp operation in both CCM and DCM operation.

In either CCM or DCM, the negative going ramp voltage ( $V_{RAMP}$  in the functional diagram)

is added to FB and this creates the FB's signal. This FB signal is applied to the negative terminal of the loop comparator. To the positive terminal of the loop comparator is applied the REF voltage of 0.8V plus an offset voltage Vos to compensate for the DC level of  $V_{RAMP}$  applied to the negative terminal. The result is an internal ramp with enough negative going offset (approximately 50mV) to trip the loop comparator whenever FB falls below regulation.

The output of the loop comparator, a rising VOLOW, causes a SET if BLANK = 0 and OVR\_I = 0. This starts inductor charging (DRVON = 1) and starts the minimum on-timer. The minimum on-timer times out and indicates DRVON can be reset if the voltage loop is satisfied. If  $V_{OUT}$  is still below the regulation point RESET is held low until  $V_{OUT}$  is above

regulation. Once RESET occurs  $T_{ON}$  minimum is reset, and the  $T_{OFF}$  one-shot is triggered to blank the loop comparator from starting a new charge cycle for a minimum period. This blanking period occurs during the noisy LX transition to discharge, where spurious comparator states may occur. For  $T_{OFF} > T_{BLANK}$  the loop is in a discharge or wait state until the loop comparator starts the next charge cycle by DRVON going high.

If an over current occurs during charge the loop is interrupted and DRVON is RESET. The offtime one-shot pulse width is widened to  $T_{OFF} = K_{OFF} / V_{OUT}$ , which holds the loop in discharge for that time. At the end of the off-time the loop is released and controlled by VOLOW. In this manner maximum inductor current is controlled on a cycle-by-cycle basis. An assertion of UVLO (undervoltage lockout) or TSD (thermal shutdown) holds the loop in no-charge until the fault has ended.

#### **On-Time Control - Discharge Phase**

The discharge phase follows with the high side PMOS switch opening and the low side NMOS switch closing to provide a discharge path for the inductor current. The decreasing inductor current and the load current cause the output voltage to drop. Under normal load conditions when the inductor current is below the programmed limit, the off-time will continue until the output voltage falls below the regulation threshold, which initiates a new charge cycle via the loop comparator.

The inductor current "floats" in continuous conduction mode. During this mode the inductor peak current is below the programmed limit and the valley current is above zero. This is to satisfy load currents that are greater than half the minimum current ripple. The current ripple, I<sub>LR</sub>, is defined by the equation:

$$I_{LR} \approx \frac{K_{ON}}{L} * \frac{V_{IN} - V_{OUT} - I_{OUT} * R_{CH}}{V_{IN} - V_{OUT}}$$

where:

L = Inductor value

$I_{OUT} = Load current$

$R_{CH}$  = PMOS on resistance, 0.3 $\Omega$  typ.

If the  $I_{OUT}$  \*  $R_{CH}$  term is negligible compared with ( $V_{IN}$  -  $V_{OUT}$ ), the above equation simplifies to:

$$I_{LR} \approx \frac{K_{ON}}{L}$$

For most applications, the inductor current ripple controlled by the SP6654 is constant regardless of input and output voltage. Because the output voltage ripple is equal to:

$$V_{OUT}$$

(ripple) =  $I_{LR} * R_{ESR}$

where:

$R_{ESR} = ESR$  of the output capacitor

the output ripple of the SP6654 regulator is independent of the input and output voltages. For battery powered applications, where the battery voltage changes significantly, the SP6654 provides constant output voltage ripple throughout the battery lifetime. This greatly simplifies the LC filter design.

The maximum loop frequency in CCM is defined by the equation:

$$F_{LP} \approx \frac{(V_{IN} - V_{OUT}) * (V_{OUT} + I_{OUT} * R_{DC})}{K_{ON} * [V_{IN} + I_{OUT} * (R_{DC} - R_{CH})]}$$

where:

$F_{LP}$  = CCM loop frequency

$R_{DC}$  = NMOS on resistance, 0.3 $\Omega$  typ.

Ignoring conduction losses simplifies the loop frequency to:

$$F_{LP} \approx \frac{1}{K_{ON}} * \frac{V_{OUT}}{V_{IN}} * (V_{IN} - V_{OUT})$$

AND'ing the loop comparator and the on-timer reduces the switching frequency for load currents below half the inductor ripple current. This increases light load efficiency. The minimum on-time insures that the inductor current ripple is a minimum of  $K_{ON}/L$ , more than the load

current demands. The converter goes in to a standard pulse frequency modulation (PFM) mode where the switching frequency is proportional to the load current.

#### Low Dropout and Load Transient Operation

AND'ing the loop comparator also increases the duty ratio past the ideal  $D = V_{OUT}/V_{IN}$  up to and including 100%. Under a light to heavy load transient, the loop comparator will hold the main switch on longer than the minimum on timer until the output is brought back into regulation.

Also, as the input voltage supply drops down close to the output voltage, the main MOSFET resistance loss will dictate a much higher duty ratio to regulate the output. Eventually as the input voltage drops low enough, the output voltage will follow, causing the loop comparator to hold the converter at 100% duty cycle.

This mode is critical in extending battery life when the output voltage is at or above the minimum usable input voltage. The dropout voltage is the minimum (V<sub>IN</sub> -V<sub>OUT</sub>) below which the output regulation cannot be maintained. The dropout voltage of SP6654 is equal to I<sub>L</sub>\* (0.3 $\Omega$ + R<sub>L1</sub>) where 0.3 $\Omega$  is the typical R<sub>DS(ON)</sub> of the P-Channel MOSFET and R<sub>L</sub> is the DC resistance of the inductor.

The SP6654 has been designed to operate in dropout with a light load Iq of only  $80\mu$ A. The on-time control circuit seamlessly operates the converter between CCM, DCM, and low dropout modes without the need for compensation. The converter's transient response is quick since there is no compensated error amplifier in the loop.

#### Inductor Over-Current Protection

To reduce the light load dropout Iq, the SP6654 over-current system is only enabled when  $I_{L1} >$ 400mA. The inductor over-current protection circuitry is programmed to limit the peak inductor current to 1.25A. This is done during the ontime by comparing the source to drain voltage drop of the PMOS passing the inductor current with a second voltage drop representing the maximum allowable inductor current. As the two voltages become equal, the over-current comparator triggers a minimum off-time one shot. The off-time one shot forces the loop into the discharge phase for a minimum T<sub>OFF</sub> time causing the inductor current to decrease. At the end of the off-time, loop control is handed back to the AND'd on-time signal. If the output voltage is still low, charging begins until the output is in regulation or the current limit has been reached again. During startup and overload conditions, the converter behaves like a current source at the programmed limit minus half the current ripple. The minimum T<sub>OFF</sub> is controlled by the equation:

$$T_{OFF (MIN)} = \frac{K_{OFF}}{V_{OUT}}$$

#### Under-Voltage Lockout

The SP6654 is equipped with a programmable under-voltage lockout to protect the input battery source from excessive currents when substantially discharged. When the input supply is below the UVLO threshold both power switches are open to prevent inductor current from flowing. The three levels of falling input voltage UVLO threshold are shown in Table 1, with a typical hysteresis of 120mV to prevent chattering due to the impedance of the input source. During UVLO, PWR<sub>GD</sub> is forced low.

#### **Under-Current Detection**

The synchronous rectifier is comprised of an inductor discharge switch, a voltage comparator, and a driver latch. During the off-time, positive inductor current flows into the PGND pin 9 through the low side NMOS switch to LX pin 10, through the inductor and the output capacitor, and back to pin 9. The comparator monitors the voltage drop across the discharge NMOS. As the inductor current approaches zero, the channel voltage sign goes from negative to positive, causing the comparator to trigger the driver latch and open the switch to prevent inductor current reversal. This circuit along with the on-timer puts the converter into PFM mode and improves light load efficiency when the load current is less than half the inductor ripple current defined by  $K_{ON}/L$ .

#### Shutdown/Enable Control

The D0, D1 pins 4,5 of the device are logic level control pins that according to Table 1 shut down the converter when both are a logic low, or enables the converter when either are a logic high. When the converter is shut down, the power switches are opened and all circuit biasing is extinguished leaving only junction leakage currents on supply pins 1 and 2. After pins 4 or 5 are brought high to enable the converter, there is a turn on delay to allow the regulator circuitry to reestablish itself. Power conversion begins with the assertion of the internal reference ready signal which occurs approximately 150µs after the enable signal is received.

#### Power Good Indicator

A power good indicator looks at the voltage on the feedback node. When this voltage is below 0.75V, the open drain NMOS on pin 3 sinks current to ground. Tying a resistor from pin 3 to  $V_{\rm IN}$  or  $V_{OUT}$  creates a logic level power good indicator.  $PWR_{GD}$  is forced low when in UVLO.

#### External Feedback Pin

The FB pin 6 is compared to an internal reference voltage of 0.8V to regulate the SP6654 output. The output voltage can be externally programmed within the range  $\pm 1.0V$  to  $\pm 5.0V$ by tying a resistor from FB to ground and FB to V<sub>OUT</sub> (pin7). See the applications section for resistor selection information.

#### **APPLICATION INFORMATION**

#### Inductor Selection

The SP6654 uses a specially adapted minimum on-time control of regulation utilizing a precision comparator and bandgap reference. This adaptive minimum on-time control has the advantage of setting a constant current ripple for a given inductor size. From the operations section it has been shown:

Inductor Current Ripple,  $I_{LR} \approx \frac{K_{ON}}{L}$

For the typical SP6654 application circuit with inductor size of 10 $\mu$ H, and K<sub>ON</sub> of 2V\* $\mu$ sec, the SP6654 current ripple would be about 200mA, and

would be fairly constant for different input and output voltages, simplifying the selection of components for the SP6654 power circuit. Other inductor values could be selected, as shown in Table 2 Components Selection. Using a larger value than 10 $\mu$ H in an attempt to reduce output voltage ripple would reduce inductor current ripple and may not produce as stable an output ripple. For larger inductors with the SP6654, which has a peak inductor current of 1.25A, most 15 $\mu$ H or 22 $\mu$ H inductors would have to be larger physical sizes, limiting their use in small portable applications. Smaller values like 6.8 $\mu$ H would more easily meet the 1.25A limit and come in small case sizes, and the increased inductor current ripple of almost 300mA would produce very stable regulation and fast load transient response at the expense of slightly reduced efficiency.

Other inductor parameters are important: the inductor current rating and the DC resistance. When the current through the inductor reaches the level of  $I_{SAT}$ , the inductance drops to 70% of the nominal value. This non-linear change can cause stability problems or excessive fluctuation in inductor current ripple. To avoid this, the inductor should be selected with saturation current at least equal to the maximum output current of the converter plus half the inductor current ripple. To provide the best performance in dynamic conditions such as start-up and load transients, inductors should be chosen with saturation current close to the SP6654 inductor current limit of 1.25A.

DC resistance, another important inductor characteristic, directly affects the efficiency of the converter, so inductors with minimum DC resistance should be chosen for high efficiency designs. Recommended inductors with low DC resistance are listed in table 2. Preferred inductors for on board power supplies with the SP6654 are magnetically shielded types to minimize radiated magnetic field emissions.

#### **Capacitor Selection**

The SP6654 has been designed to work with very low ESR output capacitors (listed in Table 2 Component Selection) which for the typical application circuit are  $22\mu$ F ceramic, POSCAP or Aluminum Polymer. These capacitors combine small size, low ESR and good value. To regulate the output with low ESR capacitors of 0.01 $\Omega$  or less, an internal ramp voltage V<sub>RAMP</sub> has been added to the FB signal to reliably trip the loop comparator (as described in the Operations section).

Output ripple for a buck regulator is determined mostly by output capacitor ESR, which for the SP6654 with a constant inductor current ripple can be expressed as:

$V_{OUT}$  (ripple) =  $I_{LR} * R_{ESR}$

For the 22 $\mu$ F POSCAP with 0.04 $\Omega$  ESR, and a 10µH inductor yielding 200mA inductor current ripple ILR, the VOUT ripple would be 8mVpp. Since 8mV is a very small signal level, the actual value would probably be larger due to noise and layout issues, but this illustrates that the SP6654 output ripple can be very low indeed. To improve stability, a small ceramic capacitor,  $C_F = 22pF$ should be paralleled with the feedback voltage divider RF, as shown on the typical application schematic on page 1. Another function of the output capacitance is to hold up the output voltage during the load transients and prevent excessive overshoot and undershoot. The typical performance characteristics curves show very good load step transient response for the SP6654 with the recommended output capacitance of 22µF ceramic.

The input capacitor will reduce the peak current drawn from the battery, improve efficiency and significantly reduce high frequency noises induced by a switching power supply. The typical input capacitor for the SP6654 is 22µF ceramic, POSCAP or Aluminum Polymer. These capacitors will provide good high frequency bypassing and their low ESR will reduce resistive losses for higher efficiency. An RC filter is recommended for the V<sub>IN</sub> pin 2 to effectively reduce the noise for the ICs analog supply rail which powers sensitive circuits. This time constant needs to be at least 5 times greater than the switching period, which is calculated as 1/FLP during the CCM mode. The typical application schematic uses the values of  $R_{VIN} = 10\Omega$  and  $C_{VIN} = 1\mu F$  to meet these requirements.

|                     |                       | IND            | UCTOR                                                      | ร รเ                 | JRFACE                     | ЕМС   | тиис                    | Г                     |                         |                         |                |

|---------------------|-----------------------|----------------|------------------------------------------------------------|----------------------|----------------------------|-------|-------------------------|-----------------------|-------------------------|-------------------------|----------------|

|                     |                       |                |                                                            |                      | Inductor                   | Spe   | cificat                 | ion                   |                         |                         |                |

| Inductance<br>(µH)  | Manufacturer/Part No. | Series         | ries R Ω I <sub>SAT</sub> (A) Size Ind<br>LxW(mm) Ht. (mm) |                      | Inductor Type              |       | Manufacturer<br>Website |                       |                         |                         |                |

| (μΠ)<br>10          | Sumida CDRH5D28-100   | 0.048 1.30     |                                                            | 5.7 x 5              | <i>'</i>                   | 3.0   | - /                     | Shielded Ferrite Core |                         | sumida.com              |                |

| 10                  | TDK RLF5018T-100MR94  | 0.056          | 0.                                                         | .94                  | 5.6 x 5.                   | .2    | 2.0                     | ) Shi                 | Shielded Ferrite Core   |                         | tdk.com        |

| 10                  | Coilcraft DO1608C-103 | 0.160          | 1.                                                         | 10                   | 6.6 x 4                    | .5    | 2.9                     | 9 Uns                 | hielded Ferrite         | Core                    | coilcraft.com  |

| 10                  | Coilcraft LPO6013-103 | 0.300          | 0.                                                         | .70                  | 6.0 x 5                    | .4    | 1.3                     | 3 Uns                 | hielded Ferrite         | Core                    | coilcraft.com  |

| 6.8                 | Sumida CDRH5D28-6R8   | 0.081          | 1.                                                         | 1.12 4.7 x 4.5 3.0 S |                            | ) Shi | Shielded Ferrite Core   |                       | sumida.com              |                         |                |

| 6.8                 | TDK RLF5018T-6R8M1R1  | 0.47 1.10      |                                                            | 5.6 x 5.             | .2                         | 2.0 S |                         | Shielded Ferrite Core |                         | tdk.com                 |                |

| 6.8                 | Coilcraft DO1608C-682 | 0.130          | 0.130 1.20                                                 |                      | 6.6 x 4                    | .5    | 2.9                     | 9 Uns                 | Inshielded Ferrite Core |                         | coilcraft.com  |

| 6.8                 | Coilcraft LPO6013-103 | 0.200          | 0 0.60 6.0 x 5.4                                           |                      | 1.3                        | 3 Uns | Unshielded Ferrite Core |                       | coilcraft.com           |                         |                |

|                     |                       | CAP            | ACITOR                                                     | S - S                | URFAC                      | E N   | IOUN                    | T                     |                         |                         |                |

|                     |                       |                |                                                            | Ca                   | apacitor S                 | peci  | ficatio                 | n                     |                         |                         |                |

| Capacitance<br>(µF) | Manufacturer/Part No. | ESR<br>Ω (max) | RippleCurr<br>(A) @ 45                                     | -                    | Size V<br>LxW(mm) Ht. (mm) |       | Voltage<br>(V)          | Capacitor             | Туре                    | Manufacturer<br>Website |                |

| 22                  | TDK C3216X5R0J226M    | 0.002          | 3.00                                                       |                      | 3.2 x 1.6                  | 1     | .6                      | 6.3                   | X5R Cera                | nic                     | tdk.com        |

| 22                  | SANYO 6APA22M         | 0.040          | 1.90                                                       |                      | 7.3 x 4.3                  | 2     | .0                      | 6.3                   | POSCAP                  |                         | sanyovideo.com |

| 47                  | TDK C3225X5R0J46M     | 0.002          | 4.00                                                       |                      | 3.2 x 1.6                  | 1     | .6                      | 6.3                   | X5R Cerar               | nic                     | tdk.com        |

| 47                  | SANYO 6TPA47M         | 0.040          | 1.90                                                       |                      | 6.0 x 3.2                  | 2     | .8                      | 6.3                   | POSCAP                  |                         | sanyovideo.com |

Note: Components highlighted in bold are those used on the SP6654 Evaluation Board.

Table 2 Component Selection

#### Output Voltage Program

The output voltage is programmed by the external divider, as shown in the typical application circuit on page 1. First pick a value for  $R_I$  that is no larger than 300K. Too large a value of  $R_I$  will reduce the AC voltage seen by the loop comparator since the internal FB pin capacitance can form a low pass filter with  $R_F$  in parallel with  $R_I$ . The formula for  $R_F$  with a given  $R_I$  and output voltage is:

$$\mathbf{R}_{\mathrm{F}} = \left(\frac{\mathbf{V}_{\mathrm{OUT}}}{0.8\mathrm{V}} - 1\right) \bullet \mathbf{R}_{\mathrm{I}}$$

#### **Output Voltage Ripple Frequency**

An important consideration in a power supply application is the frequency value of the output ripple. Given the control technique of the SP6654 (as described in the operations section), the frequency of the output ripple will vary when in light to moderate load in the discontinuous or PFM mode. For moderate to heavy loads greater than about 100mA inductor current ripple, (for the typical  $10\mu$ H inductor application on 100mA is half the 200mA inductor current ripple), the output ripple frequency will be fairly constant. From the operations section, this maximum loop frequency in continuous conduction mode is:

$$F_{LP} \approx \frac{1}{K_{ON}} * \frac{V_{OUT}}{V_{IN}} * (V_{IN} - V_{OUT})$$

Data for loop frequency, as measured from output voltage ripple frequency, can be found in the typical performance curves.

#### Layout Considerations

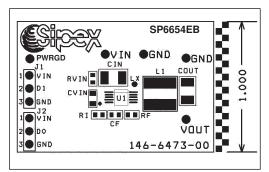

Proper layout of the power and control circuits is necessary in a switching power supply to obtain good output regulation with stability and a minimum of output noise. The SP6654 application circuit can be made very small and reside close to the IC for best performance and solution size, as long as some layout techniques are taken into consideration. To avoid excessive interference between the SP6654 high frequency converter and

#### **APPLICATION INFORMATION**

the other active components on the board, some rules should be followed. Refer to the typical application schematic on page 1 and the sample PCB layout shown in the following figures to illustrate how to layout a SP6654 power supply.

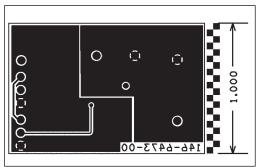

Avoid injecting noise into the sensitive part of circuit via the ground plane. Input and output capacitors conduct high frequency current through the ground plane. Separate the control and power grounds and connect them together at a single point. Power ground plane is shown in the figure titled PCB top sample layout and connects the ground of the  $C_{OUT}$  capacitor to the ground of the

$C_{IN}$  capacitor and then to the PGND pin 10. The control ground plane connects from pin 9 GND to ground of the  $C_{VIN}$  capacitor and the  $R_I$  ground return of the feedback resistor. These two separate control and power ground planes come together in the figure titled PCB top sample layout where SP6654 pin 9 GND is connected to pin 10 PGND.

Power loops on the input and output of the converter should be laid out with the shortest and widest traces possible. The longer and narrower the trace, the higher the resistance and inductance it will have. The length of traces in series with the capacitors increases its ESR and ESL and reduces their effectiveness at high frequencies. Therefore, put the 1µF bypass capacitor as close to the V<sub>IN</sub> and GND pins of the converter as possible, the 22µF  $C_{IN}$  close to the  $P_{VIN}$  pin and the  $22\mu F$  output capacitor as close to the inductor as possible. The external voltage feedback network R<sub>F</sub>, R<sub>I</sub> and feedforward capacitor C<sub>F</sub> should be placed very close to the FB pin. Any noise traces like the LX pin should be kept away from the voltage feedback network and separated from it by using power ground copper to minimize EMI.

Figure 19. SP6654 PCB Component Sample Layout

Figure 21. SP6654 PCB Bottom Sample Layout

Figure 20. SP6654 PCB Top Sample Layout

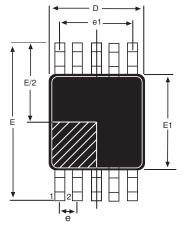

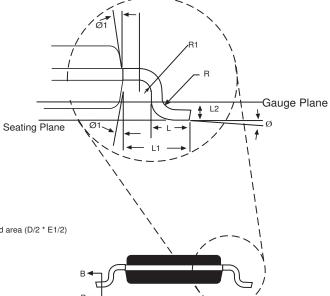

Pin #1 indentifier must be indicated within this shaded area (D/2 \* E1/2)

| 10 Pin MSOP JEDEC MO-187 (BA) Variation |             |          |      |  |  |  |  |

|-----------------------------------------|-------------|----------|------|--|--|--|--|

| SYMBOL                                  | MIN         | NOM      | MAX  |  |  |  |  |

| A                                       | -           | -        | 1.1  |  |  |  |  |

| A1                                      | 0           | -        | 0.15 |  |  |  |  |

| A2                                      | 0.75        | 0.85     | 0.95 |  |  |  |  |

| b                                       | 0.17        | -        | 0.27 |  |  |  |  |

| С                                       | 0.08        | -        | 0.23 |  |  |  |  |

| D                                       |             | 3.00 BSC |      |  |  |  |  |

| E                                       | 4.90 BSC    |          |      |  |  |  |  |

| E1                                      | 3.00 BSC    |          |      |  |  |  |  |

| e                                       | 0.50 BSC    |          |      |  |  |  |  |

| e1                                      |             | 2.00 BSC |      |  |  |  |  |

| L                                       | 0.4 0.6 0.8 |          |      |  |  |  |  |

| L1                                      |             | 0.95 REF |      |  |  |  |  |

| L2                                      |             | 0.25 BSC |      |  |  |  |  |

| N                                       | - 10 -      |          |      |  |  |  |  |

| R                                       | 0.07        | -        | -    |  |  |  |  |

| R1                                      | 0.07        | -        | -    |  |  |  |  |

| Ø                                       | 0° - 8°     |          |      |  |  |  |  |

| ø1                                      | 00          | -        | 15°  |  |  |  |  |

Note: Dimensions in (mm)

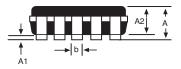

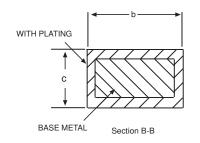

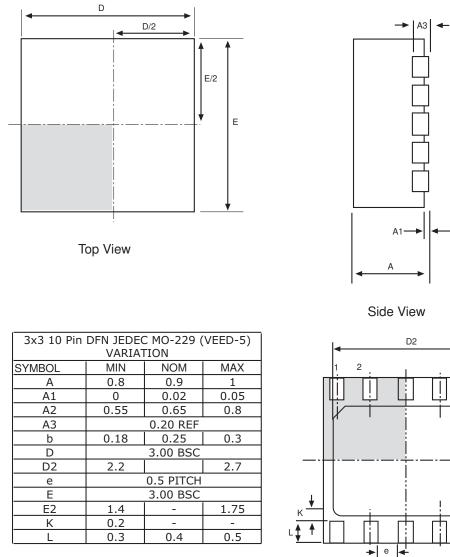

Note: Dimensions in (mm)

▶ b ►

E2

#### **ORDERING INFORMATION**

| Part Number | Operating Temperature Range | Top Mark | Package Type |

|-------------|-----------------------------|----------|--------------|

| SP6654EU    | 40°C to +85°C               | SP6654EU | 10 Pin MSOP  |

| SP6654EU/TR | 40°C to +85°C               | SP6654EU | 10 Pin MSOP  |

| SP6654ER    | 40°C to +85°C               | SP6654ER | 10 Pin DFN   |

| SP6654ER/TR | 40°C to +85°C               | SP6654ER | 10 Pin DFN   |

|             |                             |          |              |

Available in lead free packaging. To order add "-L" suffix to part number.

Example: SP6654EU/TR = standard; SP6654EU-L/TR = lead free

/TR = Tape and Reel

Pack quantity is 2,500 for MSOP and 3,000 for DFN

Sipex Corporation

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others.