Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### SP690A/692A/802L/ 802M/805L/805M

# Low Power Microprocessor Supervisory with Battery Switch-Over

#### **FEATURES**

- Precision Voltage Monitor: SP690A/SP802L/SP805L at 4.65V SP692A/SP802M/SP805M at 4.40V

- Reset Time Delay 200ms

- Watchdog Timer 1.6 sec timeout

- Minimum component count

- 60µA Maximum Operating Supply Current

- 0.6µA Maximum Battery Backup Current

- 0.1µA Maximum Battery Standby Current

- Power Switching

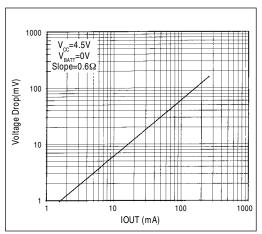

250mA Output in V<sub>cc</sub> Mode (0.6Ω)

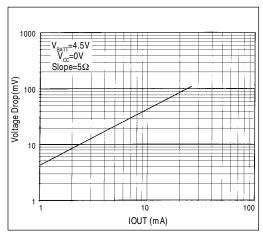

25mA Output in Battery Mode (5Ω)

- Voltage Monitor for Power Fail or Low Battery Warning

- Available in 8 pin SO and DIP packages

- RESET asserted down to V<sub>cc</sub> = 1V

Now Available in Lead Free Packaging

■ Pin Compatible Upgrades to MAX690A/692A/802L/802M/805L

#### **APPLICATIONS**

- Critical µP Power Monitoring

- Intellegent Instruments

- Computers

- Controllers

#### DESCRIPTION

The **SP690A/692A/802L/802M/805L/805M** are a family of microprocessor ( $\mu$ P) supervisory circuits that integrate a myriad of components involved in discrete solutions to monitor power-supply and battery-control functions in  $\mu$ P and digital systems. The series will significantly improve system reliability and operational efficiency when compared to discrete solutions. The features of the **SP690A/692A/802L/802M/805L/805M** include a watchdog timer, a  $\mu$ P reset and backup-battery switchover, and power-failure warning, a complete  $\mu$ P monitoring and watchdog solution. The series is ideal for applications in automotive systems, computers, controllers, and intelligent instruments. All designs where it is critical to monitor the power supply to the  $\mu$ P and it's related digital components will find the series to be an ideal solution.

| PART NUMBER | RESET<br>Threshold | RESET<br>Accuracy | RESET Active | PFI Accuracy |

|-------------|--------------------|-------------------|--------------|--------------|

| SP690A      | 4.65 V             | 125mV             | LOW          | 4%           |

| SP692A      | 4.40 V             | 125mV             | LOW          | 4%           |

| SP802L      | 4.65 V             | 75mV              | LOW          | 2%           |

| SP802M      | 4.40 V             | 75mV              | LOW          | 2%           |

| SP805L      | 4.65 V             | 125mV             | HIGH         | 4%           |

| SP805M      | 4.40 V             | 125mV             | HIGH         | 4%           |

#### **ABSOLUTE MAXIMUM RATINGS**

These are stress ratings only and functional operation of the device at these ratings or any other above those indicated in the operation sections of the specifications below is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability and cause permanent damage to the device.

| V <sub>CC</sub> 0.3V to 6.0V<br>V <sub>BATT</sub> 0.3V to 6.0V                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------|

| All Other Inputs (NOTE 1)0.3V to (V <sub>CC</sub> to 0.3V)                                                                          |

| Input Current:                                                                                                                      |

| V <sub>CC</sub> 250mA                                                                                                               |

| V <sub>BATT</sub> 50mA                                                                                                              |

| GND20mA                                                                                                                             |

| Output Current:                                                                                                                     |

| V <sub>out</sub> Short-Circuit Protected for up to 10sec                                                                            |

| All Other Inputs20mA                                                                                                                |

|                                                                                                                                     |

| Rate of Rise V V 100V/us                                                                                                            |

| Rate of Rise, $V_{CC}$ , $V_{BATT}$ 100V/ $\mu$ s Continuous Power Dissipation500mW                                                 |

| Rate of Rise, V <sub>CC</sub> , V <sub>BATT</sub> 100V/μs<br>Continuous Power Dissipation500mW<br>Storage Temperature65°C to +160°C |

| Storage Temperature65°C to +160°C                                                                                                   |

|                                                                                                                                     |

ESD (ElectroStatic Discharge) sensitive device. Permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts.

Personnel should be properly grounded prior to handling this device. The protective foam should be discharged to the destination socket before devices are removed.

#### **ELECTRICAL CHARACTERISTICS**

$V_{cc}$ =4.75v to 5.50V for SP690A/SP802L/SP805L,  $V_{CC}$ =4.50V to 5.50V for SP692A/SP802M/SP805M,  $V_{BATT}$ =2.80V,  $T_A$ = $T_{MIN}$  to  $T_{MAX}$ , typical specified at 25°C, unless otherwise noted.

| PARAMETERS                                                                            | MIN.                         | TYP.                                                 | MAX.                         | UNITS | CONDITIONS                                                                                                                                                               |

|---------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------|------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operating Voltage Range,                                                              | 0                            |                                                      | 5.5                          | Volts |                                                                                                                                                                          |

| V <sub>CC</sub> or V <sub>BATT</sub> , Note 2                                         |                              |                                                      |                              |       |                                                                                                                                                                          |

| Supply Current, I <sub>SUPPLY</sub> ,                                                 |                              | 35                                                   | 60                           | μΑ    | excluding I <sub>OUT</sub>                                                                                                                                               |

| $I_{SUPPLY}$ in Battery Backup Mode, $V_{CC} = 0V, V_{BATT} = 2.8V$                   |                              | 0.001                                                | 0.6                          | μА    |                                                                                                                                                                          |

| V <sub>BATT</sub> Standby Current, NOTE 3                                             | -0.1                         |                                                      | 0.02                         | μΑ    | $V_{CC} > V_{BATT} + 0.2V$                                                                                                                                               |

| V <sub>OUT</sub> Output                                                               | V <sub>cc</sub> - 0.1        | V <sub>cc</sub> - 0.03<br>V <sub>cc</sub> - 0.15     |                              | Volts | $I_{\text{OUT}} = 50\text{mA}$ $I_{\text{OUT}} = 250\text{mA}$                                                                                                           |

| V <sub>OUT</sub> in Battery-Backup Mode<br>V <sub>CC</sub> < V <sub>BATT</sub> - 0.2V | V <sub>BATT</sub> -0.15      | V <sub>BATT</sub> - 0.04<br>V <sub>BATT</sub> - 0.20 |                              | Volts | I <sub>OUT</sub> = 5mA<br>I <sub>OUT</sub> = 25mA                                                                                                                        |

| Battery Switch Threshold, $V_{\rm CC}$ to $V_{\rm BATT}$                              |                              | 20<br>-20                                            |                              | mV    | Power-up<br>Power-down                                                                                                                                                   |

| Battery Switchover Hysteresis                                                         |                              | 40                                                   |                              | mV    | Peak to Peak                                                                                                                                                             |

| Reset Threshold                                                                       | 4.50<br>4.25<br>4.55<br>4.30 | 4.65<br>4.40                                         | 4.75<br>4.50<br>4.70<br>4.45 | Volts | SP690A, SP802L, SP805L<br>SP692A, SP802M, SP805M<br>SP802L, T <sub>A</sub> = +25° C, V <sub>CC</sub> falling<br>SP802M, T <sub>A</sub> = +25° C, V <sub>CC</sub> falling |

#### **ELECTRICAL CHARACTERISTICS**

V<sub>cc</sub>=4.75v to 5.50V for SP690A/SP802L/SP805L, V<sub>cc</sub>=4.50V to 5.50V for SP692A/SP802M/SP805M, V<sub>BATT</sub>=2.80V, T<sub>A</sub>=T<sub>MIN</sub> to T<sub>MAX</sub>, typical specified at 25°C, unless otherwise noted

| PARAMETERS                                           | MIN.                  | TYP.           | MAX.           | UNITS | CONDITIONS                                    |

|------------------------------------------------------|-----------------------|----------------|----------------|-------|-----------------------------------------------|

| Reset Threshold Hysteresis                           |                       | 40             |                | mV    | Peak to Peak                                  |

| Reset Pulse Width, t <sub>RS</sub>                   | 140                   | 200            | 280            | ms    |                                               |

| RESET Output Voltage,                                | V <sub>cc</sub> - 1.5 |                |                |       | I <sub>SOURCE</sub> = 800μA                   |

| NOTE 5                                               |                       | 0.1            | 0.4            | Volts | $I_{SINK} = 3.2mA$                            |

|                                                      |                       | 0.004          | 0.3            |       | $I_{SINK} = 50\mu A$ , $V_{CC} = 1.0$         |

| RESET Output Voltage,                                | 0.8                   |                |                |       | $I_{SOURCE} = 4\mu A$ , $V_{CC} = 1.0V$ ,     |

| NOTE 6                                               | V <sub>cc</sub> - 1.5 |                |                | Volts | $I_{SOURCE} = 800\mu A$                       |

|                                                      |                       | 0.1            | 0.4            |       | $I_{SINK} = 3.2mA$                            |

| Watchdog Timeout, t <sub>wD</sub>                    | 1.00                  | 1.60           | 2.25           | sec   |                                               |

| WDI Pulse Width, t <sub>WP</sub> NOTE 7              | 50                    |                |                | ns    | $V_{IL} = 0.4V, V_{IH} = (0.8)(V_{CC})$       |

| WDI Input Threshold,<br>V <sub>CC</sub> = 5V, NOTE 4 | 3.5                   |                | 0.8            | Volts | Logic low<br>Logic high                       |

| WDI Input Current                                    | -150                  | 50<br>-50      | 150            | μА    | WDI =V <sub>CC</sub><br>WDI = 0V              |

| PFI Input Threshold                                  | 1.200<br>1.225        | 1.250<br>1.250 | 1.300<br>1.275 | Volts | SP690A/692A, SP805L/M<br>SP802L/M             |

| PFI Input Current                                    | -25                   | 0.01           | 25             | nA    |                                               |

| PFO Output Voltage                                   | V <sub>CC</sub> - 1.5 | 0.1            | 0.4            | Volts | $I_{SOURCE} = 800 \mu A$ $I_{SINK} = 3.2 m A$ |

**NOTE 1:** The input voltage limits on PFI (pin 4) and WDI (pin 6) may be exceeded if the current into these pins is limited to less than 10 mA.

**NOTE 2:** Either  $V_{CC}$  or  $V_{BATT}$  can go to 0V if the other is greater than 2.0V.

**NOTE 3:** "-" equals the battery-charging current, "+" equals the battery-discharging current.

**NOTE 4:** WDI is guaranteed to be in an intermediate, non-logic level state if WDI is floating and  $V_{cc}$  is in the operating voltage range. WDI is internally biased to 35% of  $V_{cc}$  with an input impedance of  $50K\Omega$ .

NOTE 5: SP690A, SP692A, SP802L, and SP802M only.

**NOTE 6:** SP805L and SP805M only.

**NOTE 7:** WDI Minimum Rise/Fall time is 2μs.

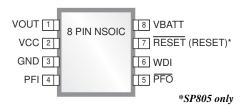

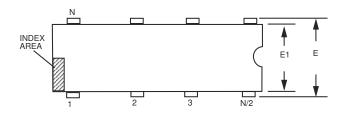

Figure 10. Pinout

#### **PIN ASSIGNMENTS**

Pin 1 — $V_{OUT}$  — Output Supply Voltage.  $V_{OUT}$  connects to  $V_{CC}$  when  $V_{CC}$  is greater than  $V_{BATT}$  and  $V_{CC}$  is above the reset threshold. When  $V_{CC}$  falls below  $V_{BATT}$  and  $V_{CC}$  is below the reset threshold,  $V_{OUT}$  connects to  $V_{BATT}$ . Connect a  $0.1\mu F$  capacitor from  $V_{OUT}$  to GND.

Pin 2 —  $V_{CC}$  — +5V Supply Input

Pin3 — GND — Ground reference for all signals

Pin 4 — PFI — Power-Fail Input. This is the noninverting input to the power-fail comparator. When PFI is less than 1.25V, PFO goes low. Connect PFI to GND or V<sub>OUT</sub> when not used.

Pin 5 — Power-Fail Output.

Pin 6 — WDI — Watchdog Input. WDI is a three level input. If WDI remains high or low for 1.6sec, the internal watchdog timer triggers a reset. If WDI is left floating or connected to a high-impedance tri-state buffer, the watchdog feature is disabled. The internal watchdog timer clears whenever reset is asserted.

Pin 7 for SP690A/692A/802 only — RESET (Active Low)—Reset Output. RESET Output goes low whenever V<sub>CC</sub> falls below the reset threshold or whenever WDI remains high or low longer than 1.6 seconds. RESET remains low for 200ms after V<sub>CC</sub> crosses the reset threshold voltage on power-up or after being triggered by WDI.

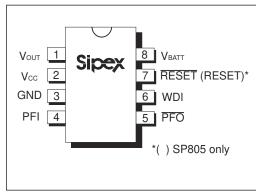

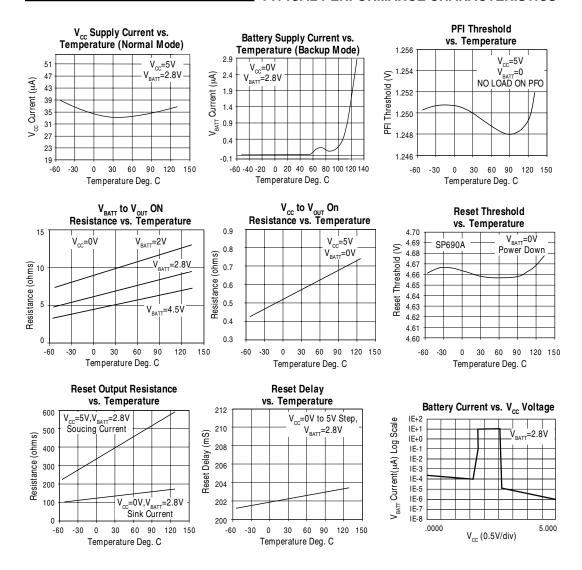

Figure 11. Internal Block Diagram

Pin 7 for **SP805 only** — RESET (Active High)—Reset Output is the inverse of  $\overline{RESET}$ ; when RESET is asserted, the RESET output voltage =  $V_{CC}$  or  $V_{BATT}$ , whichever is higher.

$\begin{array}{l} \operatorname{Pin} 8 - \operatorname{V_{BATT}} - \operatorname{Backup-Battery Input.} \ \operatorname{When} \\ \operatorname{V_{CC}} \text{ falls below the reset threshold, } \operatorname{V_{BATT}} \\ \text{will be switched to } \operatorname{V_{OUT}} \text{ if } \operatorname{V_{BATT}} \text{ is} \\ \operatorname{20mV} \text{ greater than } \operatorname{V_{CC}}. \ \operatorname{When} \operatorname{V_{CC}} \text{ rises} \\ \operatorname{20mV} \text{ above } \operatorname{V_{BATT}}, \operatorname{V_{OUT}} \text{ will be} \\ \operatorname{reconnected} \text{ to } \operatorname{V_{CC}}. \ \operatorname{The} \text{ } 40 \operatorname{mV} \\ \operatorname{hysteresis} \text{ prevents repeated switching if} \\ \operatorname{V_{CC}} \text{ falls slowly.} \end{array}$

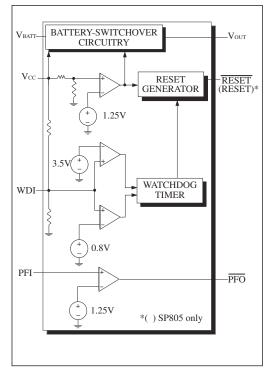

(25°C, unless otherwise noted)

Figure 1.  $V_{CC}$  to  $V_{OUT}$  Vs. Output Current

Figure 3A. SP690A RESET Output Voltage vs. Supply Voltage

Figure 4A. SP805L RESET Output Voltage vs. Supply Voltage

Figure 2.  $V_{BATT}$  to  $V_{OUT}$  Vs. Output Current

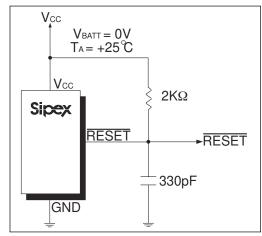

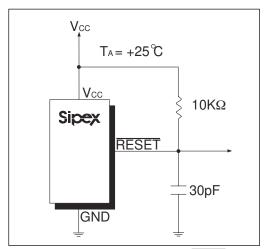

Figure 3B. Circuit for the SP690A/802L RESET Output Voltage vs. Supply Voltage

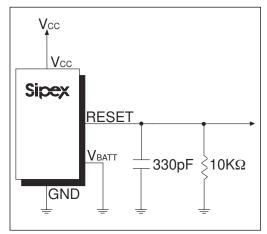

Figure 4B. Circuit for the SP805 RESET Output Voltage vs. Supply Voltage

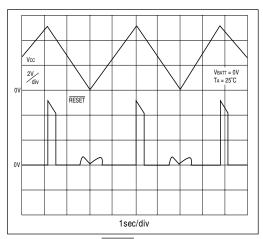

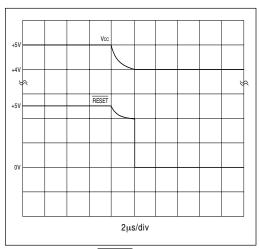

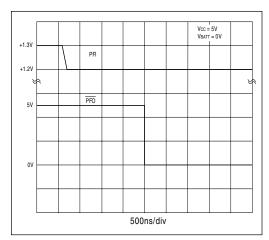

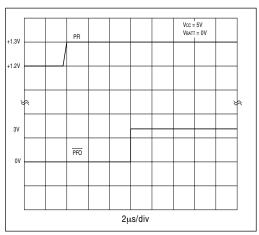

Figure 5A. SP690A RESET Response Time

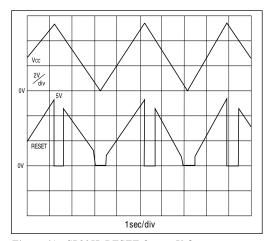

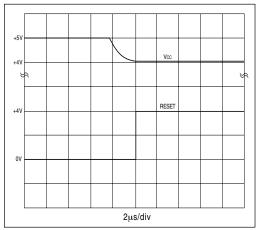

Figure 6A. SP805L RESET Response Time

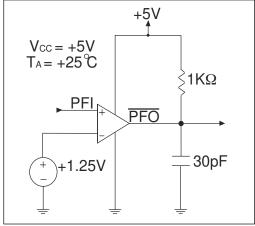

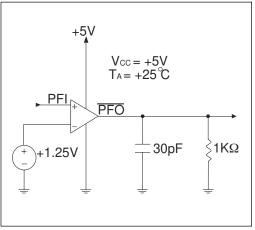

Figure 7A. Power-Fail Comparator Response Time (FALL)

Date: 11/29/04

Figure 5B. Circuit for the SP690A/802L  $\overline{RESET}$  Response Time

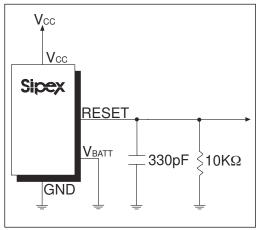

Figure 6B. Circuit for the SP805 RESET Response Time

Figure 7B. Circuit for the Power-Fail Comparator Response Time (FALL)

Figure 8A. Power-Fail Comparator Response Time (RISE)

Figure 8B. Circuit for the Power-Fail Comparator Response Time (RISE)

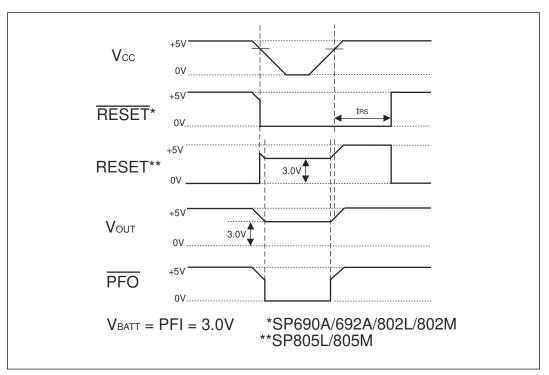

Figure 9. Timing Diagram

#### **FEATURES**

The SP690A/692A/802L/802M/805L/805M provide four key functions:

- 1. A battery backup switching for CMOS RAM, CMOS microprocessors, or other logic.

- 2. A reset output during power-up, power-down and brownout conditions.

- 3. A reset pulse if the optional watchdog timer has not been toggled within a specified time.

- 4. A 1.25V threshold detector for power-fail warning, low battery detection, or to monitor a power supply other than +5V.

The parts differ in their reset-voltage threshold levels and reset outputs. The **SP690A/802L/805L** generate a reset when the supply voltage drops below 4.65V. The **SP692A/802M/805M** generate a reset below 4.40V.

The SP690A/692A/802L/802M/805L/805M are ideally suited for applications in automotive systems, intelligent instruments, and battery-powered computers and controllers. All designs into an environment where it is critical to monitor the power supply to the  $\mu P$  and it's related digital components will find the SSP690A/692A/802L/802M/805L/805M ideal.

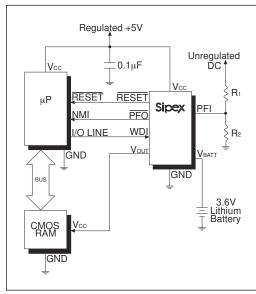

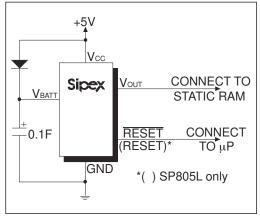

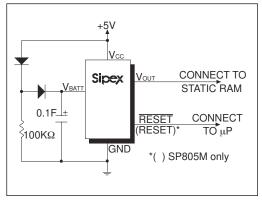

Figure 12. Typical Operating Circuit

#### THEORY OF OPERATION

The SP690A/692A/802L/802M/805L/805M microprocessor (μP) supervisory circuits monitor the power supplied to digital circuits such as microprocessors, microcontrollers, or memory. The series is an ideal solution for portable, battery-powered equipment that requires power supply monitoring. Implementing this series will reduce the number of components and overall complexity. The watchdog functions of this product family will continuously oversee the operational status of a system. The operational features and benefits of the SP690A/692A/802L/802M/805L/805M are described in more detail below.

#### **Reset Output**

The microprocessor's ( $\mu P's$ ) reset input starts the  $\mu P$  in a known state. When the  $\mu P$  is in an unknown state, it should be held in reset. The **SP690A/SP692A/SP802** assert reset during power-up and prevent code execution errors during power-down or brownout conditions.

On power-up, once  $V_{CC}$  reaches 1V,  $\overline{RESET}$  is guaranteed to be a logic low. As  $V_{CC}$  rises,  $\overline{RESET}$  remains low. When  $V_{CC}$  exceeds the reset threshold,  $\overline{RESET}$  will remain low for 200ms, Figure 9. If a brownout condition occurs and  $V_{CC}$  dips below the reset threshold,  $\overline{RESET}$  is triggered. Each time  $\overline{RESET}$  is triggered, it stays low for the reset pulse width interval. If a brownout condition interrupts a previously initiated reset pulse, the reset pulse continues for another 200ms. On power-down, once  $V_{CC}$  goes below the threshold,  $\overline{RESET}$  is guaranteed to be logic low until  $V_{CC}$  drops below 1V.

RESET is also triggered by a watchdog timeout. If WDI remains either high or low for a period that exceeds the watchdog timeout period (1.6 sec), RESET pulses low for 200mS. As long as RESET is asserted, the watchdog timer remains clear. When RESET comes high, the watchdog resumes timing and must be serviced within 1.6sec. If WDI is tied high or low, a RESET pulse is triggered every 1.8sec ( $t_{\rm WD}$  plus  $t_{\rm RS}$ ).

The **SP805L/M** active-high RESET output is the inverse of the **SP690A/SP692A/SP802** RESET output, and is valid with  $V_{CC}$  down to 1V. Some  $\mu$ P's, such as Intel's 80C51, require an active-high reset pulse.

#### Watchdog Input

The watchdog circuit monitors the  $\mu P$ 's activity. If the  $\mu P$  does not toggle the watchdog input (WDI) within 1.6sec, a reset pulse is triggered. The internal 1.6sec timer is cleared by either a reset pulse or by floating the WDI input. As long as RESET is asserted or the WDI input is floating, the timer remains cleared and does not count. As soon as RESET is released and WDI is driven high or low, the timer starts counting. It can detect pulses as short as 50ns.

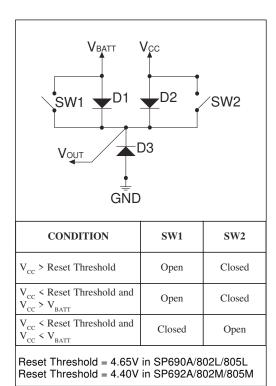

Figure 13. BACKUP-BATTERY Switchover Block Diagram

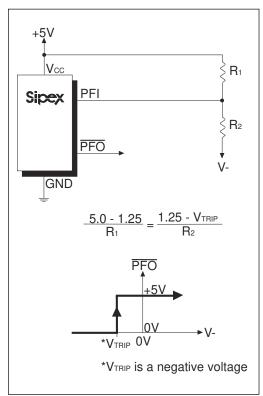

#### **Power-Fail Comparator**

The Power-Fail Comparator can be used as an under-voltage detector to signal the failing of a power supply (it is completely separate from the rest of the circuitry and does not need to be dedicated to this function). The PFI input is compared to an internal 1.25V reference. If PFI is less than 1.25V,  $\overline{PFO}$  goes low. The external voltage divider drives PFI to sense the unregulated DC input to the +5V regulator. The voltage-divider ratio can be chosen such that the voltage at PFI falls below 1.25V just before the +5V regulator drops out.  $\overline{PFO}$  then triggers an interrupt which signals the  $\mu P$  to prepare for power-down.

When V<sub>BATT</sub> connects to V<sub>OLIT</sub>, the power-fail comparator is turned off and PFO is forced low to conserve backup-battery power.

#### **Backup-Battery Switchover**

In the event of a brownout or power failure, it may be necessary to preserve the contents of RAM. With a backup battery installed at  $V_{BATT}$ , the RAM is assured to have power if  $V_{CC}$  fails. As long as  $V_{CC}$  exceeds the reset threshold,  $V_{OUT}$  connects to  $V_{CC}$  through a  $0.6\Omega$  PMOS power switch. Once  $V_{CC}$  falls below the reset threshold,  $V_{CC}$  or  $V_{BATT}$ , whichever is higher, switches to  $V_{OUT}$ .  $V_{BATT}$  connects to  $V_{OUT}$  through a  $5\Omega$  switch only when  $V_{CC}$  is below the reset threshold and  $V_{BATT}$  is greater than  $V_{CC}$ .

When  $V_{CC}$  exceeds the reset threshold, it is connected to  $V_{OUT}$ , regardless of the voltage applied to  $V_{BATT}$  Figure 13. During this time, the diode (D1) between  $V_{BATT}$  and  $V_{OUT}$  will conduct current from  $V_{BATT}$  to  $V_{OUT}$  if  $V_{BATT}$  is more than .6V above  $V_{OUT}$ .

When  $V_{BATT}$  connects to  $V_{OUT}$ , backup mode is activated and the internal circuitry will be powered from the battery *Figure 14*. When  $V_{CC}$  is just below  $V_{BATT}$ , in the backup mode the current drawn from  $V_{BATT}$  will be typically  $30\mu A$ . When  $V_{CC}$  drops to more than 1V below  $V_{BATT}$ , the internal switchover comparator shuts off and the supply current falls to less than  $0.6\mu A$ .

| SIGNAL                        | STATUS                                                                                                                 |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>cc</sub>               | Disconnected from V <sub>OUT</sub>                                                                                     |  |  |

| V <sub>OUT</sub>              | Connected to $V_{\text{BATT}}$ through an internal $8\Omega$ PMOS switch                                               |  |  |

| V <sub>BATT</sub>             | Connected to $V_{OUT}$ . Current drawn from the battery is less than 0.6 $\mu$ A, as long as $V_{CC} < V_{BATT}$ - 1V. |  |  |

| PFI                           | Power-fail comparator is disabled.                                                                                     |  |  |

| PFO                           | Logic low                                                                                                              |  |  |

| RESET                         | Logic low                                                                                                              |  |  |

| RESET                         | Logic high (SP805 only)                                                                                                |  |  |

| WDI Watchdog timer is disable |                                                                                                                        |  |  |

Figure 14. Input and Output Status in Battery-Backup Mode. To enter the Battery-Backup mode,  $V_{CC}$  must be less than the Reset threshold and less than  $V_{\rm BATT'}$

### Using a High Capacity Capacitor as a Backup Power Source

VBATT has the same operating voltage range as VCC, and the battery-switchover threshold voltages are typically +20mV centered at VBATT, allowing use of a capacitor and a simple charging circuit as a backup source (see *Figure 16*).

| PART<br>NUMBER             | MAXIMUM<br>BACKUP-BATTERY<br>VOLTAGE [V] |  |

|----------------------------|------------------------------------------|--|

| SP690A<br>SP802L<br>SP805L | 4.80                                     |  |

| SP692A<br>SP802M<br>SP805M | 4.55                                     |  |

Figure 15. Allowable BACKUP-BATTERY Voltages

Figure 16. Backup Power Source Using High Capacity Capacitor with SP690A/802L/805L and a +5V ±5% Supply

If VCC is above the reset threshold and VBATT is 0.5V above VCC, current flows to VOUT and VCC from VBATT until the voltage at VBATT is less than 0.5V above VCC.

Leakage current through the capacitor charging diode and the  $\bf SP690A/SP802L/SP805L$  internal power diode eventually discharges the capacitor to VCC. Also, if VCC and VBATT start from 0.5V above the reset threshold and power is lost at VCC, the capacitor on VBATT discharges through VCC until VBATT reaches the reset threshold; the  $\bf SP690A/SP802L/SP805L$  then switches to battery-backup mode.

Figure 17. Backup Power Source Using High Capacity Capacitor with SP692A/802M/805M and a  $+5V \pm 10\%$  Supply

Figure 18. Adding Hysteresis to the POWER-FAIL Comparator

### Allowable Backup Power-Source Batteries

Lithium batteries work very well as backup batteries due to very low self-discharge rate and high energy density. Single lithium batteries with open-circuit voltages of 3.0V to 3.6V are ideal. Any battery with an open-circuit voltage less than the minimum reset threshold plus 0.3V can be connected directly to the  $V_{\rm BATT}$  input of this series with no additional circuitry; see FIGURE 12. However, batteries with open-circuit voltages that are greater than this value cannot be used for backup, as current is sourced into  $V_{\rm OUT}$  through the diode (D1 in Figure 13) when  $V_{\rm CC}$  is close to the reset threshold.

### Operation Without a Backup Power Source

If a backup power source is not used, ground  $V_{BATT}$  and connect  $V_{OUT}$  to  $V_{CC}$ . Since there is no need to switch over to any backup power source,  $V_{OUT}$  does not need to be switched. A direct connection to  $V_{CC}$  eliminates any voltage drops across the switch which may push  $V_{OUT}$  below  $V_{CC}$ .

#### Replacing the Backup Battery

The backup battery can be removed while  $V_{CC}$  remains <u>valid</u>, without danger of triggering RESET/RESET. As long as  $V_{CC}$  stays above the reset threshold, battery-backup mode cannot be entered.

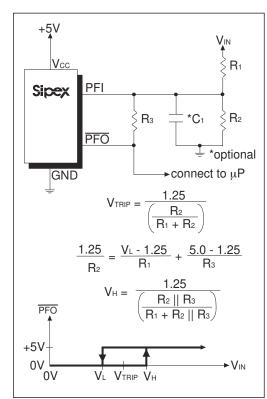

## Adding Hysteresis to the Power-Fail Comparator

Hysteresis adds a noise margin to the power-fail comparator and prevents repeated triggering of PFO when  $V_{\rm IN}$  is close to its trip point. Figure 18 shows how to add hysteresis to the power-fail comparator. Select the ratio of  $R_1$  and  $R_2$  such that PFI sees 1.25V when  $V_{\rm IN}$  falls to its trip point ( $V_{\rm TRIP}$ ).  $R_3$  adds the hysteresis. It will typically be an order of magnitude greater (about 10 times) than  $R_1$  or  $R_2$ . The current through  $R_1$  and  $R_2$  should be at least  $1\mu A$  to ensure that the 25 nA (max) PFI input current does not shift the trip point.  $R_3$  should be larger than  $10 K\Omega$  so it does not load down the PFO pin. Capacitor C1 adds additional noise rejection.

#### **Monitoring a Negative Voltage**

The power-fail comparator can be used to monitor a negative supply rail using the circuit of *Figure 19*. When the negative rail is valid,  $\overline{PFO}$  is low. When the negative supply voltage drops,  $\overline{PFO}$  goes high. This circuit's accuracy is affected by the PFI threshold tolerance, the  $V_{CC}$  voltage, and the resistors, R1 and R2.

Figure 19. Monitoring a Negative Voltage

Figure 20. Interfacing to Microprocessors with Bidirectional RESET I/O

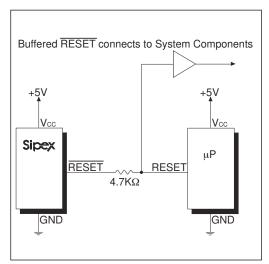

### Interfacing to Microprocessors with Bidirectional Reset Pins

Microprocessors with bidirectional reset pins, such as the Motorola 68HC11 series, can contend with this series'  $\overline{RESET}$  output. If, for example, the  $\overline{RESET}$  output is driven high and the  $\mu P$  wants to pull it low, indeterminate logic levels may result. To correct this, connect a 4.7K $\Omega$  resistor between the  $\overline{RESET}$  output and the  $\mu P$  reset I/O, as in Figure 20. Buffer the  $\overline{RESET}$  output to other system components.

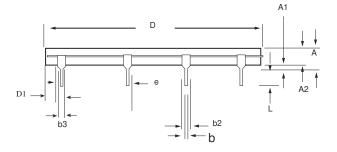

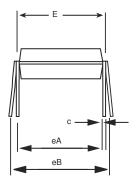

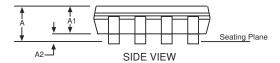

| 8 PIN PDIP JEDEC MS-001 (BA) Variation |          |       |       |  |

|----------------------------------------|----------|-------|-------|--|

| SYMBOL                                 | MIN      | NOM   | MAX   |  |

| Α                                      | -        | -     | 0.21  |  |

| A1                                     | 0.15     | -     | -     |  |

| A2                                     | 0.115    | 0.13  | 0.195 |  |

| b                                      | 0.014    | 0.018 | 0.022 |  |

| b2                                     | 0.045    | 0.06  | 0.07  |  |

| b3                                     | 0.3      | 0.039 | 0.045 |  |

| С                                      | 0.008    | 0.01  | 0.014 |  |

| D                                      | 0.355    | 0.365 | 0.4   |  |

| D1                                     | 0.005    | -     | -     |  |

| E                                      | 0.3      | 0.31  | 0.325 |  |

| E1                                     | 0.24     | 0.25  | 0.28  |  |

| е                                      | .100 BSC |       |       |  |

| eA                                     | .300 BSC |       |       |  |

| еВ                                     | 0.43     |       |       |  |

| L                                      | 0.115    | 0.13  | 0.15  |  |

Note: Dimensions in (mm)

TOP VIEW

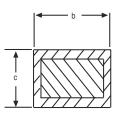

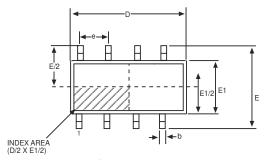

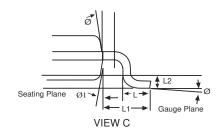

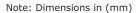

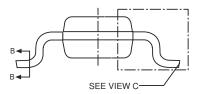

| 8 Pin NSOIC JEDEC MO-012 (AA) Variation |          |     |      |  |

|-----------------------------------------|----------|-----|------|--|

| SYMBOL                                  | MIN      | NOM | MAX  |  |

| Α                                       | 1.35     | -   | 1.75 |  |

| A1                                      | 0.1      | -   | 0.25 |  |

| A2                                      | 1.25     | -   | 1.65 |  |

| b                                       | 0.31     | -   | 0.51 |  |

| С                                       | 0.17     | -   | 0.24 |  |

| D                                       | 4.90 BSC |     |      |  |

| E                                       | 6.00 BSC |     |      |  |

| E1                                      | 3.90 BSC |     |      |  |

| е                                       | 1.27 BSC |     |      |  |

| L                                       | 0.4      | -   | 1.27 |  |

| L1                                      | 1.04 REF |     |      |  |

| L2                                      | 0.25 BSC |     |      |  |

| Ø                                       | 00 - 80  |     |      |  |

| ø1                                      | 50       | -   | 15º  |  |

|             | ORDERING INFORMATION              |               |

|-------------|-----------------------------------|---------------|

| Model       | Temperature Range<br>0°C to +70°C | Package Types |

| SP690ACN    |                                   | 8-Pin NSOIC   |

|             | 0°C to +70°C                      |               |

| SP690ACP    | 0°C to +70°C                      | 8-Pin PDIP    |

| SP690AEN    | 40°C to +85°C                     | 8-Pin NSOIC   |

| SP690AEN/TR | 40°C to +85°C                     | 8-Pin NSOIC   |

| SP690AEP    | 40°C to +85°C                     | 8-Pin PDIP    |

|             |                                   |               |

| SP692ACN    | 0°C to +70°C                      | 8-Pin NSOIC   |

|             | 0°C to +70°C                      |               |

|             | 0°C to +70°C                      |               |

|             | -40°C to +85°C                    |               |

|             | -40°C to +85°C                    |               |

|             | -40°C to +85°C                    |               |

| 01 002/121  |                                   |               |

| SP802LCN    | 0°C to +70°C                      | 8-Pin NSOIC   |

|             | 0°C to +70°C                      |               |

| SP802LCP    | 0°C to +70°C                      | 8-Pin PDIP    |

| SP802LEN    | 40°C to +85°C                     | 8-Pin NSOIC   |

|             | 40°C to +85°C                     |               |

| SP802LEP    | 40°C to +85°C                     | 8-Pin PDIP    |

|             |                                   | _             |

| SP802MCN    | 0°C to +70°C                      | 8-Pin NSOIC   |

|             | 0°C to +70°C                      |               |

| SP802MCP    | 0°C to +70°C                      | 8-Pin PDIP    |

| SP802MEN    | 40°C to +85°C                     | 8-Pin NSOIC   |

|             | 40°C to +85°C                     |               |

| SP802MEP    | 40°C to +85°C                     | 8-Pin PDIP    |

|             |                                   |               |

|             | 0°C to +70°C                      |               |

|             | 0°C to +70°C                      |               |

|             | 0°C to +70°C                      |               |

|             | 40°C to +85°C                     |               |

|             | 40°C to +85°C                     |               |

| SP805LEP    | 40°C to +85°C                     | 8-Pin PDIP    |

| 00000000    |                                   |               |

|             | 0°C to +70°C                      |               |

|             | 0°C to +70°C                      |               |

|             | 0°C to +70°C                      |               |

|             | 40°C to +85°C                     |               |

|             | 40°C to +85°C                     |               |

| SP805MEP    | 40°C to +85°C                     | 8-Pin PDIP    |

Available in lead free packaging. To order add "-L" suffix to part number.

Example: SP802LCN/TR = standard; SP802LCN-L/TR = lead free

/TR = Tape and Reel

Pack quantity 2,500 for NSOIC.

**Sipex Corporation**

Headquarters and Sales Office 233 South Hillview Drive Milpitas, CA 95035 TEL: (408) 934-7500 FAX: (408) 935-7600

Sipex Corporation reserves the right to make changes to any products described herein. Sipex does not assume any liability arising out of the application or use of any product or circuit described hereing; neither does it convey any license under its patent rights nor the rights of others.