Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### SPNZ801113

# Integrated 4-Port 10/100 Managed Switch with Two MACs MII or RMII Interfaces

**Rev 1.0**

### **General Description**

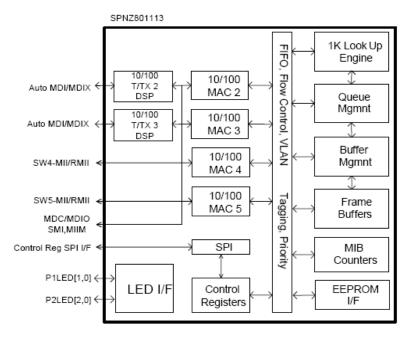

The SPNZ801113 is a highly-integrated, Layer 2 managed 4-port switch with optimized design, plentiful features and smallest package size. It is designed for cost-sensitive 10/100Mbps 4-port switch systems with on-chip termination. lowest-power consumption, and small package to save system cost. It has 1.4Gbps highperformance memory bandwidth, shared memory-based switch fabric with full non-blocking configuration. It also provides an extensive feature set such as the power management, programmable rate limiting and priority ratio. tag/port-based VLAN, packet filtering, quality of service (QoS), four queue prioritization, management interface, MIB counters. Port 3 and Port 4 support either MII or RMII interfaces with SW3-MII/RMII and SW4-MII/RMII (see Functional Diagram) for SPNZ801113 uplink data interface. An industrial temperature-grade version of the SPNY80111 is also available (see "Ordering Information" section). The SPNZ801113 provides multiple CPU control/data interfaces to effectively address both current and emerging fast Ethernet applications.

The SPNZ801113 consists of 10/100 fast Ethernet PHYs with patented and enhanced mixed-signal technology, media access control (MAC) units, a high-speed non-blocking switch fabric, a dedicated address lookup engine, and an on-chip frame buffer memory.

The SPNZ801113 contains four MACs and two PHYs. The two PHYs support the 10/100Base-T/TX.

All registers of MACs and PHYs units can be managed by the control interface of SPI or the SMI. MIIM registers of the PHYs can be accessed through the MDC/MDIO interface. EEPROM can set all control registers by I<sup>2</sup>C controller interface for the unmanaged mode.

Datasheets and support documentation can be found on Micrel's web site at: <a href="https://www.micrel.com">www.micrel.com</a>.

### **Functional Diagram**

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

June 2012 M9999-061812-1.0

#### **Features**

#### **Advanced Switch Features**

- IEEE 802.1q VLAN support for up to 128 VLAN groups (full-range 4096 of VLAN IDs).

- Static MAC table supports up to 32 entries.

- VLAN ID tag/untag options, per port basis.

- IEEE 802.1p/q tag insertion or removal on a per port basis based on ingress port (egress).

- Programmable rate limiting at the ingress and egress on a per port basis.

- Jitter-free per packet based rate limiting support.

- Broadcast storm protection with percentage control (global and per port basis).

- IEEE 802.1d rapid spanning tree protocol RSTP support.

- Tail tag mode (1 byte added before FCS) support at Port 4 to inform the processor which ingress port receives the packet.

- 1.4Gbps high-performance memory bandwidth and shared memory based switch fabric with fully nonblocking configuration.

- Dual MII/RMII with MAC 3 SW3-MII/RMII and MAC 4 SW4-MII/RMII interfaces.

- Enable/Disable option for huge frame size up to 2000 Bytes per frame.

- IGMP v1/v2 snooping (Ipv4) support for multicast packet filtering.

- IPv4/IPv6 QoS support.

- Support unknown unicast/multicast address and unknown VID packet filtering.

- Self-address filtering.

#### **Comprehensive Configuration Register Access**

- Serial management interface (MDC/MDIO) to all PHYs registers and SMI interface (MDC/MDIO) to all registers.

- High-speed SPI (up to 25MHz) and I<sup>2</sup>C master Interface to all internal registers.

- I/0 pins strapping and EEPROM to program selective registers in unmanaged switch mode.

- Control registers configurable on the fly (port-priority, 802.1p/d/q, AN...).

#### **QoS/CoS Packet Prioritization Support**

- Per port, 802.1p and DiffServ-based.

- 1/2/4-queue QoS prioritization selection.

- Programmable weighted fair queuing for ratio control.

- Re-mapping of 802.1p priority field per port basis.

#### Integrated 4-Port 10/100 Ethernet Switch

- New generation switch with five MACs and five PHYs that are fully compliant with the IEEE 802.3u standard.

- Non-blocking switch fabric assures fast packet delivery by utilizing an 1K MAC address lookup table and a store-and-forward architecture.

- On-chip 64Kbyte memory for frame buffering (not shared with 1K unicast address table).

- Full-duplex IEEE 802.3x flow control (PAUSE) with force mode option.

- Half-duplex back pressure flow control.

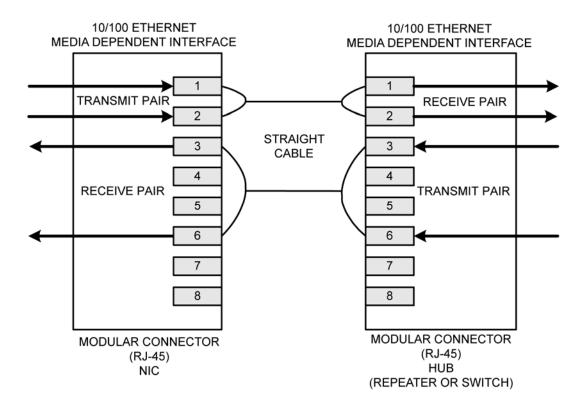

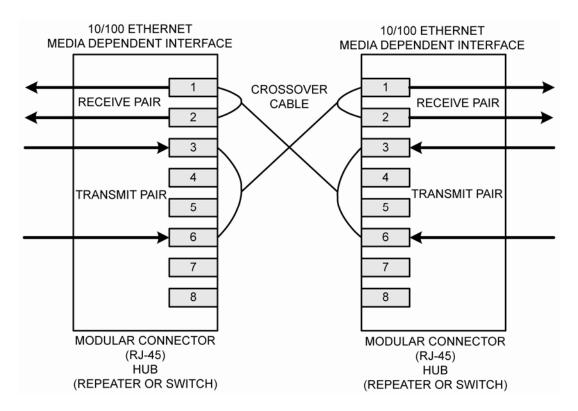

- HP Auto MDI/MDI-X and IEEE Auto crossover support.

- MII interface of MAC supports both MAC mode and PHY mode.

- Per port LED Indicators for link, activity, and 10/100 speed.

- Register port status support for link, activity, full/half duplex and 10/100 speed.

- On-chip terminations and internal biasing technology for cost down and lowest power consumption.

#### **Switch Monitoring Features**

- Port mirroring/monitoring/sniffing: ingress and/or egress traffic to any port or MII/RMII.

- MIB counters for fully-compliant statistics gathering 34 MIB counters per port.

- Loop-back support for MAC, PHY and remote diagnostic of failure.

- Interrupt for the link change on any ports.

#### Low-Power Dissipation:

- Full-chip hardware power-down.

- Full-chip software power-down and per port software power down.

- Energy-detect mode support <0.1W full-chip power consumption when all ports have no activity.

- Very-low full-chip power consumption (<0.3W), without extra power consumption on transformers.

- Dynamic clock tree shutdown feature.

- Voltages:

- Analog VDDAT 3.3V only.

- VDDIO support 3.3V, 2.5V and 1.8V.

- Low 1.2V core power.

- 0.13um CMOS technology.

- Commercial temperature range: 0°C to +70°C.

- Industrial Temperature Range: –40°C to +85°C.

- Available in 64-pin QFN, lead-free small package

## **Applications**

- VolP Phone

- Set-top/Game Box

- Automotive Ethernet

- Industrial Control

- IPTV POF

- SOHO Residential Gateway

- Broadband Gateway / Firewall / VPN

- Integrated DSL/Cable Modem

- Wireless LAN access point + gateway

- Standalone 10/100 switch

- Embedded System

## **Ordering Information**

| Part Number | Temperature Range | Package    | Lead Finish/Grade  |  |

|-------------|-------------------|------------|--------------------|--|

| SPNZ801113  | 0°C to 70°C       | 64-Pin QFN | Pb-Free/Commercial |  |

| SPNY801113  | −40°C to +85°C    | 64-Pin QFN | Pb-Free/Industrial |  |

## **Revision History**

| Revision | Date     | Description               |

|----------|----------|---------------------------|

| 1.0      | 06/18/12 | Initial document created. |

### **Contents**

| Features                                        | 2  |

|-------------------------------------------------|----|

| Pin Configuration                               | 9  |

| Pin Description                                 | 10 |

| Pin for Strap-In Options                        | 16 |

| Introduction                                    | 19 |

| Functional Overview: Physical Layer Transceiver | 19 |

| 100BASE-TX Transmit                             | 19 |

| 100BASE-TX Receive                              | 19 |

| PLL Clock Synthesizer                           | 19 |

| Scrambler/De-Scrambler (100BASE-TX only)        | 19 |

| 10BASE-T Transmit                               | 20 |

| 10BASE-T Receive                                | 20 |

| MDI/MDI-X Auto Crossover                        | 20 |

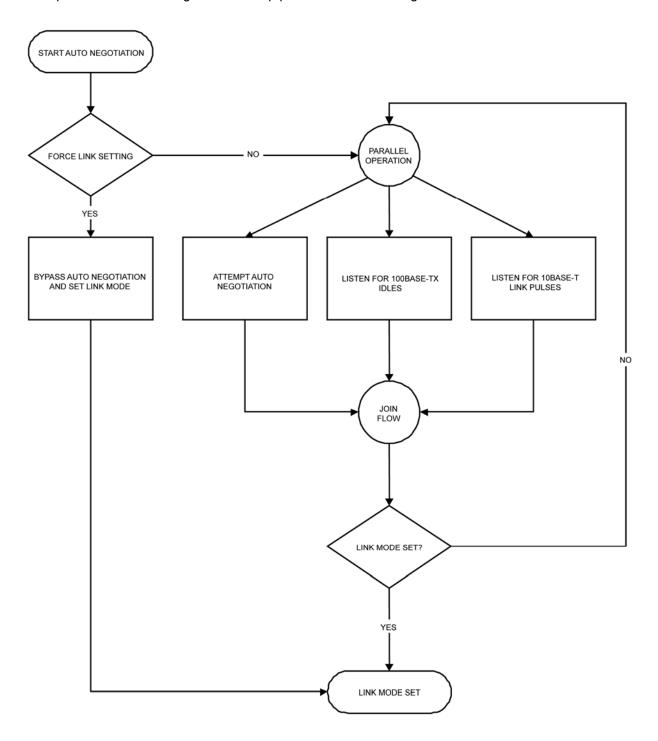

| Auto-Negotiation                                | 22 |

| On-Chip Termination Resistors                   | 24 |

| Functional Overview: Power Management           | 24 |

| Normal Operation Mode                           | 24 |

| Energy Detect Mode                              | 24 |

| Soft Power-Down Mode                            | 25 |

| Power Saving Mode                               | 25 |

| Port-Based Power-Down Mode                      | 25 |

| Functional Overview: Switch Core                | 25 |

| Address Look-Up                                 | 25 |

| Learning                                        | 25 |

| Migration                                       | 25 |

| Aging                                           | 25 |

| Forwarding                                      | 26 |

| Switching Engine                                | 26 |

| Media Access Controller (MAC) Operation         | 26 |

| Inter-Packet Gap (IPG)                          | 26 |

| Backoff Algorithm                               | 26 |

| Late Collision                                  | 26 |

| Illegal Frames                                  | 26 |

| Flow Control                                    | 26 |

| Half-Duplex Back Pressure                       | 29 |

| Broadcast Storm Protection                                                                        | 29 |

|---------------------------------------------------------------------------------------------------|----|

| MII Interface Operation                                                                           | 29 |

| Switch MAC3/MAC4 SW3/SW4-MII Interface                                                            | 29 |

| Switch MAC3/MAC4 SW3/SW4-RMII Interface Advanced Functionality                                    |    |

| Spanning Tree Support                                                                             | 34 |

| Rapid Spanning Tree Support                                                                       | 35 |

| Tail Tagging Mode                                                                                 | 36 |

| IGMP Support                                                                                      | 37 |

| Port Mirroring Support                                                                            | 37 |

| VLAN Support                                                                                      | 37 |

| Rate Limiting Support                                                                             | 38 |

| Ingress Rate Limit                                                                                | 38 |

| Egress Rate Limit                                                                                 | 39 |

| Transmit Queue Ratio Programming                                                                  | 39 |

| Filtering for Self-Address, Unknown Unicast/Multicast Address and Unknown VID Packet/IP Multicast | 39 |

| Configuration Interface                                                                           | 39 |

| SPI Slave Serial Bus Configuration                                                                | 40 |

| MII Management Interface (MIIM)                                                                   | 43 |

| Serial Management Interface (SMI)                                                                 | 43 |

| Register Description                                                                              | 45 |

| Global Registers                                                                                  | 46 |

| Port Registers                                                                                    | 56 |

| Advanced Control Registers                                                                        | 65 |

| Data Rate Selection Table in 100BT                                                                | 80 |

| Data Rate Selection Table in 10BT                                                                 |    |

| Static MAC Address Table                                                                          |    |

| VLAN Table                                                                                        |    |

| Dynamic MAC Address Table                                                                         |    |

| MIB (Management Information Base) Counters                                                        | 91 |

| For Port 1                                                                                        | 91 |

| All Ports Dropped Packet MIB Counters                                                             | 92 |

| Format of "All Dropped Packet" MMIB Counter                                                       | 92 |

| MIIM Registers                                                                                    |    |

| Absolute Maximum Ratings                                                                          |    |

| Operating Ratings                                                                                 |    |

| Electrical Characteristics                                                                        | 98 |

| Timing Diagrams                    | 100 |

|------------------------------------|-----|

| EEPROM Timing                      | 100 |

| MII Timing                         | 101 |

| RMII Timing                        | 103 |

| SPI Timing                         |     |

| Auto-Negotiation Timing            | 106 |

| MDC/MDIO Timing                    | 107 |

| Reset Timing                       | 108 |

| Selection of Isolation Transformer | 110 |

| Selection of Transformer Venders   | 110 |

| Selection of Reference Crystal     |     |

| Package Information                | 111 |

## **List of Figures**

| Figure 1.  | Typical Straight Cable Connection                       | 21  |

|------------|---------------------------------------------------------|-----|

| Figure 2.  | Typical Crossover Cable Connection                      |     |

| Figure 3.  | Auto-Negotiation                                        |     |

| Figure 4.  | Destination Address Lookup Flow Chart – Stage 1         | 27  |

| Figure 5.  | Destination Address Resolution Flow Chart – Stage 2     | 28  |

| Figure 6.  | 802.1p Priority Field Format                            | 34  |

| Figure 7.  | Tail-Tag Frame Format                                   | 36  |

| Figure 8.  | SPNZ801113 EEPROM Configuration Timing Diagram          | 40  |

| Figure 9.  | SPI Write Data Cycle                                    |     |

| Figure 10. | SPI Read Data Cycle                                     | 41  |

| Figure 11. | SPI Multiple Write                                      | 42  |

| Figure 12. | SPI Multiple Read                                       | 42  |

| Figure 13. | EEPROM Interface Input Receive Timing Diagram           | 100 |

| Figure 14. | EEPROM Interface Output Transmit Timing Diagram         | 100 |

| Figure 15. | MAC Mode MII Timing – Data Received from MII            | 101 |

| Figure 16. | MAC Mode MII Timing – Data Transmitted from MII         | 101 |

| Figure 17. | PHY Mode MII Timing – Data Received from MII            | 102 |

| Figure 18. | PHY Mode MII Timing – Data Transmitted from MII         | 102 |

| Figure 19. | RMII Timing – Data Received from RMII                   | 103 |

| Figure 20. | RMII Timing – Data Transmitted to RMII                  | 103 |

| Figure 21. | SPI Input Timing                                        | 104 |

| Figure 22. | SPI Output Timing                                       | 105 |

| Figure 23. | Auto-Negotiation Timing                                 | 106 |

| Figure 24. | MDC/MDIO Timing                                         | 107 |

| Figure 25. | Reset Timing                                            | 108 |

|            | Recommended Reset Circuit                               |     |

| Figure 27. | Recommended Circuit for Interfacing with CPU/FPGA Reset | 109 |

7

## **List of Tables**

| Table 1.  | MDI/MDI-X Pin Definitions                      |     |

|-----------|------------------------------------------------|-----|

| Table 2.  | Internal Function Block Status                 |     |

| Table 3.  | Switch MAC 3 SW3-MII and MAC 4 SW4-MII Signals | 30  |

| Table 4.  | MAC3 SW3-RMII and MAC4 SW4-RMII Connection     |     |

| Table 5.  | Tail Tag Rules                                 | 36  |

| Table 6.  | FID+DA Look-Up in the VLAN Mode                | 38  |

| Table 7.  | FID+SA Look-Up in the VLAN Mode                | 38  |

| Table 8.  | SPI Connections                                |     |

| Table 9.  | MII Management Interface Frame Format          | 43  |

| Table 10. | Serial Management Interface (SMI) Frame Format | 43  |

|           | 100BT Rate Selection for the Rate Limit        |     |

| Table 12. | 10BT Rate Selection for the Rate Limit         | 81  |

|           | Format of Static MAC Table for Reads           |     |

| Table 14. | Format of Static MAC Table for Writes          | 84  |

|           | VLAN Table                                     |     |

| Table 16. | VLAN ID and Indirect Registers                 | 88  |

| Table 17. |                                                |     |

| Table 18. | EEPROM Timing Parameters                       | 100 |

| Table 19. | MAC Mode MII Timing Parameters                 | 101 |

| Table 20. | PHY Mode MII Timing Parameters                 | 102 |

| Table 21. | RMII Timing Parameters                         | 103 |

| Table 22. | SPI Input Timing Parameters                    | 104 |

| Table 23. |                                                |     |

| Table 24. | Auto-Negotiation Timing Parameters             | 106 |

| Table 25. | MDC/MDIO Typical Timing Parameters             | 107 |

| Table 26. | Reset Timing Parameters                        | 108 |

| Table 27. |                                                |     |

| Table 28. | Qualified Magnetic Vendors                     | 110 |

| Table 29. | Typical Reference Crystal Characteristics      | 110 |

|           |                                                |     |

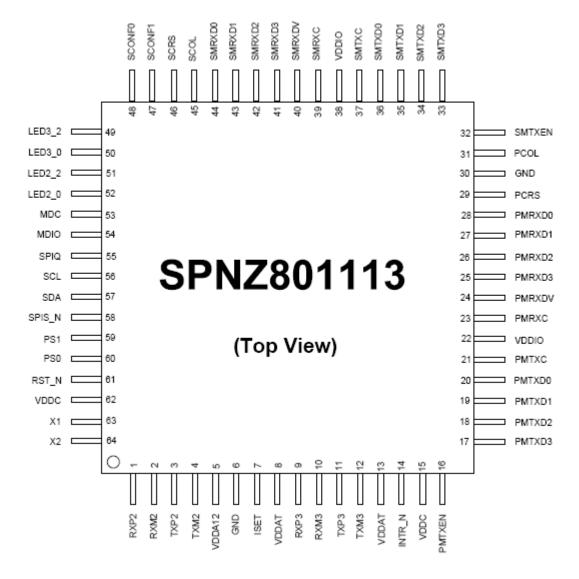

## **Pin Configuration**

64-Pin QFN

## **Pin Description**

| Pin Number | Pin Name         | Type <sup>(1)</sup> | Port | Pin Function <sup>(2)</sup>                                                                                                                                                       |  |

|------------|------------------|---------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1          | RXP1             | I                   | 1    | Physical receive signal + (differential).                                                                                                                                         |  |

| 2          | RXM1             | I                   | 1    | Physical receive signal – (differential).                                                                                                                                         |  |

| 3          | TXP1             | 0                   | 1    | Physical transmit signal + (differential).                                                                                                                                        |  |

| 4          | TXM1             | 0                   | 1    | Physical transmit signal – (differential).                                                                                                                                        |  |

| 5          | VDDA12           | Р                   |      | 1.2V analog power.                                                                                                                                                                |  |

| 6          | GND              | GND                 |      | Ground with all grounding of die bottom.                                                                                                                                          |  |

| 7          | ISET             |                     |      | Set physical transmit output current. Pull-down with a 12.4k $\Omega$ 1% resistor.                                                                                                |  |

| 8          | VDDAT            | Р                   |      | 3.3V analog V <sub>DD</sub> .                                                                                                                                                     |  |

| 9          | RXP2             | I                   | 2    | Physical receive signal + (differential).                                                                                                                                         |  |

| 10         | RXM2             | I                   | 2    | Physical receive signal - (differential).                                                                                                                                         |  |

| 11         | TXP2             | 0                   | 2    | Physical transmit signal + (differential).                                                                                                                                        |  |

| 12         | TXM2             | 0                   | 2    | Physical transmit signal – (differential).                                                                                                                                        |  |

| 13         | VDDAT            | Р                   |      | 3.3V analog V <sub>DD</sub> .                                                                                                                                                     |  |

| 14         | INTR_N           | OPU                 |      | Interrupt. This pin is Open-Drain output pin.                                                                                                                                     |  |

| 15         | VDDC             | Р                   |      | 1.2V digital core V <sub>DD</sub> .                                                                                                                                               |  |

| 16         | SM3TXEN          | IPD                 | 3    | MAC3 Switch MII/RMII transmit enable.                                                                                                                                             |  |

| 17         | SM3TXD3          | IPD                 | 3    | MAC3 Switch MII transmit bit 3.                                                                                                                                                   |  |

| 18         | SM3TXD2          | IPD                 | 3    | MAC3 Switch MII transmit bit 2.                                                                                                                                                   |  |

| 19         | SM3TXD1          | IPD                 | 3    | MAC3 Switch MII/RMII transmit bit 1.                                                                                                                                              |  |

| 20         | SM3TXD0          | IPD                 | 3    | MAC3 Switch MII/RMII transmit bit 0.                                                                                                                                              |  |

| 21         | SM3TXC/SM3REFCLK | I/O                 | 3    | MAC3 Switch MII transmit clock: Input: SW3-MII MAC mode. Output: SW3-MII PHY mode. Input: SW3-RMII reference clock.                                                               |  |

| 22         | VDDIO            | Р                   |      | 3.3V, 2.5V or 1.8V digital V <sub>DD</sub> for digital I/O circuitry.                                                                                                             |  |

| 23         | SM3RXC           | I/O                 | 3    | MAC3 Switch MII Receive clock: Input: SW3-MII MAC mode. Output: SW3-MII PHY mode. Output: SW3-RMII reference clock. Unused RMII clock can be pull-down or disable by register 87. |  |

| 24         | SM3RXDV/SM3CRSDV | IPD/O               | 3    | SM3RXDV: MAC3 Switch SW3-MII receive data valid.  SM3CRSDV: MAC3 Switch SW3-RMII Carrier Sense/Receive Data Valid.                                                                |  |

| 25         | SM3RXD3          | IPD/O               | 3    | MAC3 Switch MII receive bit 3. Strap option: PD (default) = enable flow control; PU = disable flow control.                                                                       |  |

| Pin Number | Pin Name         | Type <sup>(1)</sup> | Port                                   | Pin Function <sup>(2)</sup>                                                                                                                                                                                                                           |

|------------|------------------|---------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                  |                     |                                        | MAC3 Switch MII receive bit 2 and Strap option:                                                                                                                                                                                                       |

| 26         | SM3RXD2          | IPD/O               | 3                                      | PD (default) = disable back pressure;                                                                                                                                                                                                                 |

|            |                  |                     |                                        | PU = enable back pressure.                                                                                                                                                                                                                            |

|            |                  |                     |                                        | MAC3 Switch MII/RMII receive bit 1.                                                                                                                                                                                                                   |

| 27         | SM3RXD1          | IPD/O               | 3                                      | Strap option:                                                                                                                                                                                                                                         |

| 21         | OWOTOOD          | 11 15/0             |                                        | PD (default) = drop excessive collision packets;                                                                                                                                                                                                      |

|            |                  |                     |                                        | PU = does not drop excessive collision packets.                                                                                                                                                                                                       |

|            |                  |                     |                                        | MAC3 Switch MII/RMII receive bit 0.                                                                                                                                                                                                                   |

|            |                  |                     | _                                      | Strap option:                                                                                                                                                                                                                                         |

| 28         | SM3RXD0          | IPD/O               | 3                                      | PD (default) = disable aggressive back-off algorithm in half-duplex mode;                                                                                                                                                                             |

|            |                  |                     |                                        | PU = enable for performance enhancement.                                                                                                                                                                                                              |

| 29         | SM3CRS           | IPD/O               | 3                                      | MAC3 Switch MII carrier sense.                                                                                                                                                                                                                        |

| 30         | GND              | GND                 |                                        | Ground with all grounding of die bottom.                                                                                                                                                                                                              |

| 31         | SM3COL           | IPD/O               | 3                                      | MAC3 Switch MII collision detect.                                                                                                                                                                                                                     |

| 32         | SM4TXEN          | IPD                 | 4                                      | MAC4 Switch MII/RMII transmit enable.                                                                                                                                                                                                                 |

| 33         | SM4TXD3          | IPD                 | 4                                      | MAC4 Switch MII transmit bit 3.                                                                                                                                                                                                                       |

| 34         | SM4TXD2          | IPD                 | 4                                      | MAC4 Switch MII transmit bit 2.                                                                                                                                                                                                                       |

| 35         | SM4TXD1          | IPD                 | 4 MAC4 Switch MII/RMII transmit bit 1. |                                                                                                                                                                                                                                                       |

| 36         | SM4TXD0          | IPD                 | 4                                      | MAC4 Switch MII/RMII transmit bit 0.                                                                                                                                                                                                                  |

|            |                  |                     |                                        | MAC4 Switch MII transmit clock:                                                                                                                                                                                                                       |

|            |                  |                     |                                        | Input: SW4-MII MAC mode clock.                                                                                                                                                                                                                        |

| 37         | SM4TXC/SM4REFCLK | I/O                 | 4                                      | Input: SW4-RMII reference clock, please also see the strap-in pin P1LED1 for the clock mode and normal mode.                                                                                                                                          |

|            |                  |                     |                                        | Output: SW4-MII PHY modes.                                                                                                                                                                                                                            |

| 38         | VDDIO            | Р                   |                                        | 3.3V, 2.5V or 1.8V digital V <sub>DD</sub> for digital I/O circuitry.                                                                                                                                                                                 |

|            |                  |                     |                                        | MAC4 Switch MII Receive clock:                                                                                                                                                                                                                        |

|            |                  |                     |                                        | Input: SW4-MII MAC mode.                                                                                                                                                                                                                              |

|            |                  |                     |                                        | Output: SW4-MII PHY mode.                                                                                                                                                                                                                             |

| 39         | SM4RXC           | I/O                 | 4                                      | Output: SW4-RMII 50MHz reference clock (the device is default clock mode, the clock source comes from X1/X2 pins 25MHz crystal).                                                                                                                      |

|            |                  |                     |                                        | When set the device as normal mode (the chip's clock source comes from SM4TXC), the SM4RXC reference clock output should be disabled by the register 87. Please also see the strap-in pin P1LED1 for the selection of the clock mode and normal mode. |

| Pin Number | Pin Name            | Type <sup>(1)</sup> | Port | Pin Function <sup>(2)</sup>                             |                                                                 |                                 |  |

|------------|---------------------|---------------------|------|---------------------------------------------------------|-----------------------------------------------------------------|---------------------------------|--|

|            |                     |                     |      | SM4RXDV: MAG                                            | C4 Switch SW4-N                                                 | /III receive data valid.        |  |

| 40         | 40 SM4RXDV/SM4CRSDV |                     | 4    | SM4CRSDV: Ma<br>Valid                                   | SM4CRSDV: MAC4 Switch SW4-RMII Carrier Sense/Receive Data Valid |                                 |  |

|            |                     |                     |      | MAC4 Switch M                                           | II receive bit 3.                                               |                                 |  |

| 41         | SM4RXD3             | IPD/O               | 4    | Strap option:                                           |                                                                 |                                 |  |

| 41         | SIVIANADS           | IFD/O               | 4    | PD (default) = D                                        | isable Switch MII                                               | /RMII full-duplex flow control; |  |

|            |                     |                     |      | PU = Enable Sw                                          | itch MII/RMII full-                                             | -duplex flow control.           |  |

|            |                     |                     |      | MAC4 Switch M                                           | II receive bit 2.                                               |                                 |  |

| 42         | SM4RXD2             | IPD/O               | 4    | Strap option:                                           |                                                                 |                                 |  |

| 72         | SIVI41XD2           | 11 15/0             | _    | PD (default) = S                                        | witch MII/RMII in                                               | full-duplex mode;               |  |

|            |                     |                     |      | PU = Switch MII                                         | /RMII in half-dupl                                              | lex mode.                       |  |

|            | SM4RXD1             |                     |      | MAC4 Switch M                                           | II/RMII receive bi                                              | t 1.                            |  |

| 43         |                     | IPD/O               | 4    | Strap option:                                           |                                                                 |                                 |  |

| 45         |                     | 11 15/0             | _    | PD (default) =MAC4 Switch SW4-MII/RMII in 100Mbps mode; |                                                                 |                                 |  |

|            |                     |                     |      | PU = MAC4 Switch SW-5MII/RMII in 10Mbps mode.           |                                                                 |                                 |  |

|            |                     |                     |      | MAC4 Switch M                                           | II/RMII receive bi                                              | t 0.                            |  |

|            |                     |                     |      | Strap option: LE<br>PD (default) = m                    |                                                                 |                                 |  |

|            |                     |                     |      | PU = Mode 1.                                            |                                                                 |                                 |  |

| 44         | SM4RXD0             | IPD/O               | 4    | See "Register 1                                         | 1."                                                             |                                 |  |

|            |                     |                     |      |                                                         | Mode 0                                                          | Mode 1                          |  |

|            |                     |                     |      | PxLED1                                                  | Lnk/Act                                                         | 100Lnk/Act                      |  |

|            |                     |                     |      | PxLED0                                                  | Speed                                                           | Full duplex                     |  |

|            |                     |                     |      | MAC4 Switch M                                           | Il collision detect:                                            | :                               |  |

| 45         | SM4COL              | IPD/O               | 4    | Input: SW4-MII I                                        | MAC modes.                                                      |                                 |  |

|            |                     |                     |      | Output: SW4-MI                                          | I PHY modes.                                                    |                                 |  |

|            |                     | IPD/O               | 4    | MAC4 Switch M                                           | II modes carrier s                                              | sense:                          |  |

| 46         | SM4CRS              |                     |      | Input: SW4-MII I                                        | MAC modes.                                                      |                                 |  |

|            |                     |                     |      | Output: SW4-MI                                          | I PHY modes.                                                    |                                 |  |

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port  | Pin Function <sup>(2)</sup>                                                                                                                                                                                                                                                                                 | Pin Function <sup>(2)</sup>                                 |                                                                  |  |

|------------|----------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------|--|

|            |          |                     |       | MAC4 Switch SW4-MII enabled with PHY mode or MAC mode, have to configure SCONF1 Pin 47 with SCONF0 Pin 48 together.                                                                                                                                                                                         |                                                             |                                                                  |  |

|            |          |                     |       | See pins configu                                                                                                                                                                                                                                                                                            | uration table below:                                        |                                                                  |  |

|            |          |                     |       | Pin# (47,48)                                                                                                                                                                                                                                                                                                | Port 4 Switch MAC4                                          |                                                                  |  |

| 47         | SCONF1   | IPD                 |       | FIII# (47,40)                                                                                                                                                                                                                                                                                               | SW4- MII                                                    |                                                                  |  |

|            |          |                     |       | 00 (Default)                                                                                                                                                                                                                                                                                                | SW4-MII PHY mode                                            |                                                                  |  |

|            |          |                     |       | 01                                                                                                                                                                                                                                                                                                          | Disabled                                                    |                                                                  |  |

|            |          |                     |       | 10                                                                                                                                                                                                                                                                                                          | Disabled                                                    |                                                                  |  |

|            |          |                     |       | 11                                                                                                                                                                                                                                                                                                          | SW4-MII MAC mode                                            |                                                                  |  |

| 48         | SCONF0   | IPD                 |       | Port 4 Switch SW4-MII enabled with PHY mode or MAC mode, have to config SCONF0 pin 48 with SCONF1 Pin 47 together.                                                                                                                                                                                          |                                                             |                                                                  |  |

|            |          |                     |       | See Pin 47 desc                                                                                                                                                                                                                                                                                             | cription.                                                   |                                                                  |  |

| 49         | P2LED1   | IPU/O               | 2     | LED indicator fo                                                                                                                                                                                                                                                                                            | r Port 2.                                                   |                                                                  |  |

| 49         | FZLEDI   | 11-0/0              | 2     | This pin has to b                                                                                                                                                                                                                                                                                           | be pulled down by 1K resistor in the design for SPNZ801113. |                                                                  |  |

|            |          |                     |       | LED indicator fo                                                                                                                                                                                                                                                                                            | r Port 2.                                                   |                                                                  |  |

| 50         | P2LED0   | IPU/O               | 2     | Strap option: Switch MAC3 used only.                                                                                                                                                                                                                                                                        |                                                             |                                                                  |  |

|            | 1 22200  |                     | 150/0 | 11-0/0                                                                                                                                                                                                                                                                                                      |                                                             | PU (default) = Select MII interface for the Switch MAC3 SW3-MII. |  |

|            |          |                     |       | PD = Select RMII interface for the Switch MAC3 SW3-RMII.                                                                                                                                                                                                                                                    |                                                             |                                                                  |  |

|            |          |                     |       | LED indicator fo                                                                                                                                                                                                                                                                                            | r Port 1.                                                   |                                                                  |  |

|            |          |                     |       | Strap option: Switch RMII used only.                                                                                                                                                                                                                                                                        |                                                             |                                                                  |  |

|            |          |                     | 1     | PU (default) = Select the device as clock mode, when use RMII interface, all clock source come from pin x1/x2 crystal 25MHz.                                                                                                                                                                                |                                                             |                                                                  |  |

| 51         | P1LED1   | IPU/O               |       | PD = Select the device as normal mode when use RMII interface. All clock source comes from SW4-RMII SM4TXC pin with an external input 50MHz clock. In the normal mode, the 25MHz crystal clock from pin X1/X2 doesn't take affect and should disable SW4-RMII SW4RXC 50MHz clock output by the register 87. |                                                             |                                                                  |  |

|            |          |                     |       | The normal mode is used when SW4-RMII receive an external 50N reference clock from pin SM4TXC.                                                                                                                                                                                                              |                                                             |                                                                  |  |

| Pin Number | Pin Name   | Type <sup>(1)</sup> | Port  | Pin Function <sup>(2)</sup>                                      |                                                                                                                          |  |  |

|------------|------------|---------------------|-------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|

|            |            |                     |       | LED indicator for Port 1.                                        |                                                                                                                          |  |  |

| 52 P1LED0  | P1LED0     | IPU/O               | 1     | Strap option: for Switch MAC4 only.                              |                                                                                                                          |  |  |

| 32         | FILEDO     | IF U/O              | '     | PU (default) = Select MII interface for the Switch MAC4 SW4-MII. |                                                                                                                          |  |  |

|            |            |                     |       | PD = Select RMII interfa                                         | ce for the Switch MAC4 SW4-RMII.                                                                                         |  |  |

| 53         | MDC        | IPU                 | All   | MII management interfac                                          | ce clock. Or SMI interface clock                                                                                         |  |  |

| 54         | MDIO       | IPU/O               | All   |                                                                  | O. Or SMI interface data I/O wn to define pin state when not driven.                                                     |  |  |

|            |            |                     |       | Note: Need an external p                                         | pull-up when driven.                                                                                                     |  |  |

| 55         | SPIQ       | IPU/O               | All   | SPI serial data output in                                        | SPI slave mode.                                                                                                          |  |  |

|            | OFFICE     | 11 0/0              | 7 (11 | Note: Need an external p                                         | pull-up when driven.                                                                                                     |  |  |

|            |            |                     |       | (1) Input clock up to 25M                                        |                                                                                                                          |  |  |

| 56         | SPIC/SCL   | IPU/O               | All   | (2) output clock at 61KHz in I <sup>2</sup> C master mode.       |                                                                                                                          |  |  |

|            |            |                     |       | Note: Need an external p                                         | Note: Need an external pull-up when driven.                                                                              |  |  |

|            |            |                     |       | (1) Serial data input in SPI slave mode;                         |                                                                                                                          |  |  |

| 57         | SPID/SDA   | IPU/O               | All   | (2) serial data input/output in I <sup>2</sup> C master mode.    |                                                                                                                          |  |  |

|            |            |                     |       | Note: Need an external pull-up when driven.                      |                                                                                                                          |  |  |

|            |            |                     |       | Active low.                                                      |                                                                                                                          |  |  |

| 58         | SPIS_N     | IPU                 | All   |                                                                  | rt in SPI slave mode. When SPIS_N is high, the device is held in high impedance state, a high-to-low transition to sfer. |  |  |

|            |            |                     |       | (2) Not used in I <sup>2</sup> C maste                           | er mode.                                                                                                                 |  |  |

|            |            |                     |       | Serial bus configuration                                         | pin.                                                                                                                     |  |  |

|            |            |                     |       | For this case, if the EEP PS[1.0] = 00 default regi              | ROM is not present, the Switch will start itself with the ster values.                                                   |  |  |

|            |            |                     |       | Pin Configuration                                                | Serial Bus Configuration                                                                                                 |  |  |

| 59         | 59 PS1 IPD |                     |       | PS[1.0]=00                                                       | I <sup>2</sup> C Master Mode for EEPROM                                                                                  |  |  |

|            |            |                     |       | PS[1.0]=01                                                       | SMI Interface Mode                                                                                                       |  |  |

|            |            |                     |       | PS[1.0]=10                                                       | SPI Slave Mode for CPU Interface                                                                                         |  |  |

|            |            |                     |       | PS[1.0]=11                                                       | Factory Test Mode (BIST)                                                                                                 |  |  |

| 60         | PS0        | IPD                 |       | Serial bus configuration pin.                                    |                                                                                                                          |  |  |

SPNZ801113 Micrel, Inc.

## **Pin Description (Continued)**

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function <sup>(2)</sup>                                                                                |

|------------|----------|---------------------|------|------------------------------------------------------------------------------------------------------------|

| 61         | RST_N    | IPU                 |      | Reset the device. Active low.                                                                              |

| 62         | VDDC     | Р                   |      | 1.2V digital core V <sub>DD</sub> .                                                                        |

| 63         | X1       | 1                   |      | 25MHz crystal clock connection/or 3.3V Oscillator input. Crystal/Oscillator should be <= ±50ppm tolerance. |

| 64         | X2       | 0                   |      | 25MHz crystal clock connection.                                                                            |

#### Notes:

P = Power supply.

I = Input. O = Output.

I/O = Bidirectional.

GND = Ground.

IPU = Input w/internal pull-up.

IPD = Input w/internal pull-down.

IPD/O = Input w/internal pull-down during reset, output pin otherwise.

IPU/O = Input w/internal pull-up during reset, output pin otherwise.

NC = No connect.

PU = Strap pin pull-up. PD = Strap pull-down. 2.

OTRI = Output tristated.

## **Pin for Strap-In Options**

The SPNZ801113 can function as a managed switch or unmanaged switch. If no EEPROM or micro-controller exists, the SPNZ801113 will operate from its default setting. The strap-in option pins can be configures by external pull-up/down resistors and take the effect after power up reset or warm reset, the functions are described in the following table:

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port                          | Pin Function <sup>(2)</sup>                                      |                                                                           |             |  |

|------------|----------|---------------------|-------------------------------|------------------------------------------------------------------|---------------------------------------------------------------------------|-------------|--|

|            |          |                     | MAC3 Switch MII receive bit 3 |                                                                  |                                                                           |             |  |

| 25         | SM3RXD3  | IPD/O               |                               | Strap option:                                                    |                                                                           |             |  |

| 25         |          |                     |                               | PD (default) = enable flow control;                              |                                                                           |             |  |

|            |          |                     |                               | PU = disable flow control.                                       |                                                                           |             |  |

|            |          |                     |                               | MAC3 Switch MII receive bit 2 and Strap option:                  |                                                                           |             |  |

| 26         | SM3RXD2  | IPD/O               |                               | PD (default) = disable back pressure;                            |                                                                           |             |  |

|            |          |                     |                               | PU = enable back pressure.                                       |                                                                           |             |  |

|            |          |                     |                               | MAC3 Switch MII/RMII receive bit 1                               |                                                                           |             |  |

| 07         | OMODVD4  | IDD/O               |                               | Strap option:                                                    |                                                                           |             |  |

| 27         | SM3RXD1  | IPD/O               |                               | PD (default) = dr                                                | op excessive collisio                                                     | n packets;  |  |

|            |          |                     |                               | PU = does not d                                                  | rop excessive collision                                                   | on packets. |  |

|            |          |                     |                               | MAC3 Switch MII/RMII receive bit 0                               |                                                                           |             |  |

| 28         | OMODVDO  | IPD/O               |                               | Strap option:                                                    |                                                                           |             |  |

| 20         | SM3RXD0  |                     |                               | PD (default) = di                                                | PD (default) = disable aggressive back-off algorithm in half-duplex mode; |             |  |

|            |          |                     |                               | PU = enable for                                                  | performance enhanc                                                        | rement.     |  |

|            |          | IPD/O               |                               | MAC4 Switch MII receive bit 3.                                   |                                                                           |             |  |

| 41         | SM4RXD3  |                     |                               | Strap option:                                                    |                                                                           |             |  |

| 41         |          |                     |                               | PD (default) = Disable Switch MII/RMII full-duplex flow control; |                                                                           |             |  |

|            |          |                     |                               |                                                                  | PU = Enable Switch MII/RMII full-duplex flow control.                     |             |  |

|            |          |                     |                               | MAC4 Switch MII receive bit 2.                                   |                                                                           |             |  |

| 42         | SM4RXD2  | IPD/O               |                               | Strap option:                                                    |                                                                           |             |  |

| 42         |          |                     |                               | PD (default) = Switch MII/RMII in full-duplex mode;              |                                                                           |             |  |

|            |          |                     |                               | PU = Switch MII/RMII in half-duplex mode.                        |                                                                           |             |  |

|            |          |                     |                               | MAC4 Switch MII/RMII receive bit 1.                              |                                                                           |             |  |

| 43         | SM4RXD1  | IPD/O               |                               | Strap option:                                                    |                                                                           |             |  |

| 43         |          |                     |                               | PD (default) =MAC4 Switch SW4-MII/RMII in 100Mbps mode;          |                                                                           |             |  |

|            |          |                     |                               | PU = MAC4 Switch SW-5MII/RMII in 10Mbps mode.                    |                                                                           |             |  |

|            | SM4RXD0  | IPD/O               |                               | MAC4 Switch MII/RMII receive bit 0.                              |                                                                           |             |  |

| 44         |          |                     |                               | Strap option: LED mode                                           |                                                                           |             |  |

|            |          |                     |                               | PD (default) = mode 0;                                           |                                                                           |             |  |

|            |          |                     |                               | PU = mode 1.                                                     |                                                                           |             |  |

| 44         |          |                     |                               | See "Register 11."                                               |                                                                           |             |  |

|            |          |                     |                               |                                                                  | Mode 0                                                                    | Mode 1      |  |

|            |          |                     |                               | PxLED1                                                           | Lnk/Act                                                                   | 100Lnk/Act  |  |

|            |          |                     |                               | PxLED0                                                           | Speed                                                                     | Full duplex |  |

## **Pin for Strap-In Options (Continued)**

| Pin Number | Pin Name | Type <sup>(1)</sup> | Port | Pin Function <sup>(2)</sup>                                                                                                                                                                                                                                                                                 |                                                                                          |  |  |

|------------|----------|---------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

| 47         | SCONF1   | IPD                 |      | MAC4 Switch SW4-MII enabled with PHY mode or MAC mode, have to configure SCONF1 Pin 47 with SCONF0 Pin 48 together.                                                                                                                                                                                         |                                                                                          |  |  |

|            |          |                     |      | See pins configuration table below:                                                                                                                                                                                                                                                                         |                                                                                          |  |  |

|            |          |                     |      | Pin# (47,48)                                                                                                                                                                                                                                                                                                | Switch MAC4                                                                              |  |  |

|            |          |                     |      | PIN# (47,40)                                                                                                                                                                                                                                                                                                | SW4- MII/RMII                                                                            |  |  |

|            |          |                     |      | 00 (Default)                                                                                                                                                                                                                                                                                                | SW4-MII PHY mode                                                                         |  |  |

|            |          |                     |      | 01                                                                                                                                                                                                                                                                                                          | Disabled                                                                                 |  |  |

|            |          |                     |      | 10                                                                                                                                                                                                                                                                                                          | Disabled                                                                                 |  |  |

|            |          |                     |      | 11                                                                                                                                                                                                                                                                                                          | SW4-MII MAC mode                                                                         |  |  |

| 48         | SCONF0   | IPD                 |      |                                                                                                                                                                                                                                                                                                             | W4-MII enabled with PHY mode or MAC mode, have to configure with SCONF1 Pin 47 together. |  |  |

|            |          |                     |      | See pin 47 desc                                                                                                                                                                                                                                                                                             | ription.                                                                                 |  |  |