Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **DDR 14-Bit Registered Buffer**

# ICSSSTV16857C

#### **Recommended Applications:**

- DDR Memory Modules

- Provides complete DDR DIMM logic solution with ICS93V857 or ICS95V857

- SSTL 2 compatible data registers

#### **Product Features:**

- · Differential clock signal

- Meets SSTL\_2 signal data

- Supports SSTL\_2 class I & II specifications

- Low-voltage operation

- $-V_{DD} = 2.3V \text{ to } 2.7V$

- 48 pin TSSOP package

# Truth Table<sup>1</sup>

|        | Inputs           |                  |                  |                               |  |  |

|--------|------------------|------------------|------------------|-------------------------------|--|--|

| RESET# | CLK              | CLK#             | D                | Q                             |  |  |

| L      | X or<br>Floating | X or<br>Floating | X or<br>Floating | L                             |  |  |

| Н      | 1                | <b>\</b>         | Н                | Н                             |  |  |

| Н      | 1                | $\downarrow$     | L                | L                             |  |  |

| Н      | L or H           | L or H           | Х                | Q <sub>0</sub> <sup>(2)</sup> |  |  |

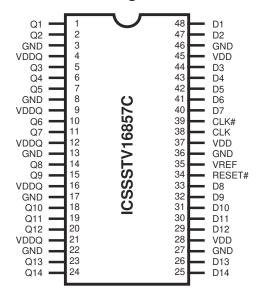

# **Pin Configuration**

#### 48-Pin TSSOP & TVSOP

6.10 mm. Body, 0.50 mm. pitch = TSSOP 4.40 mm. Body, 0.40 mm. pitch = TSSOP (TVSOP)

### Notes:

- 1. H = High Signal Level

- L = Low Signal Level

- ↑ = Transition LOW-to-HIGH

- ↓ = Transition HIGH -to LOW

- X = Irrelevant

- Output level before the indicated steady state input conditions were established.

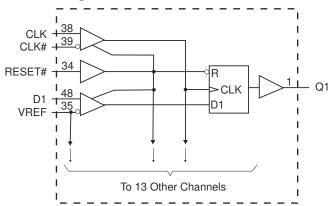

# **Block Diagram**

### **General Description**

The 14-bit ICSSSTV16857C is a universal bus driver designed for 2.3V to 2.7V  $V_{DD}$  operation and SSTL\_2 I/O levels, except for the LVCMOS RESET# input.

Data flow from D to Q is controlled by the differential clock (CLK/CLK#) and a control signal (RESET#). The positive edge of CLK is used to trigger the data flow and CLK# is used to maintain sufficient noise margins where as RESET#, an LVCMOS asynchronous signal, is intended for use at the time of power-up only. ICSSSTV16857C supports low-power standby operation. A logic level "Low" at RESET# assures that all internal registers and outputs (Q) are reset to the logic "Low" state, and all input receivers, data (D) and clock (CLK/CLK#) are switched off. Please note that RESET# must always be supported with LVCMOS levels at a valid logic state because VREF may not be stable during power-up.

To ensure that outputs are at a defined logic state before a stable clock has been supplied, RESET# must be held at a logic "Low" level during power up.

In the DDR DIMM application, RESET# is specified to be completely asynchronous with respect to CLK and CLK#. Therefore, no timing relationship can be guaranteed between the two signals. When entering a low-power standby state, the register will be cleared and the outputs will be driven to a logic "Low" level quickly relative to the time to disable the differential input receivers. This ensures there are no glitches on the output. However, when coming out of low-power standby state, the register will become active quickly relative to the time to enable the differential input receivers. When the data inputs are at a logic level "Low" and the clock is stable during the "Low"-to-"High" transition of RESET# until the input receivers are fully enabled, the design ensures that the outputs will remain at a logic "Low" level.

# **Pin Configuration**

| PIN NUMBER                                              | PIN NAME | TYPE   | DESCRIPTION             |

|---------------------------------------------------------|----------|--------|-------------------------|

| 24, 23, 20, 19, 18,<br>15, 14, 11, 10, 7,<br>6, 5, 2, 1 | Q (14:1) | OUTPUT | Data output             |

| 3, 8, 13, 22,<br>27, 36, 46                             | GND      | PWR    | Ground                  |

| 4, 9, 12, 16, 21                                        | VDDQ     | PWR    | Output supply voltage   |

| 25, 26, 29, 30, 31, 32, 33, 40, 41, 42, 43, 44, 47, 48  | D (14:1) | INPUT  | Data input              |

| 38                                                      | CLK      | INPUT  | Positive clock input    |

| 39                                                      | CLK#     | INPUT  | Negative clock input    |

| 28, 37, 45                                              | VDD      | PWR    | Core supply voltage     |

| 34                                                      | RESET#   | INPUT  | Reset (active low)      |

| 35                                                      | VREF     | INPUT  | Input reference voltage |

# **Absolute Maximum Ratings**

| Storage Temperature                                   | -65°C to +150°C          |

|-------------------------------------------------------|--------------------------|

| Supply Voltage                                        | -0.5 to 3.6V             |

| Input Voltage <sup>1</sup>                            | $-0.5$ to $V_{DD} + 0.5$ |

| Output Voltage <sup>1,2</sup>                         | -0.5 to $V_{DDQ}$ +0.5   |

| Input Clamp Current                                   |                          |

| Output Clamp Current                                  | ±50 mA                   |

| Continuous Output Current                             | ±50 mA                   |

| V <sub>DD</sub> , V <sub>DDQ</sub> or GND Current/Pin | ±100 mA                  |

| Package Thermal Impedance <sup>3</sup>                | 55°C/W                   |

#### Notes:

- The input and output negative voltage ratings may be excluded if the input and output clamp ratings are observed.

- 2. This current will flow only when the output is in the high state level V<sub>0</sub> > V<sub>DDQ</sub>.

- 3. The package thermal impedance is calculated in accordance with JESD 51.

Stresses above those listed under *Absolute Maximum Ratings* may cause permanent damage to the device. These ratings are stress specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product reliability.

**Recommended Operating Conditions**

| PARAMETER            | DESCRIPTION                                        |             | MIN                         | TYP       | MAX                     | UNITS |

|----------------------|----------------------------------------------------|-------------|-----------------------------|-----------|-------------------------|-------|

| $V_{DD}$             | Supply Voltage                                     |             | 2.3                         | 2.5       | 2.7                     |       |

| $V_{DDQ}$            | I/O Supply Voltage                                 |             | 2.3                         | 2.5       | 2.7                     |       |

| $V_{REF}$            | Reference Voltage                                  |             | 1.15                        | 1.25      | 1.35                    |       |

| $V_{TT}$             | Termination Voltage                                |             | V <sub>REF</sub> - 0.04     | $V_{REF}$ | $V_{REF} + 0.04$        |       |

| $V_{I}$              | Input Voltage                                      |             | 0                           |           | $V_{DDQ}$               |       |

| V <sub>IH (DC)</sub> | DC Input High Voltage                              |             | V <sub>REF</sub> + 0.15     |           |                         |       |

| V <sub>IH (AC)</sub> | AC Input High Voltage                              | Dota Inputa | V <sub>REF</sub> + 0.31     |           |                         |       |

| V <sub>IL (DC)</sub> | DC Input Low Voltage                               | Data Inputs |                             |           | V <sub>REF</sub> - 0.15 | V     |

| V <sub>IL (DC)</sub> | AC Input Low Voltage                               |             |                             |           | V <sub>REF</sub> - 0.31 |       |

| $V_{IH}$             | Input High Voltage Level                           | RESET#      | 1.7                         |           |                         |       |

| $V_{IL}$             | Input Low Voltage Level                            | INESET#     |                             |           | 0.7                     |       |

| $V_{ICR}$            | Common mode Input Range                            | CLK, CLK#   | 0.97                        |           | 1.53                    |       |

| $V_{ID}$             | Differential Input Voltage                         | OLN, OLN#   | 0.36                        |           |                         |       |

| V <sub>IX</sub>      | Cross Point Voltage of Differential Clock<br>Pair  |             | (V <sub>DDQ</sub> /2) - 0.2 |           | $(V_{DDQ}/2) + 0.2$     |       |

| I <sub>OH</sub>      | High-Level Output Current Low-Level Output Current |             |                             |           | -20                     | m A   |

| I <sub>OL</sub>      |                                                    |             |                             |           | 20                      | mA    |

| T <sub>A</sub>       | Operating Free-Air Temperatu                       | re          | 0                           |           | 70                      | °C    |

<sup>&</sup>lt;sup>1</sup>Guarenteed by design, not 100% tested in production.

# **Electrical Characteristics - DC**

$T_A = 0 - 70^{\circ}$  C;  $V_{DD} = 2.5$  +/-0.2V,  $V_{DDQ} = 2.5$  +/-0.2V; (unless otherwise stated)

| SYMBOL            | PARAMETERS                                                | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  | $V_{DDQ}$ | MIN                    | TYP  | MAX        | UNITS                 |    |

|-------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----------|------------------------|------|------------|-----------------------|----|

| V <sub>IK</sub>   |                                                           | I <sub>I</sub> = -18mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | 2.3V      |                        |      | -1.2       |                       |    |

| V <sub>OH</sub>   |                                                           | I <sub>OH</sub> = -100μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  | 2.3V-2.7V | V <sub>DDQ</sub> - 0.2 |      |            | V                     |    |

|                   |                                                           | I <sub>OH</sub> = -16mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  | 2.3V      | 1.95                   |      |            | V                     |    |

| V <sub>OL</sub>   |                                                           | $I_{OL} = 100 \mu A$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  | 2.3V-2.7V |                        |      | 0.2        |                       |    |

| V OL              |                                                           | $I_{OL} = 16mA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 2.3V      |                        |      | 0.35       |                       |    |

| I <sub>I</sub>    | All Inputs                                                | $V_I = V_{DD}$ or GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  | 2.7V      |                        |      | ±5         | μΑ                    |    |

|                   | Standby (Static)                                          | RESET# = GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |           |                        |      | 0.01       | μΑ                    |    |

| I <sub>DD</sub>   | Operating (Static)                                        | $V_{I} = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>RESET# = $V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |           |                        |      | 52         |                       | mA |

|                   | Dynamic operating (clock only)                            | $\label{eq:RESET} \begin{aligned} &\text{RESET\#} = \text{V}_{\text{DD}}, \\ &\text{V}_{\text{I}} = \text{V}_{\text{IH}(\text{AC})} \text{ or } \text{V}_{\text{IL}(\text{AC})}, \\ &\text{CLK and CLK\# switching} \\ &50\% \text{ duty cycle}. \end{aligned} \qquad \textbf{I}_{O} = 0$ $\label{eq:RESET\#} \begin{aligned} &\text{RESET\#} = \text{V}_{\text{DD}}, \\ &\text{V}_{\text{I}} = \text{V}_{\text{IH}(\text{AC})} \text{ or } \text{V}_{\text{IL}} \text{ (AC)}, \\ &\text{CLK and CLK\# switching} \\ &50\% \text{ duty cycle}. \text{ One data} \\ &\text{input switching at half} \\ &\text{clock frequency, 50\%} \\ &\text{duty cycle} \end{aligned}$ |  | 2.7V      |                        | 75   |            | μΑ/clock<br>MHz       |    |

| I <sub>DDD</sub>  | Dynamic Operating (per each data input)                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  | 2.7 V     |                        | 15   |            | μΑ/ clock<br>MHz/data |    |

| r <sub>OH</sub>   | Output High                                               | $I_{OH} = -20mA$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  | 2.3V-2.7V | 7                      | 13.5 | 20         | Ω                     |    |

| r <sub>OL</sub>   | Output Low                                                | I <sub>OL</sub> = 20mA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  | 2.3V-2.7V | 7                      | 13   | 20         | Ω                     |    |

| r <sub>O(D)</sub> | [r <sub>OH</sub> - r <sub>OL</sub> ] each<br>separate bit | I <sub>O</sub> = 20mA, T <sub>A</sub> = 25° C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  | 2.5V      |                        |      | 4          | Ω                     |    |

| C <sub>i</sub>    | Data Inputs CLK and CLK#                                  | $V_{I} = V_{REF} \pm 350 \text{mV}$<br>$V_{ICR} = 1.25 \text{V}, V_{I(PP)} = 360 \text{mV}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  | 2.5V      | 2.5<br>2.5             |      | 3.5<br>3.5 | рБ                    |    |

### Notes:

<sup>1 -</sup> Guaranteed by design, not 100% tested in production.

# Timing Requirements<sup>1</sup>

(over recommended operating free-air temperature range, unless otherwise noted)

| SYMBOL              | PARAMETERS                                     |                          | $V_{DDQ} = 2$ | 2.5±0.2V | UNITS |

|---------------------|------------------------------------------------|--------------------------|---------------|----------|-------|

| STINIBOL PARAMETERS |                                                |                          | MIN           | MAX      | UNITS |

| f <sub>clock</sub>  | Clock frequency                                |                          |               | 200      | MHz   |

| t <sub>PD</sub>     | Clock to output time                           |                          | 1.7           | 2.5      | ns    |

| t <sub>RST</sub>    | Reset to output time                           |                          |               | 3.5      | ns    |

| t <sub>SL</sub>     | Output slew rate                               |                          | 1             | 4        | V/ns  |

| t <sub>s</sub>      | Setup time, fast slew rate 284                 | Data before CLK↑, CLK#↓  | 0.4           |          | ns    |

| us .                | Setup time, slow slew rate 3 & 4               | Data before OLICE, OLICE | 0.5           |          | ns    |

|                     | Hold time, fast slew rate <sup>2 &amp; 4</sup> | Data after CLK↑, CLK#↓   | 0.4           |          | ns    |

| ' h                 | Hold time, slow slew rate 3 & 4                | Data aliei OLIVI, OLIV#  | 0.5           |          | ns    |

Notes:

- 1 Guaranteed by design, not 100% tested in production.

- 2 For data signal input slew rate  $\geq 1 V/ns$ .

- 3 For data signal input slew rate  $\geq 0.5 V/ns$  and < 1 V/ns.

- 4 CLK, CLK# signals input slew rates are ≥ 1V/ns.

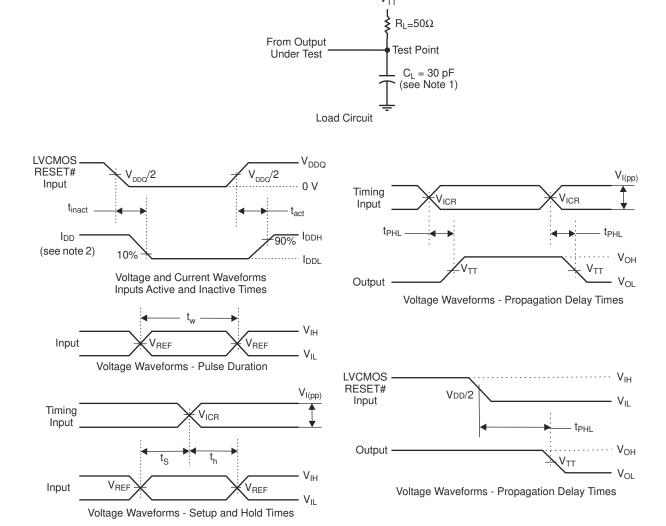

### **Switching Characteristics**

(over recommended operating free-air temperature range, unless otherwise noted) (see Figure 1)

| _(or or recommended specialising reso and comperiations rainge, and occurrence record) (or or right |           |          |                             |     | 19010 17 |       |

|-----------------------------------------------------------------------------------------------------|-----------|----------|-----------------------------|-----|----------|-------|

| SYMBOL                                                                                              | From      | То       | To $V_{DD} = 2.5V \pm 0.2V$ |     | 2V       | UNITS |

| STIVIBUL                                                                                            | (Input)   | (Output) | MIN                         | TYP | MAX      | UNITS |

| f <sub>max</sub>                                                                                    |           |          | 200                         |     |          | MHz   |

| $t_PD$                                                                                              | CLK, CLK# | Q        | 1.7                         | 2.1 | 2.5      | ns    |

| t <sub>phl</sub>                                                                                    | RESET#    | Q        |                             |     | 3.5      | ns    |

Figure 1 - Parameter Measurement Information (V<sub>DDO</sub> = 2.5V ±0.2V)

Notes: 1. CL includes probe and jig capacitance.

- 2.  $I_{DD}$  tested with clock and data inputs held at  $V_{DDQ}$  or GND, and  $I_{O} = 0$  mA.

- 3. All input pulses are supplied by generators having the following characteristics: PRR @10 MHz,  $Zo=50\Omega$ , input slew rate = 1 V/ns  $\pm 20\%$  (unless otherwise specified).

- 4. The outputs are measured one at a time with one transition per measurement.

- $5. V_{TT} = V_{REF} = V_{DDQ}/2$

- 6.  $V_{IH} = V_{REF} + 310 \text{mV}$  (AC voltage levels) for differential inputs.  $V_{IH} = V_{DDQ}$  for LVCMOS input.

- 7.  $V_{IL} = V_{REF}$  310mV (AC voltage levels) for differential inputs.  $V_{IL} = GND$  for LVCMOS input.

- 8. tplH and tpHL are the same as tpd

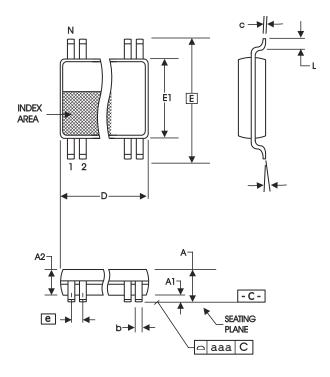

6.10 mm. Body, 0.50 mm. pitch TSSOP (240 mil) (0.020 mil)

|        | In Millin      | neters   | In Inches      |           |  |

|--------|----------------|----------|----------------|-----------|--|

| SYMBOL | COMMON DI      | MENSIONS | COMMON D       | IMENSIONS |  |

|        | MIN MAX        |          | MIN            | MAX       |  |

| Α      |                | 1.20     |                | .047      |  |

| A1     | 0.05           | 0.15     | .002           | .006      |  |

| A2     | 0.80           | 1.05     | .032           | .041      |  |

| b      | 0.17           | 0.27     | .007           | .011      |  |

| С      | 0.09           | 0.20     | .0035          | .008      |  |

| D      | SEE VAR        | IATIONS  | SEE VARIATIONS |           |  |

| E      | 8.10 B         | ASIC     | 0.319 BASIC    |           |  |

| E1     | 6.00           | 6.20     | .236           | .244      |  |

| е      | 0.50 B         | ASIC     | 0.020 BASIC    |           |  |

| L      | 0.45           | 0.75     | .018           | .030      |  |

| N      | SEE VARIATIONS |          | SEE VAR        | IATIONS   |  |

| α      | 0°             | 8°       | 0°             | 8°        |  |

| aaa    |                | 0.10     |                | .004      |  |

#### **VARIATIONS**

| N    | D mm. |       | D (inch) |      |

|------|-------|-------|----------|------|

| l IN | MIN   | MAX   | MIN      | MAX  |

| 48   | 12.40 | 12.60 | .488     | .496 |

Reference Doc.: JEDEC Publication 95, MO-153

10-0039

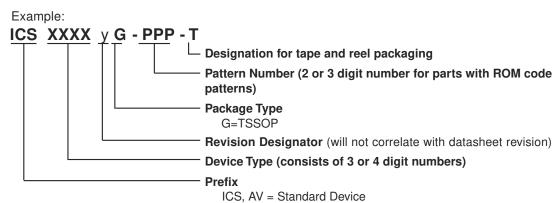

# **Ordering Information**

## ICSSSTV16857CG-T

|        | In Mil            | limeters | In Inc         | hes       |  |

|--------|-------------------|----------|----------------|-----------|--|

| SYMBOL | COMMON DIMENSIONS |          | COMMON D       | IMENSIONS |  |

|        | MIN               | MIN MAX  |                | MAX       |  |

| Α      |                   | 1.20     |                | .047      |  |

| A1     | 0.05              | 0.15     | .002           | .006      |  |

| A2     | 0.80              | 1.05     | .032           | .041      |  |

| b      | 0.13              | 0.23     | .005           | .009      |  |

| С      | 0.09              | 0.20     | .0035          | .008      |  |

| D      | SEE VA            | RIATIONS | SEE VARIATIONS |           |  |

| E      | 6.40              | BASIC    | 0.252 BASIC    |           |  |

| E1     | 4.30              | 4.50     | .169           | .177      |  |

| е      | 0.40              | BASIC    | 0.016 E        | BASIC     |  |

| L      | 0.45              | 0.75     | .018           | .030      |  |

| N      | SEE VARIATIONS    |          | SEE VAR        | IATIONS   |  |

| α      | 0°                | 8°       | 0°             | 8°        |  |

| aaa    |                   | 0.08     |                | .003      |  |

#### **VARIATIONS**

| N  | D mm. |      | D (inch) |      |

|----|-------|------|----------|------|

| IN | MIN   | MAX  | MIN      | MAX  |

| 48 | 9.60  | 9.80 | .378     | .386 |

Reference Doc.: JEDEC Publication 95, M O-153

10-0037

4.40 mm. Body, 0.40 mm. pitch TSSOP (173 mil) (16 mil)

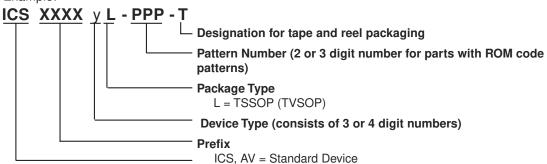

# **Ordering Information**

### ICSSSTV16857CL-T

# Innovate with IDT and accelerate your future networks. Contact:

# www.IDT.com

### For Sales

800-345-7015 408-284-8200 Fax: 408-284-2775

### For Tech Support

clockhelp@idt.com 408-284-8200

#### **Corporate Headquarters**

Integrated Device Technology, Inc. 6024 Silver Creek Valley Road San Jose, CA 95138 United States 800 345 7015 +408 284 8200 (outside U.S.)

### Asia Pacific and Japan

Integrated Device Technology Singapore (1997) Pte. Ltd. Reg. No. 199707558G 435 Orchard Road #20-03 Wisma Atria Singapore 238877 +65 6 887 5505

#### Europe

IDT Europe, Limited Prime House Barnett Wood Lane Leatherhead, Surrey United Kingdom KT22 7DE +44 1372 363 339