# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## ST10F269Zx

## 16-BIT MCU WITH MAC UNIT. 128K to 256K BYTE FLASH MEMORY AND 12K BYTE RAM

- HIGH PERFORMANCE 32 OR 40 MHZ CPU WITH DSP FUNCTION

- 16-bit CPU With 4-stage Pipeline

- 50ns (or 62.5ns) Instruction Cycle Time at 40MHz (or 32MHz) Max CPU Clock

- Multiply/accumulate Unit (Mac) 16 X 16-bit Multiplication, 40-bit Accumulator

- Repeat Unit

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Single-cycle Context Switching Support

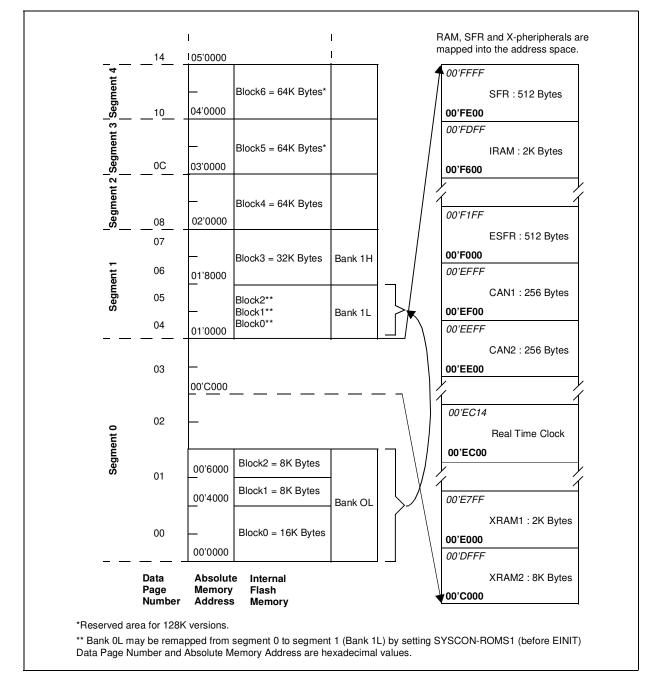

- MEMORY ORGANIZATION

- 128K or 256K Byte On-chip Flash Memory Single Voltage With Erase/program Controller

- Up to 1K Erasing/programming Cycles

- Up to 16 MByte Linear Address Space For Code And Data (5 MBytes With CAN)

- 2K Byte On-chip Internal RAM (IRAM)

- 10K Byte On-chip Extension RAM (XRAM)

- FAST AND FLEXIBLE BUS

- Programmable External Bus Characteristics for Different Address Ranges

- 8-bit or 16-bit External Data Bus

- Multiplexed or Demultiplexed External Address/data Buses

- Five Programmable Chip-select Signals

- Hold-acknowledge Bus Arbitration Support

- INTERRUPT

- 8-channel Peripheral Event Controller for Single Cycle Interrupt Driven Data Transfer

- 16-priority-level Interrupt System with 56 Sources, Sampling Rate Down to 25ns at 40MHz (31.25ns at 32MHz)

- TIMERS

- Two Multi-functional General Purpose Timer Units with 5 Timers

- TWO 16-CHANNEL CAPTURE / COMPARE UNITS

- A/D CONVERTER

- 16-channel 10-bit

- 4.85µs Conversion Time at 40MHz CPU Clock (6.06µs at 32MHz)

- **4-CHANNEL PWM UNIT**

- SERIAL CHANNELS

- Synchronous / Asynchronous Serial Channel

- High-speed Synchronous Channel

- REAL TIME CLOCK

- **UP TO 111 GENERAL PURPOSE I/O LINES**

- Individually Programmable as Input, Output or Special Function

- Programmable Threshold (Hysteresis)

- IDLE AND POWER DOWN MODES

- SINGLE VOLTAGE SUPPLY: 5V ±10% (EMBEDDED REGULATOR FOR 2.7 or 3.3 V CORE SUPPLY).

- TEMPERATURE RANGES: -40 +125°C / -40 to 85°C

- 144-PIN PQFP/TQFP PACKAGES

## TABLE OF CONTENTS

## ST10F269

| 1 -        | Introduction |                                                                                                            |    |  |  |  |  |  |  |  |  |  |

|------------|--------------|------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

| 2 -<br>3 - |              | ata                                                                                                        |    |  |  |  |  |  |  |  |  |  |

| -          |              | ctional Description                                                                                        |    |  |  |  |  |  |  |  |  |  |

| 4 -        |              | ry Organization1                                                                                           |    |  |  |  |  |  |  |  |  |  |

| 5 -        | Intern       | al Flash Memory                                                                                            | 17 |  |  |  |  |  |  |  |  |  |

|            | 5.1 -        | OVERVIEW                                                                                                   | 17 |  |  |  |  |  |  |  |  |  |

|            | 5.2 -        | OPERATIONAL OVERVIEW                                                                                       | 17 |  |  |  |  |  |  |  |  |  |

|            | 5.3 -        | ARCHITECTURAL DESCRIPTION                                                                                  | 19 |  |  |  |  |  |  |  |  |  |

|            |              | 5.3.1 - Read Mode                                                                                          | 19 |  |  |  |  |  |  |  |  |  |

|            |              | 5.3.2 - Command Mode                                                                                       |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.3.3 - Ready/Busy Signal                                                                                  |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.3.4 - Flash Status Register                                                                              |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.3.5 - Flash Protection Register                                                                          |    |  |  |  |  |  |  |  |  |  |

|            |              | <ul><li>5.3.6 - Instructions Description</li><li>5.3.7 - Reset Processing and Initial State</li></ul>      |    |  |  |  |  |  |  |  |  |  |

|            |              | 5                                                                                                          |    |  |  |  |  |  |  |  |  |  |

|            | 5.4 -        | FLASH MEMORY CONFIGURATION                                                                                 | 26 |  |  |  |  |  |  |  |  |  |

|            | 5.5 -        | APPLICATION EXAMPLES2                                                                                      |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.5.1 - Handling of Flash Addresses                                                                        |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.5.2 - Basic Flash Access Control                                                                         |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.5.3 - Programming Examples                                                                               | 28 |  |  |  |  |  |  |  |  |  |

|            | 5.6 -        | BOOTSTRAP LOADER                                                                                           |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.6.1 - Entering the Bootstrap Loader                                                                      |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.6.2 - Memory Configuration After Reset                                                                   |    |  |  |  |  |  |  |  |  |  |

|            |              | 5.6.3 - Loading the Startup Code                                                                           |    |  |  |  |  |  |  |  |  |  |

|            |              | <ul><li>5.6.4 - Exiting Bootstrap Loader Mode</li><li>5.6.5 - Choosing the Baud Rate for the BSL</li></ul> |    |  |  |  |  |  |  |  |  |  |

| 6 -        | Centr        | al Processing Unit (CPU)                                                                                   |    |  |  |  |  |  |  |  |  |  |

| U          | 6.1 -        | MULTIPLIER-ACCUMULATOR UNIT (MAC)                                                                          |    |  |  |  |  |  |  |  |  |  |

|            | 0.1          | 6.1.1 - Features                                                                                           |    |  |  |  |  |  |  |  |  |  |

|            |              | 6.1.1.1 - Enhanced Addressing Capabilities                                                                 |    |  |  |  |  |  |  |  |  |  |

|            |              | 6.1.1.2 - Multiply-Accumulate Unit                                                                         |    |  |  |  |  |  |  |  |  |  |

|            |              | 6.1.1.3 -Program Control                                                                                   | 37 |  |  |  |  |  |  |  |  |  |

|            | 6.2 -        | INSTRUCTION SET SUMMARY                                                                                    |    |  |  |  |  |  |  |  |  |  |

|            | 6.3 -        | MAC COPROCESSOR SPECIFIC INSTRUCTIONS                                                                      | 39 |  |  |  |  |  |  |  |  |  |

| 7 -        | Exter        | nal Bus Controller                                                                                         | 43 |  |  |  |  |  |  |  |  |  |

|            | 7.1 -        | PROGRAMMABLE CHIP SELECT TIMING CONTROL                                                                    | 43 |  |  |  |  |  |  |  |  |  |

|            | 7.2 -        | READY PROGRAMMABLE POLARITY                                                                                | 43 |  |  |  |  |  |  |  |  |  |

| 8 -        | Interr       | upt System                                                                                                 | 45 |  |  |  |  |  |  |  |  |  |

|            | 8.1 -        | EXTERNAL INTERRUPTS                                                                                        | 45 |  |  |  |  |  |  |  |  |  |

|            | 8.2 -        | INTERRUPT REGISTERS AND VECTORS LOCATION LIST                                                              | 46 |  |  |  |  |  |  |  |  |  |

|            | 8.3 -        | INTERRUPT CONTROL REGISTERS47                                                                              |    |  |  |  |  |  |  |  |  |  |

### ST10F269

| TABLE        | OFC             | ONTENTS                          | 3                                                                                                                | PAGE           |

|--------------|-----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------|----------------|

| 9 -<br>10 -  | •               | re/Compa                         | ON AND ERROR TRAPS LIST<br>re (CAPCOM) Units<br>e Timer Unit                                                     | 49             |

|              | 10.1 -          | GPT1                             |                                                                                                                  |                |

| 11 -<br>12 - | PWM I           | Module                           |                                                                                                                  | 56             |

|              | 12.1 -          | INTRODU                          | JCTION                                                                                                           | 57             |

|              | 12.2 -          | 12.2.1 -<br>12.2.2 -<br>12.2.3 - | CIAL FEATURES<br>Open Drain Mode<br>Input Threshold Control<br>Output Driver Control<br>Alternate Port Functions | 59<br>59<br>60 |

|              | 12.3 -          |                                  | Alternate Functions of PORT0                                                                                     |                |

|              | 12.4 -          |                                  | Alternate Functions of PORT1                                                                                     |                |

|              | 12.5 -          |                                  | Alternate Functions of Port 2                                                                                    |                |

|              | 12.6 -          |                                  | Alternate Functions of Port 3                                                                                    |                |

|              | 12.7 -          | PORT 4 .                         | Alternate Functions of Port 4                                                                                    | 76             |

|              | 12.8 -          | PORT 5 .<br>12.8.1 -             | Alternate Functions of Port 5<br>Port 5 Schmitt Trigger Analog Inputs                                            | 80<br>81       |

|              | 12.9 -          |                                  | Alternate Functions of Port 6                                                                                    |                |

|              | 12.10 -         |                                  | Alternate Functions of Port 7                                                                                    |                |

| 13 -<br>14 - | A/D Co          | 12.11.1 -<br>onverter .          | Alternate Functions of Port 8                                                                                    | 91<br>93       |

|              | 14.1 -          | 14.1.1 -                         | RONOUS / SYNCHRONOUS SERIAL INTERFACE (ASCO)<br>ASCO in Asynchronous Mode<br>ASCO in Synchronous Mode            |                |

| 15 -         | 14.2 -<br>CAN N |                                  | EED SYNCHRONOUS SERIAL CHANNEL (SSC)                                                                             |                |

|              | 15.1 -          | 15.1.1 -                         | DULES MEMORY MAPPING<br>CAN1<br>CAN2                                                                             | 103            |

|              | 15.2 -          | CAN BUS                          | CONFIGURATIONS                                                                                                   |                |

## ST10F269

| TABLE        | OFC             | ONTENTS PA                                                                                                                                                                                                                                                                                                                  | ٩GE                                       |

|--------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| 16 -         | Real T          | ime Clock                                                                                                                                                                                                                                                                                                                   | 105                                       |

|              | 16.1 -          | RTC REGISTERS         16.1.1 -       RTCCON: RTC Control Register         16.1.2 -       RTCPH & RTCPL: RTC PRESCALER Registers         16.1.3 -       RTCDH & RTCDL: RTC DIVIDER Counters         16.1.4 -       RTCH & RTCL: RTC Programmable COUNTER Registers         16.1.5 -       RTCAH & RTCAL: RTC ALARM Registers | . 106<br>. 108<br>. 108<br>. 109          |

| 17 -<br>18 - | System          | PROGRAMMING THE RTC<br>dog Timer<br>n Reset<br>LONG HARDWARE RESET                                                                                                                                                                                                                                                          | 112<br>114                                |

|              | 10.1            | <ul> <li>18.1.1 - Asynchronous Reset</li></ul>                                                                                                                                                                                                                                                                              | . 114<br>. 115                            |

|              | 18.2 -          | SHORT HARDWARE RESET                                                                                                                                                                                                                                                                                                        | .116                                      |

|              | 18.3 -          | SOFTWARE RESET                                                                                                                                                                                                                                                                                                              | .117                                      |

|              | 18.4 -          | WATCHDOG TIMER RESET                                                                                                                                                                                                                                                                                                        | .117                                      |

|              | 18.5 -          | RSTOUT, RSTIN, BIDIRECTIONAL RESET                                                                                                                                                                                                                                                                                          | .118<br>.118                              |

| 19 -         | 18.6 -<br>Power | RESET CIRCUITRY                                                                                                                                                                                                                                                                                                             |                                           |

|              | 19.1 -          | IDLE MODE                                                                                                                                                                                                                                                                                                                   | .122                                      |

|              | 19.2 -          | POWER DOWN MODE         19.2.1 -       Protected Power Down Mode         19.2.2 -       Interruptible Power Down Mode                                                                                                                                                                                                       | . 122<br>. 122                            |

| 20 -         | •               | al Function Register Overview                                                                                                                                                                                                                                                                                               |                                           |

|              |                 |                                                                                                                                                                                                                                                                                                                             |                                           |

| 21 -         |                 | SYSTEM CONFIGURATION REGISTERS                                                                                                                                                                                                                                                                                              |                                           |

|              | 21.1 -          | ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                    | . 139                                     |

|              | 21.2 -          | PARAMETER INTERPRETATION                                                                                                                                                                                                                                                                                                    | . 139                                     |

|              | 21.3 -          | DC CHARACTERISTICS                                                                                                                                                                                                                                                                                                          | .144                                      |

|              | 21.4 -          | AC CHARACTERISTICS                                                                                                                                                                                                                                                                                                          | . 146<br>. 146<br>. 148<br>. 149<br>. 149 |

## ST10F269

| TABLE OF CONTENTS                                              | PAGE |

|----------------------------------------------------------------|------|

| 21.4.7 - Phase Locked Loop                                     | 149  |

| 21.4.8 - External Clock Drive XTAL1                            | 150  |

| 21.4.9 - Memory Cycle Variables                                | 151  |

| 21.4.10 - Multiplexed Bus                                      | 152  |

| 21.4.11 - Demultiplexed Bus                                    |      |

| 21.4.12 - CLKOUT and READY                                     |      |

| 21.4.13 - External Bus Arbitration                             | 171  |

| 21.4.14 - High-Speed Synchronous Serial Interface (SSC) Timing | 174  |

| 21.4.14.1Master Mode                                           |      |

| 21.4.14.2Slave mode                                            |      |

| 22 - Package Mechanical Data                                   | 178  |

| 23 - Ordering Information                                      | 180  |

## **ERRATA SHEET**

57

| 1 - |       |                                                                                            |     |  |  |  |  |  |  |  |

|-----|-------|--------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|

| 2 - | FUNC  | TIONAL PROBLEMS                                                                            | 181 |  |  |  |  |  |  |  |

|     | 2.1 - | PWRDN.1 - EXECUTION OF PWRDN INSTRUCTION                                                   | 181 |  |  |  |  |  |  |  |

|     | 2.2 - | MAC.9 - COCMP INSTRUCTION INVERTED OPERANDS                                                | 182 |  |  |  |  |  |  |  |

|     | 2.3 - | MAC.10 - E FLAG EVALUATION FOR COSHR AND COASHR INSTRUCTIONS WE SATURATION MODE IS ENABLED |     |  |  |  |  |  |  |  |

|     | 2.4 - | ST_PORT.3 - BAD BEHAVIOR OF HYSTERESIS FUNCTION ON INPUT FALLING EDGE                      |     |  |  |  |  |  |  |  |

| 3 - | DEVIA | TIONS FROM DC/AC PRELIMINARY SPECIFICATION                                                 |     |  |  |  |  |  |  |  |

| 4 - | ERRA  | TA SHEET VERSION INFORMATION                                                               | 183 |  |  |  |  |  |  |  |

لركم اركم

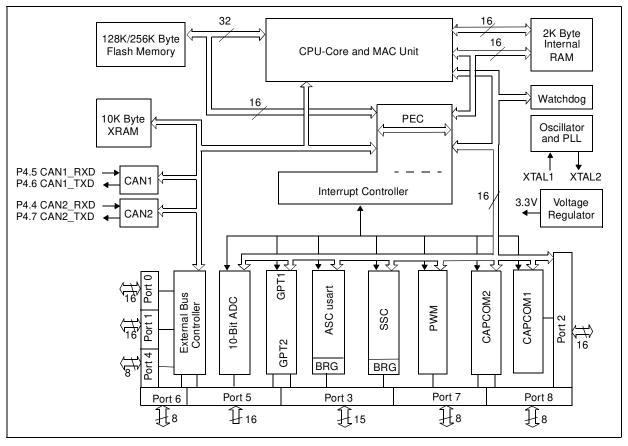

#### **1 - INTRODUCTION**

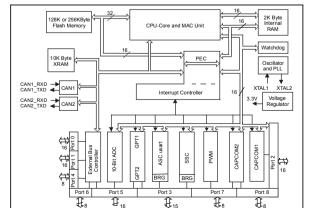

The ST10F269 is а derivative of the **ST10** STMicroelectronics family 16-bit of single-chip CMOS microcontrollers. It combines high CPU performance (up to 20 million instructions per second) with high peripheral functionality and enhanced I/O-capabilities. It also provides on-chip high-speed single voltage Flash memory, on-chip high-speed RAM, and clock generation via PLL.

ST10F269 is processed in  $0.35\mu$ m CMOS technology. The MCU core and the logic is supplied with a 5V to 3.3V on chip voltage regulator on PQFP144 devices (or 5V to 2.7V on TQFP144 devices). The part is supplied with a single 5V supply and I/Os work at 5V.

The device is upward compatible with the ST10F168 device, with the following set of differences:

- The Multiply/Accumulate unit is available as standard. This MAC unit adds powerful DSP functions to the ST10 architecture, but maintains full compatibility for existing code.

- Flash control interface is now based on STMicroelectronics third generation of stand-alone Flash memories, with an embedded Erase/Program Controller. This completely

frees up the CPU during programming or erasing the Flash.

- 128-KByte Flash Option

- Two dedicated pins (DC1 and DC2) on the 144-pin package are used for decoupling the internally generated 3.3V (or 2.7V on TQFP144 devices) core logic supply. Do not connect these two pins to 5.0V external supply. Instead, these pins should be connected to a decoupling capacitor (ceramic type, value  $\geq$  330 nF).

- The A/D Converter characteristics are different from previous ST10 derivatives ones. Refer to Section 21.3.1 -.

- The AC and DC parameters are adapted to the 40MHz maximum CPU frequency on PQFP144 devices (32MHz on TQFP144 devices). The characterization is performed with  $C_L = 50$ pF max on output pins. Refer to Section 21.3 -.

- In order to reduce EMC, the rise/fall time and the sink/source capability of the drivers of the I/O pads are programmable. Refer to Section 12.2 -.

- The Real Time Clock functionality is added.

- The external interrupt sources can be selected with the EXISEL register.

- The reset source is identified by a dedicated status bit in the WDTCON register.

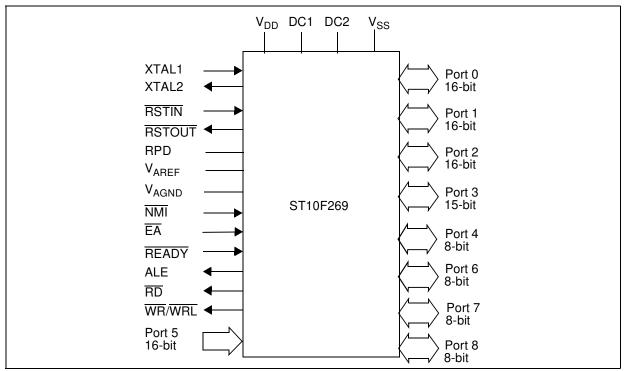

Figure 1 : Logic Symbol

#### 2 - PIN DATA

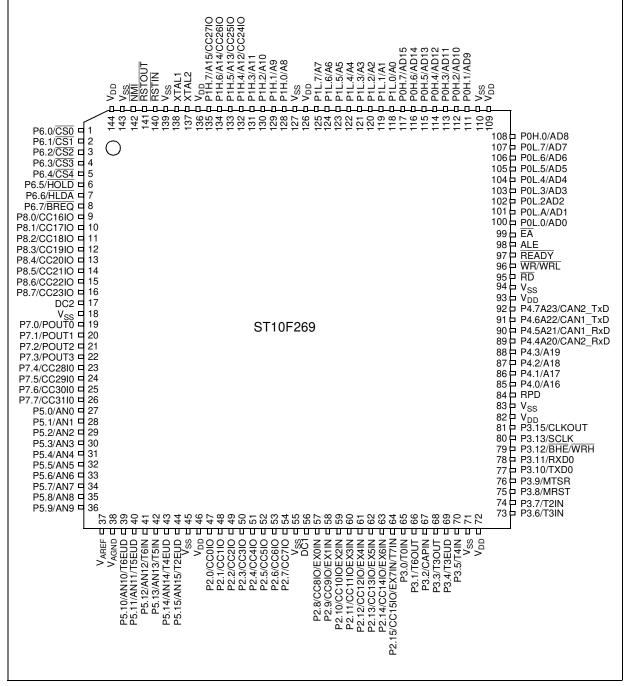

Figure 2 : Pin Configuration (top view)

57

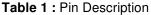

| Symbol                       | Pin            | Туре | Function                                                                                                                                                                                                                                                                                                                                                                     |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|------------------------------|----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| P6.0 - P6.7                  | 1 - 8          | I/O  | 8-bit bidirectional I/O port, bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. Port 6 outputs can be configured as push-pull or open drain drivers. The following Port 6 pins have alternate functions:                                                          |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 1              | 0    | P6.0                                                                                                                                                                                                                                                                                                                                                                         | CS0                                                   | Chip Select 0 Output                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                              |                |      |                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 5              | 0    | P6.4                                                                                                                                                                                                                                                                                                                                                                         | CS4                                                   | Chip Select 4 Output                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                              | 6              | I    | P6.5                                                                                                                                                                                                                                                                                                                                                                         | HOLD                                                  | External Master Hold Request Input                                                                                                                                                                                                                                        |  |  |  |  |  |

|                              | 7              | 0    | P6.6                                                                                                                                                                                                                                                                                                                                                                         | HLDA                                                  | Hold Acknowledge Output                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                              | 8              | 0    | P6.7                                                                                                                                                                                                                                                                                                                                                                         | BREQ                                                  | Bus Request Output                                                                                                                                                                                                                                                        |  |  |  |  |  |

| P8.0 - P8.7                  | 9-16           | I/O  | 8-bit bidirectional I/O port, bit-wise programmable for input or output via dir<br>bit. Programming an I/O pin as input forces the corresponding output driver to<br>impedance state. Port 8 outputs can be configured as push-pull or open<br>drivers. The input threshold of Port 8 is selectable (TTL or special).<br>The following Port 8 pins have alternate functions: |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 9              | I/O  | P8.0                                                                                                                                                                                                                                                                                                                                                                         | CC16IO                                                | CAPCOM2: CC16 Capture Input / Compare Output                                                                                                                                                                                                                              |  |  |  |  |  |

|                              |                |      |                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 16             | I/O  | P8.7                                                                                                                                                                                                                                                                                                                                                                         | CC23IO                                                | CAPCOM2: CC23 Capture Input / Compare Output                                                                                                                                                                                                                              |  |  |  |  |  |

| P7.0 - P7.7                  | 19-26          | I/O  | bit. Pro<br>impeda<br>drivers.                                                                                                                                                                                                                                                                                                                                               | gramming an I/C<br>nce state. Port<br>The input thres | ort, bit-wise programmable for input or output via direction<br>D pin as input forces the corresponding output driver to high<br>7 outputs can be configured as push-pull or open drain<br>hold of Port 7 is selectable (TTL or special).<br>Is have alternate functions: |  |  |  |  |  |

|                              | 19             | 0    | P7.0                                                                                                                                                                                                                                                                                                                                                                         | POUT0                                                 | PWM Channel 0 Output                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                              |                |      |                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 22             | 0    | P7.3                                                                                                                                                                                                                                                                                                                                                                         | POUT3                                                 | PWM Channel 3 Output                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                              | 23             | I/O  | P7.4                                                                                                                                                                                                                                                                                                                                                                         | CC28IO                                                | CAPCOM2: CC28 Capture Input / Compare Output                                                                                                                                                                                                                              |  |  |  |  |  |

|                              |                |      |                                                                                                                                                                                                                                                                                                                                                                              |                                                       |                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                              | 26             | I/O  | P7.7                                                                                                                                                                                                                                                                                                                                                                         | CC31IO                                                | CAPCOM2: CC31 Capture Input / Compare Output                                                                                                                                                                                                                              |  |  |  |  |  |

| P5.0 - P5.9<br>P5.10 - P5.15 | 27-36<br>39-44 |      | the ana                                                                                                                                                                                                                                                                                                                                                                      | log input chann                                       | ith Schmitt-Trigger characteristics. The pins of Port 5 can be<br>els (up to 16) for the A/D converter, where P5.x equals ANx<br>(c), or they are timer inputs:                                                                                                           |  |  |  |  |  |

|                              | 39             | I    | P5.10                                                                                                                                                                                                                                                                                                                                                                        | T6EUD                                                 | GPT2 Timer T6 External Up / Down Control Input                                                                                                                                                                                                                            |  |  |  |  |  |

|                              | 40             | I    | P5.11                                                                                                                                                                                                                                                                                                                                                                        | T5EUD                                                 | GPT2 Timer T5 External Up / Down Control Input                                                                                                                                                                                                                            |  |  |  |  |  |

|                              | 41             | I    | P5.12                                                                                                                                                                                                                                                                                                                                                                        | T6IN                                                  | GPT2 Timer T6 Count Input                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                              | 42             | I    | P5.13                                                                                                                                                                                                                                                                                                                                                                        | T5IN                                                  | GPT2 Timer T5 Count Input                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                              | 43             | I    | P5.14                                                                                                                                                                                                                                                                                                                                                                        | T4EUD                                                 | GPT1 Timer T4 External Up / Down Control Input                                                                                                                                                                                                                            |  |  |  |  |  |

|                              | 44             | I    | P5.15                                                                                                                                                                                                                                                                                                                                                                        | T2EUD                                                 | GPT1 Timer T2 External Up / Down Control Input                                                                                                                                                                                                                            |  |  |  |  |  |

57

| Symbol                                | Pin                    | Туре              | Function                                                                                                                                                                                                                                                                                                                                                                                       |        |                                                          |  |  |  |  |  |  |

|---------------------------------------|------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------------------|--|--|--|--|--|--|

| P2.0 - P2.7<br>P2.8 - P2.15           | 47-54<br>57-64         | I/O               | 16-bit bidirectional I/O port, bit-wise programmable for input or output via direction<br>bit. Programming an I/O pin as input forces the corresponding output driver to high<br>impedance state. Port 2 outputs can be configured as push-pull or open drain<br>drivers. The input threshold of Port 2 is selectable (TTL or special).<br>The following Port 2 pins have alternate functions: |        |                                                          |  |  |  |  |  |  |

|                                       | 47                     | I/O               | P2.0                                                                                                                                                                                                                                                                                                                                                                                           | CC0IO  | CAPCOM: CC0 Capture Input / Compare Output               |  |  |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                          |  |  |  |  |  |  |

|                                       | 54                     | I/O               | P2.7                                                                                                                                                                                                                                                                                                                                                                                           | CC7IO  | CAPCOM: CC7 Capture Input / Compare Output               |  |  |  |  |  |  |

|                                       | 57                     | I/O               | P2.8                                                                                                                                                                                                                                                                                                                                                                                           | CC8IO  | CAPCOM: CC8 Capture Input / Compare Output               |  |  |  |  |  |  |

|                                       |                        | Ι                 |                                                                                                                                                                                                                                                                                                                                                                                                | EX0IN  | Fast External Interrupt 0 Input                          |  |  |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                                |        |                                                          |  |  |  |  |  |  |

|                                       | 64                     | I/O               | P2.15                                                                                                                                                                                                                                                                                                                                                                                          | CC15IO | CAPCOM: CC15 Capture Input / Compare Output              |  |  |  |  |  |  |

|                                       |                        | I                 |                                                                                                                                                                                                                                                                                                                                                                                                | EX7IN  | Fast External Interrupt 7 Input                          |  |  |  |  |  |  |

|                                       |                        | I                 |                                                                                                                                                                                                                                                                                                                                                                                                | T7IN   | CAPCOM2 Timer T7 Count Input                             |  |  |  |  |  |  |

| P3.0 - P3.5<br>P3.6 - P3.13,<br>P3.15 | 65-70,<br>73-80,<br>81 | I/O<br>I/O<br>I/O | 15-bit (P3.14 is missing) bidirectional I/O port, bit-wise programmable for input output via direction bit. Programming an I/O pin as input forces the correspond output driver to high impedance state. Port 3 outputs can be configured as push-p or open drain drivers. The input threshold of Port 3 is selectable (TTL or special). The following Port 3 pins have alternate functions:   |        |                                                          |  |  |  |  |  |  |

|                                       | 65                     | I                 | P3.0                                                                                                                                                                                                                                                                                                                                                                                           | TOIN   | CAPCOM Timer T0 Count Input                              |  |  |  |  |  |  |

|                                       | 66                     | 0                 | P3.1                                                                                                                                                                                                                                                                                                                                                                                           | T6OUT  | GPT2 Timer T6 Toggle Latch Output                        |  |  |  |  |  |  |

|                                       | 67                     | I                 | P3.2                                                                                                                                                                                                                                                                                                                                                                                           | CAPIN  | GPT2 Register CAPREL Capture Input                       |  |  |  |  |  |  |

|                                       | 68                     | 0                 | P3.3                                                                                                                                                                                                                                                                                                                                                                                           | T3OUT  | GPT1 Timer T3 Toggle Latch Output                        |  |  |  |  |  |  |

|                                       | 69                     | I                 | P3.4                                                                                                                                                                                                                                                                                                                                                                                           | T3EUD  | GPT1 Timer T3 External Up / Down Control Input           |  |  |  |  |  |  |

|                                       | 70                     | I                 | P3.5                                                                                                                                                                                                                                                                                                                                                                                           | T4IN   | GPT1 Timer T4 Input for Count / Gate / Reload / Capture  |  |  |  |  |  |  |

|                                       | 73                     | I                 | P3.6                                                                                                                                                                                                                                                                                                                                                                                           | T3IN   | GPT1 Timer T3 Count / Gate Input                         |  |  |  |  |  |  |

|                                       | 74                     | I                 | P3.7                                                                                                                                                                                                                                                                                                                                                                                           | T2IN   | GPT1 Timer T2 Input for Count / Gate / Reload / Capture  |  |  |  |  |  |  |

|                                       | 75                     | I/O               | P3.8                                                                                                                                                                                                                                                                                                                                                                                           | MRST   | SSC Master-Receiver / Slave-Transmitter I/O              |  |  |  |  |  |  |

|                                       | 76                     | I/O               | P3.9                                                                                                                                                                                                                                                                                                                                                                                           | MTSR   | SSC Master-Transmitter / Slave-Receiver O/I              |  |  |  |  |  |  |

|                                       | 77                     | 0                 | P3.10                                                                                                                                                                                                                                                                                                                                                                                          | TxD0   | ASC0 Clock / Data Output (Asynchronous /<br>Synchronous) |  |  |  |  |  |  |

|                                       | 78                     | I/O               | P3.11                                                                                                                                                                                                                                                                                                                                                                                          | RxD0   | ASC0 Data Input (Asynchronous) or I/O (Synchronous)      |  |  |  |  |  |  |

|                                       | 79                     | 0                 | P3.12                                                                                                                                                                                                                                                                                                                                                                                          | BHE    | External Memory High Byte Enable Signal                  |  |  |  |  |  |  |

|                                       |                        |                   |                                                                                                                                                                                                                                                                                                                                                                                                | WRH    | External Memory High Byte Write Strobe                   |  |  |  |  |  |  |

|                                       | 80                     | I/O               | P3.13                                                                                                                                                                                                                                                                                                                                                                                          | SCLK   | SSC Master Clock Output / Slave Clock Input              |  |  |  |  |  |  |

|                                       | 81                     | 0                 | P3.15                                                                                                                                                                                                                                                                                                                                                                                          | CLKOUT | System Clock Output (=CPU Clock)                         |  |  |  |  |  |  |

| Symbol          | Pin   | Туре | Function                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|-----------------|-------|------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| P4.0 –P4.7      | 85-92 | I/O  | via dire<br>driver t<br>Port 4.0<br>In case | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise programmable for input or output via direction bit. Programming an I/O pin as input forces the corresponding output driver to high impedance state. The input threshold is selectable (TTL or special). Port 4.6 & 4.7 outputs can be configured as push-pull or open drain drivers. In case of an external bus configuration, Port 4 can be used to output the segment address lines: |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                 | 85    | 0    | P4.0                                        | P4.0 A16 Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                 | 86    | 0    | P4.1                                        | A17                                                                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                 | 87    | 0    | P4.2                                        | A18                                                                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                 | 88    | 0    | P4.3                                        | A19                                                                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                 | 89    | 0    | P4.4                                        | A20                                                                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                 |       | I    | CAN2_RxD CAN2 Receive Data Input            |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                 | 90    | 0    | P4.5                                        | Segment Address Line                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                 |       | I    |                                             | CAN1_RxD                                                                                                                                                                                                                                                                                                                                                                                                                                         | CAN1 Receive Data Input                                                                                                                                                                                                                              |  |  |  |  |  |  |  |

|                 | 91    | 0    | P4.6                                        | A22                                                                                                                                                                                                                                                                                                                                                                                                                                              | Segment Address Line<br>CAN1 Transmit Data Output                                                                                                                                                                                                    |  |  |  |  |  |  |  |

|                 |       | 0    |                                             | CAN1_TxD                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

|                 | 92    | 0    | P4.7                                        | A23                                                                                                                                                                                                                                                                                                                                                                                                                                              | Most Significant Segment Address Line                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                 |       | 0    |                                             | CAN2_TxD                                                                                                                                                                                                                                                                                                                                                                                                                                         | CAN2 Transmit Data Output                                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| RD              | 95    | 0    | Externa read ac                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Strobe. $\overline{\text{RD}}$ is activated for every external instruction or data                                                                                                                                                                   |  |  |  |  |  |  |  |

| WR/WRL          | 96    | 0    | data w<br>access                            | rite access. In<br>es on a 16-bit l                                                                                                                                                                                                                                                                                                                                                                                                              | Strobe. In $\overline{\text{WR}}$ -mode this pin is activated for every external $\overline{\text{WRL}}$ mode this pin is activated for low Byte data write bus, and for every data write access on an 8-bit bus. See N register for mode selection. |  |  |  |  |  |  |  |

| READY/<br>READY | 97    | I    | enable                                      | Ready Input. The active level is programmable. When the Ready function is enabled, the selected inactive level at this pin, during an external memory access, will force the insertion of waitstate cycles until the pin returns to the selected active level.                                                                                                                                                                                   |                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| ALE             | 98    | 0    |                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output. In case of use of external addressing or of multi-<br>I is the latch command of the address lines.                                                                                                                                           |  |  |  |  |  |  |  |