## mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## ST72260Gx, ST72262Gx, ST72264Gx

8-BIT MCU WITH FLASH OR ROM MEMORY, ADC, TWO 16-BIT TIMERS, I<sup>2</sup>C, SPI, SCI INTERFACES

#### Memories

- 4 K or 8 Kbytes Program memory: ROM or Single voltage extended Flash (XFlash) with read-out protection write protection and In-Circuit Programming and In-Application Programming (ICP and IAP). 10K write/erase cycles guaranteed, data retention: 20 years at 55°C.

- 256 bytes RAM

#### Clock, Reset and Supply Management

- Enhanced reset system

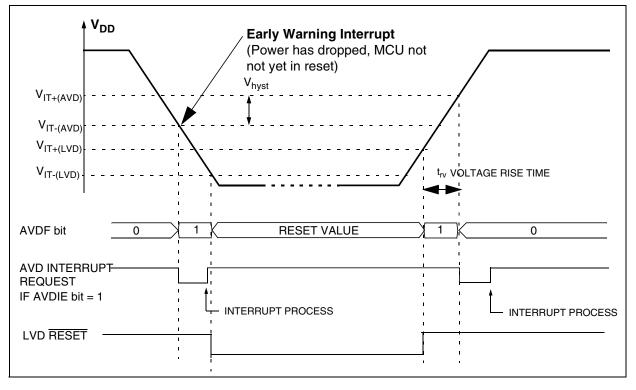

- Enhanced low voltage supply supervisor (LVD) with 3 programmable levels and auxiliary voltage detector (AVD) with interrupt capability for implementing safe power-down procedures

- Clock sources: crystal/ceramic resonator oscillators, internal RC oscillator and bypass for external clock

- PLL for 2x frequency multiplication

- Clock-out capability

- 4 Power Saving Modes: Halt, Active Halt, Wait and Slow

#### Interrupt Management

- Nested interrupt controller

- 10 interrupt vectors plus TRAP and RESET

- 22 external interrupt lines (on 2 vectors)

#### 22 I/O Ports

- 22 multifunctional bidirectional I/O lines

- 20 alternate function lines

- 8 high sink outputs

- 4 Timers

- Main Clock Controller with Real time base and Clock-out capabilities

- Configurable watchdog timer

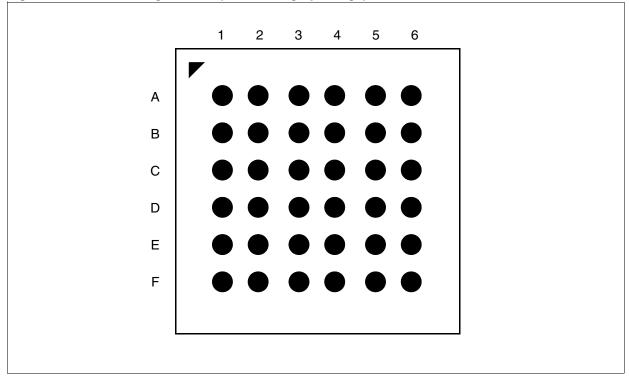

# SDIP32 FBGA 6x6mm SO28

Two 16-bit timers with: 2 input captures, 2 output compares, external clock input on one timer, PWM and Pulse generator modes

#### 3 Communication Interfaces

- SPI synchronous serial interface

- I<sup>2</sup>C multimaster interface (SMBus V1.1 Compliant)

- SCI asynchronous serial interface

- 1 Analog peripheral

- 10-bit ADC with 6 input channels

- Instruction Set

- 8-bit data manipulation

- 63 basic instructions with illegal opcode detection

- 17 main addressing modes

- 8 x 8 unsigned multiply instruction

- Development Tools

- Full hardware/software development package

#### **Device Summary**

| Features               | ST72260G1 ST72262G1                           |             | ST72262G2                     | ST72264G1 S                                                                |           | 72264G2 |  |  |

|------------------------|-----------------------------------------------|-------------|-------------------------------|----------------------------------------------------------------------------|-----------|---------|--|--|

| Program memory - bytes | 4K                                            | 4K          | 8K                            | 4K                                                                         | 8K        |         |  |  |

| RAM (stack) - bytes    | RAM (stack) - bytes 256 (128)                 |             |                               |                                                                            |           |         |  |  |

| Peripherals            | Watchdog timer, RTC,<br>Two16-bit timers, SPI |             | timer, RTC,<br>ners, SPI, ADC | Watchdog timer, RTC,<br>Two 16-bit timers, SPI, SCI, I <sup>2</sup> C, ADC |           |         |  |  |

| Operating Supply       |                                               | •           | 2.7 V to                      | 5.5 V                                                                      |           |         |  |  |

| CPU Frequency          |                                               | Up to 8 MHz | z (with oscillator u          | p to 16 MHz) PL                                                            | L 4/8 MHz |         |  |  |

| Operating Temperature  |                                               | -40° C to + | -40° C to +85° C              | 0° C to +70° C /<br>-40° C to +85° C                                       |           |         |  |  |

| Packages               | SO28 / SDIP32 SO28 / SDIP32                   |             |                               |                                                                            |           |         |  |  |

## **Table of Contents**

| 2 PIN DE<br>3 REGIS | DUCTION<br>ESCRIPTION<br>TER & MEMORY MAP<br>I PROGRAM MEMORY | 6<br>10 |

|---------------------|---------------------------------------------------------------|---------|

| 4.1                 |                                                               | 14      |

| 4.2                 | MAIN FEATURES                                                 | 14      |

| 4.3                 | PROGRAMMING MODES                                             | 14      |

| 4.4                 | ICC INTERFACE                                                 | 15      |

| 4.5                 | MEMORY PROTECTION                                             | 16      |

| 4.6                 | RELATED DOCUMENTATION                                         | 16      |

| 4.7                 | REGISTER DESCRIPTION                                          | 16      |

| 5 CENT              | RAL PROCESSING UNIT                                           | 17      |

| 5.1                 |                                                               | 17      |

| 5.2                 | MAIN FEATURES                                                 | 17      |

| 5.3                 | CPU REGISTERS                                                 | 17      |

| 6 SUPPL             | LY, RESET AND CLOCK MANAGEMENT                                | 20      |

| 6.1                 | PHASE LOCKED LOOP                                             | 20      |

| 6.2                 | MULTI-OSCILLATOR (MO)                                         | 21      |

| 6.3                 | RESET SEQUENCE MANAGER (RSM)                                  | 22      |

| 6.4                 | SYSTEM INTEGRITY MANAGEMENT (SI)                              | 24      |

| 7 INTER             | RUPTS                                                         | 28      |

| 7.1                 | INTRODUCTION                                                  | 28      |

| 7.2                 | MASKING AND PROCESSING FLOW                                   | 28      |

| 7.3                 | INTERRUPTS AND LOW POWER MODES                                | 30      |

| 7.4                 | CONCURRENT & NESTED MANAGEMENT                                | 30      |

| 7.5                 | INTERRUPT REGISTER DESCRIPTION                                | 31      |

| 8 POWE              | R SAVING MODES                                                | 33      |

| 8.1                 |                                                               | 33      |

| 8.2                 | SLOW MODE                                                     | 33      |

| 8.3                 | WAIT MODE                                                     |         |

| 8.4                 | ACTIVE-HALT AND HALT MODES                                    | 35      |

| 8.5                 | HALT MODE                                                     | 36      |

| 9 I/O PO            | RTS                                                           | 38      |

| 9.1                 |                                                               | 38      |

| 9.2                 | FUNCTIONAL DESCRIPTION                                        | 38      |

| 9.3                 | I/O PORT IMPLEMENTATION                                       | 41      |

| 9.4                 | UNUSED I/O PINS                                               | 41      |

| 9.5                 | LOW POWER MODES                                               | 41      |

| 9.6                 | INTERRUPTS                                                    | 41      |

| 9.7                 | DEVICE-SPECIFIC I/O PORT CONFIGURATION                        | 42      |

| 9.8                 | I/O PORT REGISTER DESCRIPTION                                 |         |

| 10 MISC             | ELLANEOUS REGISTERS                                           | 45      |

57

### Table of Contents

\_

| 10.1 I/O PORT INTERRUPT SENSITIVITY                              | 45 |

|------------------------------------------------------------------|----|

| 10.2 I/O PORT ALTERNATE FUNCTIONS                                | 45 |

| 10.3 MISCELLANEOUS REGISTER DESCRIPTION                          | 46 |

| 11 ON-CHIP PERIPHERALS                                           | 48 |

| 11.1 WATCHDOG TIMER (WDG)                                        |    |

| 11.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (MCC/RTC)        | 53 |

| 11.3 16-BIT TIMER                                                | 55 |

| 11.4 SERIAL PERIPHERAL INTERFACE (SPI)                           | 75 |

| 11.5 SERIAL COMMUNICATIONS INTERFACE (SCI)                       | 87 |

| 11.6 I2C BUS INTERFACE (I2C) 1                                   | 03 |

| 11.7 10-BIT A/D CONVERTER (ADC) 1                                | 16 |

| 12 INSTRUCTION SET                                               | 20 |

| 12.1 CPU ADDRESSING MODES 1                                      | 20 |

| 12.2 INSTRUCTION GROUPS 1                                        | 23 |

| 13 ELECTRICAL CHARACTERISTICS 1                                  | 26 |

| 13.1 PARAMETER CONDITIONS 1                                      |    |

| 13.2 ABSOLUTE MAXIMUM RATINGS 1                                  | 27 |

| 13.3 OPERATING CONDITIONS 1                                      | 28 |

| 13.4 SUPPLY CURRENT CHARACTERISTICS 1                            | 31 |

| 13.5 CLOCK AND TIMING CHARACTERISTICS 1                          | 35 |

| 13.6 MEMORY CHARACTERISTICS 1                                    | 40 |

| 13.7 EMC CHARACTERISTICS 1                                       | 41 |

| 13.8 I/O PORT PIN CHARACTERISTICS 1                              | 44 |

| 13.9 CONTROL PIN CHARACTERISTICS 1                               | 50 |

| 13.10 TIMER PERIPHERAL CHARACTERISTICS                           | 52 |

| 13.11 COMMUNICATION INTERFACE CHARACTERISTICS                    | 53 |

| 13.12 10-BIT ADC CHARACTERISTICS 1                               | 57 |

| 14 PACKAGE CHARACTERISTICS                                       | 59 |

| 14.1 PACKAGE MECHANICAL DATA 1                                   | 59 |

| 14.2 THERMAL CHARACTERISTICS 1                                   | 60 |

| 14.3 LEAD-FREE PACKAGE INFORMATION 1                             | 61 |

| 15 DEVICE CONFIGURATION AND ORDERING INFORMATION                 | 62 |

| 15.1 OPTION BYTES 1                                              | 62 |

| 15.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE 1 | 64 |

| 15.3 DEVELOPMENT TOOLS 1                                         | 66 |

| 16 KNOWN LIMITATIONS                                             | 68 |

| 16.1 ALL FLASH AND ROM DEVICES 1                                 | 68 |

| 16.2 FLASH DEVICES ONLY 1                                        | 68 |

| 17 REVISION HISTORY                                              | 71 |

To obtain the most recent version of this datasheet, please check at www.st.com>products>technical literature>datasheet Please note that the list of known limitations can be found at the end of this document on page 168.

57

#### **1 INTRODUCTION**

The ST72260Gx, ST72262Gx and ST72264Gx devices are members of the ST7 microcontroller family. They can be grouped as follows :

- ST72264Gx devices are designed for mid-range applications with ADC, I<sup>2</sup>C and SCI interface capabilities.

- ST72262Gx devices target the same range of applications but without 1<sup>2</sup>C interface or SCI.

- ST72260Gx devices are for applications that do not need ADC, I<sup>2</sup>C peripherals or SCI.

All devices are based on a common industrystandard 8-bit core, featuring an enhanced instruction set.

The ST72F260G, ST72F262G, and ST72F264G versions feature single-voltage FLASH memory with byte-by-byte In-Circuit Programming (ICP) capabilities.

Under software control, all devices can be placed in WAIT, SLOW, Active-HALT or HALT mode, reducing power consumption when the application is in idle or stand-by state.

The enhanced instruction set and addressing modes of the ST7 offer both power and flexibility to software developers, enabling the design of highly efficient and compact application code. In addition to standard 8-bit data management, all ST7 microcontrollers feature true bit manipulation, 8x8 unsigned multiplication and indirect addressing modes.

For easy reference, all parametric data is located in Section 13 on page 126.

#### **Related Documentation**

AN1365: Guidelines for migrating ST72C254 applications to ST72F264

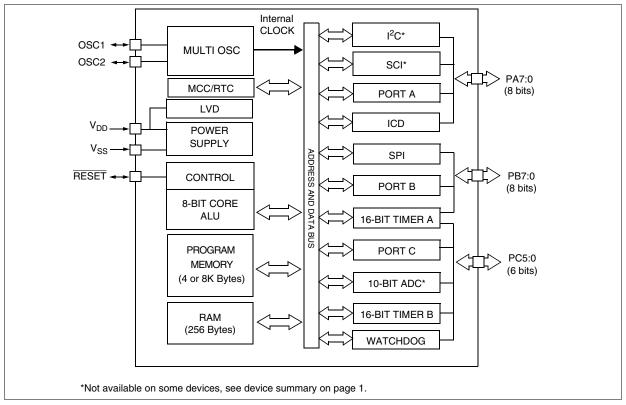

#### Figure 1. General Block Diagram

#### **2 PIN DESCRIPTION**

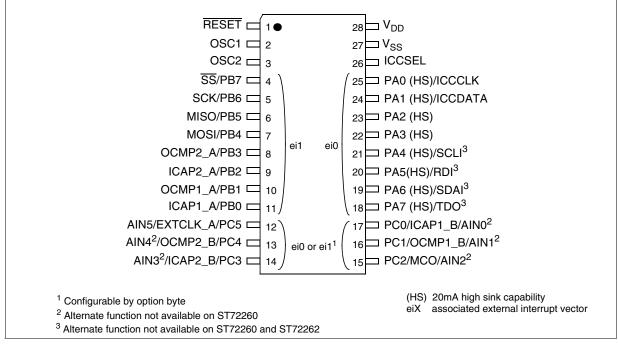

#### Figure 2. 28-Pin SO Package Pinout

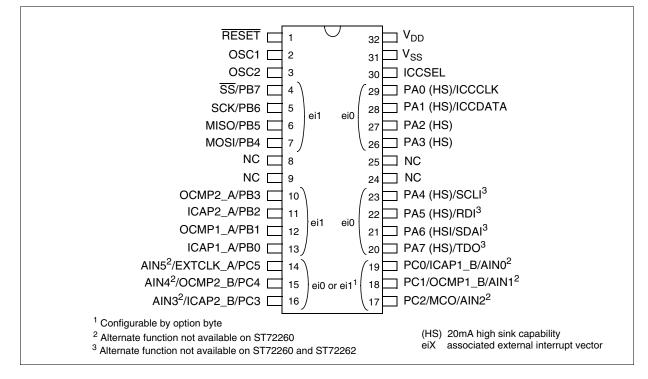

#### Figure 3. 32-Pin SDIP Package Pinout

#### PIN DESCRIPTION (Cont'd)

57

#### Figure 4. TFBGA Package Pinout (view through package)

#### PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to Section 13 "ELECTRICAL CHARACTERISTICS" on page 126.

#### Legend / Abbreviations for Table 1:

Type:I = input, O = output, S = supplyInput level:A = Dedicated analog inputIn/Output level: $C_T$  = CMOS 0.3 V<sub>DD</sub>/0.7 V<sub>DD</sub> with input triggerOutput level:HS = 20 mA high sink (on N-buffer only)Port and control configuration:

- Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1</sup>), ana = analog

- Output:  $OD = open drain^{2}$ , PP = push-pull

Refer to Section 9 "I/O PORTS" on page 38 for more details on the software configuration of the I/O ports. The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

## Table 1. Device Pin Description

| F      | Pin n° |     |                    | Level |       | Port / Control |       |                |       |     |         | Main                                                                                                                 |                                                                                                                  |                                                               |                               |

|--------|--------|-----|--------------------|-------|-------|----------------|-------|----------------|-------|-----|---------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------|

| 32     | 28     | A   | Pin Name           | Type  | ut    | out            |       | Inp            | ut    |     | Out     | put                                                                                                                  | Function<br>(after                                                                                               | Alternate Function                                            |                               |

| SDIP32 | S028   | BGA |                    | н     | Input | Output         | float | ndw            | int   | ana | OD      | ЬΡ                                                                                                                   | reset)                                                                                                           |                                                               |                               |

| 1      | 1      | A3  | RESET              | I/O   | Ст    |                |       | х              |       |     | х       |                                                                                                                      | Top prior tive low)                                                                                              | ity non maskable interrupt (ac-                               |                               |

| 2      | 2      | C4  | OSC1 <sup>3)</sup> | Ι     |       |                |       |                |       |     |         |                                                                                                                      | External clock input or Resonator oscillator inverter input or resistor input for RC oscillator                  |                                                               |                               |

| 3      | 3      | B3  | OSC2 <sup>3)</sup> | 0     |       |                |       |                |       |     |         |                                                                                                                      |                                                                                                                  | or oscillator inverter output or ca-<br>put for RC oscillator |                               |

| 4      | 4      | A2  | PB7/SS             | I/O   | C     | CT             | Х     | ei             | 1     |     | Х       | Х                                                                                                                    | Port B7                                                                                                          | SPI Slave Select (active low)                                 |                               |

| 5      | 5      | A1  | PB6/SCK            | I/O   | C     | CT             | X ei1 |                |       | Х   | Х       | Port B6                                                                                                              | SPI Serial Clock                                                                                                 |                                                               |                               |

| 6      | 6      | B1  | PB5/MISO           | I/O   | C     | C <sub>T</sub> | X ei1 |                | X ei1 |     |         | Х                                                                                                                    | Х                                                                                                                | Port B5                                                       | SPI Master In/ Slave Out Data |

| 7      | 7      | B2  | PB4/MOSI           | I/O   | C     | C <sub>T</sub> | X ei1 |                | Х     | Х   | Port B4 | SPI Master Out / Slave In Data                                                                                       |                                                                                                                  |                                                               |                               |

| 8      |        | C1  | NC                 |       |       |                |       |                |       |     |         |                                                                                                                      |                                                                                                                  |                                                               |                               |

| 9      |        | C2  | NC                 |       |       |                |       |                |       |     | Ν       | ot C                                                                                                                 | onnected                                                                                                         |                                                               |                               |

|        |        | D1  | NC                 |       |       |                |       |                |       |     |         |                                                                                                                      |                                                                                                                  |                                                               |                               |

| 10     | 8      | C3  | PB3/OCMP2_A        | I/O   | C     | CT             | Χ     | ei             | 1     |     | Х       | Х                                                                                                                    | Port B3                                                                                                          | Timer A Output Compare 2                                      |                               |

| 11     | 9      | D2  | PB2/ICAP2_A        | I/O   | C     | C <sub>T</sub> | X     | ei             | 1     |     | Х       | Х                                                                                                                    | Port B2                                                                                                          | Timer A Input Capture 2                                       |                               |

| 12     | 10     | E1  | PB1 /OCMP1_A       | I/O   | C     | Ст             | x     | <b>X</b> ei1 X |       | х   | Port B1 | Timer A Output Compare 1<br><b>Caution:</b> Negative current<br>injection not allowed on<br>this pin <sup>4)</sup> . |                                                                                                                  |                                                               |                               |

| 13     | 11     | F1  | PB0 /ICAP1_A       | I/O   | C     | Ст             | x     | ei             | 1     |     | х       | х                                                                                                                    | Port B0 Timer A Input Capture 1<br>Caution: Negative cur<br>injection not allowed of<br>this pin <sup>4)</sup> . |                                                               |                               |

| 14     | 12     | F2  | PC5/EXTCLK_A/AIN5  | I/O   | C     | C <sub>T</sub> | x     | ei0/           | ei1   | х   | х       | Х                                                                                                                    | Port C5                                                                                                          | Timer A Input Clock or ADC<br>Analog Input 5                  |                               |

| Pin n° |      | þ   |                   |      | Level          |                |       | Ро        | rt / C | Cont        | rol |       | Main                                                 |                                                   |         |                                                                |

|--------|------|-----|-------------------|------|----------------|----------------|-------|-----------|--------|-------------|-----|-------|------------------------------------------------------|---------------------------------------------------|---------|----------------------------------------------------------------|

| 32     | 28   | A   | Pin Name          | Type | rt             | out            |       | Inp       | out    |             | Out | tput  | Function<br>(after                                   | Alternate Function                                |         |                                                                |

| SDIP32 | S028 | BGA |                   | F    | Input          | Output         | float | ndm       | int    | ana         | OD  | ЬΡ    | reset)                                               |                                                   |         |                                                                |

| 15     | 13   | E2  | PC4/OCMP2_B/AIN4  | I/O  | (              | CT             | х     | ei0       | /ei1   | х           | х   | х     | Port C4                                              | Timer B Output Compare 2 or<br>ADC Analog Input 4 |         |                                                                |

| 16     | 14   | F3  | PC3/ ICAP2_B/AIN3 | I/O  | 0              | CT             | x     | ei0,      | /ei1   | х           | х   | х     | Port C3                                              | Timer B Input Capture 2 or<br>ADC Analog Input 3  |         |                                                                |

| 17     | 15   | E3  | PC2/MCO/AIN2      | I/O  | (              | CT             | x     | X ei0/ei1 |        | X ei0/ei1 X |     | х     | х                                                    | х                                                 | Port C2 | Main clock output (f <sub>CPU</sub> ) or<br>ADC Analog Input 2 |

| 18     | 16   | F4  | PC1/OCMP1_B/AIN1  | I/O  | C              | C <sub>T</sub> | x     | ei0/ei1 X |        | Х           | Х   | х     | Port C1 Timer B Output Compare<br>ADC Analog Input 1 |                                                   |         |                                                                |

| 19     | 17   | D3  | PC0/ICAP1_B/AIN0  | I/O  | C              | CT             | x     | ei0/ei1   |        | Х           | Х   | х     | Port C0                                              | Timer B Input Capture 1 or<br>ADC Analog Input 0  |         |                                                                |

| 20     | 18   | E4  | PA7/TDO           | I/O  | $C_T$          | HS             | Х     | е         | i0     |             | Х   | х     | Port A7                                              | SCI output                                        |         |                                                                |

| 21     | 19   | F5  | PA6/SDAI          | I/O  | $C_T$          | HS             | Χ     |           | ei0    |             | Т   |       | Port A6                                              | I <sup>2</sup> C DATA                             |         |                                                                |

| 22     | 20   | F6  | PA5 /RDI          | I/O  | $C_T$          | HS             | Х     | е         | i0     |             | Х   | Х     | Port A5                                              | SCI input                                         |         |                                                                |

| 23     | 21   | E6  | PA4/SCLI          | I/O  | $C_T$          | HS             | X     |           | ei0    |             | Т   |       | Port A4                                              | I <sup>2</sup> C CLOCK                            |         |                                                                |

| 24     |      | E5  | NC                |      |                |                | 1     |           |        |             |     |       |                                                      |                                                   |         |                                                                |

| 25     |      | D6  | NC                |      |                |                |       |           |        |             | Ν   | ot C  | onnected                                             |                                                   |         |                                                                |

|        |      | D5  | NC                |      |                |                |       |           |        |             |     |       |                                                      |                                                   |         |                                                                |

| 26     | 22   | C6  | PA3               | I/O  | $C_T$          | HS             | Χ     | е         | i0     |             | Х   | Х     | Port A3                                              |                                                   |         |                                                                |

| 27     | 23   | D4  | PA2               | I/O  | $C_T$          | HS             | Х     | е         | i0     |             | Х   | Х     | Port A2                                              |                                                   |         |                                                                |

|        |      | C5  | NC                |      | 1              |                |       |           |        |             |     |       |                                                      |                                                   |         |                                                                |

|        |      | B6  | NC                |      |                |                |       |           |        |             | IN  | ot Co | onnected                                             |                                                   |         |                                                                |

| 28     | 24   | A6  | PA1/ICCDATA       | I/O  | $C_T$          | HS             | X     | е         | i0     |             | Х   | Х     | Port A1                                              | In Circuit Communication Data                     |         |                                                                |

| 29     | 25   | A5  | PA0/ICCCLK        | I/O  | C <sub>T</sub> | HS             | x     | е         | i0     |             | х   | х     | Port A0                                              | In Circuit Communication<br>Clock                 |         |                                                                |

| 30     | 26   | B5  | ICCSEL            | Ι    | $C_T$          |                | Х     |           |        |             |     |       | ICC mode pin, must be tied low                       |                                                   |         |                                                                |

| 31     | 27   | A4  | V <sub>SS</sub>   | S    |                |                |       |           |        |             |     |       | Ground                                               |                                                   |         |                                                                |

| 32     | 28   | B4  | V <sub>DD</sub>   | S    |                |                |       |           |        |             |     |       | Main pow                                             | ver supply                                        |         |                                                                |

#### Notes:

1. In the interrupt input column, "eiX" defines the associated external interrupt vector. If the weak pull-up column (wpu) is merged with the interrupt column (int), then the I/O configuration is a pull-up interrupt input, otherwise the configuration is a floating interrupt input. Port C is mapped to ei0 or ei1 by option byte.

2. In the open drain output column, "T" defines a true open drain I/O (P-Buffer and protection diode to  $V_{DD}$  are not implemented). See Section 9 "I/O PORTS" on page 38 for more details.

3. OSC1 and OSC2 pins connect a crystal or ceramic resonator, or an external source to the on-chip oscillator see Section 2 "PIN DESCRIPTION" on page 6 and Section 6.2 "MULTI-OSCILLATOR (MO)" on page 21 for more details.

4: For details refer to Section 13.8 on page 144

#### **3 REGISTER & MEMORY MAP**

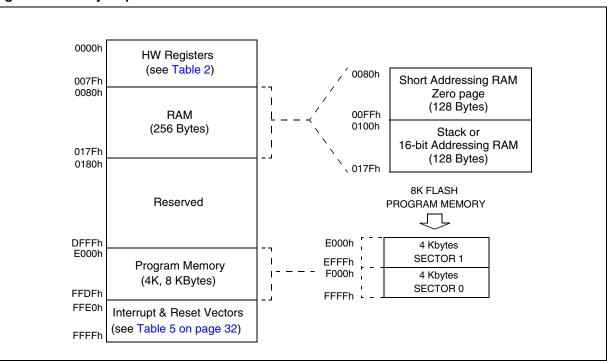

As shown in Figure 5, the MCU is capable of addressing 64K bytes of memories and I/O registers.

The available memory locations consist of 128 bytes of register location, 256 bytes of RAM and up to 8 Kbytes of user program memory. The RAM space includes up to 128 bytes for the stack from 0100h to 017Fh.

The highest address bytes contain the user reset and interrupt vectors.

The Flash memory contains two sectors (see Figure 5) mapped in the upper part of the ST7 ad-

dressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

The size of Flash Sector 0 and other device options are configurable by Option byte (refer to Section 15.1 on page 162).

**IMPORTANT:** Memory locations marked as "Reserved" must never be accessed. Accessing a reseved area can have unpredictable effects on the device.

#### **Related Documentation**

AN 985: Executing Code in ST7 RAM

#### Figure 5. Memory Map

#### Table 2. Hardware Register Map

57

| Address                                                     | Block            | Register<br>Label                                                  | Register Name                                                                                                                                                                                                                                                                   | Reset<br>Status                               | Remarks                                                     |

|-------------------------------------------------------------|------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------|

| 0000h<br>0001h<br>0002h                                     | Port C           | PCDR<br>PCDDR<br>PCOR                                              | Port C Data Register<br>Port C Data Direction Register<br>Port C Option Register                                                                                                                                                                                                | xx000000h <sup>1)</sup><br>00h<br>00h         | R/W <sup>2)</sup><br>R/W <sup>2)</sup><br>R/W <sup>2)</sup> |

| 0003h                                                       |                  |                                                                    | Reserved (1 Byte)                                                                                                                                                                                                                                                               |                                               |                                                             |

| 0004h<br>0005h<br>0006h                                     | Port B           | PBDR<br>PBDDR<br>PBOR                                              | Port B Data Register<br>Port B Data Direction Register<br>Port B Option Register                                                                                                                                                                                                | 00h <sup>1)</sup><br>00h<br>00h               | R/W<br>R/W<br>R/W.                                          |

| 0007h                                                       |                  |                                                                    | Reserved (1 Byte)                                                                                                                                                                                                                                                               |                                               |                                                             |

| 0008h<br>0009h<br>000Ah                                     | Port A           | 00h <sup>1)</sup><br>00h<br>00h                                    | R/W<br>R/W<br>R/W                                                                                                                                                                                                                                                               |                                               |                                                             |

| 000Bh<br>to<br>001Bh                                        |                  |                                                                    | Reserved (17 Bytes)                                                                                                                                                                                                                                                             |                                               |                                                             |

| 001Ch<br>001Dh<br>001Eh<br>001Fh                            | ITC              | ISPR0<br>ISPR1<br>ISPR2<br>ISPR3                                   | Interrupt software priority register0<br>Interrupt software priority register1<br>Interrupt software priority register2<br>Interrupt software priority register3                                                                                                                | FFh<br>FFh<br>FFh<br>FFh                      | R/W<br>R/W<br>R/W<br>R/W                                    |

| 0020h                                                       |                  | MISCR1                                                             | Miscellanous register 1                                                                                                                                                                                                                                                         | 00h                                           | R/W                                                         |

| 0021h<br>0022h<br>0023h                                     | SPI              | SPIDR<br>SPICR<br>SPICSR                                           | SPI Data I/O Register<br>SPI Control Register<br>SPI Status Register                                                                                                                                                                                                            | xxh<br>0xh<br>00h                             | R/W<br>R/W<br>R/W                                           |

| 0024h                                                       | WATCHDOG         | WDGCR                                                              | Watchdog Control Register                                                                                                                                                                                                                                                       | 7Fh                                           | R/W                                                         |

| 0025h                                                       |                  | SICSR                                                              | System Integrity Control / Status Register                                                                                                                                                                                                                                      | 000x 000x                                     | R/W                                                         |

| 0026h                                                       | MCC              | MCCSR                                                              | Main Clock Control / Status Register                                                                                                                                                                                                                                            | 00h                                           | R/W                                                         |

| 0027h                                                       |                  |                                                                    | Reserved (1 Byte)                                                                                                                                                                                                                                                               | ·                                             |                                                             |

| 0028h<br>0029h<br>002Ah<br>002Bh<br>002Ch<br>002Dh<br>002Eh | l <sup>2</sup> C | I2CCR<br>I2CSR1<br>I2CSR2<br>I2CCCR<br>I2COAR1<br>I2COAR2<br>I2CDR | I <sup>2</sup> C Control Register<br>I <sup>2</sup> C Status Register 1<br>I <sup>2</sup> C Status Register 2<br>I <sup>2</sup> C Clock Control Register<br>I <sup>2</sup> C Own Address Register 1<br>I <sup>2</sup> C Own Address Register2<br>I <sup>2</sup> C Data Register | 00h<br>00h<br>00h<br>00h<br>00h<br>40h<br>00h | R/W<br>Read Only<br>R/W<br>R/W<br>R/W<br>R/W                |

| 002Fh<br>0030h                                              |                  | 1                                                                  | Reserved (2 Bytes)                                                                                                                                                                                                                                                              | 1                                             |                                                             |

| Address                                                                                                                                                                                                     | Block               | Register<br>Label                                                                                                                                                                                                                                                                                             | Register Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Reset<br>Status                                                                                                                                        | Remarks                                                                                                                                                                                                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0031h<br>0032h<br>0033h<br>0034h<br>0035h<br>0036h                                                                                                                                                          |                     | TACR2<br>TACR1<br>TASCSR<br>TAIC1HR<br>TAIC1LR<br>TAOC1HR                                                                                                                                                                                                                                                     | Timer A Control Register 2<br>Timer A Control Register 1<br>Timer A Control/Status Register<br>Timer A Input Capture 1 High Register<br>Timer A Input Capture 1 Low Register<br>Timer A Output Compare 1 High Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00h<br>00h<br>xxh<br>xxh<br>xxh<br>xxh<br>80h                                                                                                          | R/W<br>R/W<br>R/W<br>Read Only<br>Read Only<br>R/W                                                                                                                                                            |  |  |  |

| 0037h<br>0038h<br>0039h<br>003Ah<br>003Bh<br>003Ch<br>003Dh<br>003Eh<br>003Fh                                                                                                                               | TIMER A             | TAOC1LR<br>TACHR<br>TACLR<br>TAACHR<br>TAACLR<br>TAIC2HR<br>TAIC2LR<br>TAOC2HR<br>TAOC2LR                                                                                                                                                                                                                     | Timer A Output Compare 1 Low Register<br>Timer A Counter High Register<br>Timer A Counter Low Register<br>Timer A Alternate Counter High Register<br>Timer A Alternate Counter Low Register<br>Timer A Input Capture 2 High Register<br>Timer A Input Capture 2 Low Register<br>Timer A Output Compare 2 High Register<br>Timer A Output Compare 2 Low Register                                                                                                                                                                                                                                                                                                                                                                                         | 00h<br>FFh<br>FCh<br>FCh<br>xxh<br>xxh<br>80h<br>00h                                                                                                   | R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W<br>R/W                                                                                                                            |  |  |  |

| 0040h                                                                                                                                                                                                       |                     | MISCR2                                                                                                                                                                                                                                                                                                        | Miscellanous register 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 00h                                                                                                                                                    | R/W                                                                                                                                                                                                           |  |  |  |

| 0041h<br>0042h<br>0043h<br>0044h<br>0045h<br>0046h<br>0047h<br>0048h<br>0049h<br>004Ah<br>004Bh<br>004Ch<br>004Ch<br>004Ch<br>004Ch<br>004Ch<br>004Fh<br>0051h<br>0052h<br>0053h<br>0053h<br>0055h<br>0056h | TIMER B             | TBCR2<br>TBCR1<br>TBSCSR<br>TBIC1HR<br>TBIC1LR<br>TBOC1HR<br>TBOC1HR<br>TBCLR<br>TBCLR<br>TBCLR<br>TBCLR<br>TBC2HR<br>TBIC2HR<br>TBIC2HR<br>TBIC2HR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR<br>TBIC2LR | Timer B Control Register 2<br>Timer B Control Register 1<br>Timer B Control/Status Register<br>Timer B Input Capture 1 High Register<br>Timer B Input Capture 1 Low Register<br>Timer B Output Compare 1 High Register<br>Timer B Output Compare 1 Low Register<br>Timer B Counter High Register<br>Timer B Counter Low Register<br>Timer B Alternate Counter High Register<br>Timer B Alternate Counter Low Register<br>Timer B Input Capture 2 High Register<br>Timer B Input Capture 2 Low Register<br>Timer B Output Compare 2 High Register<br>Timer B Output Compare 2 Low Register<br>SCI Status Register<br>SCI Data Register<br>SCI Data Register<br>SCI Control Register1<br>SCI Control Register2<br>SCI Extended Receive Prescaler Register | 00h<br>00h<br>xxh<br>xxh<br>xxh<br>80h<br>00h<br>FFh<br>FCh<br>FCh<br>FCh<br>xxh<br>80h<br>00h<br>00h<br>xxh<br>00h<br>x000 0000h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>Read Only<br>Read Only<br>R/W<br>R/W<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>Read Only<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W |  |  |  |

| 0057h<br>to<br>006Eh                                                                                                                                                                                        |                     |                                                                                                                                                                                                                                                                                                               | Reserved (24 Bytes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |                                                                                                                                                                                                               |  |  |  |

| 006Fh<br>0070h<br>0071h                                                                                                                                                                                     | ADC                 | ADCDRL<br>ADCDRH<br>ADCCSR                                                                                                                                                                                                                                                                                    | Data Register Low <sup>3)</sup><br>Data Register High <sup>3)</sup><br>Control/Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 00h<br>00h<br>00h                                                                                                                                      | Read Only<br>Read Only<br>R/W                                                                                                                                                                                 |  |  |  |

| 0072h                                                                                                                                                                                                       | FLASH               | FCSR                                                                                                                                                                                                                                                                                                          | Flash Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00h                                                                                                                                                    | R/W                                                                                                                                                                                                           |  |  |  |

| 0073h<br>to<br>007Fh                                                                                                                                                                                        | Reserved (13 Bytes) |                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |                                                                                                                                                                                                               |  |  |  |

57

#### Legend: x=Undefined, R/W=Read/Write

#### Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

3. For compatibility with the ST72C254, the ADCDRL and ADCDRH data registers are located with the LSB on the lower address (6Fh) and the MSB on the higher address (70h). As this scheme is not little Endian, the ADC data registers cannot be treated by C programs as an integer, but have to be treated as two char registers.

#### 4 FLASH PROGRAM MEMORY

#### 4.1 Introduction

The ST7 single voltage extended Flash (XFlash) is a non-volatile memory that can be electrically erased and programmed either on a byte-by-byte basis or up to 32 bytes in parallel.

The XFlash devices can be programmed off-board (plugged in a programming tool) or on-board using In-Circuit Programming or In-Application Programming.

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

#### 4.2 Main Features

- ICP (In-Circuit Programming)

- IAP (In-Application Programming)

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Sector 0 size configurable by option byte

- Read-out and write protection against piracy

#### **4.3 PROGRAMMING MODES**

The ST7 can be programmed in three different ways:

- Insertion in a programming tool. In this mode, FLASH sectors 0 and 1 and option byte row can be programmed or erased.

- In-Circuit Programming. In this mode, FLASH sectors 0 and 1 and option byte row can be programmed or erased without removing the device from the application board.

- In-Application Programming. In this mode, sector 1 can be programmed or erased without removing the device from the application

board and while the application is running.

#### 4.3.1 In-Circuit Programming (ICP)

ICP uses a protocol called ICC (In-Circuit Communication) which allows an ST7 plugged on a printed circuit board (PCB) to communicate with an external programming device connected via cable. ICP is performed in three steps:

Switch the ST7 to ICC mode (In-Circuit Communications). This is done by driving a specific signal sequence on the ICCCLK/DATA pins while the RESET pin is pulled low. When the ST7 enters ICC mode, it fetches a specific RESET vector which points to the ST7 System Memory containing the ICC protocol routine. This routine enables the ST7 to receive bytes from the ICC interface.

- Download ICP Driver code in RAM from the ICCDATA pin

- Execute ICP Driver code in RAM to program the FLASH memory

Depending on the ICP Driver code downloaded in RAM, FLASH memory programming can be fully customized (number of bytes to program, program locations, or selection of the serial communication interface for downloading).

#### 4.3.2 In Application Programming (IAP)

This mode uses an IAP Driver program previously programmed in Sector 0 by the user (in ICP mode).

This mode is fully controlled by user software. This allows it to be adapted to the user application, (user-defined strategy for entering programming mode, choice of communications protocol used to fetch the data to be stored etc.)

IAP mode can be used to program any memory areas except Sector 0, which is write/erase protected to allow recovery in case errors occur during the programming operation.

#### FLASH PROGRAM MEMORY (Cont'd)

#### 4.4 ICC interface

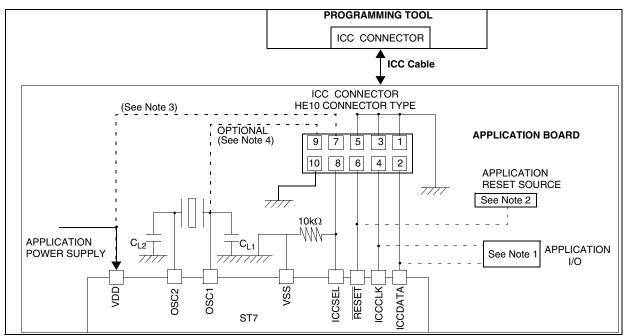

ICP needs a minimum of 4 and up to 7 pins to be connected to the programming tool. These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input serial data pin

- ICCSEL: ICC selection (not required on devices without ICCSEL pin)

- OSC1: main clock input for external source (not required on devices without OSC1/OSC2 pins)

- V<sub>DD</sub>: application board power supply (optional, see Note 3)

#### Notes:

1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to be implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

2. During the ICP session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset management IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

3. The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

4. Pin 9 has to be connected to the OSC1 pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

Figure 6. Typical ICC Interface

#### FLASH PROGRAM MEMORY (Cont'd)

#### **4.5 Memory Protection**

There are two different types of memory protection: Read Out Protection and Write/Erase Protection which can be applied individually.

#### 4.5.1 Read out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In flash devices, this protection is removed by reprogramming the option. In this case the program memory is automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

#### 4.5.2 Flash Write/Erase Protection

Write/erase protection, when set, makes it impossible to both overwrite and erase program memory. Its purpose is to provide advanced security to applications and prevent any change being made to the memory content.

**Warning**: Once set, Write/erase protection can never be removed. A write-protected flash device is no longer reprogrammable.

Write/erase protection is enabled through the FMP\_W bit in the option byte.

#### 4.6 Related Documentation

For details on Flash programming and ICC protocol, refer to the ST7 Flash Programming Reference Manual and to the ST7 ICC Protocol Reference Manual.

AN1477: Emulated data EEPROM with XFlash memory

AN1576: IAP drivers for ST7 HDFlash or XFlash MCUs

AN1575: On Board Programming methods for ST7 HDFlash or XFlash MCUs

AN1070: Checksum self checking capability

#### 4.7 Register Description

#### FLASH CONTROL/STATUS REGISTER (FCSR) Read/Write

Reset Value: 000 0000 (00h) 1st RASS Key: 0101 0110 (56h) 2nd RASS Key: 1010 1110 (AEh)

| 7 |   |   |   |   |     |     | 0   |

|---|---|---|---|---|-----|-----|-----|

| 0 | 0 | 0 | 0 | 0 | OPT | LAT | PGM |

**Note:** This register is reserved for programming using ICP, IAP or other programming methods. It controls the XFlash programming and erasing operations.

When an EPB or another programming tool is used (in socket or ICP mode), the RASS keys are sent automatically.

#### **5 CENTRAL PROCESSING UNIT**

#### **5.1 INTRODUCTION**

This CPU has a full 8-bit architecture and contains six internal registers allowing efficient 8-bit data manipulation.

#### **5.2 MAIN FEATURES**

- Enable executing 63 basic instructions

- Fast 8-bit by 8-bit multiply

- 17 main addressing modes (with indirect addressing mode)

- Two 8-bit index registers

- 16-bit stack pointer

- Low power HALT and WAIT modes

- Priority maskable hardware interrupts

- Non-maskable software/hardware interrupts

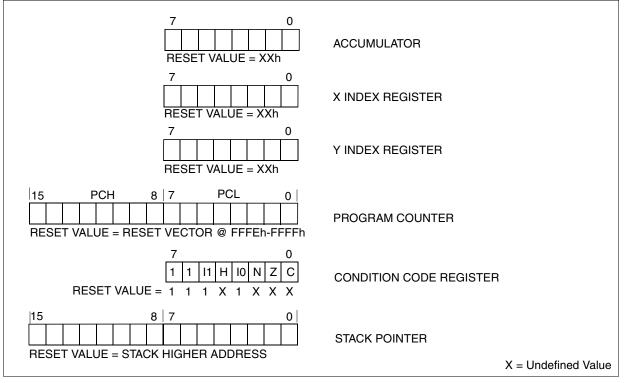

#### **5.3 CPU REGISTERS**

The 6 CPU registers shown in Figure 7 are not present in the memory mapping and are accessed by specific instructions.

#### Accumulator (A)

The Accumulator is an 8-bit general purpose register used to hold operands and the results of the arithmetic and logic calculations and to manipulate data.

#### Index Registers (X and Y)

These 8-bit registers are used to create effective addresses or as temporary storage areas for data manipulation. (The Cross-Assembler generates a precede instruction (PRE) to indicate that the following instruction refers to the Y register.)

The Y register is not affected by the interrupt automatic procedures.

#### Program Counter (PC)

The program counter is a 16-bit register containing the address of the next instruction to be executed by the CPU. It is made of two 8-bit registers PCL (Program Counter Low which is the LSB) and PCH (Program Counter High which is the MSB).

#### Figure 7. CPU Registers

5/

#### CENTRAL PROCESSING UNIT (Cont'd)

Condition Code Register (CC)

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### Arithmetic Management Bits

Bit  $4 = \mathbf{H}$  Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred.

1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

Bit 2 = N Negative.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result  $7^{th}$  bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(i.e. the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

#### Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

0: The result of the last operation is different from zero.

1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### **Interrupt Management Bits**

#### Bit 5,3 = **I1**, **I0** Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 1 | 10 |

|-------------------------------|---|----|

| Level 0 (main)                | 1 | 0  |

| Level 1                       | 0 | 1  |

| Level 2                       | 0 | 0  |

| Level 3 (= interrupt disable) | 1 | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

#### CENTRAL PROCESSING UNIT (Cont'd)

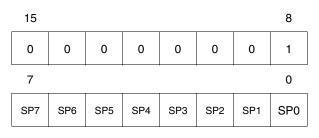

**Stack Pointer (SP)**

Read/Write

Reset Value: 01 7Fh

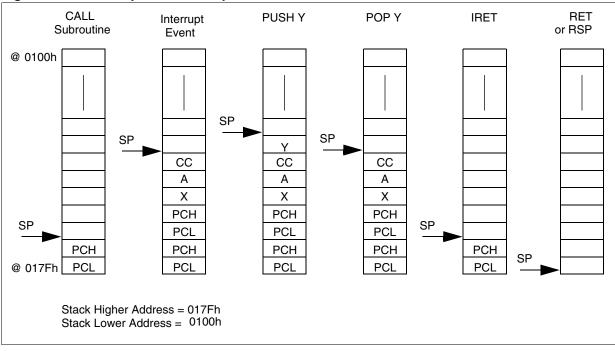

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 8).

Since the stack is 128 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

#### Figure 8. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 8

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

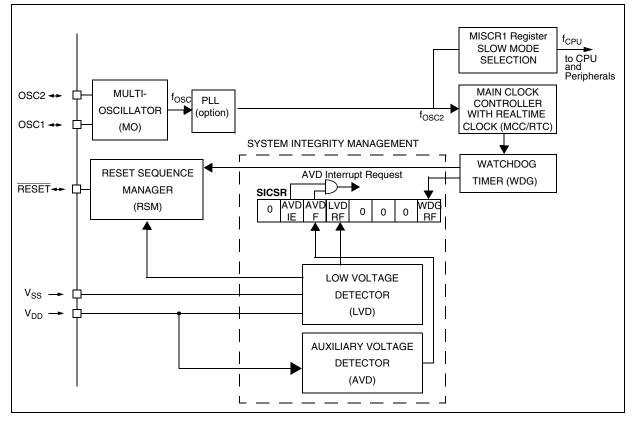

#### **6 SUPPLY, RESET AND CLOCK MANAGEMENT**

The device includes a range of utility features for securing the application in critical situations (for example in case of a power brown-out), and reducing the number of external components. An overview is shown in Figure 10.

For more details, refer to dedicated parametric section.

#### **Main Features**

- Optional PLL for multiplying the frequency by 2 (not to be used with internal RC oscillator)

- Reset Sequence Manager (RSM)

- Multi-Oscillator Clock Management (MO)

- 4 Crystal/Ceramic resonator oscillators

- 1 Internal RC oscillator

- System Integrity Management (SI)

- Main supply Low Voltage Detector (LVD)

- Auxiliary Voltage Detector (AVD) with interrupt capability for monitoring the main supply

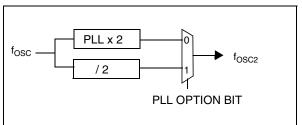

#### 6.1 PHASE LOCKED LOOP

If the clock frequency input to the PLL is in the 2 to 4 MHz range, the PLL can be used to multiply the frequency by two to obtain an  $f_{OSC2}$  of 4 to 8 MHz.

The PLL is enabled by option byte. If the PLL is disabled, then  $f_{OSC2} = f_{OSC}/2$ .

**Caution:** The PLL is not recommended for applications where timing accuracy is required. See "PLL Characteristics" on page 139.

#### Figure 9. PLL Block Diagram

#### Figure 10. Clock, Reset and Supply Block Diagram

#### 6.2 MULTI-OSCILLATOR (MO)

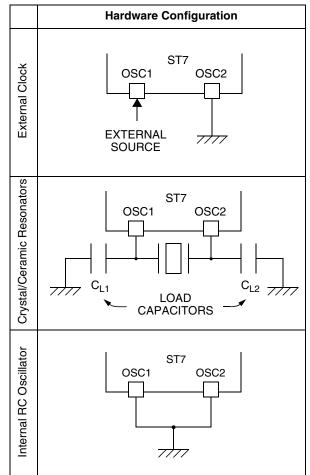

The main clock of the ST7 can be generated by four different source types coming from the multioscillator block:

- an external source

- 5 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 3. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effects Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

57/

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 5 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to Section 15.1 on page 162 for more details on the frequency ranges). In this mode of the multioscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

#### **Related documentation**

AN1530: Accurate timebase for low cost ST7 applications with internal RC.

#### Table 3. ST7 Clock Sources

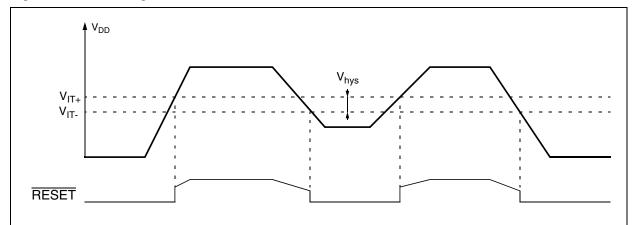

#### 6.3 RESET SEQUENCE MANAGER (RSM)

#### 6.3.1 Introduction

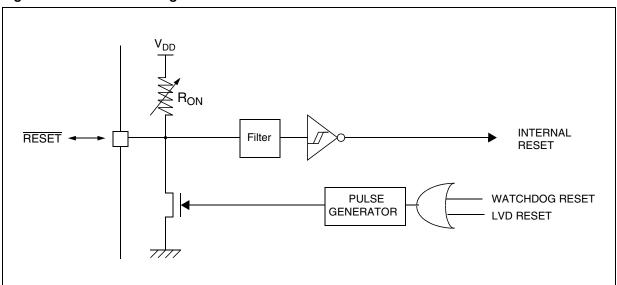

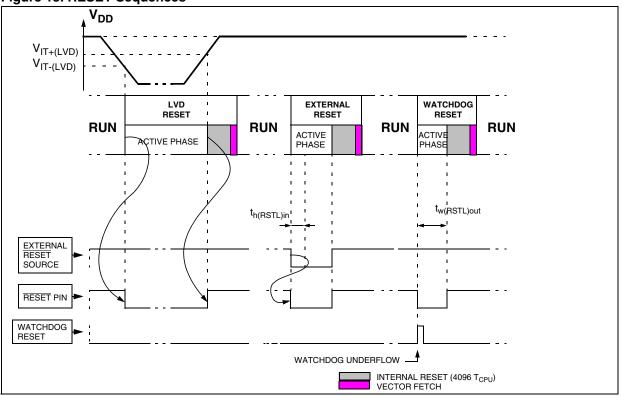

The reset sequence manager includes three RE-SET sources as shown in Figure 12:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

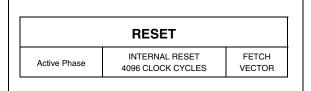

The basic RESET sequence consists of 3 phases as shown in Figure 11:

- Active Phase depending on the RESET source

- 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

The 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application.

#### Figure 12. Reset Block Diagram