# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **STA5630**

### Low power GPS RF front-end

#### Data brief - production data

#### **Features**

- Integrated LNA

- Low power consumption (< 25 mW)

- 1.8 V supply voltage

- GPS and Galileo compliant

- Minimum external components

- Serial interface

- 3 bits A/D converter

- CMOS 65 nm technology

- Standard QFN-32 package

- Ambient temperature range: -40 °C to +85 °C

#### **Description**

The STA5630 is a fully integrated RF front-end able to down-convert either the GPS L1 signal from 1575.42 MHz to 4.092 MHz.

The STA5630 embeds high performance LNA minimizing external component count. The chip uses state of the art CMOS 65 nm technology.

A 3-bit ADC converts the IF signal to Sign (SIGN) and Magnitude (MAG0 and MAG1). The magnitude bits are internally integrated in order to control the variable gain amplifiers. The VGA gain can be also set by the SPI interface.

The STA5630 accepts a range of reference clocks (10 to 52 MHz) and generates a 16.368 MHz sampling clock (GPS\_CLK) for the baseband. The STA5630 embeds LDO to supply the internal core of the device facilitating requirements to external power supply.

High performance, low power, and cost effective device, the STA5630 is the ideal solution for automotive, cellular and consumer battery powered applications.

| Table 1. | Device | summary |

|----------|--------|---------|

|----------|--------|---------|

| Order code                | Marking  | Package  | Packing       |

|---------------------------|----------|----------|---------------|

| STA5630TR                 | STA5630  | VFQFPN32 | Tape and reel |

| STA5630ATR <sup>(1)</sup> | STA5630A | VFQFPN32 | Tape and reel |

1. Automotive Grade.

#### September 2013

### Contents

| 1 | Applications        |

|---|---------------------|

|   | 1.1 Block diagram   |

| 2 | Pin description     |

| 3 | Package information |

| 4 | Revision history    |

### 1 Applications

Three main applications cases are considered and described hereafter.

The first uses a passive antenna and only a single RF SAW in front of the internal LNA. It targets low cost and medium performance applications. In this case LNA is ON and RFA could be set at minimum gain if heavy blocker signals are present.

The second uses a passive antenna and two RF SAWs. It maximizes the performances in presence of severe blockers. In this case LNA is ON and RFA is set at maximum gain.

The third case uses an active antenna. This solution targets applications where the GPS antenna is far from the RF front-end. In this case the signal can be fed into either LNA or RFA input depending on the application conditions.

STA5630 is suitable for baseband requiring 16.368/4.092 clock/RF interface and one, two or three bits samples. It accepts reference clocks (TCXO) in the range of 10-52 MHz and delivers a TCXO buffered copy to the baseband.

The STA5630 has two default modes selectable by an external pin (MODE):

- MODE 0: the chip is configured to use 16.368 MHz as reference frequency,

- MODE 1: the chip is configured to use 26 MHz as reference frequency.

Other modes are programmed through the serial interface

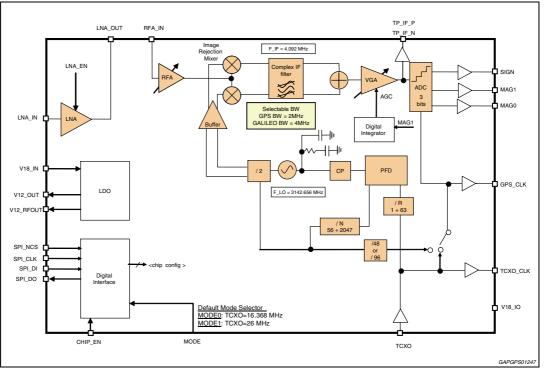

#### 1.1 Block diagram

#### Figure 1. Block diagram

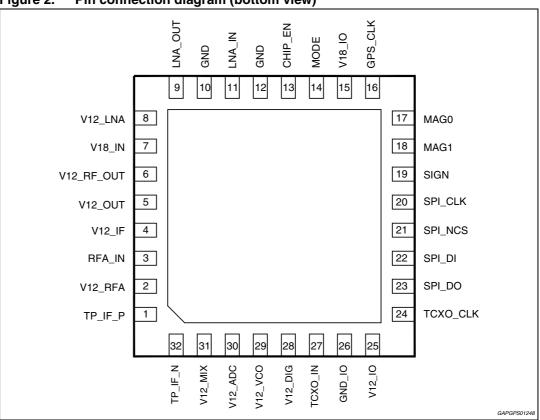

## 2 Pin description

| Table 2. | Pin | list | description |  |

|----------|-----|------|-------------|--|

|          |     | 1131 | acouption   |  |

| Pin # | Pin name   | Description                                                                         | Туре           |

|-------|------------|-------------------------------------------------------------------------------------|----------------|

| 1     | TP_IF_P    | RF/IF receiver chain test positive output                                           | Analog output  |

| 2     | V12_RFA    | RF amplifier (RFA) power supply (1.2V)                                              | Supply pin     |

| 3     | RFA_IN     | RFA input, DC coupled                                                               | Analog input   |

| 4     | V12_IF     | IF section power supply (1.2V)                                                      | Supply pin     |

| 5     | V12_OUT    | LDO IF/DIG output. Power supply (1.2V) delivered for IF/ADC/DIG_TCXO/VCO/VDD_IO VCC | Output         |

| 6     | V12_RF_OUT | LDO RF output: Power supply (1.2V) delivered for<br>LNA/RFA/MIXER VCC               | Output         |

| 7     | V18_IN     | LDOs power supply (1.8V)                                                            | Supply pin     |

| 8     | V12_LNA    | Low noise amplifier (LNA) power supply (1.2V)                                       | Supply pin     |

| 9     | LNA_OUT    | LNA output                                                                          | Analog output  |

| 10    | GND        | Ground                                                                              | Ground         |

| 11    | LNA_IN     | LNA input, DC coupled                                                               | Analog input   |

| 12    | GND        | Ground                                                                              | Ground         |

| 13    | CHIP_EN    | Chip Enable                                                                         | Digital input  |

| 14    | MODE       | Power-On Default Configuration Selector                                             | Digital input  |

| 15    | V18_IO     | I/Os power supply (1.8V)                                                            | Supply pin     |

| 16    | GPS_CLK    | GPS clock (16.368MHz)                                                               | Digital output |

| 17    | MAG0       | Mag0 data (Last significant bit)                                                    | Digital output |

| 18    | MAG1       | Mag1 data                                                                           | Digital output |

| 19    | SIGN       | Sign data (most significant bit)                                                    | Digital output |

| 20    | SPI_CLK    | Serial Parallel Interface Clock                                                     | Digital input  |

| 21    | SPI_NCS    | Serial Parallel Interface Chip Select (Active Low - 1.8V domain)                    | Digital input  |

| 22    | SPI_DI     | Serial Parallel Interface Data Input                                                | Digital input  |

| 23    | SPI_DO     | Serial Parallel Interface Data Output                                               | Digital output |

| 24    | TCXO_CLK   | TCXO Buffered Output                                                                | Digital output |

| 25    | V12_IO     | Power supply for I/Os digital section (1.2V)                                        | Supply pin     |

| 26    | GND_IO     | I/Os Ground                                                                         | Ground         |

| 27    | TCXO_IN    | TCXO Input, DC coupled                                                              | Analog input   |

| 28    | V12_DIG    | Digital section and TCXO buffer input power supply (1.2V)                           | Supply pin     |

| 29    | V12_VCO    | VCO power supply (1.2V)                                                             | Supply pin     |

| 30    | V12_ADC    | ADC section power supply (1.2V)                                                     | Supply pin     |

| 31    | V12_MIX    | Mixer power supply (1.2V)                                                           | Supply pin     |

| 32    | TP_IF_N    | RF/IF receiver chain test negative output                                           | Analog output  |

| EP    | GND        | Ground                                                                              | Ground         |

Figure 2. Pin connection diagram (bottom view)

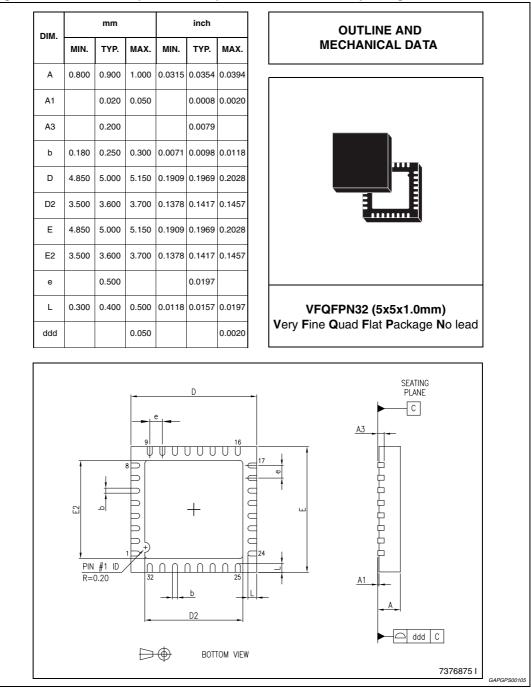

### 3 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*.

$ECOPACK^{

end{tabular}{R}}$  is an ST trademark.

Figure 3. VFQFPN32 (5x5x1.0 mm) mechanical data and package dimensions

## 4 Revision history

#### Table 3.Document revision history

| Date        | Revision | Changes                                                                                                                                               |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22-Jul-2009 | 1        | Initial release.                                                                                                                                      |

| 03-Mar-2010 | 2        | Updated: <i>Features on page 1</i> ;<br>Updated: <i>Figure 1: Block diagram on page 3</i> ;<br>Updated: <i>Section 2: Pin description on page 4</i> . |

| 27-Jun-2012 | 3        | Updated: <i>Features on page 1</i> and <i>Table 1: Device summary on page 1</i> .                                                                     |

| 17-Sep-2013 | 4        | Updated Disclaimer                                                                                                                                    |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

Doc ID 16055 Rev 4