Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Overvoltage protection device

Datasheet - production data

#### **Features**

- Input overvoltage protection up to 28 V

- Integrated high voltage N-channel MOSFET switch - low R<sub>DS(on)</sub> of 170 mΩ

- Integrated charge pump

- Maximum continuous current of 1.2 A

- Thermal shutdown

- Soft-start feature to control the inrush current

- Enable input (EN)

- Fault indication output (FLT)

- IN input ESD protection: ±15 kV air discharge, ±8 kV contact discharge (with 1 µF input capacitor), ±2 kV HBM (standalone device)

- Certain overvoltage options compliant with the China Communications Standard YD/T 1591-2006 (overvoltage protection only)

- Small, RoHS compliant 2 x 2 x 0.75 mm TDFN 8-lead package with thermal pad.

#### **Applications**

- Smart phones

- Digital cameras

- PDA and palmtop devices

- MP3 players

- Low power handheld devices.

Contents STBP110

# **Contents**

| 1    | Description                         |                                           |            |  |  |  |

|------|-------------------------------------|-------------------------------------------|------------|--|--|--|

| 2    | Pin description                     |                                           |            |  |  |  |

|      | 2.1                                 | Input (IN)                                | 7          |  |  |  |

|      | 2.2                                 | Output (OUT)                              | 7          |  |  |  |

|      | 2.3                                 | Fault indication output (FLT)             | 7          |  |  |  |

|      | 2.4                                 | Enable input (EN)                         | 7          |  |  |  |

|      | 2.5                                 | No connect (NC)                           | 8          |  |  |  |

|      | 2.6                                 | Ground (GND)                              | 8          |  |  |  |

| 3    | Operation 10                        |                                           |            |  |  |  |

|      | 3.1                                 | Power-up                                  | 10         |  |  |  |

|      | 3.2                                 | Normal operation                          | 10         |  |  |  |

|      | 3.3                                 | Undervoltage lockout (UVLO)               | 10         |  |  |  |

|      | 3.4                                 | Overvoltage lockout (OVLO)                | 10         |  |  |  |

|      | 3.5                                 | Thermal shutdown                          | 11         |  |  |  |

| 4    | Timi                                | ing diagrams                              | 12         |  |  |  |

| 5    | Typical operating characteristics14 |                                           |            |  |  |  |

|      | Typic                               | cal operating characteristics (STBP110GT) |            |  |  |  |

| 6    | Max                                 | Maximum rating                            |            |  |  |  |

| 7    | DC a                                | DC and AC parameters                      |            |  |  |  |

| 8    | Application information             |                                           |            |  |  |  |

|      | 8.1                                 | Calculating the power dissipation         | 30         |  |  |  |

|      | 8.2                                 | Calculating the junction temperature      | 30         |  |  |  |

|      | 8.3                                 | PCB layout recommendations                |            |  |  |  |

| 9    | Pack                                | Package mechanical data                   |            |  |  |  |

| 10   | Таре                                | Tape and reel information                 |            |  |  |  |

| 2/40 |                                     | Doc ID 018687 Rev 3                       | <b>47/</b> |  |  |  |

| STBP110 |                             | Contents |  |

|---------|-----------------------------|----------|--|

| 11      | Part numbering              | 37       |  |

| 12      | Package marking information | 38       |  |

| 13      | Revision history            | 39       |  |

List of tables STBP110

# List of tables

| Table 1.  | Pin description and signal names                                | 8  |

|-----------|-----------------------------------------------------------------|----|

| Table 2.  | Absolute maximum ratings                                        |    |

| Table 3.  | Thermal data                                                    | 27 |

| Table 4.  | Operating and AC measurement conditions                         | 28 |

| Table 5.  | DC and AC characteristics                                       |    |

| Table 6.  | Package mechanical dimensions for TDFN 8-lead (2 x 2 x 0.75 mm) |    |

| Table 7.  | Carrier tape dimensions                                         |    |

| Table 8.  | Further tape and reel information                               |    |

| Table 9.  | Reel dimensions                                                 |    |

| Table 10. | Ordering information scheme                                     | 37 |

| Table 11. | Marking description                                             |    |

| Table 12  | Document revision history                                       |    |

STBP110 List of figures

# **List of figures**

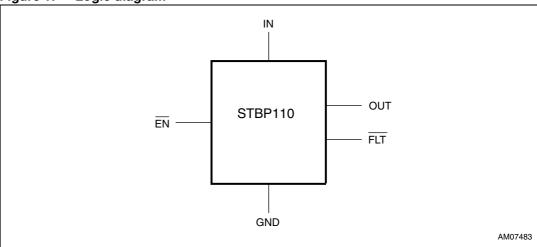

| Figure 1.  | Logic diagram                                                                                |

|------------|----------------------------------------------------------------------------------------------|

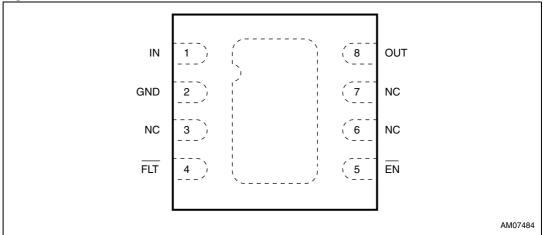

| Figure 2.  | Pinout                                                                                       |

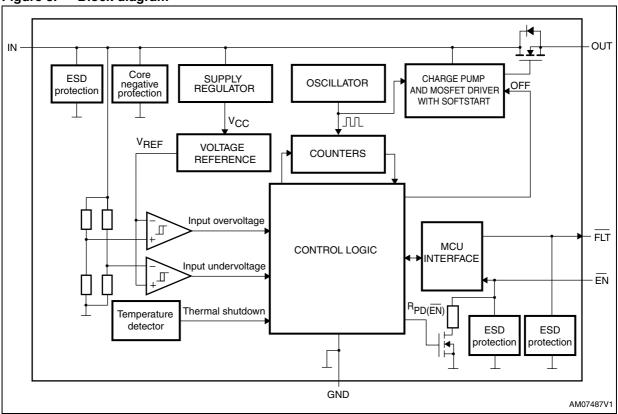

| Figure 3.  | Block diagram                                                                                |

| Figure 4.  | Typical application circuit                                                                  |

| Figure 5.  | Power-up                                                                                     |

| Figure 6.  | Overvoltage protection                                                                       |

| Figure 7.  | Disable (EN = high)                                                                          |

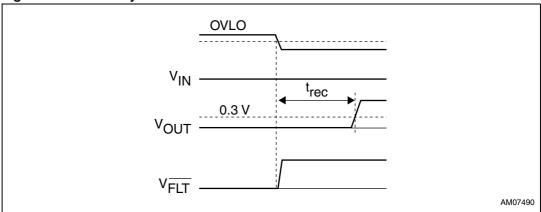

| Figure 8.  | Recovery from OVP                                                                            |

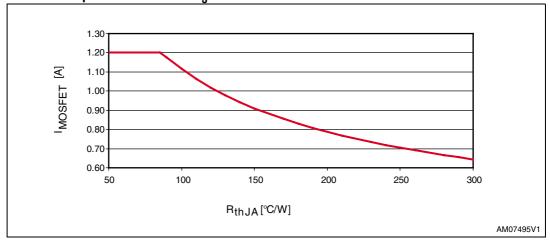

| Figure 9.  | Maximum MOSFET current at T <sub>A</sub> = 85 °C for various PCB thermal performance         |

|            | and $T_J \le 125 ^{\circ}\text{C}$                                                           |

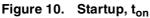

| Figure 10. | Startup, t <sub>op</sub>                                                                     |

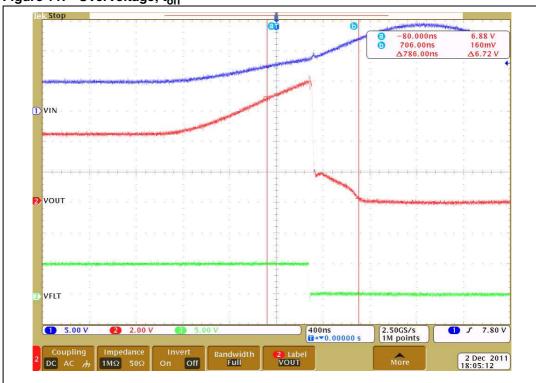

| Figure 11. | Overvoltage, t <sub>off</sub>                                                                |

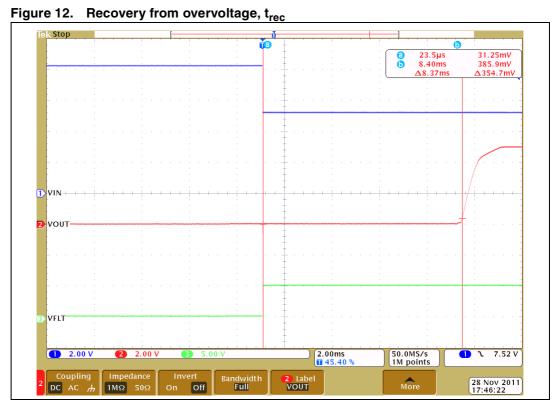

| Figure 12. | Recovery from overvoltage, t <sub>rec</sub>                                                  |

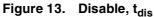

| Figure 13. | Disable, t <sub>dis</sub>                                                                    |

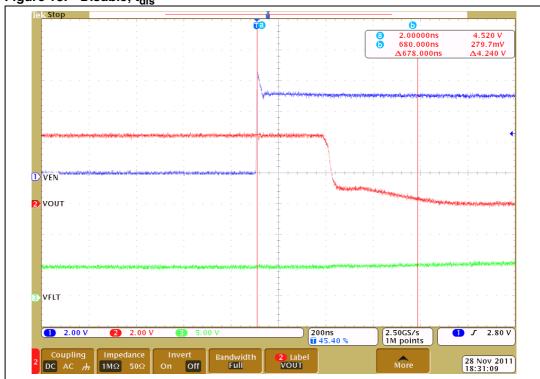

| Figure 14. | Startup to overvoltage                                                                       |

| Figure 15. | Startup to overvoltage (detail)                                                              |

| Figure 16. | Soft-start performance for 10 µF capacitive load                                             |

| Figure 17. | Soft-start performance for 100 µF capacitive load                                            |

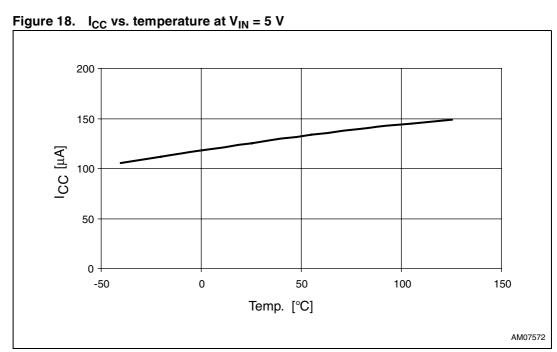

| Figure 18. | I <sub>CC</sub> vs. temperature at V <sub>IN</sub> = 5 V                                     |

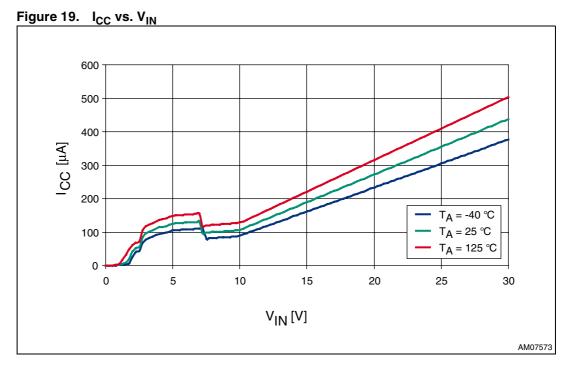

| Figure 19. | I <sub>CC</sub> vs. V <sub>IN</sub>                                                          |

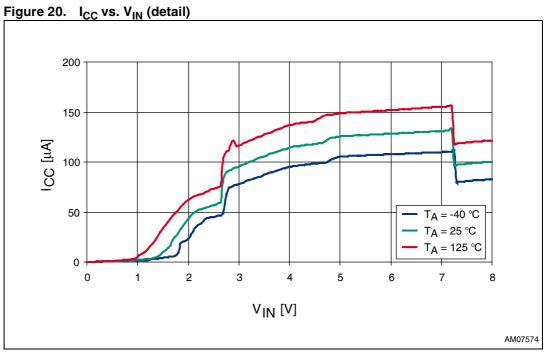

| Figure 20. | I <sub>CC</sub> vs. V <sub>IN</sub> (detail)                                                 |

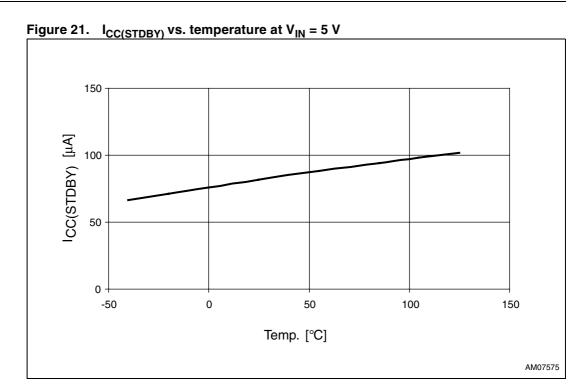

| Figure 21. | I <sub>CC(STDBY)</sub> vs. temperature at V <sub>IN</sub> = 5 V                              |

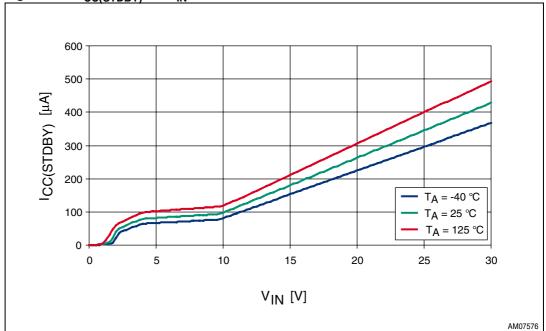

| Figure 22. | I <sub>CC(STDBY)</sub> vs. V <sub>IN</sub>                                                   |

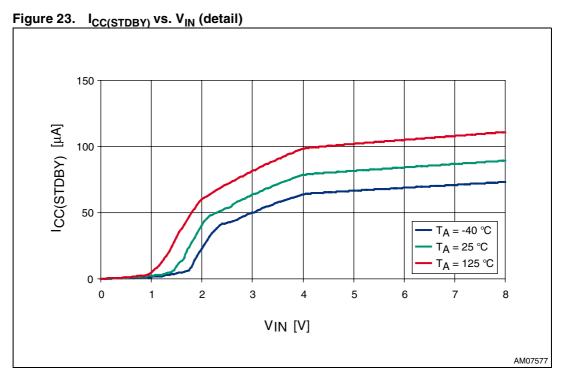

| Figure 23. | I <sub>CC(STDBY)</sub> vs. V <sub>IN</sub> (detail)                                          |

| Figure 24. | V <sub>OVI O</sub> vs. temperature                                                           |

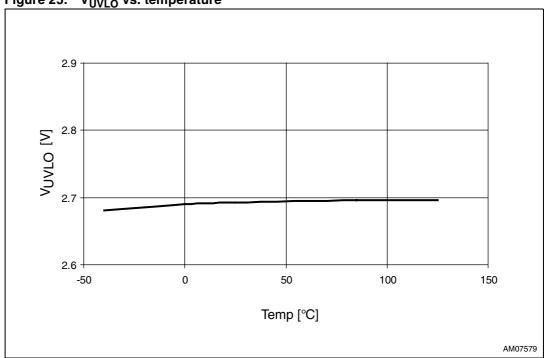

| Figure 25. | V <sub>UVLO</sub> vs. temperature                                                            |

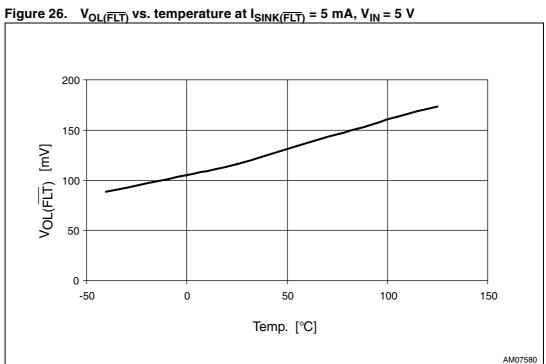

| Figure 26. | V <sub>OL(FLT)</sub> vs. temperature at I <sub>SINK(FLT)</sub> = 5 mA, V <sub>IN</sub> = 5 V |

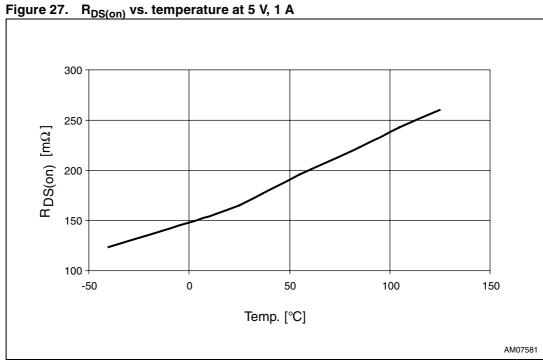

| Figure 27. | R <sub>DS(on)</sub> vs. temperature at 5 V, 1 A                                              |

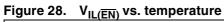

| Figure 28. | V <sub>IL(EN)</sub> vs. temperature                                                          |

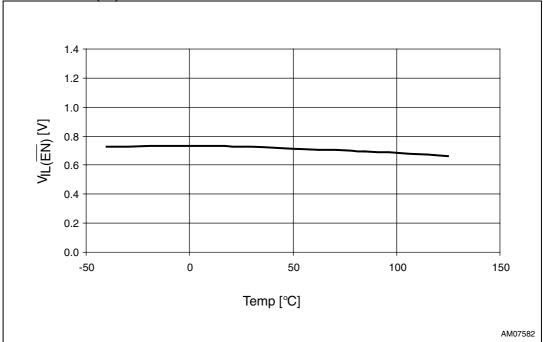

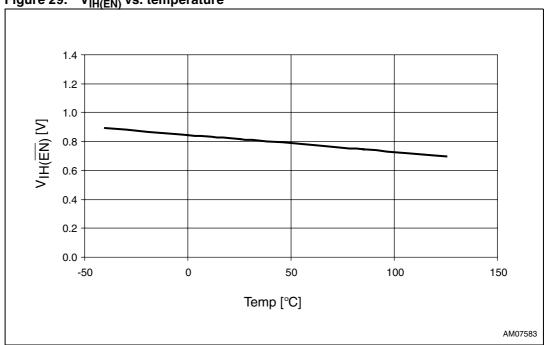

| Figure 29. | V <sub>IH(EN)</sub> vs. temperature                                                          |

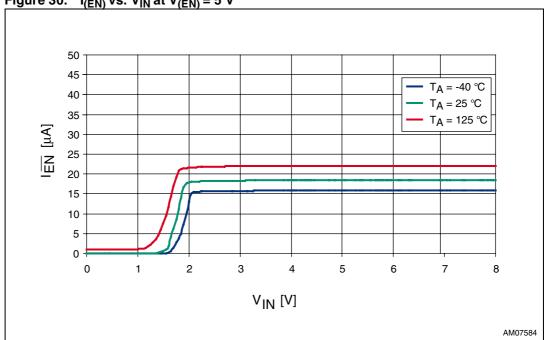

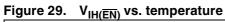

| Figure 30. | $I_{(\overline{EN})}$ vs. $V_{IN}$ at $V_{(\overline{EN})} = 5 \text{ V} \dots 24$           |

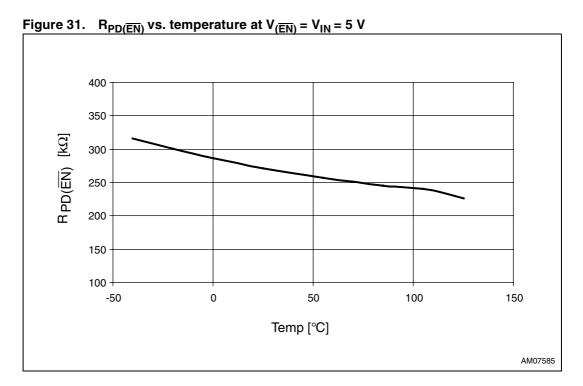

| Figure 31. | $R_{PD(\overline{EN})}$ vs. temperature at $V_{(\overline{EN})} = V_{IN} = 5 \text{ V}$      |

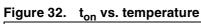

| Figure 32. | t <sub>on</sub> vs. temperature                                                              |

| Figure 33. | t <sub>rec</sub> vs. temperature                                                             |

| Figure 34. | Package mechanical drawing for TDFN 8-lead (2 x 2 x 0.75 mm)                                 |

| Figure 35. | Tape and reel                                                                                |

| Figure 36. | Reel dimensions                                                                              |

| Figure 37. | Tape trailer/leader                                                                          |

| Figure 38. | Pin 1 orientation                                                                            |

Description STBP110

### 1 Description

The STBP110 device provides overvoltage protection for input voltage up to +28 V. Its low  $R_{DS(on)}$  N-channel MOSFET switch protects the systems connected to the OUT pin against failures of the DC power supplies in accordance with the China MII Communications Standard YD/T 1591-2006.

In the event of an input overvoltage condition, the device immediately disconnects the DC power supply by turning off an internal low  $R_{DS(on)}$  N-channel MOSFET to prevent damage to protected components.

In addition, the device also monitors its own junction temperature and switches off the internal MOSFET if the junction temperature exceeds the specified limit.

The device can be controlled by the microcontroller and can also provide status information about fault conditions.

The STBP110 is offered in a small, RoHS-compliant 8-lead TDFN (2 mm x 2 mm) package.

Figure 1. Logic diagram

Figure 2. Pinout

1. Exposed thermal pad may be tied to GND.

STBP110 Pin description

### 2 Pin description

#### 2.1 Input (IN)

Input voltage (IN) pin. The IN pin is connected to the DC power supply. An external low ESR ceramic capacitor of minimum value 1  $\mu$ F must be connected between IN and GND. This capacitor is needed for decoupling and also protects the IC against fast voltage spikes and ESD events. This capacitor should be located as close to the IN pin as possible.

#### 2.2 Output (OUT)

Output voltage (OUT) pin. The OUT pin is connected to the input through a low  $R_{DS(on)}$  N-channel MOSFET switch.

If no fault is detected and the STBP110 is enabled by the  $\overline{\text{EN}}$  input, this switch is turned on and the output voltage follows the input voltage.

The output is disconnected from the input when the input voltage is under the UVLO threshold or above the OVLO threshold, when the junction temperature is above the thermal shutdown threshold or when the device is disabled by the  $\overline{\text{EN}}$  input.

After the input voltage or junction temperature returns to the specified range, there is a recovery delay, t<sub>rec</sub>, and the power output is then connected to the input (see *Figure 8*).

The switch turn-on time is intentionally prolonged to limit the inrush current and voltage drop caused, for example, by charging output capacitors (soft-start feature).

### 2.3 Fault indication output (FLT)

The active low, open-drain fault indication output provides information on the STBP110 state to the application controller. The FLT is asserted (i.e. driven low), if the STBP110 is in the overvoltage condition or thermal shutdown mode is active.

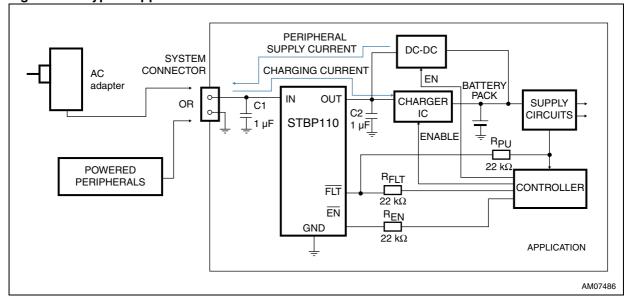

As the  $\overline{\text{FLT}}$  output is of the open-drain type, it may be pulled up by an external resistor R<sub>PU</sub> to the controller supply voltage (see *Figure 4*). If there is no need to use this output, it may be left disconnected. The suitable R<sub>PU</sub> resistor value is in the range of 10 k $\Omega$  to 1 M $\Omega$ .

To improve safety and to prevent damage to application circuits in the event of extreme voltage or current conditions, an optional protective resistor  $R_{FLT}$  can be connected between the  $\overline{FLT}$  output and the controller input (see *Figure 4*). The suitable  $R_{FLT}$  resistor value is in the range of 10 k $\Omega$ to 100 k $\Omega$ .

The  $\overline{\text{FLT}}$  output is in Hi-Z (high impedance) state when the device is disabled by  $\overline{\text{EN}}$  input or when the input voltage is lower than the UVLO threshold.

### 2.4 Enable input (EN)

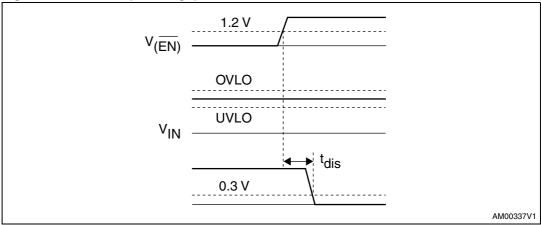

This active low logical input can be used to enable or disable the device. When the  $\overline{\text{EN}}$  input is driven high, the STBP110 is in shutdown mode and the power output is disconnected from the input (see *Figure 8*). When the  $\overline{\text{EN}}$  input is driven low and all operating conditions are within specified limits, the power output is connected to the input.

Pin description STBP110

The  $\overline{\text{EN}}$  input is equipped with an internal pull-down resistor of 250 k $\Omega$  (typical value). If there is no need to use this input, it may be left floating or, preferably, connected to GND.

For  $V_{IN}$  lower than 2.5 V (max.), the pull-down resistor is internally disconnected to lower the  $\overline{EN}$  pin input current in case the external AC adapter is not connected, the application is running from an internal battery and the STBP110 device is disabled.

To improve safety and to prevent damage to application circuits in the event of extreme voltage or current conditions, an optional protective resistor  $R_{EN}$  can be connected between the  $\overline{EN}$  input and the controller output (see *Figure 4*). The protective resistor forms a voltage divider with the internal pull-down resistor, which limits the maximum possible  $R_{EN}$  value with respect to the  $V_{IH(\overline{EN})}$  threshold of  $\overline{EN}$  input and the controller's output voltage for logic high,  $V_{OH}$ . For the worst case, the highest protective resistor value is

$R_{ENmax} = R_{PD(\overline{EN})min} \times (V_{OH} / V_{IH(\overline{EN})} - 1),$

where  $R_{PD(\overline{EN})min}$  is 100 k $\Omega$  and  $V_{IH(\overline{EN})}$  is 1.2 V.

For most cases, an R<sub>EN</sub> value of 10 k $\Omega$  to 100 k $\Omega$  is adequate.

The FLT output is in Hi-Z state when the device is disabled by EN input.

#### 2.5 No connect (NC)

Pin 3, 6, and 7 are no connect (NC). They may be left floating or connected to GND.

#### 2.6 Ground (GND)

Ground terminal. All voltages are referenced to GND. The exposed thermal pad is internally connected to GND.

| Table 1. I'm description and signal names |      |              |                                          |  |  |  |

|-------------------------------------------|------|--------------|------------------------------------------|--|--|--|

| Pin                                       | Name | Туре         | Function                                 |  |  |  |

| 1                                         | IN   | Input/supply | Input voltage                            |  |  |  |

| 2                                         | GND  | Supply       | Ground                                   |  |  |  |

| 3, 6, 7                                   | NC   | -            | Not connected                            |  |  |  |

| 4                                         | FLT  | Output       | Fault indication output (open-drain)     |  |  |  |

| 5                                         | EN   | Input        | Enable input (pull-down resistor to GND) |  |  |  |

| 8                                         | OUT  | Output       | Output voltage                           |  |  |  |

Table 1. Pin description and signal names

STBP110 Pin description

Figure 3. Block diagram

Figure 4. Typical application circuit

- Optional resistors R<sub>EN</sub> and R<sub>ELT</sub> prevent damage to the controller under extreme voltage or current conditions and are not required. Low ESR ceramic capacitor C1 is necessary to ensure proper function of the STBP110. Capacitor C2 is not necessary for STBP110 but may be required by the charger IC.

- 2. The STBP110 MOSFET switch topology allows the current to flow also in a reverse direction, i.e. from OUT to IN, which can be useful for powering external peripherals from the system connector. If the reverse current (supply current) is undesirable, it may be prevented by connecting an external Schottky diode in series with the OUT pin. The voltage drop between IN and the charger is then increased by the voltage drop across the diode.

Operation STBP110

### 3 Operation

The STBP110 provides overvoltage protection for positive input voltage up to 28 V using a built-in low  $R_{DS(on)}$  N-channel MOSFET switch.

#### 3.1 Power-up

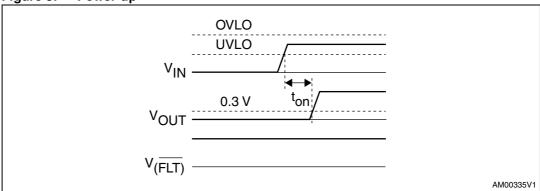

At power-up, with  $\overline{\text{EN}}$  = low, the MOSFET switch is turned on after the startup delay,  $t_{\text{on}}$ , after the input voltage exceeds the UVLO threshold to ensure the input voltage is stabilized (see *Figure 5*).

#### 3.2 Normal operation

The device continuously monitors the input voltage and its own internal temperature so the output voltage is kept within the specified range. The internal MOSFET switch is turned on and the  $\overline{\text{FLT}}$  output is deasserted.

The STBP110 enters normal operation state if the input voltage returns to the interval between  $V_{UVLO}$  and  $V_{OVLO}$  -  $V_{HYS(OVLO)}$  and the junction temperature falls below  $T_{off}$  -  $T_{HYS(off)}$ . The internal MOSFET is turned on after the  $t_{rec}$  delay to ensure that the conditions have stabilized and the  $\overline{FLT}$  output is deasserted.

Note:

The STBP110 MOSFET switch topology allows the current to flow also in a reverse direction, i.e. from OUT to IN, which can be useful for powering external peripherals from the system connector (see the supply current in Figure 4). At first, the current flows through the MOSFET body diode. If the voltage that appears on the IN terminal is above the UVLO threshold, the MOSFET is (after the startup delay) turned on so the voltage drop across STBP110 is significantly reduced.

If the reverse current is undesirable, it may be prevented by connecting an external, properly rated low drop Schottky diode in series with the OUT pin. The voltage drop between IN and charger is increased by the voltage drop across the diode.

### 3.3 Undervoltage lockout (UVLO)

To ensure proper operation under any condition, the STBP110 has an undervoltage lockout (UVLO) threshold. When the input voltage is rising, the output remains disconnected from input until the  $V_{IN}$  voltage exceeds the  $V_{UVLO}$  threshold. This circuit is equipped with hysteresis,  $V_{HYS(UVLO)}$ , to improve noise immunity under transient conditions.

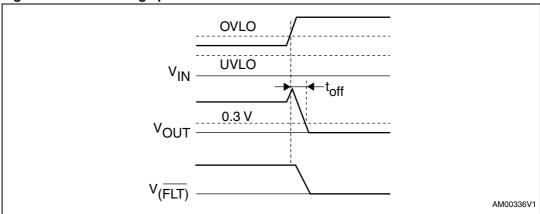

### 3.4 Overvoltage lockout (OVLO)

If the input voltage  $V_{IN}$  rises above the threshold level  $V_{OVLO}$ , the MOSFET switch is immediately turned off. At the same time, the fault indication output  $\overline{FLT}$  is activated (i.e. driven low), see *Figure 6*. This device is equipped with hysteresis,  $V_{HYS(OVLO)}$ , to improve noise immunity under transient conditions.

STBP110 Operation

#### 3.5 Thermal shutdown

If the STBP110 internal junction temperature exceeds the  $T_{\underline{off}}$  threshold, the internal MOSFET switch is turned off and the fault indication output  $\overline{FLT}$  is driven low.

To improve thermal robustness, this circuit has a 20 °C hysteresis, T<sub>HYS(off)</sub>.

Due to the internal reverse diode, the thermal shutdown is not functional for the reverse current.

Timing diagrams STBP110

# 4 Timing diagrams

Figure 5. Power-up

1.  $\overline{\mathsf{EN}}$  input is low.

Figure 6. Overvoltage protection

1. EN input is low.

Figure 7. Disable ( $\overline{EN} = high$ )

1.  $\overline{\text{FLT}}$  output is in Hi-Z state when  $\overline{\text{EN}}$  driven high.

STBP110 Timing diagrams

Figure 8. Recovery from OVP

1. EN input is low.

# 5 Typical operating characteristics

Figure 9. Maximum MOSFET current at  $T_A$  = 85 °C for various PCB thermal performance and  $T_J \le$  125 °C

## Typical operating characteristics (STBP110GT)

1. Output load is 100  $k\Omega$ .

Figure 11. Overvoltage, toff

1. Output load is 5  $\Omega$ .

1. Output load is 5  $\Omega$ .

1. Output load is 5  $\Omega$ .

Figure 14. Startup to overvoltage

1. Output load is 5  $\Omega$ .

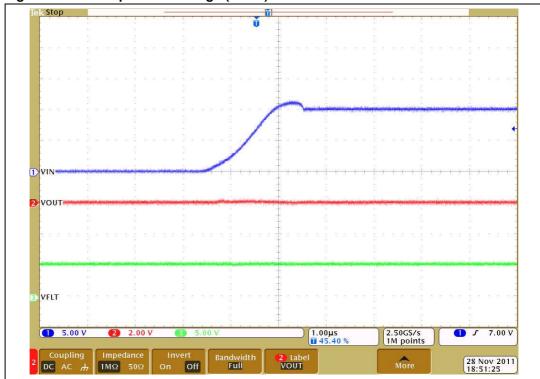

Figure 15. Startup to overvoltage (detail)

1. Output load is 5  $\Omega.$  Almost no glitch on the output.

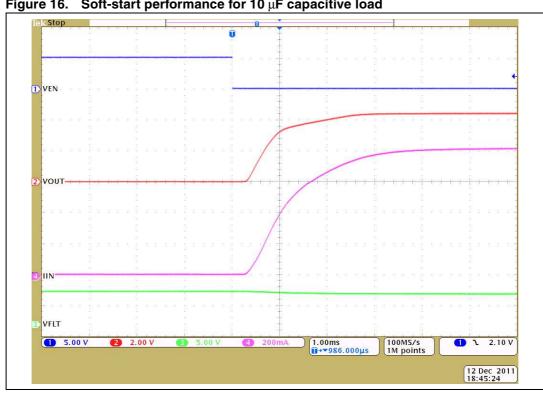

Figure 16. Soft-start performance for 10  $\mu$ F capacitive load

1. Output load is 10  $\mu F$  in parallel with 5  $\Omega.$

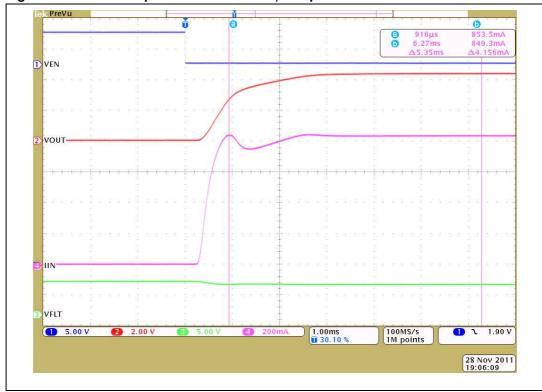

Figure 17. Soft-start performance for 100  $\mu\text{F}$  capacitive load

1. Output load is 100  $\mu F$  in parallel with 5  $\Omega.$

Figure 24.  $V_{OVLO}$  vs. temperature 7.3 VOVLO [V] 7.0 50 100 -50 150 Temp [°C] AM07578

Figure 25.  $V_{UVLO}$  vs. temperature

Figure 30.  $I_{(\overline{EN})}$  vs.  $V_{IN}$  at  $V_{(\overline{EN})} = 5$  V