Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STCD22x0, STCD23x0, STCD24x0

#### Multichannel clock distribution circuit

#### **Features**

- 2, 3 or 4 output buffered clock distribution

- Single-ended square wave (or sine wave) clock input

- Rail-to-rail (0 V to VTCXO) square wave output

- Individual enable pin for each output

- 1.8 V, high PSRR LDO for external clock source voltage supply (VTCXO)

- No AC coupling capacitor needed

- Ultra-low phase noise and standby current

- Common system clock request, open drain, active low

- Clock enable signal polarities factory programmable (STCD23x0)

- Option pins allow clock enable polarities to be user configurable (STCD22x0 and STCD24x0)

- High isolation output-to-output & output-to-input

- 2.5 V to 5.1 V battery supply voltage

- 40 pF max load driving capability per output

- Available in chip scale package (CSP)

- Operating temperature : –20 °C to 85 °C

### **Applications**

- Multimode RF clock reference

- Baseband peripheral device clock reference

- Mobile Internet Devices (MIDs)

| Table | 1. | Device | summary |

|-------|----|--------|---------|

|-------|----|--------|---------|

| Reference | Part number                      | Channels Enable polarity |                 | Package                                |  |

|-----------|----------------------------------|--------------------------|-----------------|----------------------------------------|--|

| STCD22x0  | STCD22x0 STCD2200 <sup>(1)</sup> |                          |                 | Flip Chip 12-bump<br>(1.2 mm x 1.6 mm) |  |

| STCD24x0  | STCD2400                         | 4-channel                | User program    | Flip Chip 16-bump                      |  |

|           | STCD2410 <sup>(1)</sup>          | 4-chamiei                |                 | (1.6 mm x 1.6 mm)                      |  |

| STCD23x0  | STCD2300 <sup>(1)</sup>          |                          | Factory program | Flip Chip 12-bump<br>(1.2 mm x 1.6 mm) |  |

|           | STCD2310 <sup>(1)</sup>          | 3-channel                |                 |                                        |  |

|           | STCD2320 <sup>(1)</sup>          | 3-criamiei               |                 |                                        |  |

|           | STCD2330 <sup>(1)</sup>          |                          |                 |                                        |  |

<sup>1.</sup> Contact local ST sales office for availability.

## **Contents**

| 1  | Desc | Description                     |  |  |  |  |  |

|----|------|---------------------------------|--|--|--|--|--|

| 2  | Devi | ce overview 6                   |  |  |  |  |  |

| 3  | Devi | ce operation 12                 |  |  |  |  |  |

|    | 3.1  | Operation                       |  |  |  |  |  |

|    | 3.2  | Enable polarity                 |  |  |  |  |  |

| 4  | App  | lication information            |  |  |  |  |  |

|    | 4.1  | LDO input capacitor             |  |  |  |  |  |

|    | 4.2  | LDO output capacitor            |  |  |  |  |  |

|    | 4.3  | LDO BYP pin                     |  |  |  |  |  |

|    | 4.4  | MC <sub>REQ</sub> pin           |  |  |  |  |  |

|    | 4.5  | Phase noise                     |  |  |  |  |  |

|    | 4.6  | Jitter 16                       |  |  |  |  |  |

|    | 4.7  | Output trace line               |  |  |  |  |  |

|    | 4.8  | Typical application connections |  |  |  |  |  |

| 5  | Турі | cal operating characteristics19 |  |  |  |  |  |

| 6  | Maxi | imum ratings                    |  |  |  |  |  |

| 7  | DC a | and AC parameters               |  |  |  |  |  |

| 8  | Pack | kage mechanical data            |  |  |  |  |  |

| 9  | Part | numbering                       |  |  |  |  |  |

| 10 | Revi | sion history                    |  |  |  |  |  |

# List of tables

| Table 1.  | Device summary                                                                            | 1    |

|-----------|-------------------------------------------------------------------------------------------|------|

| Table 2.  | Pin functions (STCD22x0, 2-channel)                                                       | . 10 |

| Table 3.  | Pin functions (STCD23x0, 3-channel)                                                       | . 10 |

| Table 4.  | Pin functions (STCD24x0, 4-channel)                                                       | . 11 |

| Table 5.  | Truth table for clock enable (EN1-4), master clock request (MC <sub>REO</sub> ) and VTCXO | . 12 |

| Table 6.  | Truth table for enable signals (EN1-4), master clock input (MCLK) and output              |      |

|           | clocks (CLK1-4)                                                                           | . 13 |

| Table 7.  | STCD22x0, STCD23x0 and STCD24x0 and enable polarity options                               | . 13 |

| Table 8.  | Absolute maximum ratings                                                                  | . 27 |

| Table 9.  | Operating and AC measurement conditions                                                   | . 28 |

| Table 10. | DC and AC characteristics                                                                 | . 28 |

| Table 11. | Flip Chip 12-bump, package mechanical data                                                |      |

| Table 12. | Flip Chip 16-bump, package mechanical data                                                | . 34 |

| Table 13. | Ordering information scheme                                                               |      |

| Table 14. | Document revision history                                                                 | . 38 |

577

# List of figures

| Figure 1.  | Logic diagram                                                                                     | . 6 |

|------------|---------------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Block diagram                                                                                     | . 7 |

| Figure 3.  | Hardware hookup (master clock enable active low)                                                  | . 7 |

| Figure 4.  | Hardware hookup (master clock enable active high)                                                 | . 8 |

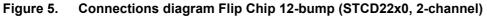

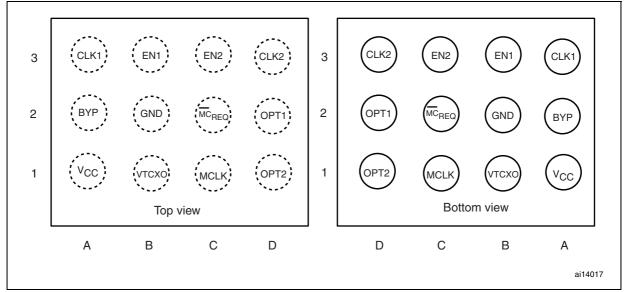

| Figure 5.  | Connections diagram Flip Chip 12-bump (STCD22x0, 2-channel)                                       |     |

| Figure 6.  | Connections diagram Flip Chip 12-bump (STCD23x0, 3-channel)                                       | . 9 |

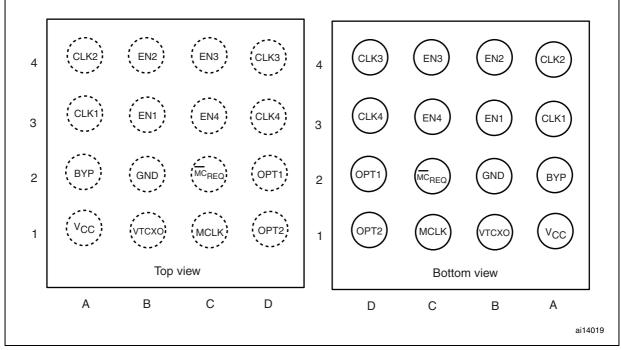

| Figure 7.  | Connections diagram Flip Chip 16-bump (STCD24x0, 4-channel)                                       | . 9 |

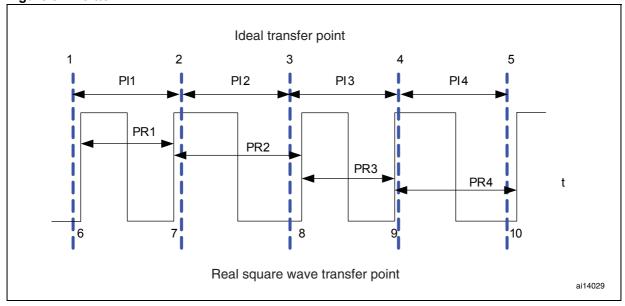

| Figure 8.  | Jitter                                                                                            | 16  |

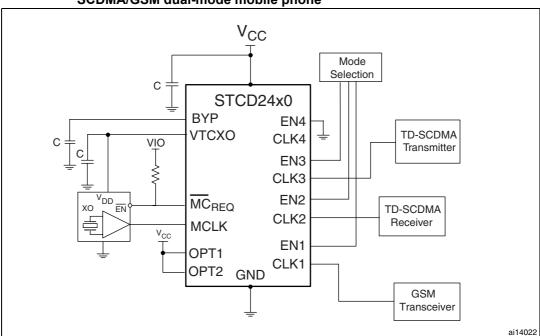

| Figure 9.  | Typical application circuit using STCD24x0 for RF ends of TD-SCDMA/GSM dual-mode                  |     |

| J          | mobile phone                                                                                      | 17  |

| Figure 10. | Typical application circuit using STCD24x0 for baseband peripherals in mobile phone               | 18  |

| Figure 11. | Quiescent current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 1,                                  |     |

|            | no master clock input)                                                                            | 19  |

| Figure 12. | Quiescent current vs. temperature (EN1 = EN2 = EN3 = EN4 = 1,                                     |     |

| _          | C <sub>load</sub> = 20 pF, no master clock input)                                                 | 19  |

| Figure 13. | Active current vs. temperature (EN1 = EN2 = EN3 = EN4 = 1, C <sub>load</sub> = 20 pF,             |     |

| _          | V <sub>CC</sub> = 3.8 V, f <sub>MCLK</sub> = 26 MHz)                                              | 20  |

| Figure 14. | Standby current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 0, no master clock input)             | 20  |

| Figure 15. | Active current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 1, f <sub>MCLK</sub> = 26 MHz,         |     |

|            | C <sub>load</sub> = 20 pF)                                                                        | 21  |

| Figure 16. | Active current vs. master clock input voltage level (EN1 = EN2 = EN3 = EN4 = 1,                   |     |

|            | f <sub>MCLK</sub> = 26 MHz, C <sub>load</sub> = 20 pF)                                            | 21  |

| Figure 17. | Active current vs. master clock frequency (EN1 = EN2 = EN3 = EN4 = 1, C <sub>load</sub> = 20 pF). | 21  |

| Figure 18. | STCD2400 recovery time from standby to active (VTCXO is on)                                       | 22  |

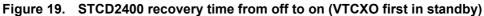

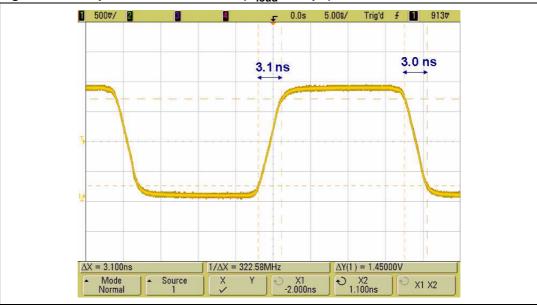

| Figure 19. | STCD2400 recovery time from off to on (VTCXO first in standby)                                    | 22  |

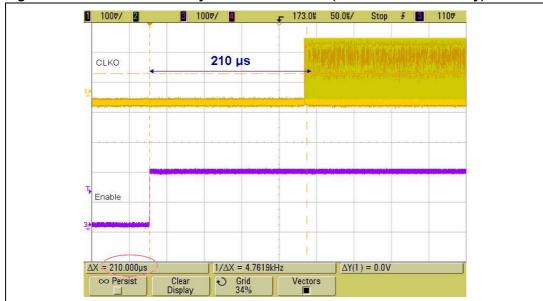

| Figure 20. | Output clock rise/fall time (C <sub>load</sub> = 40 pF)                                           | 23  |

| Figure 21. | STCD2400 power-up sequence                                                                        | 24  |

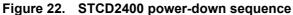

| Figure 22. | STCD2400 power-down sequence                                                                      | 24  |

| Figure 23. | Phase noise input (from the clock source, 26 MHz square wave XO KC2520C26 from                    |     |

|            | Kyocera)                                                                                          |     |

| Figure 24. | Phase noise output (include the clock source and STCD2400 additive phase noise)                   | 26  |

| Figure 25. | Flip Chip 12-bump, package mechanical outline                                                     | 31  |

| Figure 26. | Flip Chip 16-bump, package mechanical outline                                                     | 33  |

| Figure 27. | Flip Chip 12-bump tape and reel specifications                                                    | 35  |

| Figure 28  | Flip Chip 16-hump tane and real specifications                                                    | 36  |

## 1 Description

The STCD22x0, STCD23x0 and STCD24x0 are 2, 3 or 4 output clock distribution circuits which accept external square wave or sine wave signals and output rail-to-rail (0 V to VTCXO) square wave signals. They are used to provide a common frequency clock to multimode mobile RF applications. They can also be used for those baseband peripheral applications in mobile phones such as WLAN, Bluetooth, GPS and DVB-H as the clock reference. The STCD22x0, STCD23x0 and STCD24x0 isolate each device driven by their clock outputs and minimize interference between the devices. Each of the clock buffers can be disabled to lower the power consumption whenever the connected device does not need the clock. The STCD22x0, STCD23x0 and STCD24x0 accept commonly used mobile master clock frequencies ranging from 10 MHz to 52 MHz.

The STCD22x0, STCD23x0 and STCD24x0 have a common clock request (open drain output, active low) controlling the external clock source. A 1.8 V, high PSRR LDO is also integrated in the STCD22x0, STCD23x0 and STCD24x0 to supply power to the external clock source (for example, TCXO). STMicroelectronics offers different versions for the enable polarities. The STCD22x0, STCD23x0 and STCD24x0 are available in, respectively, 1.2 mm x 1.6 mm (12-bump), 1.2 mm x 1.6 mm (16-bump) chip scale packages and can be operated with a battery supply voltage ranging from 2.5 V to 5.1 V. The operating temperature is -20 to +85 °C.

## 2 Device overview

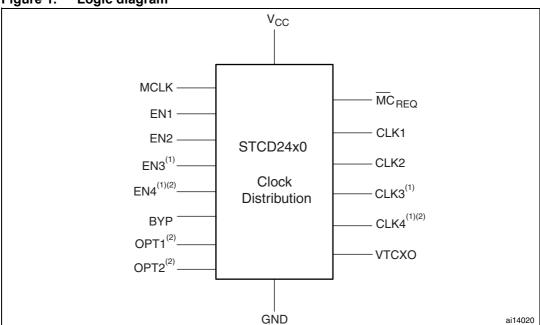

Figure 1. Logic diagram

- 1. EN3, CLK3, EN4, and CLK4 do not exist for STCD22x0.

- 2. OPT1, OPT2, EN4, and CLK4 do not exist for STCD23x0.

$V_{CC}$ STCD24x0 EN4 VTCXO  $V_{CC}$ CLK4 Bandgap BYP -EN3 VTCXO LDO VTCXO <del>◄</del> CLK3 EN2 VTCXO  $\overline{\mathsf{MC}}_{\mathsf{REQ}}$ CLK2 OPT1 OPT2 EN1 ттсхо MCLK -CLK1 **GND** ai14021

Figure 2. Block diagram

Note:

Enable signals (EN1-4) can be factory programmed either active high or active low for STCD23x0 and can have different polarity options by configuring OPT1 and OPT2 for STCD22x0 and STCD24x0. Master clock request ( $\overline{MC}_{REQ}$ ) is open drain output and active low.

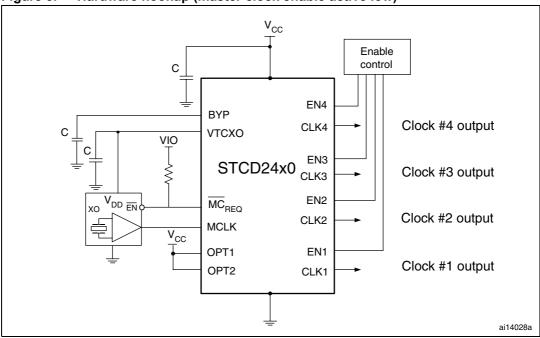

Figure 3. Hardware hookup (master clock enable active low)

ai14028h

Enable control С EN4 BYP Clock #4 output CLK4 VTCXO С EN3 STCD24x0 Clock #3 output CLK3 EN2  $V_{DD EN}$  $\overline{\rm MC}_{\rm REQ}$ Clock #2 output CLK2 MCLK  $V_{CC}$ OPT1 EN1 Clock #1 output OPT2 CLK1

Figure 4. Hardware hookup (master clock enable active high)

Note: OPT1 is used to configure EN1 polarity. Connect OPT1 to  $V_{CC}$  to configure EN1 active high or connect OPT1 to GND to configure EN1 active low. In the same way OPT2 is used to configure EN2.

CLK2 CLK1 3 3 2 2 BYP VCC 1 1 Bottom view Top view Α В С D D С В Α ai14018

Figure 6. Connections diagram Flip Chip 12-bump (STCD23x0, 3-channel)

Note:

EN1~EN3 can be active high or active low. STMicroelectronics offers several polarity options, refer to Section 3.2: Enable polarity for detailed information.

Figure 7. Connections diagram Flip Chip 16-bump (STCD24x0, 4-channel)

Note:

OPT1 is used to configure EN1 and EN2 polarity. Connect OPT1 to  $V_{\rm CC}$  to configure EN1 and EN2 active high or connect OPT1 to GND to configure EN1 and EN2 active low. In the same way OPT2 is used to configure EN3 and EN4. STMicroelectronics offers different control options, refer to Section 3.2: Enable polarity for detailed information.

Table 2. Pin functions (STCD22x0, 2-channel)

| Pin<br>number | Pin<br>name       | Description                                                                                                                                                           |

|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1            | V <sub>CC</sub>   | Supply voltage (decouple with a 1 μF capacitor to GND)                                                                                                                |

| B1            | VTCXO             | LDO output for external clock source (decouple with a 1 µF capacitor to GND)                                                                                          |

| C1            | MCLK              | Master clock input                                                                                                                                                    |

| D1            | OPT2              | Optional pin 2. Connect to V <sub>CC</sub> or GND on PC board to field configure EN2 active high/low. Refer to Section 3.2: Enable polarity for detailed information. |

| A2            | BYP               | Bypass capacitor input pin (10 nF capacitor should be connected to GND in order to improve thermal noise performance)                                                 |

| B2            | GND               | Supply ground                                                                                                                                                         |

| C2            | MC <sub>REQ</sub> | Master clock request signal (open drain, active low)                                                                                                                  |

| D2            | OPT1              | Optional pin 1. Connect to $V_{CC}$ or GND on PC board to field configure EN1 active high/low. Refer to Section 3.2: Enable polarity for detailed information.        |

| A3            | CLK1              | Clock output channel - output 1                                                                                                                                       |

| В3            | EN1               | Clock output channel enable-1 (active high/low OPT1 field programmable)                                                                                               |

| С3            | EN2               | Clock output channel enable-2 (active high/low OPT2 field programmable)                                                                                               |

| D3            | CLK2              | Clock output channel - output 2                                                                                                                                       |

Table 3. Pin functions (STCD23x0, 3-channel)

| Pin<br>number | Pin<br>name                         | Description                                                                                                           |

|---------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| A1            | $V_{CC}$                            | Supply voltage (decouple with a 1 μF capacitor to GND)                                                                |

| B1            | VTCXO                               | LDO output for external clock source (decouple with a 1 µF capacitor to GND)                                          |

| C1            | MCLK                                | Master clock input                                                                                                    |

| D1            | EN3                                 | Clock output channel enable-3 (active high/low factory laser programmable)                                            |

| A2            | BYP                                 | Bypass capacitor input pin (10 nF capacitor should be connected to GND in order to improve thermal noise performance) |

| B2            | GND                                 | Supply ground                                                                                                         |

| C2            | $\overline{\text{MC}}_{\text{REQ}}$ | Master clock request signal (open drain, active low)                                                                  |

| D2            | CLK3                                | Clock output channel - output 3                                                                                       |

| A3            | CLK1                                | Clock output channel - output 1                                                                                       |

| В3            | EN1                                 | Clock output channel enable-1 (active high/low factory laser programmable)                                            |

| С3            | EN2                                 | Clock output channel enable-2 (active high/low factory laser programmable)                                            |

| D3            | CLK2                                | Clock output channel - output 2                                                                                       |

Table 4. Pin functions (STCD24x0, 4-channel)

|               | 1 in functions (510D24x0, 4-chainer) |                                                                                                                                                                        |  |  |  |

|---------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>number | Pin<br>name                          | Description                                                                                                                                                            |  |  |  |

| A1            | V <sub>CC</sub>                      | Supply voltage (decouple with a 1 μF capacitor to GND)                                                                                                                 |  |  |  |

| B1            | VTCXO                                | LDO output for external clock source (decouple with a 1 µF capacitor to GND)                                                                                           |  |  |  |

| C1            | MCLK                                 | Master clock input                                                                                                                                                     |  |  |  |

| D1            | OPT2                                 | Optional pin 2. Connect to $V_{CC}$ or GND on PC board to field configure EN3 and EN4 active high/low. Refer to Section 3.2: Enable polarity for detailed information. |  |  |  |

| A2            | BYP                                  | Bypass capacitor input pin (10 nF capacitor should be connected to GND in order to improve thermal noise performance)                                                  |  |  |  |

| B2            | GND                                  | Supply ground                                                                                                                                                          |  |  |  |

| C2            | $\overline{\text{MC}}_{\text{REQ}}$  | Master clock request signal (open drain, active low)                                                                                                                   |  |  |  |

| D2            | OPT1                                 | Optional pin 1. Connect to $V_{CC}$ or GND on PC board to field configure EN1 and EN2 active high/low. Refer to Section 3.2: Enable polarity for detailed information. |  |  |  |

| A3            | CLK1                                 | Clock output channel - output 1                                                                                                                                        |  |  |  |

| В3            | EN1                                  | Clock output channel enable-1 (active high/low OPT1 field programmable)                                                                                                |  |  |  |

| C3            | EN4                                  | Clock output channel enable-4 (active high/low OPT2 field programmable)                                                                                                |  |  |  |

| D3            | CLK4                                 | Clock output channel - output 4                                                                                                                                        |  |  |  |

| A4            | CLK2                                 | Clock output channel - output 2                                                                                                                                        |  |  |  |

| B4            | EN2                                  | Clock output channel enable-2 (active high/low OPT1 field programmable)                                                                                                |  |  |  |

| C4            | EN3                                  | Clock output channel enable-3 (active high/low OPT2 field programmable)                                                                                                |  |  |  |

| D4            | CLK3                                 | Clock output channel - output 3                                                                                                                                        |  |  |  |

### 3 Device operation

#### 3.1 Operation

The STCD22x0, STCD23x0 and STCD24x0 are 2, 3 or 4 buffered clock distribution circuits. They accept the clock (either square wave or sine wave) input from an external clock source and send 2, 3 or 4 buffered rail-to-rail (0 V to VTCXO) square wave outputs to different devices. A 1.8 V, high PSRR LDO (VTCXO) is also integrated in the STCD22x0, STCD23x0 and STCD24x0 which can be used as a voltage supply for the external master clock source (such as a TCXO). This LDO stops the current increase through PMOS when the load current reaches the limit value of the current-limit protection circuit. When the load current falls below the limit values, the current limit is released.

Each of the STCD22x0, STCD23x0 and STCD24x0 clock outputs can be enabled individually. If the device connected to the output is in standby, and does not require a clock, the buffered output can be disabled to save power consumption. Once the buffered output is disabled, it is pulled down to GND internally. If all the devices connected are in standby, the STCD22x0, STCD23x0 and STCD24x0 are also put into standby mode (the internal LDO is also shut down) for further power consumption savings. All of the output enable signals are logic ORed with an open drain output ( $\overline{\text{MC}}_{\text{REQ}}$ ) to control the output of the source clock. If the output clock is required by at least one device, the LDO wakes up and the  $\overline{\text{MC}}_{\text{REQ}}$  activates the clock source. The truth table for enable signals, the master clock request signal and the VTCXO is given in *Table 5*. The truth table for enable signals, output clock signals and the master clock is given in *Table 6*.

The STCD22x0, STCD23x0 and STCD24x0 have the master clock input detector integrated. If the input master clock peak-to-peak voltage is below the minimum specified level, even if the outputs are enabled, there are no clock outputs and STCD22x0, STCD23x0 and STCD24x0 enter standby mode. Once the master clock peak-to-peak voltage level reaches the minimum value, the output clocks are asserted if the enable pins are active.

In *Table 5* and 6, the enable signals are active high and the  $\overline{\text{MC}}_{\text{REQ}}$  is active low. These enable signals can be active high or active low. The enable polarity is described in *Section 3.2: Enable polarity*. Customers can select different polarity options for different applications. Contact the STMicroelectronics local sales office for availability.

| Table 5. | Truth table for clock enable (EN1-4), master clock request (MC <sub>REQ</sub> ) and |

|----------|-------------------------------------------------------------------------------------|

|          | VTCXO                                                                               |

| EN1 | EN2 | EN3 | EN4 | MC <sub>REQ</sub> | VTCXO |

|-----|-----|-----|-----|-------------------|-------|

| 0   | 0   | 0   | 0   | 1                 | GND   |

| 1   | 0   | 0   | 0   | 0                 | 1.8 V |

| 1   | 1   | 0   | 0   | 0                 | 1.8 V |

| -   | -   | -   | -   | 0                 | 1.8 V |

| 1   | 1   | 1   | 1   | 0                 | 1.8 V |

Note:

"0" means logic low which disables the clock output and "1" means logic high which enables the clock output. This is an active high truth table. Refer to Section 3.2: Enable polarity for the detailed enable active high/low options.

Table 6. Truth table for enable signals (EN1-4), master clock input (MCLK) and output clocks (CLK1-4)

| EN1 | EN2 | EN3 | EN4 | MCLK  | CLK1     | CLK2     | CLK3     | CLK4     |

|-----|-----|-----|-----|-------|----------|----------|----------|----------|

| 0   | 0   | 0   | 0   | Х     | NO CLOCK | NO CLOCK | NO CLOCK | NO CLOCK |

| 1   | 0   | 0   | 0   | CLOCK | CLOCK    | NO CLOCK | NO CLOCK | NO CLOCK |

| 1   | 1   | 0   | 0   | CLOCK | CLOCK    | CLOCK    | NO CLOCK | NO CLOCK |

| -   | -   | -   | -   | -     | -        | -        | -        | -        |

| 1   | 1   | 1   | 1   | CLOCK | CLOCK    | CLOCK    | CLOCK    | CLOCK    |

Note:

"0" means logic low and "1" means logic high. When there is NO CLOCK output, the CLKx pin stays at logic low. "X" means don't care. This is an active high truth table. Refer to Section 3.2: Enable polarity for the detailed enable active high/low options.

### 3.2 Enable polarity

In different applications, the user may have different requirements for enable active high or active low (enable polarities).  $\overline{\text{MC}}_{\text{REQ}}$  is active low. STMicroelectronics offers different solutions for the user to obtain different enable polarities.

In the STCD22x0 and STCD24x0, the user can configure the enable active high or active low on the PC board by connecting OPT1 and OPT2 to either  $V_{CC}$  or ground. Refer to *Table 7* for detailed information.

In the STCD23x0, STMicroelectronics offers 4 enable polarity options by factory programming for the user. Refer to *Table 7* for detailed information.

The user should note that OPT1 and OPT2 must be connected to either  $V_{CC}$  or GND on the PC board and floating on these pins could cause problems.

Table 7. STCD22x0, STCD23x0 and STCD24x0 and enable polarity options

| Part number | Enable polarities (OPT1, OPT2)                                                                                                      | Enable polarity program method |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--|--|

| STCD2200    | OPT1 connected to V <sub>CC</sub> , EN1 active high OPT1 connected to GND, EN1 active low OPT2 controls EN2                         |                                |  |  |

| STCD2400    | OPT1 connected to V <sub>CC</sub> , EN1 and EN2 active high OPT1 connected to GND, EN1 and EN2 active low OPT2 controls EN3 and EN4 | User program                   |  |  |

| STCD2410    | OPT1 connected to V <sub>CC</sub> , EN1 active high OPT1 connected to GND, EN1 active low OPT2 controls EN2, EN3, and EN4           |                                |  |  |

| STCD2300    | EN1, EN2 and EN3 all active low                                                                                                     |                                |  |  |

| STCD2310    | STCD2310 EN1, EN2 active low, and EN3 active high                                                                                   |                                |  |  |

| STCD2320    | STCD2320 EN1, EN2 active high and EN3 active low                                                                                    |                                |  |  |

| STCD2330    | EN1, EN2 and EN3 all active high                                                                                                    |                                |  |  |

## 4 Application information

#### 4.1 LDO input capacitor

A 1  $\mu$ F input capacitor is required for the input of the LDO of the STCD22x0, STCD23x0 and STCD24x0 (the amount of capacitance can be increased without limit). This capacitor must be located as close as possible to the  $V_{CC}$  pin on the PC board and return to a clean analog ground. Any good quality ceramic, tantalum or film capacitor can be used for this capacitor.

#### 4.2 LDO output capacitor

A 1  $\mu$ F external capacitor is required for the output VTCXO of the LDO of the STCD22x0, STCD23x0 and STCD24x0. The STCD22x0, STCD23x0 and STCD24x0 are designed to work with low ESR (equivalent series resistance) ceramic capacitors. Make sure the ESR is lower than 500 m $\Omega$  to stabilize the VTCXO. Also, capacitor tolerance and variation with temperature must be considered to assure the minimum amount of capacitance provided at all times. This capacitor should be located as close as possible to the VTCXO pin on the PC board.

#### 4.3 LDO BYP pin

A 10 nF ceramic capacitor is required for the LDO BYP pin to ensure lower noise. Any good quality ceramic, tantalum or film capacitor can be used. The capacitor should be located as close as possible to the BYP pin on the PC board.

## 4.4 MC<sub>REQ</sub> pin

In the STCD22x0, STCD23x0, and STCD24x0, the MC<sub>BEO</sub> pin is open drain and active low.

Since  $\overline{\text{MC}}_{\text{REQ}}$  is active low, if none of the clock output is required, the STCD22x0, STCD23x0 and STCD24x0 are set to standby mode which turns off the internal LDO VTCXO.

$\overline{\text{MC}}_{\text{REQ}}$  is designed as an open drain structure. A pull-up resistor (50 k $\Omega$  recommended) is needed on the PC board to connect this pin to an external 1.8 V supply. Make sure the current flowing through this pin is kept within 3 mA to guarantee the proper function of the circuit.

If the  $\overline{MC}_{REQ}$  function is not used in the application, the user can connect this pin to GND or leave it unconnected. Other functions of the STCD2xx0 will not be affected.

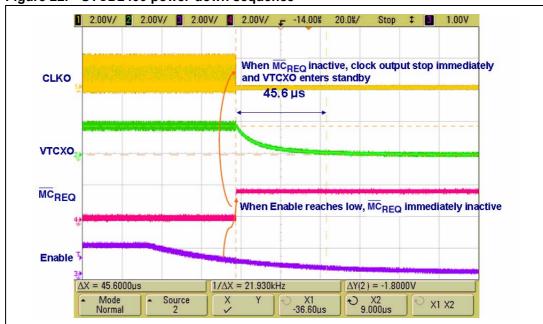

#### 4.5 Phase noise

Phase noise is a frequency domain phenomenon and is a critical specification in reference clocks. It is illustrated by a continuous spreading of the energy of the wave mainly caused by random noise. The phase noise is normally specified with a unit of dBc/Hz at a given offset in frequency (for example, 10 kHz) from the carrier wave (for example, 26 MHz). The value of the phase noise is the difference of the power contained within 1 Hz bandwidth of the offset frequency to the power at the carrier frequency. The total phase noise of the clock tree is obtained by adding the additive phase noise of STCD22x0, STCD23x0 and STCD24x0 and the phase noise of the clock source (for example, TCXO) in power which is illustrated in *Equation 1*.

#### **Equation 1**

$$PN_T = 10 log(10^{\frac{PN_C}{10}} + 10^{\frac{PN_X}{10}}) < PN_A$$

where:

PN<sub>T</sub> is the total phase noise in dBc/Hz

PN<sub>C</sub> is the additive phase noise of STCD22x0, STCD23x0 and STCD24x0 and

PN<sub>X</sub> is the phase noise of clock source

Make sure the total phase noise is kept within the phase noise requirement of each application  $PN_A$ . The user should choose the right TCXO with proper phase noise to meet the requirement.

#### 4.6 Jitter

In the time domain, energy spreading can result in jitter, which is the same phenomenon as phase noise in the frequency domain. As a sine wave passes its zero-crossing or a square wave changes state, the real clock signal transition is not exactly the same as the ideal case, thus causing variation in the waveform transition point. This deviation of the transition point is known as jitter as illustrated in *Figure 8*.

Figure 8. Jitter

In *Figure 8* the square wave ideal transition point should happen at points 1, 2, 3, 4 and 5, and each "ideal" period PI1 to PI4 should be the same, thus no time jitter has occurred. Actually, the real transition point happens at points 6, 7, 8, 9 and 10, thus causing "real" periods PR1 to PR4 to not be the same, and exhibit visible jitter. If each of the real periods of the cycles (PR1 to PR4) is measured, period jitter is obtained. The cycle-to-cycle jitter is also obtained by calculating the difference between two adjacent periods (for example, PR2-PR1, PR3-PR2 ...).

These periods of jitter are described as peak-to-peak jitter and are calculated by subtracting the minimum value from the maximum value or may also be described by the root-mean-square (RMS) value, representing one standard deviation of the Gaussian distribution.

#### 4.7 Output trace line

The STCD22x0, STCD23x0 and STCD24x0 is designed with maximum 50  $\Omega$  impedance output. On the PC board, a 50  $\Omega$  transmission line with proper series termination should be used to avoid signal distortion and reflection.

### 4.8 Typical application connections

The STCD2400 clock distribution circuit requires a source clock input as the reference clock (for example, XO). At most 4 devices can be connected to the outputs. The typical application circuit using STCD2400 is shown in Figure~9 and 10. The  $\overline{\text{MC}}_{\text{REQ}}$  is open drain output and active low. A pull-up resistor is needed to connect to an external 1.8 V supply VIO. If the clock source enable is active high, the user can use VTCXO as the master clock enable control signal, please refer to Figure~4 for the detailed connection.

In *Figure 9*, the clock from XO is distributed to the TD-SCDMA transmitter and receiver and GSM transceiver separately to be used as reference clocks.

In *Figure 10*, the buffer #4 output is fed into the Bluetooth system. In order to allow minimum power consumption, a Bluetooth system always has a clock request feature. If the Bluetooth system does not require the clock, the clock request disables the clock output. The enable pins can also be connected to an external 1.8 V supply to force the buffer to always be on.

In Figure 9 and 10, all the output clock enables are active high since both OPT1 and OPT2 are connected to  $V_{\rm CC}$ .

Figure 9. Typical application circuit using STCD24x0 for RF ends of TD-SCDMA/GSM dual-mode mobile phone

$V_{\overline{C}C}$ BT\_External\_Req Internal\_Req STCD24x0 Bluetooth BYP EN4 CLK4 **VTCXO** EN3 VIO WLAN Ţ Ş CLK3 EN2 GPS  $\overline{\rm MC}_{\rm REQ}$ CLK2 MCLK V<sub>CC</sub> EN1 OPT1 CLK1 OPT2 GND Other device ai14023

Figure 10. Typical application circuit using STCD24x0 for baseband peripherals in mobile phone

## 5 Typical operating characteristics

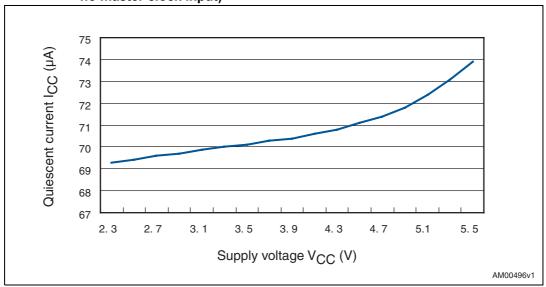

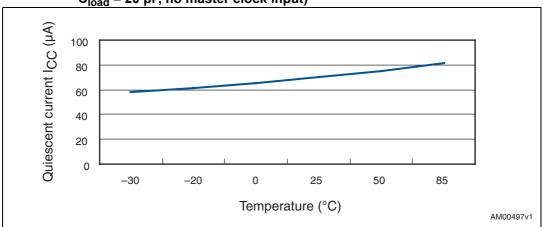

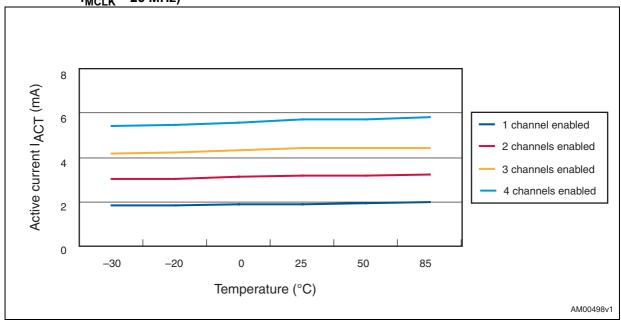

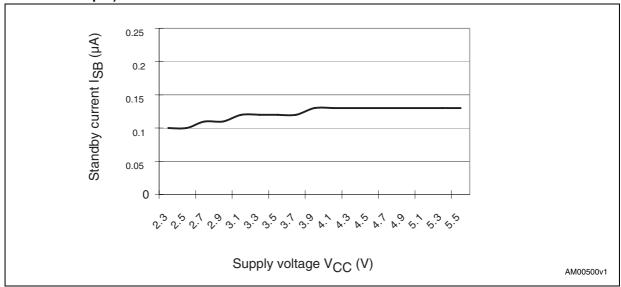

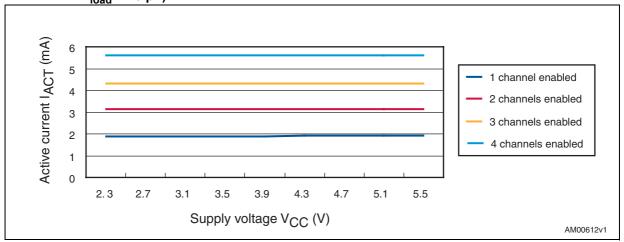

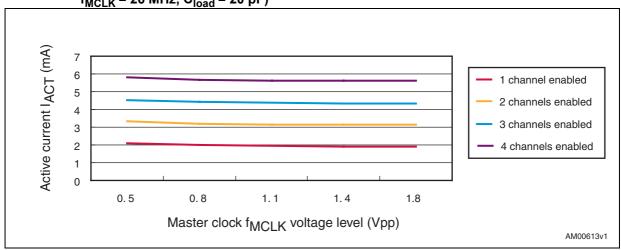

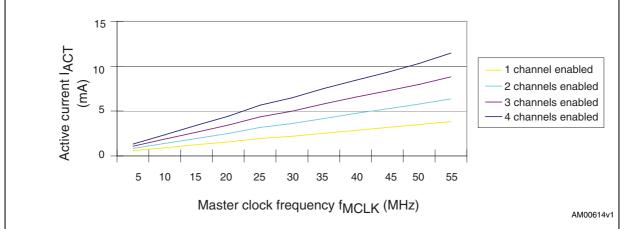

Typical operating characteristics are at  $T_A$  = 25 °C,  $C_{load}$  = 20 pF at each channel,  $V_{CC}$  = 3.8 V,  $f_{MCL\ K}$  = 26 MHz.

Figure 11. Quiescent current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 1, no master clock input)

Figure 12. Quiescent current vs. temperature (EN1 = EN2 = EN3 = EN4 = 1, C<sub>load</sub> = 20 pF, no master clock input)

Figure 13. Active current vs. temperature (EN1 = EN2 = EN3 = EN4 = 1,  $C_{load}$  = 20 pF,  $V_{CC}$  = 3.8 V,  $f_{MCLK}$  = 26 MHz)

Figure 14. Standby current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 0, no master clock input)

Figure 15. Active current vs. supply voltage (EN1 = EN2 = EN3 = EN4 = 1,  $f_{MCLK}$  = 26 MHz,  $C_{load} = 20 pF$

Figure 16. Active current vs. master clock input voltage level (EN1 = EN2 = EN3 = EN4 = 1,  $f_{MCLK} = 26 \text{ MHz}, C_{load} = 20 \text{ pF})$

Figure 17. Active current vs. master clock frequency (EN1 = EN2 = EN3 = EN4 = 1, C<sub>load</sub> = 20 pF)

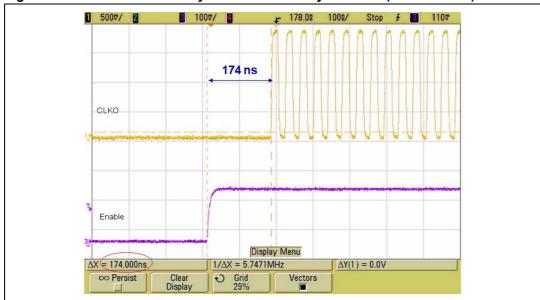

Figure 18. STCD2400 recovery time from standby to active (VTCXO is on)

Figure 20. Output clock rise/fall time (C<sub>load</sub> = 40 pF)

Figure 21. STCD2400 power-up sequence

Figure 23. Phase noise input (from the clock source, 26 MHz square wave XO KC2520C26 from Kyocera)