# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STEF05D

### Electronic fuse for 5 V line

#### Datasheet - preliminary data

- Hard disk and SSD arrays

- Set-top boxes

- DVD and Blu-ray disc drivers

### Description

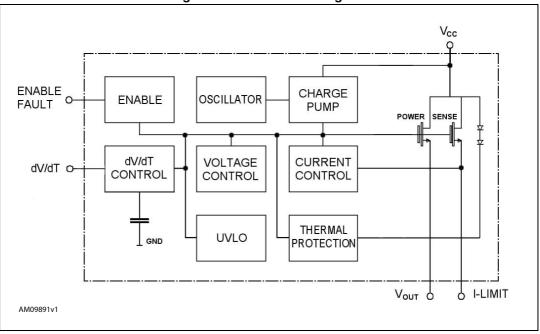

The STEF05D is an integrated electronic fuse optimized for monitoring output current and input voltage. Connected in series to a 5 V rail, it is capable of protecting the electronic circuitry on its output from overcurrent and overvoltage. The device has a controlled delay and turn-on time. When an overload condition occurs, the STEF05D limits the output current to a predefined safe value. If the anomalous overload condition. persists, it goes into an open state, disconnecting the load from the power supply. If a continuous short-circuit is present on the board, when power is re-applied the E-fuse initially limits the output current to a safe value, and then again goes into an open state.

The device is equipped with a thermal protection circuit. The intervention of the thermal protection is signal led to the board monitoring circuits through a signal on the Fault pin.

Unlike mechanical fuses, which must be physically replaced after a single event, the Efuse does not degrade in its performance after short-circuit/thermal protection interventions and it is reset either by recycling the supply voltage or using the Enable pin.

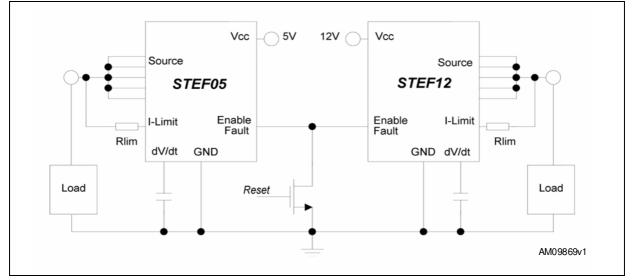

The companion chip for 12 V power rails is also available with part number STEF12.

### Features

- Continuous current typ: 3.6 A

- N-channel on-resistance typ: 40 mΩ

- Enable/fault functions

- Output clamp voltage typ: 6.65 V

- Undervoltage lockout

- Short-circuit limit

- Overload current limit

- Controlled output voltage ramp

- Thermal latch typ: 165 °C

- Uses tiny capacitors

- Operating junction temp. 40 °C to 125 °C

- Available in DFN10 (3 x 3 mm).

### Applications

- Hard disk drives

- Solid state drives (SSD)

#### Table 1.Device summary

| Order code | Package          | Packaging     |

|------------|------------------|---------------|

| STEF05DPUR | DFN10 (3 x 3 mm) | Tape and reel |

March 2013

DocID024394 Rev 1

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

### Contents

| 1 | Block | k diagra              | ım                         | 3 |

|---|-------|-----------------------|----------------------------|---|

| 2 | Pin c | onfigura              | ation                      | 4 |

| 3 | Maxir | num rat               | tings                      | 5 |

| 4 | Elect | rical cha             | aracteristics              | 6 |

| 5 | Туріс | al appli              | ication                    | 8 |

|   | 5.1   | Operati               | ing modes                  | 8 |

|   |       | 5.1.1                 | Turn-on                    | 8 |

|   |       | 5.1.2                 | Normal operating condition | 9 |

|   |       | 5.1.3                 | Output voltage clamp       | 9 |

|   |       | 5.1.4                 | Current limiting           | 9 |

|   |       | 5.1.5                 | Thermal shutdown           | 9 |

|   | 5.2   | R <sub>Limit</sub> ca | alculation                 | 9 |

|   | 5.3   | C <sub>dv/dt</sub> ca | alculation                 | 9 |

|   | 5.4   | Enable/               | /fault pin                 | 0 |

| 6 | Туріс | al perfo              | ormance characteristics1   | 2 |

| 7 | Packa | age meo               | chanical data              | 4 |

| 8 | Revis | sion hist             | tory                       | 8 |

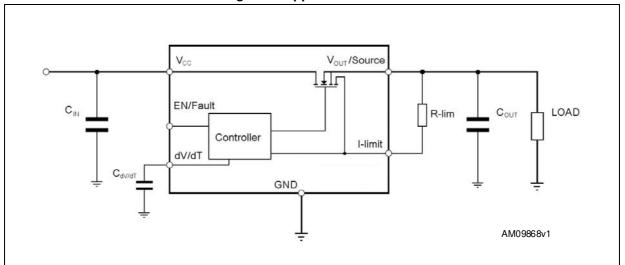

### 1 Block diagram

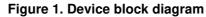

# 2 Pin configuration

#### Table 2. Pin description

| Pin N° | Symbol                   | Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 5 | V <sub>OUT/</sub> Source | Connected to the Source of the internal power MOSFET and to the output terminal of the fuse                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6      | NC                       | Not connected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7      | I-Limit                  | A resistor between this pin and the Source pin sets the overload and short-<br>circuit current limit levels.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8      | En/Fault                 | The enable/fault pin is a tri-state, bi-directional interface. During normal operation the pin must be left floating, or it can be used to disable the output of the device by pulling it to Ground using an open drain or open collector device.<br>If a thermal fault occurs, the voltage on this pin will go to an intermediate state to signal a monitor circuit that the device is in thermal shutdown. It can be connected to another device of this family to cause a simultaneous shutdown during thermal events. |

| 9      | dv/dt                    | The internal dv/dt circuit controls the slew rate of the output voltage at turn-<br>on. The internal capacitor allows a ramp-up time of around 1ms. An external<br>capacitor can be added to this pin to increase the ramp time. If an additional<br>capacitor is not required, this pin should be left open.                                                                                                                                                                                                             |

| 10     | GND                      | Ground Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 11     | V <sub>CC</sub>          | Exposed pad. Positive input voltage must be connected to $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

### 3 Maximum ratings

| Symbol                   | Parameter                                           | Value           | Unit |

|--------------------------|-----------------------------------------------------|-----------------|------|

| V                        | Positive power supply voltage (steady state)        | -0.3 to 10      | V    |

| V <sub>CC</sub>          | Positive power supply voltage (max 100 ms)          | -0.3 to 15      | v    |

| V <sub>OUT</sub> /source | (max 100 ms)                                        | -0.3 to Vcc+0.3 | V    |

| I-Limit                  | (max 100 ms)                                        | -0.3 to 15      | V    |

| En/Fault                 |                                                     | -0.3 to 7       | V    |

| dv/dt                    |                                                     | -0.3 to 7       | V    |

| T <sub>OP</sub>          | Operating junction temperature range <sup>(1)</sup> | -40 to 125      | °C   |

| T <sub>STG</sub>         | Storage temperature range                           | -65 to 150      | °C   |

| T <sub>LEAD</sub>        | Lead temperature (Soldering) 10 sec                 | 260             | °C   |

1. The thermal limit is set above the maximum thermal rating. It is not recommended to operate the device at temperatures greater than the maximum ratings for extended periods of time.

*Note:* Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.

#### Table 4. Thermal data

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 52.7  | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case    | 17.4  | °C/W |

#### Table 5. ESD performances

| Symbol | Parameter      | Test conditions | Value | Unit |

|--------|----------------|-----------------|-------|------|

|        |                | HBM             | 2     | KV   |

| ESD    | ESD Protection | MM              | 150   | V    |

|        |                | CDM             | 500   | V    |

# 4 Electrical characteristics

$V_{CC}$  = 5 V,  $V_{EN}$  = 3.3 V,  $C_{I}$  = 10  $\mu F,$   $C_{O}$  = 47  $\mu F,$   $T_{J}$  = 25 °C, unless otherwise specified

| Symbol              | Parameter                                       | Test conditions                                                                          | Min. | Тур. | Max. | Unit     |  |

|---------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|------|------|------|----------|--|

|                     | Und                                             | er/Overvoltage Protection                                                                | I.   |      |      |          |  |

| V <sub>Clamp</sub>  | Output clamping voltage                         | V <sub>CC</sub> = 10 V                                                                   | 5.95 | 6.65 | 7.7  | V        |  |

| V <sub>UVLO</sub>   | Undervoltage lockout                            | Turn-on, voltage going up                                                                | 3.2  | 3.6  | 4.3  | V        |  |

| V <sub>Hyst</sub>   | UVLO Hysteresis                                 |                                                                                          |      | 0.40 |      | V        |  |

|                     |                                                 | Power MOSFET                                                                             |      |      |      |          |  |

| t <sub>dly</sub>    | Delay time                                      | Enabling of chip to $I_D = 100 \text{ mA}$ with a 1 A resistive load                     |      | 200  |      | μs       |  |

| _                   | (1)                                             | T <sub>J</sub> = 25 °C                                                                   |      | 40   | 60   |          |  |

| R <sub>DSon</sub>   | ON resistance <sup>(1)</sup>                    | T <sub>J</sub> = 125 °C <sup>(2)</sup>                                                   |      |      | 70   | mΩ       |  |

| V <sub>OFF</sub>    | Off state output voltage                        | $V_{CC} = 10 V, V_{GS} = 0,$<br>$R_{Limit} = infinite$                                   |      | 50   | 200  | mV       |  |

| Ι <sub>D</sub>      | Continuous current                              | 0.5 inch <sup>2</sup> pad <sup>(2)</sup> , $T_A = 25 \text{ °C}$                         |      | 3.6  |      |          |  |

|                     |                                                 | Minimum copper, T <sub>A</sub> = 80 °C                                                   |      | 1.7  |      | A        |  |

|                     |                                                 | Current Limit                                                                            |      |      |      | <u> </u> |  |

| I <sub>Short</sub>  | Short-circuit current limit                     | R <sub>Limit</sub> = 11 Ω                                                                | 3.1  | 4.1  | 5.1  | Α        |  |

| I <sub>Lim</sub>    | Overload current limit                          | R <sub>Limit</sub> = 11 Ω                                                                |      | 4    |      | Α        |  |

|                     | ·                                               | dv/dt Circuit                                                                            |      |      |      |          |  |

| dv/dt               | Output voltage ramp time                        | Enable to $V_{OUT}$ =4.7V, No $C_{dv/dt}$                                                |      | 0.8  |      | ms       |  |

|                     |                                                 | Enable/Fault                                                                             |      |      |      |          |  |

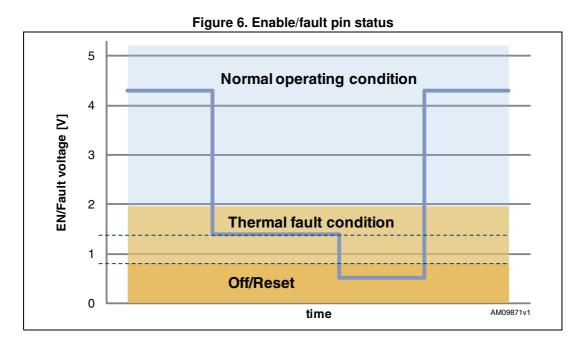

| V <sub>IL</sub>     | Low level input voltage <sup>(2)</sup>          | Output Disabled                                                                          | 0.35 | 0.58 | 0.81 | V        |  |

| V <sub>I(INT)</sub> | Intermediate level input voltage <sup>(2)</sup> | Thermal Fault, Output Disabled                                                           | 0.82 | 1.4  | 1.95 | V        |  |

| V <sub>IH</sub>     | High level input voltage                        | Output Enabled                                                                           | 1.96 | 2.64 | 3.3  | V        |  |

| V <sub>I(MAX)</sub> | High state maximum voltage                      |                                                                                          | 3.4  | 4.3  | 5.4  | V        |  |

| Ι <sub>ΙL</sub>     | Low level input current (sink)                  | V <sub>Enable</sub> = 0 V                                                                |      | -10  | -30  | μA       |  |

| I                   | High level leakage current for external switch  | V <sub>Enable</sub> = 3.3 V                                                              |      |      | 1    | μA       |  |

|                     | Maximum fan-out for fault signal                | Total numbers of chips that can<br>be connected to this pin for<br>simultaneous shutdown |      |      | 3    | Units    |  |

| Symbol            | Parameter                           | Test conditions    | Min. | Тур. | Max. | Unit |

|-------------------|-------------------------------------|--------------------|------|------|------|------|

|                   |                                     | Total Device       |      |      |      |      |

| I <sub>Bias</sub> | Bias current                        | Device operational |      | 0.5  | 2    | mA   |

|                   |                                     | Thermal Shutdown   |      | 1    |      | ma   |

| V <sub>min</sub>  | Minimum operating voltage           |                    |      |      | 3.1  | V    |

|                   | •                                   | Thermal Latch      | ·    |      |      |      |

| TSD               | Shutdown temperature <sup>(2)</sup> |                    |      | 165  |      | °C   |

#### Table 6. Electrical characteristics for STEF05D

1. Pulse test: Pulse width = 300  $\mu$ s, Duty cycle = 2%

2. Limits in temperature are guaranteed by design, but not tested in production

# 5 Typical application

Figure 3. Application circuit

#### Figure 4. Typical HDD application circuit

### 5.1 Operating modes

#### 5.1.1 Turn-on

When the input voltage is applied, the Enable/Fault pin goes up to the high state, enabling the internal control circuitry.

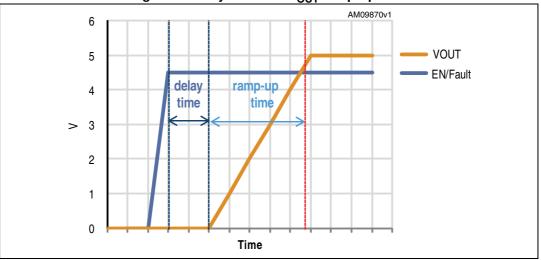

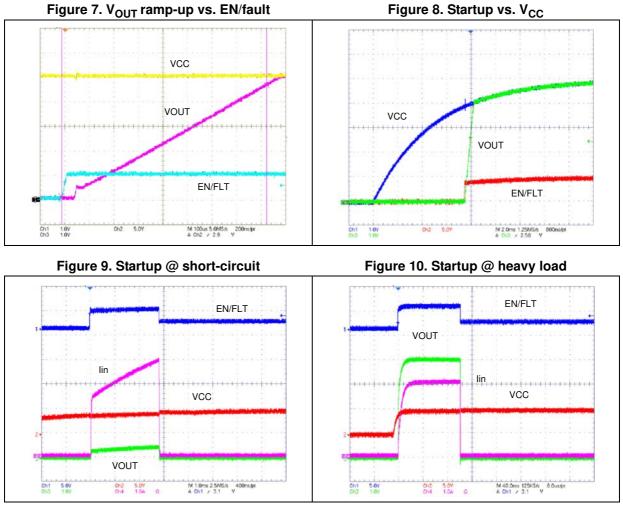

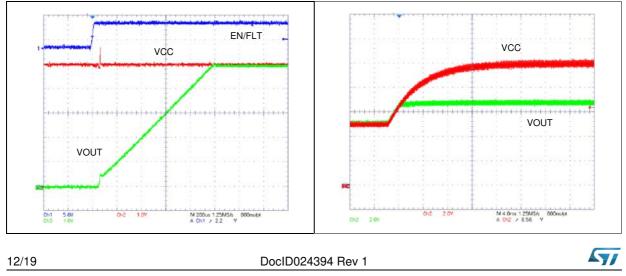

After an initial delay time of typically 200  $\mu$ s, the output voltage is supplied with a slope defined by the internal dv/dt circuitry. If no additional capacitor is connected to dv/dt pin, the total time from the Enable signal going high and the output voltage reaching the nominal value is around 1 ms (refer to *Figure 5 and Figure 7*).

#### 5.1.2 Normal operating condition

The STEF05D E-fuse behaves like a mechanical fuse, buffering the circuitry on its output with the same voltage shown at its input, with a small voltage fall due to the N-channel MOSFET  $R_{DSOn}$ .

#### 5.1.3 Output voltage clamp

This internal protection circuit clamps the output voltage to a maximum safe value, typically 6.65V, if the input voltage exceeds this threshold.

#### 5.1.4 Current limiting

When an overload event occurs, the current limiting circuit reduces the conductivity of the power MOSFET, in order to clamp the output current at the value selected externally by means of the limiting resistor  $R_{\text{Limit}}$  (*Figure 3*).

#### 5.1.5 Thermal shutdown

If the device temperature exceeds the thermal latch threshold, typically 165°C, the thermal shutdown circuitry turns the power MOSFET off, thus disconnecting the load. The EN/Fault pin of the device will automatically be set at an intermediate voltage, in order to signal the overtemperature event.

From this condition the E-fuse can be reset either by cycling the supply voltage or by pulling down the EN pin below the  $V_{il}$  threshold, and then releasing it.

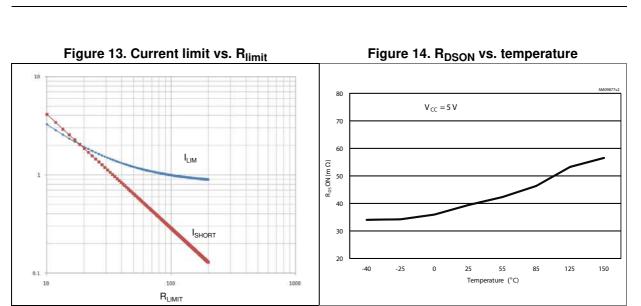

### 5.2 R<sub>Limit</sub> calculation

As shown in *Figure 3*, the device uses an internal N-channel sense FET with a fixed ratio, to monitor the output current and limit it at the level set by the user.

The  $R_{\text{Limit}}$  value for achieving the requested current limitation can be estimated by using the following theoretical formula, together with the graph in *Figure 13*:

#### **Equation 1**

$$\mathsf{RLimit} = \frac{42}{\mathsf{Ishort}}$$

### 5.3 C<sub>dv/dt</sub> calculation

Connecting a capacitor between the  $C_{dv/dt}$  pin and GND will allow the modification of the output voltage ramp time.

Given the desired time interval  $\Delta t$  during which the output voltage goes from zero to his maximum value, the capacitance to be added on  $C_{dv/dt}$  pin can be calculated using the following theoretical formula:

#### **Equation 2**

$$C_{dvdt} = 36 \times 10^{-9} \Delta t - 30 \times 10^{-12}$$

Where  $C_{dv/dt}$  is expressed in Farad, and the time  $\Delta t$  in seconds.

*Figure 5* shows a graphical explanation of delay time and ramp-up time.

### 5.4 Enable/fault pin

The Enable/Fault pin has the dual function of controlling the output of the device and, at the

same time, of providing information about the device status to the application.

When it is used, it should be connected to an external open-drain or open-collector device. In this case, when it is pulled at low logic level, it turns the output of the E-Fuse off.

If this pin is left floating, since it has internal pull-up circuitry, the output of the E-Fuse is kept ON in normal operating conditions.

In case of thermal fault, the pin is pulled to an intermediate state (*Figure 6*). This signal can be provided to a monitor circuit, informing it that a thermal shutdown has occurred, or it can be directly connected to the Enable/Fault pins of other STEFxx devices on the same application in order to achieve a simultaneous enable/disable feature.

When a thermal fault occurs, the device can be reset either by cycling the supply voltage or by pulling down the Enable pin below the  $V_{il}$  threshold and then releasing it.

#### STEF05D

# 6 Typical performance characteristics

The following plots are referred to the typical application circuit and, unless otherwise noted, at  $T_A = 25^{\circ}C$ .

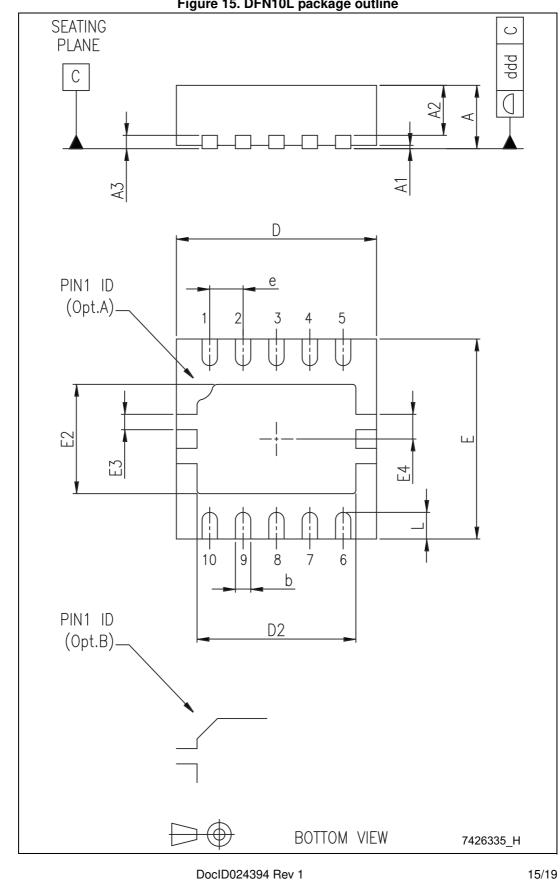

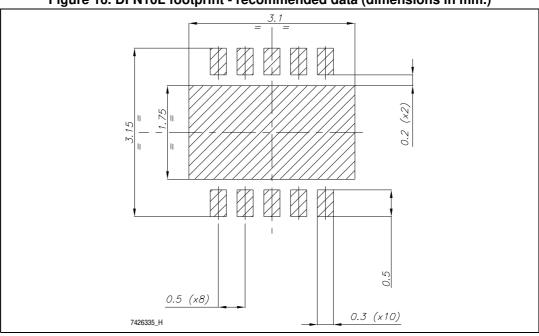

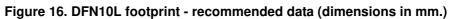

### 7 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

| Dim.  |      | mm.   |      |  |  |

|-------|------|-------|------|--|--|

| Dini. | Min. | Тур.  | Max. |  |  |

| A     | 0.80 | 0.90  | 1.00 |  |  |

| A1    |      | 0.02  | 0.05 |  |  |

| A2    | 0.55 | 0.65  | 0.80 |  |  |

| A3    |      | 0.20  |      |  |  |

| b     | 0.18 | 0.25  | 0.30 |  |  |

| D     | 2.85 | 3.00  | 3.15 |  |  |

| D2    | 2.20 |       | 2.70 |  |  |

| E     | 2.85 | 3.00  | 3.15 |  |  |

| E2    | 1.40 |       | 1.75 |  |  |

| E3    |      | 0.230 |      |  |  |

| E4    |      | 0.365 |      |  |  |

| е     |      | 0.50  |      |  |  |

| L     | 0.30 | 0.40  | 0.50 |  |  |

| ddd   |      |       | 0.08 |  |  |

Table 7. DFN10L (3 x 3 mm.) mechanical data

**T**

**T**

Figure 15. DFN10L package outline

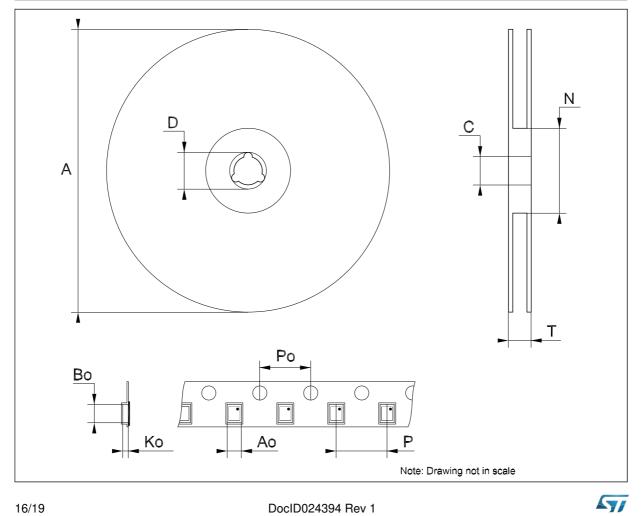

| Dim.  |      | mm.  |      | inch. |       |        |

|-------|------|------|------|-------|-------|--------|

| Dini. | Min. | Тур. | Max. | Min.  | Тур.  | Max.   |

| А     |      |      | 330  |       |       | 12.992 |

| С     | 12.8 |      | 13.2 | 0.504 |       | 0.519  |

| D     | 20.2 |      |      | 0.795 |       |        |

| Ν     | 60   |      |      | 2.362 |       |        |

| Т     |      |      | 18.4 |       |       | 0.724  |

| Ao    |      | 3.3  |      |       | 0.130 |        |

| Во    |      | 3.3  |      |       | 0.130 |        |

| Ko    |      | 1.1  |      |       | 0.043 |        |

| Po    |      | 4    |      |       | 0.157 |        |

| Р     |      | 8    |      |       | 0.315 |        |

# 8 Revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 19-Mar-2013 | 1        | Initial release. |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com