# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## STGIPL20K60

### SLLIMM<sup>™</sup> (small low-loss intelligent molded module) IPM, 3-phase inverter - 20 A, 600 V short-circuit rugged IGBT

- Isolation rating of 2500 V<sub>rms</sub>/min

- 5 kΩ NTC for temperature control

- UL Recognized: UL1557 file E81734

#### Applications

- 3-phase inverters for motor drives

- Home appliances, such as washing machines, refrigerators, air conditioners and sewing machines

### Description

This intelligent power module provides a compact, high performance AC motor drive in a simple, rugged design. Combining ST proprietary control ICs with the most advanced short-circuit-rugged IGBT system technology, this device is ideal for 3-phase inverters in applications such as home appliances and air conditioners. SLLIMM<sup>™</sup> is a trademark of STMicroelectronics.

### Features

- IPM 20 A, 600 V 3-phase IGBT inverter bridge including control ICs for gate driving and freewheeling diodes

- Short-circuit rugged IGBTs

- V<sub>CE(sat)</sub> negative temperature coefficient

- 3.3 V, 5 V, 15 V CMOS/TTL inputs comparators with hysteresis and pull down/pull up resistors

- Undervoltage lockout

- Internal bootstrap diode

- Interlocking function

- Smart shutdown function

- Comparators for fault protection against overtemperature and overcurrent

- Op amps for advanced current sensing

- DBC substrate leading to low thermal resistance

#### Table 1. Device summary

| Order code  | Marking   | Package  | Packaging |

|-------------|-----------|----------|-----------|

| STGIPL20K60 | GIPL20K60 | SDIP-38L | Tube      |

DocID018946 Rev 3

### Contents

| 1 | Inter | nal schematic diagram and pin configuration |

|---|-------|---------------------------------------------|

| 2 | Elect | trical ratings                              |

|   | 2.1   | Absolute maximum ratings 6                  |

|   | 2.2   | Thermal data                                |

| 3 | Elect | trical characteristics8                     |

|   | 3.1   | Control part                                |

|   |       | 3.1.1 NTC thermistor                        |

|   | 3.2   | Waveform definitions 14                     |

| 4 | Sma   | rt shutdown function 15                     |

| 5 | Appl  | ication information                         |

|   | 5.1   | Recommendations                             |

| 6 | Pack  | age mechanical data 19                      |

| 7 | Revi  | sion history                                |

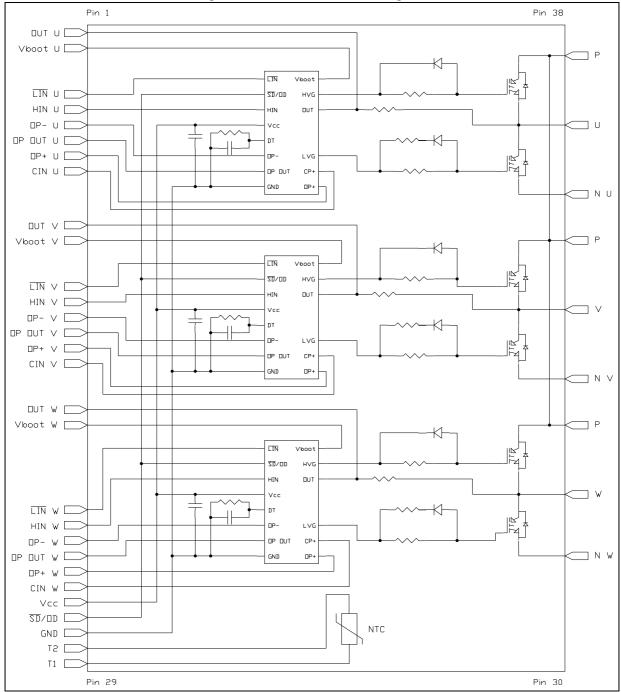

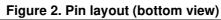

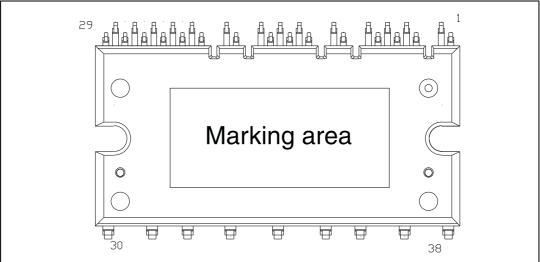

### 1 Internal schematic diagram and pin configuration

Figure 1. Internal schematic diagram

| Pin | Symbol              | Description                                                        |

|-----|---------------------|--------------------------------------------------------------------|

| 1   | OUT <sub>U</sub>    | High side reference output for U phase                             |

| 2   | V <sub>boot U</sub> | Bootstrap voltage for U phase                                      |

| 3   | LINU                | Low side logic input for U phase                                   |

| 4   | ΗΙΝ <sub>υ</sub>    | High side logic input for U phase                                  |

| 5   | OP-U                | Op amp inverting input for U phase                                 |

| 6   | OP <sub>OUT U</sub> | Op amp output for U phase                                          |

| 7   | OP+U                | Op amp non inverting input for U phase                             |

| 8   | CINU                | Comparator input for U phase                                       |

| 9   | OUT <sub>V</sub>    | High side reference output for V phase                             |

| 10  | V <sub>boot V</sub> | Bootstrap voltage for V phase                                      |

| 11  | LINV                | Low side logic input for V phase                                   |

| 12  | HINV                | High side logic input for V phase                                  |

| 13  | OP-V                | Op amp inverting input for V phase                                 |

| 14  | OP <sub>OUT V</sub> | Op amp output for V phase                                          |

| 15  | OP+ <sub>V</sub>    | Op amp non inverting input for V phase                             |

| 16  | CINV                | Comparator input for V phase                                       |

| 17  | OUT <sub>W</sub>    | High side reference output for W phase                             |

| 18  | V <sub>boot W</sub> | Bootstrap voltage for W phase                                      |

| 19  | LINW                | Low side logic input for W phase                                   |

| 20  | HINW                | High side logic input for W phase                                  |

| 21  | OP-W                | Op amp inverting input for W phase                                 |

| 22  | OP <sub>OUT W</sub> | Op amp output for W phase                                          |

| 23  | OP+ <sub>W</sub>    | Op amp non inverting input for W phase                             |

| 24  | CINW                | Comparator input for W phase                                       |

| 25  | V <sub>CC</sub>     | Low voltage power supply                                           |

| 26  | SD / OD             | Shutdown logic input (active low) / open drain (comparator output) |

| 27  | GND                 | Ground                                                             |

| 28  | T <sub>2</sub>      | NTC thermistor terminal 2                                          |

| 29  | T <sub>1</sub>      | NTC thermistor terminal 1                                          |

| 30  | N <sub>W</sub>      | Negative DC input for W phase                                      |

| 31  | W                   | W phase output                                                     |

| 32  | Р                   | Positive DC input                                                  |

| 33  | N <sub>V</sub>      | Negative DC input for V phase                                      |

| 34  | V                   | V phase output                                                     |

Table 2. Pin description

DocID018946 Rev 3

| Pin | Symbol | Description                   |  |  |  |

|-----|--------|-------------------------------|--|--|--|

| 35  | Р      | Positive DC input             |  |  |  |

| 36  | NU     | Negative DC input for U phase |  |  |  |

| 37  | U      | U phase output                |  |  |  |

| 38  | Р      | Positive DC input             |  |  |  |

Table 2. Pin description (continued)

### 2 Electrical ratings

### 2.1 Absolute maximum ratings

| Symbol                 | Parameter                                                                                                                     | Value | Unit |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------|------|

| V <sub>PN</sub>        | Supply voltage applied between $\text{P-N}_{\text{U}},\text{N}_{\text{V}},\text{N}_{\text{W}}$                                | 450   | V    |

| V <sub>PN(surge)</sub> | Supply voltage (surge) applied between $\text{P-N}_{\text{U}},$ $\text{N}_{\text{V}},$ $\text{N}_{\text{W}}$                  | 500   | V    |

| V <sub>CES</sub>       | Each IGBT collector emitter voltage ( $V_{IN}^{(1)} = 0$ )                                                                    | 600   | V    |

| $\pm I_{C}^{(2)}$      | Each IGBT continuous collector current at $T_{C} = 25 \ ^{\circ}C$                                                            | 20    | А    |

| $\pm I_{CP}^{(3)}$     | Each IGBT pulsed collector current                                                                                            | 40    | А    |

| P <sub>TOT</sub>       | Each IGBT total dissipation at $T_C = 25 \text{ °C}$                                                                          | 56    | W    |

| t <sub>scw</sub>       | Short circuit withstand time, $V_{CE} = 0.5 V_{(BR)CES} T_j$<br>= 125 °C, $V_{CC} = V_{boot} = 15 V$ , $V_{IN (1)} = 0 - 5 V$ | 5     | μs   |

#### Table 3. Inverter part

1. Applied between  $HIN_i$ ,  $\overline{LIN}_i$  and GND for i = U, V, W

2. Calculated according to the iterative formula:

$$I_{C}(T_{C}) = \frac{T_{j(max)} - T_{C}}{R_{thj-c} \times V_{CE(sat)(max)}(T_{j(max)}, I_{C}(T_{C}))}$$

3. Pulse width limited by max junction temperature

| Symbol                | Parameter                                                                                      | Min.                   | Max.                    | Unit |

|-----------------------|------------------------------------------------------------------------------------------------|------------------------|-------------------------|------|

| V <sub>OUT</sub>      | Output voltage applied between<br>OUT <sub>U</sub> , OUT <sub>V</sub> , OUT <sub>W</sub> - GND | V <sub>boot</sub> - 21 | V <sub>boot</sub> + 0.3 | V    |

| V <sub>CC</sub>       | Low voltage power supply                                                                       | - 0.3                  | 21                      | V    |

| V <sub>CIN</sub>      | Comparator input voltage                                                                       | - 0.3                  | V <sub>CC</sub> + 0.3   | V    |

| V <sub>op+</sub>      | OPAMP non-inverting input                                                                      | - 0.3                  | V <sub>CC</sub> + 0.3   | V    |

| V <sub>op-</sub>      | OPAMP inverting input                                                                          | - 0.3                  | V <sub>CC</sub> + 0.3   | V    |

| V <sub>boot</sub>     | Bootstrap voltage                                                                              | - 0.3                  | 620                     | V    |

| V <sub>IN</sub>       | Logic input voltage applied between HIN, $\overline{\text{LIN}}$ and GND                       | - 0.3                  | 15                      | V    |

| V <sub>SD/OD</sub>    | Open drain voltage                                                                             | - 0.3                  | 15                      | V    |

| dV <sub>OUT</sub> /dt | Allowed output slew rate                                                                       |                        | 50                      | V/ns |

#### Table 4. Control part

| Symbol           | Parameter                                                                                           | Value      | Unit |

|------------------|-----------------------------------------------------------------------------------------------------|------------|------|

| V <sub>ISO</sub> | Isolation withstand voltage applied between each pin and heatsink plate (AC voltage, $t = 60$ sec.) | 2500       | V    |

| Тj               | Power chips operating junction temperature                                                          | -40 to 150 | °C   |

| Т <sub>С</sub>   | Module case operation temperature                                                                   | -40 to 125 | °C   |

Table 5. Total system

### 2.2 Thermal data

#### Table 6. Thermal data

| Symbol            | Parameter                                     | Value | Unit |

|-------------------|-----------------------------------------------|-------|------|

| Б                 | Thermal resistance junction-case single IGBT  | 2.2   | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction-case single diode | 4.5   | °C/W |

### **3** Electrical characteristics

$T_i = 25 \ ^{\circ}C$  unless otherwise specified.

| Symbol               | Parameter                                                            | Test condition                                                                                                        |      | Unit |      |      |

|----------------------|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Symbol               |                                                                      | lest condition                                                                                                        | Min. | Тур. | Max. | Unit |

| Very                 | Collector-emitter                                                    | $V_{CC} = V_{Boot} = 15 \text{ V}, V_{IN}^{(1)} = 0 - 5 \text{ V},$<br>$I_{C} = 12 \text{ A}$                         | -    | 2.2  | 2.75 | v    |

| V <sub>CE(sat)</sub> | CE(sat) saturation voltage                                           | $V_{CC} = V_{Boot} = 15 \text{ V}, V_{IN}^{(1)} = 0 - 5 \text{ V},$<br>$I_{C} = 12 \text{ A}, T_{j} = 125 \text{ °C}$ | -    | 1.8  |      | v    |

| I <sub>CES</sub>     | Collector-cut off current $(V_{IN}^{(1)} = 0 \text{ "logic state"})$ | $V_{CE} = 550 V$<br>$V_{CC} = V_{boot} = 15 V$                                                                        | -    |      | 150  | μA   |

| V <sub>F</sub>       | Diode forward voltage                                                | $V_{IN}^{(1)} = 0$ "logic state", $I_C = 12 \text{ A}$                                                                | -    | 1.7  | 2.1  | V    |

| Inductive            | load switching time and                                              | energy                                                                                                                |      |      |      |      |

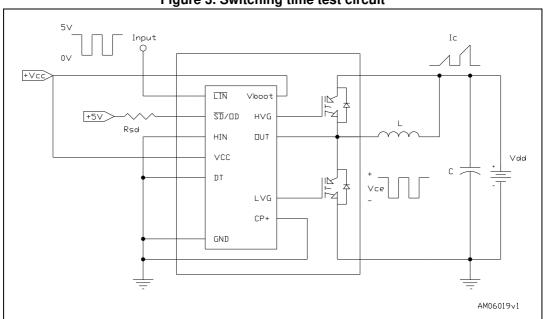

| t <sub>on</sub>      | Turn-on time                                                         |                                                                                                                       | -    | 915  |      |      |

| t <sub>c(on)</sub>   | Crossover time (on)                                                  | V <sub>DD</sub> = 300 V,                                                                                              | -    | 155  |      |      |

| t <sub>off</sub>     | Turn-off time                                                        | $V_{DD} = 300 \text{ V},$<br>$V_{CC} = V_{boot} = 15 \text{ V},$                                                      | -    | 375  |      | ns   |

| t <sub>c(off)</sub>  | Crossover time (off)                                                 | $V_{IN}^{(1)} = 0 - 5 V,$<br>$I_{C} = 12 A$                                                                           | -    | 120  |      |      |

| t <sub>rr</sub>      | Reverse recovery time                                                |                                                                                                                       | -    | 75   |      | ]    |

| E <sub>on</sub>      | Turn-on switching losses                                             | (see <i>Figure 3</i> )                                                                                                | -    | 300  |      |      |

| E <sub>off</sub>     | Turn-off switching losses                                            |                                                                                                                       | -    | 170  |      | μJ   |

#### Table 7. Inverter part

1. Applied between HINi  $\overline{\text{LIN}}$  i and GND for i = U, V, W ( $\overline{\text{LIN}}$  inputs are active-low).

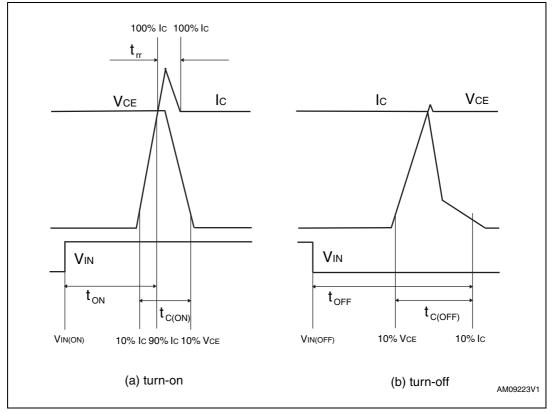

Note:  $t_{on}$  and  $t_{off}$  include the propagation delay time of the internal drive.  $t_{C(ON)}$  and  $t_{C(OFF)}$  are the switching time of IGBT itself under the internally given gate driving condition.

Figure 3. Switching time test circuit

Figure 4 "Switching time definition" refers to HIN inputs (active high). For LIN inputs (active low), V<sub>IN</sub> polarity must be inverted for turn-on and turn-off.

### 3.1 Control part

#### Table 8. Low voltage power supply (V<sub>CC</sub> = 15 V unless otherwise specified)

| Symbol                | Parameter                                   | Test conditions                                                                                                                                                                                 | Min. | Тур. | Max. | Unit |

|-----------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| V <sub>cc_hys</sub>   | V <sub>cc</sub> UV hysteresis               |                                                                                                                                                                                                 | 1.2  | 1.5  | 1.8  | V    |

| V <sub>cc_thON</sub>  | V <sub>cc</sub> UV turn ON threshold        |                                                                                                                                                                                                 | 11.5 | 12   | 12.5 | V    |

| V <sub>cc_thOFF</sub> | V <sub>cc</sub> UV turn OFF threshold       |                                                                                                                                                                                                 | 10   | 10.5 | 11   | V    |

| I <sub>qccu</sub>     | Undervoltage quiescent<br>supply current    | $\label{eq:V_CC} \begin{split} &V_{CC} = 10 \text{ V} \\ &\overline{\text{SD/OD}} = 5 \text{ V}; \ \overline{\text{LIN}} = 5 \text{ V}; \\ &H_{\text{IN}} = 0, \ C_{\text{IN}} = 0 \end{split}$ |      |      | 450  | μA   |

| I <sub>qcc</sub>      | Quiescent current                           |                                                                                                                                                                                                 |      |      | 3.5  | mA   |

| V <sub>ref</sub>      | Internal comparator (CIN) reference voltage |                                                                                                                                                                                                 | 0.5  | 0.54 | 0.58 | V    |

#### Table 9. Bootstrapped voltage ( $V_{CC}$ = 15 V unless otherwise specified)

| Symbol               | Parameter                                      | Test conditions                                                           | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------|---------------------------------------------------------------------------|------|------|------|------|

| V <sub>BS_hys</sub>  | V <sub>BS</sub> UV hysteresis                  |                                                                           | 1.2  | 1.5  | 1.8  | V    |

| V <sub>BS_thON</sub> | V <sub>BS</sub> UV turn ON threshold           |                                                                           | 11.1 | 11.5 | 12.1 | V    |

| $V_{BS_{thOFF}}$     | V <sub>BS</sub> UV turn OFF threshold          |                                                                           | 9.8  | 10   | 10.6 | V    |

| I <sub>QBSU</sub>    | Undervoltage V <sub>BS</sub> quiescent current | $V_{BS} < 9 V$<br>SD/OD = 5 V; LIN and<br>HIN = 5 V; C <sub>IN</sub> = 0  |      | 70   | 110  | μΑ   |

| I <sub>QBS</sub>     | V <sub>BS</sub> quiescent current              | $V_{BS} = 15 V$<br>SD/OD = 5 V; LIN and<br>HIN = 5 V; C <sub>IN</sub> = 0 |      | 200  | 300  | μA   |

| R <sub>DS(on)</sub>  | Bootstrap driver on resistance                 | LVG ON                                                                    |      | 120  |      | W    |

#### Table 10. Logic inputs (V<sub>CC</sub> = 15 V unless otherwise specified)

| Symbol            | Parameter                        | Test conditions  | Min. | Тур. | Max. | Unit |  |

|-------------------|----------------------------------|------------------|------|------|------|------|--|

| V <sub>il</sub>   | Low logic level voltage          |                  | 0.8  |      | 1.1  | V    |  |

| V <sub>ih</sub>   | High logic level voltage         |                  | 1.9  |      | 2.25 | V    |  |

| I <sub>HINh</sub> | HIN logic "1" input bias current | HIN = 15 V       | 110  | 175  | 260  | μΑ   |  |

| I <sub>HINI</sub> | HIN logic "0" input bias current | HIN = 0 V        |      |      | 1    | μΑ   |  |

| I <sub>LINI</sub> | LIN logic "1" input bias current | LIN = 0 V        | 3    | 6    | 20   | μΑ   |  |

| I <sub>LINh</sub> | LIN logic "0" input bias current | LIN = 15 V       |      |      | 1    | μA   |  |

| I <sub>SDh</sub>  | SD logic "0" input bias current  | <u>SD</u> = 15 V | 30   | 120  | 300  | μΑ   |  |

| I <sub>SDI</sub>  | SD logic "1" input bias current  | <u>SD</u> = 0 V  |      |      | 3    | μA   |  |

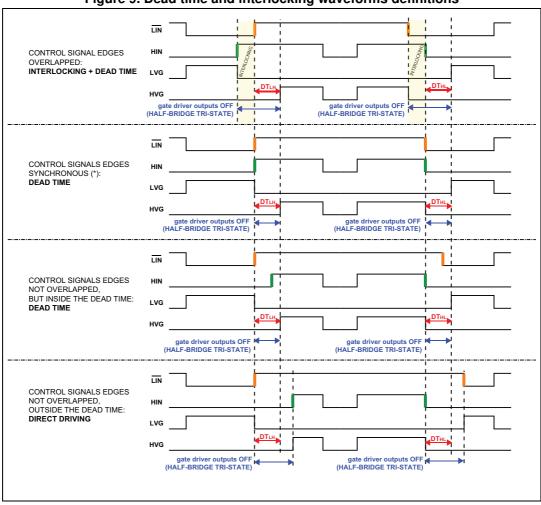

| Dt                | Dead time                        | see Figure 9     |      | 600  |      | ns   |  |

| Symbol           | Parameter                                   | Test condition                                | Min. | Тур. | Max. | Unit |

|------------------|---------------------------------------------|-----------------------------------------------|------|------|------|------|

| V <sub>io</sub>  | Input offset voltage                        | $V_{ic} = 0 V, V_o = 7.5 V$                   |      |      | 6    | mV   |

| l <sub>io</sub>  | Input offset current                        | $V_{ic} = 0 V, V_{o} = 7.5 V$                 |      | 4    | 40   | nA   |

| l <sub>ib</sub>  | Input bias current (1)                      | $v_{ic} = 0 v, v_0 = 7.5 v$                   |      | 100  | 200  | nA   |

| V <sub>icm</sub> | Input common mode voltage range             |                                               | 0    |      |      | V    |

| V <sub>OL</sub>  | Low level output voltage                    | $R_L = 10 \text{ k}\Omega \text{ to } V_{CC}$ |      | 75   | 150  | mV   |

| V <sub>OH</sub>  | High level output voltage                   | $R_L = 10 \ k\Omega$ to GND                   | 14   | 14.7 |      | V    |

|                  |                                             | Source,<br>$V_{id} = +1; V_o = 0 V$           | 16   | 30   |      | mA   |

| lo               | I <sub>o</sub> Output short circuit current |                                               | 50   | 80   |      | mA   |

| SR               | Slew rate                                   | $V_i = 1 - 4 V; C_L = 100 pF;$<br>unity gain  | 2.5  | 3.8  |      | V/µs |

| GBWP             | Gain bandwidth product                      | V <sub>o</sub> = 7.5 V                        | 8    | 12   |      | MHz  |

| A <sub>vd</sub>  | Large signal voltage gain                   | $R_L = 2 k\Omega$                             | 70   | 85   |      | dB   |

| SVR              | Supply voltage rejection ratio              | vs. V <sub>CC</sub>                           | 60   | 75   |      | dB   |

| CMRR             | Common mode rejection ratio                 |                                               | 55   | 70   |      | dB   |

Table 11. Op amp characteristics ( $V_{CC}$  = 15 V unless otherwise specified)

1. The direction of input current is out of the IC.

| Symbol              | Parameter                                                                        | Test conditions                                                            | Min. | Тур. | Max. | Unit   |

|---------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|------|------|--------|

| I <sub>ib</sub>     | Input bias current                                                               | V <sub>CIN</sub> = 1 V                                                     | -    |      | 3    | μΑ     |

| V <sub>ol</sub>     | Open-drain low-level output voltage                                              | I <sub>od</sub> = 3 mA                                                     | -    |      | 0.5  | V      |

| t <sub>d_comp</sub> | Comparator delay                                                                 | $\overline{SD}$ /OD pulled to 5 V through 100 k $\Omega$ resistor          | -    | 90   | 130  | ns     |

| SR                  | Slew rate                                                                        | $C_L = 180 \text{ pF}; \text{ R}_{pu} = 5 \text{ k}\Omega$                 | -    | 60   |      | V/µsec |

| t <sub>sd</sub>     | Shutdown to high / low side driver propagation delay                             |                                                                            | 50   | 125  | 200  |        |

| t <sub>isd</sub>    | Comparator triggering to high /<br>low side driver turn-off<br>propagation delay | Measured applying a voltage step from 0 V to 3.3 V to pin CIN <sub>i</sub> | 50   | 200  | 250  | ns     |

| Condition                                   |       | Logic input (V <sub>I</sub> ) |     | tput |     |

|---------------------------------------------|-------|-------------------------------|-----|------|-----|

| Condition                                   | SD/OD | LIN                           | HIN | LVG  | HVG |

| Shutdown enable<br>half-bridge 3-state      | L     | х                             | х   | L    | L   |

| Interlocking<br>half-bridge 3-state         | н     | L                             | н   | L    | L   |

| 0 ''logic state"<br>half-bridge 3-state     | н     | н                             | L   | L    | L   |

| 1 "logic state"<br>low side direct driving  | н     | L                             | L   | н    | L   |

| 1 "logic state"<br>high side direct driving | н     | н                             | н   | L    | н   |

Table 13. Truth table

Note: X: don't care.

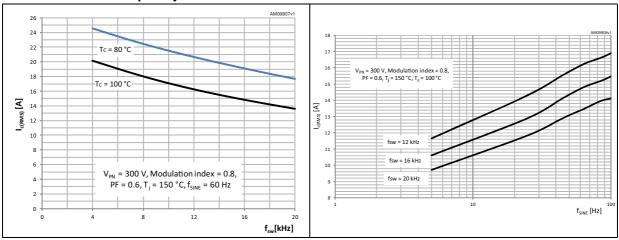

Figure 5. Maximum  $I_{C(RMS)}$  current vs. switching frequency <sup>(1)</sup>

Figure 6. Maximum  $\rm I_{C(RMS)}$  current vs.  $\rm f_{sine}^{(1)}$

1. Simulated curves refer to typical IGBT parameters and maximum R<sub>thj-c.</sub>

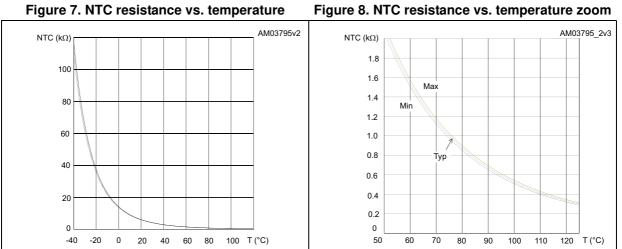

#### 3.1.1 NTC thermistor

| Table | 14 | NTC  | therm         | nistor |

|-------|----|------|---------------|--------|

| Table |    | 1110 | <b>UICIII</b> | iistoi |

| Symbol           | Parameter             | Test conditions                                 | Min. | Тур. | Max. | Unit. |

|------------------|-----------------------|-------------------------------------------------|------|------|------|-------|

| R <sub>25</sub>  | Resistance            | $T_{NTC} = 25^{\circ}C \text{ to } 85^{\circ}C$ |      | 5    |      | kΩ    |

| R <sub>125</sub> | Resistance            | T <sub>NTC</sub> = 125°C                        |      | 300  |      | Ω     |

| В                | B-constant            | $T_C = 25^{\circ}C$ to $85^{\circ}C$            |      | 3340 |      | К     |

| Т                | Operating temperature |                                                 | -40  |      | 125  | °C    |

#### Equation 1: resistance variation vs. temperature

$$\mathsf{R}(\mathsf{T}) = \mathsf{R}_{25} \cdot \mathsf{e}^{\mathsf{B}\left(\frac{1}{\mathsf{T}} - \frac{1}{298}\right)}$$

Where T are temperatures in Kelvin

#### Figure 8. NTC resistance vs. temperature zoom

### 3.2 Waveform definitions

Figure 9. Dead time and interlocking waveforms definitions

### 4 Smart shutdown function

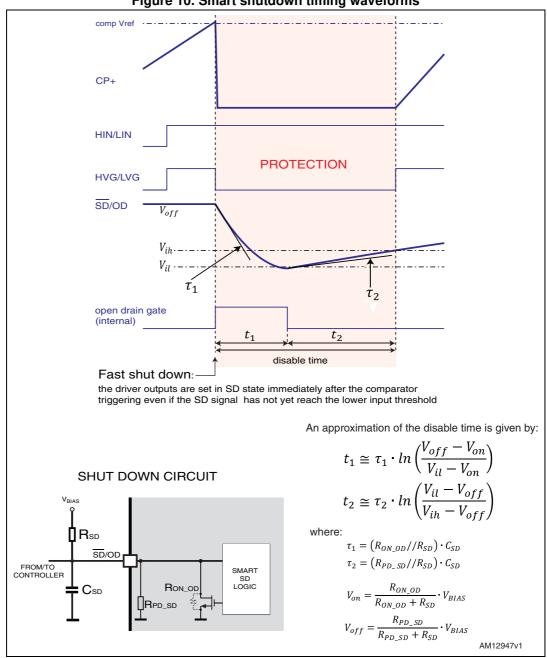

The STGIPL20K60 integrates a comparator for fault sensing purposes. The comparator non-inverting input (CIN) can be connected to an external shunt resistor in order to implement a simple overcurrent protection function. When the comparator triggers, the device is set in shutdown state and both its outputs are set to low-level leading the half-bridge in 3-state. In the common overcurrent protection architectures the comparator output is usually connected to the shutdown input through a RC network, in order to provide a mono-stable circuit, which implements a protection time that follows the fault condition. Our smart shutdown architecture allows to immediately turn-off the output gate driver in case of overcurrent, the fault signal has a preferential path which directly switches off the outputs. The time delay between the fault and the outputs turn-off is no more dependent on the RC values of the external network connected to the shutdown pin. At the same time the internal logic turns on the open-drain output and holds it on until the shutdown voltage goes below the logic input lower threshold. Finally the smart shutdown function provides the possibility to increase the real disable time without increasing the constant time of the external RC network.

Figure 10. Smart shutdown timing waveforms

Pls refer to *Table 12* for internal propagation delay time details.

## 5 Application information

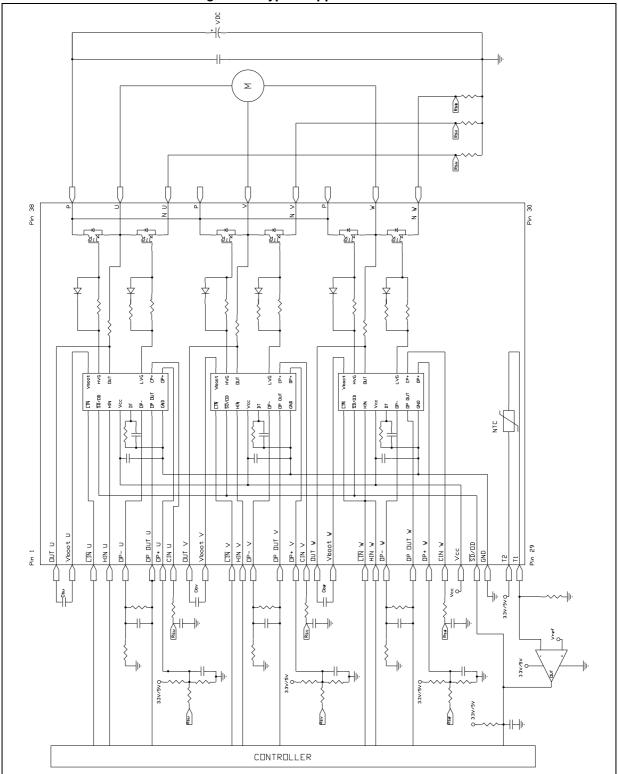

Figure 11. Typical application circuit

#### 5.1 Recommendations

- Input signal HIN is active high logic. A 85 k $\Omega$  (typ.) pull down resistor is built-in for each high side input. If an external RC filter is used, for noise immunity, pay attention to the variation of the input signal level.

- Input signal  $\overline{\text{LIN}}$  is active low logic. A 720 k $\Omega$  (typ.) pull-up resistor, connected to an internal 5 V regulator through a diode, is built-in for each low side input.

- To prevent the input signals oscillation, the wiring of each input should be as short as possible.

- By integrating an application specific type HVIC inside the module, direct coupling to MCU terminals without any opto-coupler is possible.

- Each capacitor should be located as nearby the pins of IPM as possible.

- Low inductance shunt resistors should be used for phase leg current sensing.

- Electrolytic bus capacitors should be mounted as close to the module bus terminals as possible. Additional high frequency ceramic capacitor mounted close to the module pins will further improve performance.

- The SD/OD signal should be pulled up to 5 V / 3.3 V with an external resistor (see *Section 4: Smart shutdown function* for detailed info).

| Symbol            | Parameter                             | Conditions                                                       |                | Value | Unit |     |

|-------------------|---------------------------------------|------------------------------------------------------------------|----------------|-------|------|-----|

|                   | Farameter                             | Conditions                                                       | Min. Typ. Max. |       |      | onn |

| V <sub>PN</sub>   | Supply voltage                        | Applied between P-Nu, Nv, Nw                                     |                | 300   | 400  | V   |

| V <sub>CC</sub>   | Control supply voltage                | Applied between V <sub>CC</sub> -GND                             | 13.5           | 15    | 18   | V   |

| V <sub>BS</sub>   | High side bias voltage                | Applied between $V_{BOOTI}$ -OUT <sub>i</sub> for i = U, V, W    | 13             |       | 18   | V   |

| t <sub>dead</sub> | Blanking time to<br>prevent Arm-short | For each input signal                                            | 1              |       |      | μs  |

| f <sub>PWM</sub>  | PWM input signal                      | -40°C < T <sub>c</sub> < 100°C<br>-40°C < T <sub>j</sub> < 125°C |                |       | 20   | kHz |

| т <sub>с</sub>    | Case operation temperature            |                                                                  |                |       | 100  | °C  |

#### Table 15. Recommended operating conditions

For further details refer to AN3338.

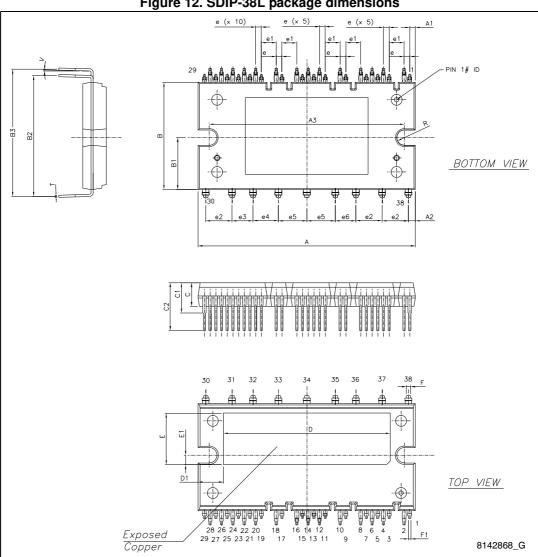

### 6 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

Please refer to dedicated technical note TN0107 for mounting instructions.

| Discontinue |       | mm.   |       |

|-------------|-------|-------|-------|

| Dimensions  | Min.  | Тур.  | Max.  |

| A           | 49.10 | 49.60 | 50.10 |

| A1          | 1.10  | 1.30  | 1.50  |

| A2          | 1.40  | 1.60  | 1.80  |

| A3          | 44.10 | 44.60 | 45.10 |

| В           | 24.00 | 24.50 | 25.00 |

| B1          | 11.25 | 11.85 | 12.45 |

| B2          | 27.10 | 27.60 | 28.10 |

| B3          | 28.60 | 29.10 | 29.60 |

| С           | 5.00  | 5.40  | 6.00  |

| C1          | 6.50  | 7.00  | 7.50  |

| C2          | 10.35 | 10.85 | 11.35 |

| e           | 1.10  | 1.30  | 1.50  |

| e1          | 3.20  | 3.40  | 3.60  |

| e2          | 5.80  | 6.00  | 6.20  |

| e3          | 4.60  | 4.80  | 5.00  |

| e4          | 5.60  | 5.80  | 6.00  |

| e5          | 6.30  | 6.50  | 6.70  |

| e6          | 4.50  | 4.70  | 4.90  |

| D           |       | 38.10 |       |

| D1          |       | 5.75  |       |

| E           |       | 11.80 |       |

| E1          |       | 2.15  |       |

| F           | 0.85  | 1.00  | 1.15  |

| F1          | 0.35  | 0.50  | 0.65  |

| R           | 1.55  | 1.75  | 1.95  |

| Table 16 | SDIP-38I       | mechanical data | • |

|----------|----------------|-----------------|---|

|          | <b>JDIL-20</b> | meenamear uala  |   |

| Table 16. SDIP-38L mechanical data (continued) |      |      |      |  |

|------------------------------------------------|------|------|------|--|

| Т                                              | 0.45 | 0.55 | 0.65 |  |

| V                                              | 0°   |      | 6°   |  |

#### Figure 12. SDIP-38L package dimensions

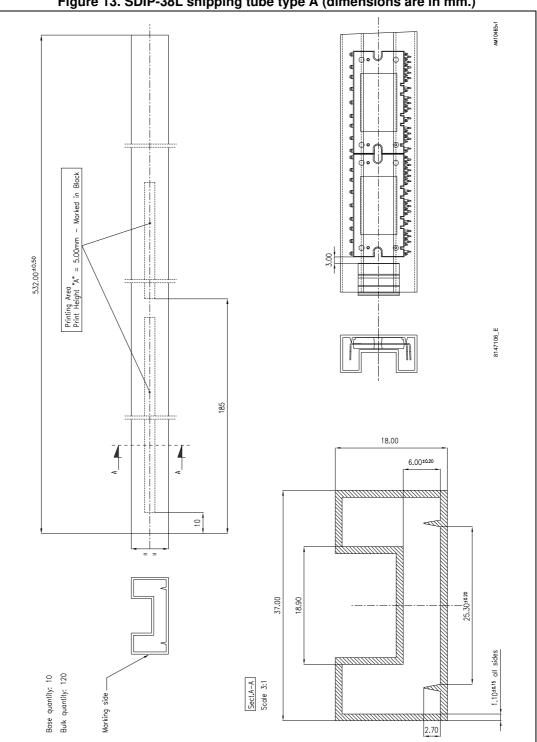

Figure 13. SDIP-38L shipping tube type A (dimensions are in mm.)

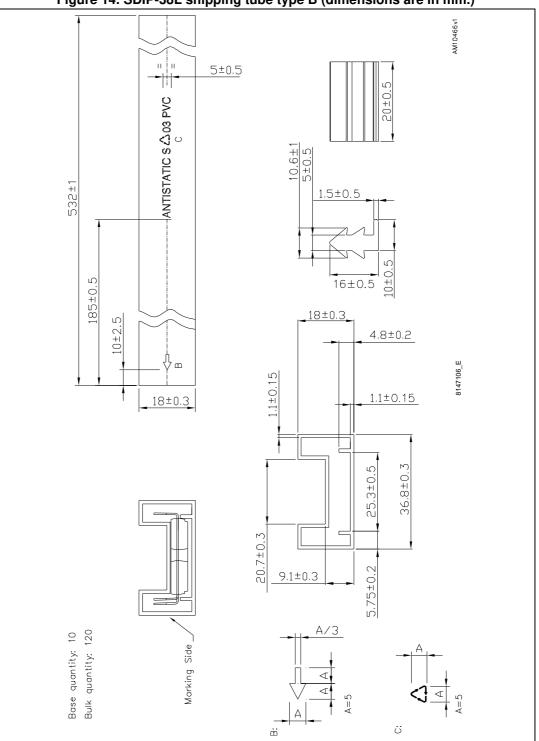

Figure 14. SDIP-38L shipping tube type B (dimensions are in mm.)

## 7 Revision history

| Date        | Revision | Changes                                                                                                                                    |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 16-Jun-2011 | 1        | Initial release                                                                                                                            |

| 28-Aug-2012 | 2        | Modified: Min. and Max. value <i>Table 4 on page 6</i> .<br>Updated: <i>Figure 13 on page 21</i> .<br>Added: <i>Figure 14 on page 22</i> . |

| 17-Jun-2013 | 3        | Updated Figure 9: Dead time and interlocking waveforms definitions.                                                                        |

Table 17. Document revision history

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

ST PRODUCTS ARE NOT AUTHORIZED FOR USE IN WEAPONS. NOR ARE ST PRODUCTS DESIGNED OR AUTHORIZED FOR USE IN: (A) SAFETY CRITICAL APPLICATIONS SUCH AS LIFE SUPPORTING, ACTIVE IMPLANTED DEVICES OR SYSTEMS WITH PRODUCT FUNCTIONAL SAFETY REQUIREMENTS; (B) AERONAUTIC APPLICATIONS; (C) AUTOMOTIVE APPLICATIONS OR ENVIRONMENTS, AND/OR (D) AEROSPACE APPLICATIONS OR ENVIRONMENTS. WHERE ST PRODUCTS ARE NOT DESIGNED FOR SUCH USE, THE PURCHASER SHALL USE PRODUCTS AT PURCHASER'S SOLE RISK, EVEN IF ST HAS BEEN INFORMED IN WRITING OF SUCH USAGE, UNLESS A PRODUCT IS EXPRESSLY DESIGNATED BY ST AS BEING INTENDED FOR "AUTOMOTIVE, AUTOMOTIVE SAFETY OR MEDICAL" INDUSTRY DOMAINS ACCORDING TO ST PRODUCT DESIGN SPECIFICATIONS. PRODUCTS FORMALLY ESCC, QML OR JAN QUALIFIED ARE DEEMED SUITABLE FOR USE IN AEROSPACE BY THE CORRESPONDING GOVERNMENTAL AGENCY.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries. Information in this document supersedes and replaces all information previously supplied. The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

DocID018946 Rev 3