Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## STHDMI002A

## Wide bandwidth, 2 to 1 HDMI switch with single enable

#### **Features**

- Compatible with HDMI v1.2, DVI v1.0 digital interfaces

- 165MHz speed operation supports all video formats up to 1080p and SXGA (1280 x 1024 at 75Hz)

- Data rate per channel for UXGA: 1.65Gbps

- Low R<sub>ON</sub>: 5.5 Ω(typ)

- V<sub>CC</sub> operating range: 3.135V to 3.465V

- Low current consumption: 20µA

- ESD human body model HBM Voltage:

- ±2KV for all I/Os

- Channel ON capacitance: 6pF (typ)

- Switching speed: 9ns

- Near-zero propagation delay: 250ps

- Low crosstalk: -32dB at 825MHz

- Bit-to-bit skew: 200ps

- Very low ground bounce in flow through mode

- Data and control inputs provide an undershoot clamp diode

- Wide bandwidth minimizes skew and jitter

- Hot insertion capable

- Isolated Digital Display Control (DDC) bus for unused ports

- 5V tolerance to all DDC and HPD\_SINK inputs

- Supports bi-directional operation

- Available in the TQFP48 package

- -40°C to 85°C operating temperature range

### **Applications**

- Advanced TVs

- Front projectors

- LCD TVs

- PDPs

- LCD monitors

- Notebook PCs

- STB and DVD players

### **Description**

The STHDMI002A is a differential Single Pole Double Throw (SPDT) 2 to 1, low Ron, bi-directional HDMI switch designed for advanced TV applications supporting HDMI/DVI which demand high definition superior image quality. The differential signal from the 2 ports of HDMI is multiplexed through the switch to form a single output HDMI channel going to the HDMI receiver while the unselected output goes to the high-Z state.

It is designed for very low cross-talk, low bit-to-bit skew, high channel-to-channel noise isolation and low I/O capacitance. The switch offers very little or practically no attenuation of the high-speed signals at the outputs, thus preserving the signal integrity to pass stringent requirements.

The STHDMI002A also includes the DDC as well as the HPD line switching. The pin layout is optimized for easy PCB routing to the HDMI connector and HDMI receivers.

The maximum DVI/HDMI data rate of 1.65Gbps provides the resolution required by the advanced HDTV and PC graphics.

### **Advantages**

STHDMI002A provides the ability to switch a single source output to various display devices or switch video display devices between multiple sources. It reduces the overall BOM costs by eliminating the need for more costly multi inputoutput controllers.

# **Contents**

| 1 | Fund  | ctional diagram                        |

|---|-------|----------------------------------------|

| 2 | Fund  | ctional description5                   |

|   | 2.1   | HPD pins                               |

|   | 2.2   | DDC channels                           |

| 3 | App   | lication diagram6                      |

| 4 | Pin d | configuration7                         |

|   | 4.1   | configuration                          |

| 5 | Max   | imum rating                            |

| 6 | DC e  | electrical characteristics             |

|   | 6.1   | Capacitance                            |

|   | 6.2   | Power supply characteristics           |

|   | 6.3   | Dynamic electrical characteristics     |

|   | 6.4   | Dynamic switching characteristics      |

|   | 6.5   | ESD performance                        |

| 7 | Test  | circuit for electrical characteristics |

| 8 | Timi  | ng waveforms                           |

| 9 | App   | lication information                   |

|   | 9.1   | Power supply sequencing                |

| 9.3 Diffe  Package n  Order cod | rential traces | lata         |                 |                 |                  |

|---------------------------------|----------------|--------------|-----------------|-----------------|------------------|

| Order cod                       |                |              |                 |                 | 2                |

| Povision b                      | es             |              |                 |                 |                  |

| Revision h                      |                |              |                 |                 | 24               |

|                                 | istory         |              |                 |                 | 25               |

|                                 |                |              | 0/050/          | etePro          | ducils           |

| eiteP                           | koqinc,        | (5)          |                 |                 |                  |

|                                 |                |              |                 |                 |                  |

|                                 | eteP           | lețe Product | nete Productish | nete Product(s) | nete Product(s). |

577

STHDMI002A

STHDMI002A Functional diagram

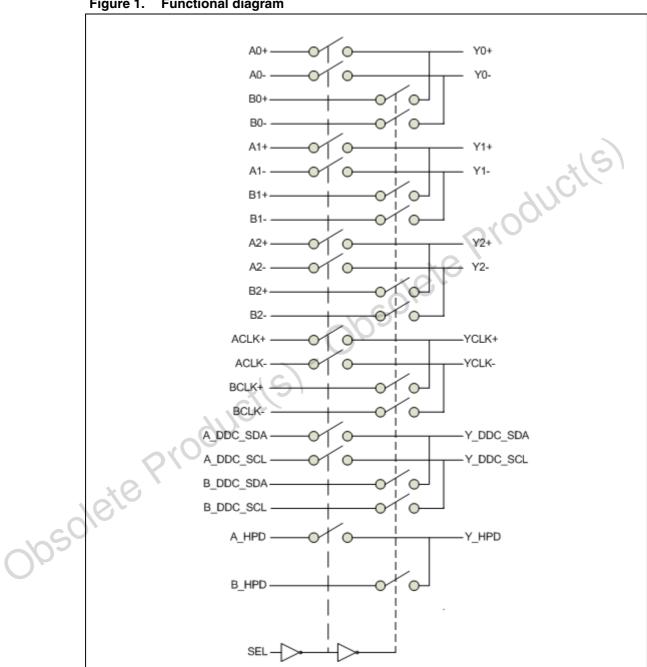

#### **Functional diagram** 1

Figure 1. **Functional diagram**

STHDMI002A Functional description

## 2 Functional description

The STHDMI002A routes physical layer signals for high bandwidth digital video and is compatible with low voltage differential signaling standards like TMDS. The device multiplexes differential outputs from a video source to one of the two corresponding outputs to a common display. The low on-resistance and low I/O capacitance of STHDMI002A result in a very small propagation delay. The device integrates SPDT-type switches for 3 differential data TMDS channels and 1 differential clock channel. Additionally it integrates the switches for DDC and HPD lines switching.

The I<sup>2</sup>C interface of the selected input port is linked to the I<sup>2</sup>C interface of the output port, and the hot plug detector (HPD) of the selected input port is output to HPD\_SINK. For the unused ports, the I<sup>2</sup>C interfaces are isolated, and the HPD pins are also isolated.

### 2.1 HPD pins

The input of the Y\_HPD is 5V tolerant, allowing direct connection to 5V signals. The switch is able to pass both 0V and 5V signal levels. The HPD switch resistance depends on the input voltage level. At low (near to 0V) input voltage levels, the resistance is  $20\Omega$  typically and at high (near to 5V) input voltage levels, the resistance is  $150\Omega$  typically.

### 2.2 DDC channels

The DDC channels are designed with a bi-directional NMOS gate, providing 5V signal tolerance. The 5V tolerance allows direct connection to a standard I<sup>2</sup>C bus, thus eliminating the need for a level shifter. When the input is a 5V, the NMOS switch is turned off and the pull up resistor on either side of the switch determines the high voltage potential.

Application diagram STHDMI002A

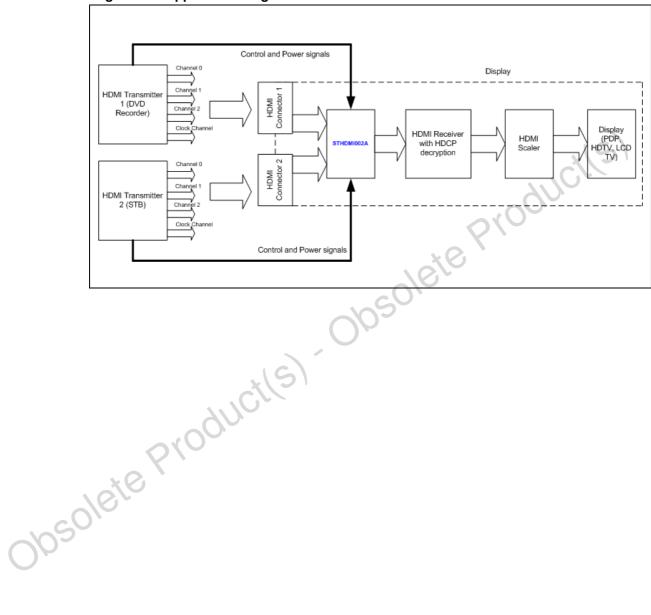

# 3 Application diagram

Figure 2. Application diagram

STHDMI002A Pin configuration

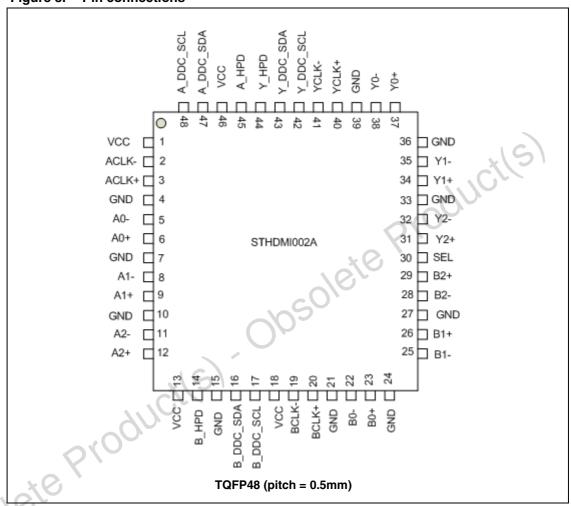

# 4 Pin configuration

Figure 3. Pin connections

7/26

Pin configuration STHDMI002A

Table 1. Pin description

| iable 1. Pi | Table 1. Pin description |        |                                                 |  |  |  |

|-------------|--------------------------|--------|-------------------------------------------------|--|--|--|

| Pin number  | Pin Name                 | Туре   | Function                                        |  |  |  |

| 1           | VCC                      | Power  | Supply voltage (3.3V ± 5%)                      |  |  |  |

| 2           | ACLK-                    | Input  | TMDS Clock- for port A                          |  |  |  |

| 3           | ACLK+                    | Input  | TMDS Clock+ for port A                          |  |  |  |

| 4           | GND                      | Power  | Ground                                          |  |  |  |

| 5           | A0-                      | Input  | TMDS Data 0- for port A                         |  |  |  |

| 6           | A0+                      | Input  | TMDS Data 0+ for port A                         |  |  |  |

| 7           | GND                      | Power  | Ground                                          |  |  |  |

| 8           | A1-                      | Input  | TMDS Data 1- for port A                         |  |  |  |

| 9           | A1+                      | Input  | TMDS Data 1+ for port A                         |  |  |  |

| 10          | GND                      | Power  | Ground                                          |  |  |  |

| 11          | A2-                      | Input  | TMDS Data 2- for port A                         |  |  |  |

| 12          | A2+                      | Input  | TMDS Data 2+ for port A                         |  |  |  |

| 13          | VCC                      | Power  | Supply voltage (3.3V ± 5%)                      |  |  |  |

| 14          | B_HPD                    | Output | Hot Plug Detect (HPD) output for port B         |  |  |  |

| 15          | GND                      | Power  | Ground                                          |  |  |  |

| 16          | B_DDC_SDA                | I/O    | DDC SDA input for port B                        |  |  |  |

| 17          | B_DDC_SCL                | C 1/O  | DDC SCL input for port B                        |  |  |  |

| 18          | VCC                      | Power  | Supply voltage (3.3V ± 5%)                      |  |  |  |

| 19          | BCLK-                    | Input  | TMDS Clock- for port B                          |  |  |  |

| 20          | BCLK+                    | Input  | TMDS Clock+ for port B                          |  |  |  |

| 21          | GND                      | Power  | Ground                                          |  |  |  |

| 22          | В0-                      | Input  | TMDS Data 0- for port B                         |  |  |  |

| 23          | B0+                      | Input  | TMDS Data 0+ for port B                         |  |  |  |

| 24          | GND                      | Power  | Ground                                          |  |  |  |

| 25          | B1-                      | Input  | TMDS Data 1- for port B                         |  |  |  |

| 26          | B1+                      | Input  | TMDS Data 1+ for port B                         |  |  |  |

| 27          | GND                      | Power  | Ground                                          |  |  |  |

| 28          | B2-                      | Input  | TMDS Data 2- for port B                         |  |  |  |

| 29          | B2+                      | Input  | TMDS Data 2+ for port B                         |  |  |  |

| 30          | SEL                      | Input  | Select control input to select port A or port B |  |  |  |

| 31          | Y2+                      | Output | TMDS Data2+ output                              |  |  |  |

| 32          | Y2-                      | Output | TMDS Data2- output                              |  |  |  |

| 33          | GND                      | Power  | Ground                                          |  |  |  |

| 34          | Y1+                      | Output | TMDS Data1+ output                              |  |  |  |

STHDMI002A Pin configuration

Table 1. Pin description

| Pin number | Pin name  | Туре   | Function                                                                                                                                                                            |

|------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35         | Y1-       | Output | TMDS Data1- output                                                                                                                                                                  |

| 36         | GND       | Power  | Ground                                                                                                                                                                              |

| 37         | Y0+       | Output | TMDS Data0+ output                                                                                                                                                                  |

| 38         | Y0-       | Output | TMDS Data0- output                                                                                                                                                                  |

| 39         | GND       | Power  | Ground                                                                                                                                                                              |

| 40         | YCLK+     | Output | TMDS Clock+ output                                                                                                                                                                  |

| 41         | YCLK-     | Output | TMDS Clock- output                                                                                                                                                                  |

| 42         | Y_DDC_SCL | I/O    | DDC SCL output                                                                                                                                                                      |

| 43         | Y_DDC_SDA | I/O    | DDC SDA output                                                                                                                                                                      |

| 44         | Y_HPD     | Input  | Sink side hot plug detector input High: 5V power signal asserted from source to sink and EDID is ready Low: No 5V power signal is asserted from source to sink or EDID is not ready |

| 45         | A_HPD     | Output | Hot Plug Detect (HPD) output for port A                                                                                                                                             |

| 46         | VCC       | Power  | Supply voltage (3.3V ± 5%)                                                                                                                                                          |

| 47         | A_DDC_SDA | 1/0    | DDC SDA input for port A                                                                                                                                                            |

| 48         | A_DDC_SCL | 1/0    | DDC SCL input for port A                                                                                                                                                            |

# 4.1 Function table

Table 2. Function table

| SEL | Signal status                  | DDC Status            | HPD Status            |

|-----|--------------------------------|-----------------------|-----------------------|

| C.E | Y= TMDS Data, Clock for port A | Y = DDC for port A    | Y= HPD for port A     |

|     | Port B is in 'Z' state         | DDC for port B is 'Z' | HPD for port B is 'Z' |

| Н   | Y=TMDS Data, Clock for port B  | Y = DDC for port B    | Y= HPD for port B     |

|     | Port A is in 'Z' state         | DDC for port A is 'Z' | HPD for port A is 'Z' |

Maximum rating STHDMI002A

# 5 Maximum rating

Stressing the device above the rating listed in the "absolute maximum ratings" table may cause permanent damage to the device. these are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Refer also to the STMicroelectronics sure program and other relevant quality documents.

Table 3. Absolute maximum ratings

| Symbol           | Parameter                                                           |                   | Value        | Unit |

|------------------|---------------------------------------------------------------------|-------------------|--------------|------|

| V <sub>CC</sub>  | Supply voltage to Ground                                            |                   | -0.5 to +4.0 | V    |

|                  | DC Input Voltage (TMDS A,B ports)                                   |                   | 1.7 to +4.0  | V    |

| VI               | SEL                                                                 | -0.5 to +4.0      | V            |      |

| ·                | A_DDC_SDA, A_DDC_SCL, B_DDC_SDA<br>Y_DDC_SDA, Y_DDC_SCL, Y_HPD, A_H | -0.5 to +6.0      | V            |      |

| V <sub>IC</sub>  | DC control input voltage                                            | 3/8               | -0.5 to +4.0 | V    |

| I <sub>O</sub>   | DC output current                                                   | Ole,              | 120          | mA   |

| T <sub>STG</sub> | Storage temperature                                                 |                   | -65 to +150  | °C   |

| T <sub>L</sub>   | Lead temperature (10 sec)                                           |                   | 300          | °C   |

| V <sub>ESD</sub> | Flactrostatia diagharga valtaga an IOc(1)1                          | Human body model  | -2 to +2     | kV   |

| *ESD             | Electrostatic discharge voltage on IOs <sup>(1)1</sup>              | Contact discharge | -2 to +2     | kV   |

<sup>1.</sup> In accordance with the MIL STD 883 method 3015

Table 4. Thermal data

| Symbol            | Description                         | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal Resistance Junction-ambient | TBA   | °C/W |

STHDMI002A DC electrical characteristics

# 6 DC electrical characteristics

$T_A = -40 \text{ to } +85 \text{ °C}, V_{CC} = 3.3V \pm 5\%$

Table 5. DC electrical characteristics

| Symbol               | Parameter                                                                               | Test conditions                                                                              | Min  | Тур        | Max  | Unit     |

|----------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------|------------|------|----------|

| V <sub>IH</sub>      | HIGH level input voltage (SEL pin)                                                      | High level guaranteed                                                                        | 2.0  |            |      | ٧        |

| V <sub>IL</sub>      | LOW level input voltage (SEL pin)                                                       | Low level guaranteed                                                                         | -0.5 |            | 0.8  | ٧        |

| V <sub>IK</sub>      | Clamp Diode voltage (All IOs)                                                           | V <sub>CC</sub> = 3.465V, I <sub>IN</sub> = -18mA                                            |      | -0.8       | -1.2 | ٧        |

| I <sub>IH</sub>      | Input high current (SEL pin, A, B data ports)                                           | V <sub>CC</sub> = 3.465V, V <sub>IN</sub> = V <sub>CC</sub>                                  |      |            | ±5   | μΑ       |

| I <sub>IL</sub>      | Input low current (SEL pin, A, B data ports)                                            | V <sub>CC</sub> = 3.465V, V <sub>IN</sub> = GND                                              |      | <i>'</i> C | ±5   | μΑ       |

| I <sub>OFF</sub>     | Power down leakage current                                                              | $V_{CC} = 0V;$ Outputs (Y-port) = 0V; Inputs (A-port) = 3.465V; Inputs (B-port) = 3.465V     | 000  |            | ±5   | μΑ       |

| R <sub>ON</sub>      | Switch ON resistance <sup>(1)</sup>                                                     | $V_{CC} = 3.135 \text{ V},$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -40 \text{mA}$       |      | 5.5        | 7.5  | Ω        |

| R <sub>FLAT</sub>    | ON resistance flatness <sup>(1)</sup> <sup>(2)</sup>                                    | $V_{CC} = 3.135 \text{ V},$ $V_{IN} = 1.5 \text{ to } V_{CC}$ $I_{IN} = -40 \text{mA}$       |      | 0.8        |      | Ω        |

| ΔR <sub>ON</sub>     | ON resistance match between channels $\Delta R_{ON} = R_{ONMAX} - R_{ONMIN}^{~(1)~(3)}$ | $V_{CC} = 3.135 \text{ V},$<br>$V_{IN} = 1.5 \text{ to } V_{CC}$<br>$I_{IN} = -40 \text{mA}$ |      | 1.0        | 1.3  | Ω        |

| DDC I/O I            | Pins                                                                                    |                                                                                              |      |            |      |          |

| I <sub>I(leak)</sub> | Input leakage current                                                                   | $V_{CC} = 3.465V$ $V_{I}$ (max) = 5.3V on isolated DDC ports $Y = 0.0V$                      |      | 0.1        | +2   | μΑ       |

| I <sub>OFF</sub>     | Power down leakage current                                                              | $V_{CC} = 0V;$ Outputs (Y-port) = 0V; Inputs (A-port) = 5.3V; Inputs (B-port) = 5.3V         |      |            | ±5   | μΑ       |

| C <sub>I/O</sub>     | Switch off capacitance Switch on capacitance                                            | $V_I$ =0V, $V_{CC}$ =3.3V, T= 25°C<br>F = 1 MHz                                              |      | 5<br>9     |      | pF<br>pF |

11/26

DC electrical characteristics STHDMI002A

Table 5. DC electrical characteristics

| Symbol               | Parameter                                    | Test conditions                                                                            | Min | Тур    | Max | Unit     |

|----------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|-----|--------|-----|----------|

|                      |                                              | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 0.0V$                                             |     | 32     |     | Ω        |

| Б                    | Outline and internal                         | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 0.4V$                                             |     | 36     |     | Ω        |

| R <sub>ON</sub>      | Switch resistance                            | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 0.8V$                                             |     | 42     |     | Ω        |

|                      |                                              | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 1.5V$                                             |     | 62     |     | Ω        |

| Status pi            | ns (Y_HPD)                                   |                                                                                            |     |        |     | )        |

| I <sub>I(leak)</sub> | Input leakage current                        | V <sub>CC</sub> = 3.465V<br>V <sub>I</sub> (max) = 5.3V on<br>isolated HPD port<br>Y= 0.0V | (OG | 0.1    | +2  | μΑ       |

| l <sub>OFF</sub>     | Power down leakage current                   | V <sub>CC</sub> = 0V;<br>(Y-port) = 0V;<br>(A-port) = 5.3V;<br>(B-port) = 5.3V             |     |        | ±5  | μА       |

| Status pi            | ns (A_HPD, B_HPD)                            |                                                                                            |     |        |     |          |

| C <sub>I/O</sub>     | Switch off capacitance Switch on capacitance | V <sub>I</sub> =0V, V <sub>CC</sub> =3.3V, T= 25°C<br>F = 1 MHz                            |     | 5<br>9 |     | pF<br>pF |

| В                    | individual series                            | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 0.0V$                                             |     | 24     |     | Ω        |

| R <sub>ON</sub>      | Switch resistance                            | $V_{CC} = 3.3V$<br>$I_{O} = 3mA; V_{O} = 5.0V$                                             |     | 150    |     | Ω        |

Measured by voltage drop between channels at the indicated current through the switch. On-resistance is determined by the lower of the two voltages.

<sup>2.</sup> Flatness is defined as the difference between the  $R_{\mbox{\scriptsize ONMAX}}$  and the  $R_{\mbox{\scriptsize ONMIN}}$  of the on resistance over the specified range.

<sup>3.</sup>  $\Delta R_{ON}$  measured at the same  $V_{CC}$ , temperature and voltage level.

STHDMI002A DC electrical characteristics

#### 6.1 **Capacitance**

$T_A = 25^{\circ}C$ , f = 1MHz

Table 6. Capacitance

| Symbol           | Parameter                                      | Test conditions | Min | Тур | Max | Unit |

|------------------|------------------------------------------------|-----------------|-----|-----|-----|------|

| C <sub>IN</sub>  | Input capacitance                              | $V_{IN} = 0V$   |     | 2   | 3   | pF   |

| C <sub>OFF</sub> | Port x0 to Port x1, Switch off (Note 4)        | $V_{IN} = 0V$   |     | 4   | 6   | pF   |

| C <sub>ON</sub>  | Capacitance switch on (x to x0 or x to x1) (1) | $V_{IN} = 0V$   |     | 6   | 12  | pF   |

<sup>1.</sup> x = Port Y; x0 = Port A; x1 = Port B

#### 6.2 **Power supply characteristics**

Table 7. Power supply characteristics

| 1. x = Por                       | t Y; x0 = Port A; x1 = Port B                |                                                              |     |     |     |      |

|----------------------------------|----------------------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| 6.2 Power supply characteristics |                                              |                                                              |     |     |     |      |

|                                  | $T_A = -40 \text{ to } +85 ^{\circ}\text{C}$ |                                                              |     | 90  |     |      |

| Table 7.                         | Power supply characteristics                 |                                                              | 2/0 | )   |     |      |

| Symbol                           | Parameter                                    | Test conditions                                              | Min | Тур | Max | Unit |

| I <sub>cc</sub>                  | Quiescent power supply current               | $V_{CC} = 3.465 \text{ V},$ $V_{IN} = V_{CC} \text{ or GND}$ |     | 50  | 500 | μА   |

#### **Dynamic electrical characteristics** 6.3

$T_A = -40 \text{ to } +85 \,^{\circ}\text{C}, \, V_{CC} = 3.3 \text{V} \pm 5\%$

Table 8. Dynamic electrical characteristics

| Symbol            | Parameter                       | Test conditions                  | Min | Тур  | Max | Unit |

|-------------------|---------------------------------|----------------------------------|-----|------|-----|------|

| X <sub>TALK</sub> | Non-adjacent channel Cross-talk | $R_L = 100\Omega, f = 370MHz$    |     | -32  |     | dB   |

|                   | .*8                             | $R_L = 100\Omega$ , $f = 825MHz$ |     | -31  |     | dB   |

| O <sub>IRR</sub>  | Off Isolation                   | $R_L = 100\Omega, f = 370MHz$    |     | -36  |     | dB   |

| ~SU               |                                 | $R_L = 100\Omega, f = 825MHz$    |     | -30  |     | dB   |

| BW                | -3dB bandwidth                  |                                  |     | 850  |     | MHz  |

| D <sub>R</sub>    | Data rate per channel           |                                  |     | 1.65 |     | Gbps |

DC electrical characteristics STHDMI002A

## 6.4 Dynamic switching characteristics

$T_A$  = -40 to +85 °C,  $V_{CC}$  = 3.3V  $\pm$  5%

Table 9. Dynamic switching characteristics

| Symbol                              | Parameter                                                                                                                         | Test conditions                      | Min | Тур  | Max | Unit |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|------|-----|------|--|

| t <sub>PD</sub>                     | Propagation delay                                                                                                                 | V <sub>CC</sub> = 3.135V to 3.465V   |     | 0.30 |     | ns   |  |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Line Enable Time, SEL to x to x0 or x to x1                                                                                       | V <sub>CC</sub> = 3.135V to 3.465V   | 0.5 | 6.5  | 9   | ns   |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Line Disable Time, SEL to x to x0 or x to x1                                                                                      | V <sub>CC</sub> = 3.135V to 3.465V   | 0.5 | 6.5  | 8.5 | ns   |  |

| t <sub>SK(O)</sub>                  | Output skew between center port to any other port                                                                                 | V <sub>CC</sub> = 3.135V to 3.465V   |     | 0.1  | 0.2 | ns   |  |

| t <sub>SK(P)</sub>                  | Skew between opposite transition of the same output (t <sub>PHL</sub> - t <sub>PLH)</sub>                                         | V <sub>CC</sub> = 3.135V to 3.465V   |     | 0.1  | 0.2 | ns   |  |

| DDC I/O p                           | DDC I/O pins                                                                                                                      |                                      |     |      |     |      |  |

| t <sub>PD(DDC)</sub>                | Propagation delay from A_DDC_SDA/ B_DDC_SDA to Y_DDC_SDA or A_DDC_SCL/B_DDC_SCL to Y_DDC_SCL or Y_DDC_SDA to A_DDC_SDA/ B_DDC_SDA | C <sub>L</sub> = 10pF                |     |      | 2.5 | ns   |  |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Line Enable Time, SEL to x to x0 or x to x1                                                                                       | V <sub>CC</sub> = 3.135V to 3.465V   |     | 6.5  | 9   | ns   |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Line Disable Time, SEL to x to x0 or x to x1                                                                                      | $V_{CC} = 3.135V \text{ to } 3.465V$ |     | 6.5  | 8.5 | ns   |  |

| Status pins (Y_HPD, A_HPD, B_HPD)   |                                                                                                                                   |                                      |     |      |     |      |  |

| t <sub>PD(HPD)</sub>                | Propagation delay (from Y_HPD to the active port of HPD)                                                                          | C <sub>L</sub> = 10pF                |     |      | 2.5 | ns   |  |

| t <sub>PZH</sub> , t <sub>PZL</sub> | Line Enable Time, SEL to x to x0 or x to x1                                                                                       | V <sub>CC</sub> = 3.135V to 3.465V   |     | 6.5  | 9   | ns   |  |

| t <sub>PHZ</sub> , t <sub>PLZ</sub> | Line Disable Time, SEL to x to x0 or x to x1                                                                                      | V <sub>CC</sub> = 3.135V to 3.465V   |     | 6.5  | 8.5 | ns   |  |

Note: x = Port Y; x0 = Port A; x1 = Port B

## 6.5 ESD performance

Table 10. ESD performance

| Symbol | Parameter                          | Test conditions        | Min | Тур       | Max | Unit |

|--------|------------------------------------|------------------------|-----|-----------|-----|------|

| ESD    | MIL STD 883 method 3015 (all pins) | Human Body Model (HBM) |     | <u>±2</u> |     | kV   |

## 7 Test circuit for electrical characteristics

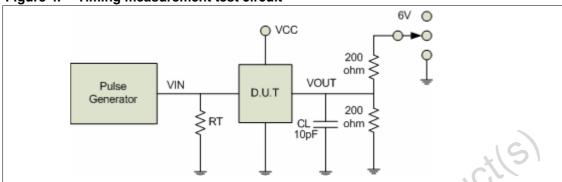

Figure 4. Timing measurement test circuit

Note: 1 CL = Load capacitance: includes jig and probe capacitance.

2 RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

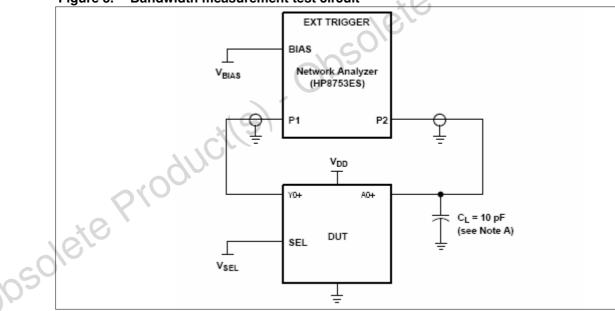

Figure 5. Bandwidth measurement test circuit

Note: C<sub>1</sub> includes probe and jig capacitance

Frequency response is measured at the output of the ON channel. For example, when VSEL = 0 and Y0+ is the input, the output is measured at A0+. All unused analog I/O ports are left open.

#### HP8753ES set up:

Average = 4

RBW = 3kHz

VBIAS = 0.35V

ST = 2s

P1 = 0dBm

EXT TRIGGER BIAS  $\mathsf{L}$ Network Analyzer VBIAS (HP8753ES)  $V_{DD}$ Y0+ A0+ Y0-A0-BO+ BO-DUT A1+ B 1+ B 1-

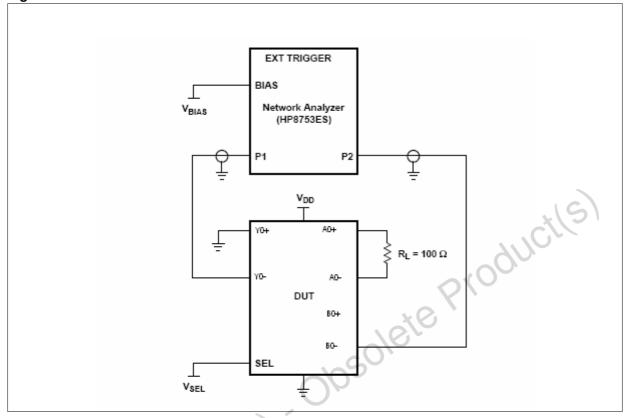

Figure 6. Crosstalk measurement test circuit

Note: 1 CL includes probe and jig capacitance

2 A 50 $\Omega$  termination resistor is needed to match the loading network analyzer

Crosstalk is measured at the output of the non-adjacent ON channel. For example, when VSEL = 0, and Y0- is the input, the output is measured at Y1-. All unused analog input ports (Y) are connected to GND and output ports (A,B) are left open.

#### HP8753ES set up:

Average = 4

RBW = 3kHz

VBIAS = 0.35V

ST = 2s

P1 = 0dBm

Figure 7. Off-isolation measurement test circuit

Note: 1 CL includes probe and jig capacitance

2 A  $50\Omega$  termination resistor is needed to match the loading network analyzer

Off-isolation is measured at the output of the OFF channel. For example, when VSEL=0, and Y0- is the input, the output is measured at B0-. All unused analog input ports (Y) are connected to GND and output ports (A,B) are left open.

### HP8753ES set up:

Average = 4

RBW = 3kHz

VBIAS = 0.35V

ST = 2s

P1 = 0dBm

**57/**

Timing waveforms STHDMI002A

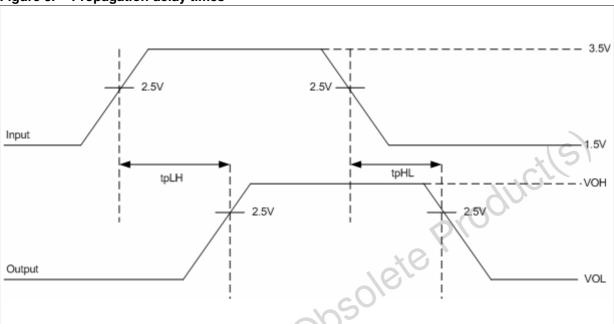

# 8 Timing waveforms

Figure 8. Propagation delay times

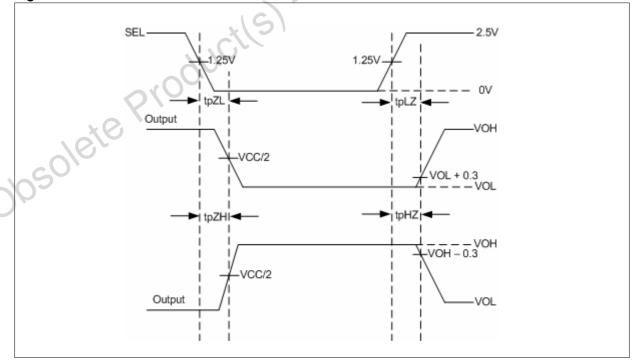

Figure 9. Enable and disable times

STHDMI002A Timing waveforms

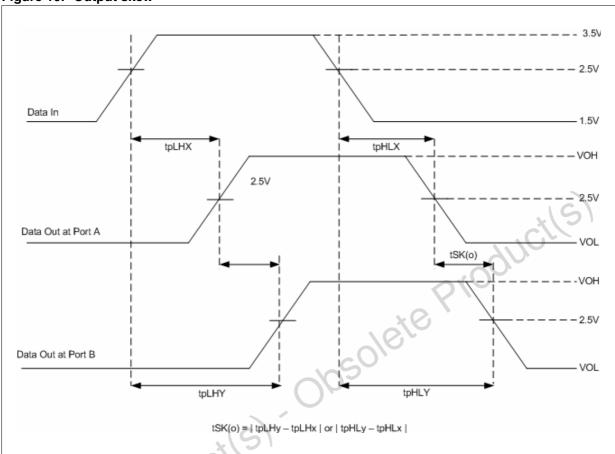

Figure 10. Output skew

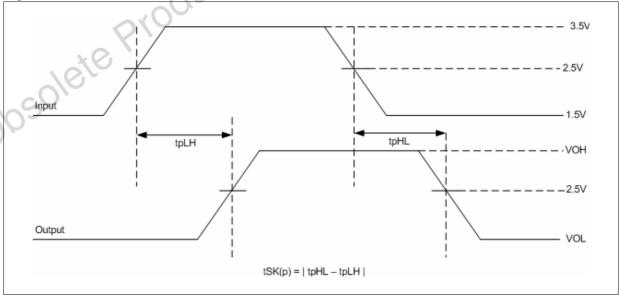

Figure 11. Pulse skew

**5**//

Application information STHDMI002A

# 9 Application information

### 9.1 Power supply sequencing

Proper power-supply sequencing is advised for all CMOS devices. It is recommended to always apply  $V_{CC}$  before applying any signals to the input/output or control pins.

### 9.2 Supply bypassing

Bypass each of the  $V_{CC}$  pins with  $0.1\mu F$  and 1nF capacitors in parallel as close to the device as possible, with the smaller-valued capacitor as close to the  $V_{CC}$  pin of the device as possible.

### 9.3 Differential traces

The high-speed TMDS inputs are the most critical parts for the device. There are several considerations to minimize discontinuities on these transmission lines between the connectors and the device.

- a) Maintain 100- $\Omega$  differential transmission line impedance into and out of the STHDMI002A.

- b) Keep an uninterrupted ground plane below the high-speed I/Os.

- c) Keep the ground-path vias to the device as close as possible to allow the shortest return current path.

- Layout of the TMDS differential inputs should be with the shortest stubs from the connectors.

Output trace characteristics affect the performance of the STHDMI002A. Use controlled impedance traces to match trace impedance to both the transmission medium impedance and termination resistor. Run the differential traces close together to minimize the effects of the noise. Reduce skew by matching the electrical length of the traces. Avoid discontinuities in the differential trace layout. Avoid 90 degree turns and minimize the number of vias to further prevent impedance discontinuities.

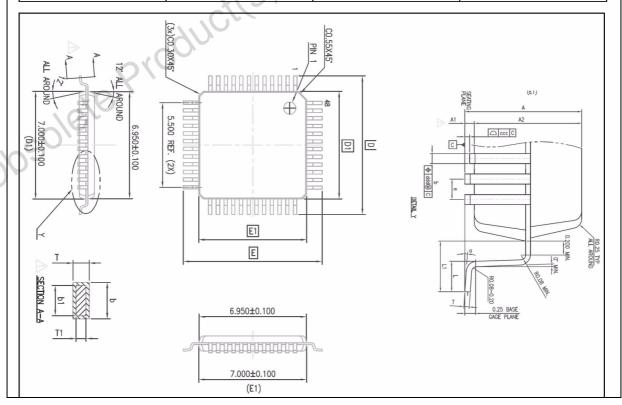

# 10 Package mechanical data

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a Lead-free second level interconnect . The category of second Level Interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label. ECOPACK is an ST trademark. ECOPACK specifications are available at: www.st.com.

Obsolete Product(s). Obsolete Product(s)

577

STHDMI002A

Figure 12. TQFP48 package dimensions

### **TQFP48 MECHANICAL DATA**

| DIM.      | mm.  |       |      |  |  |

|-----------|------|-------|------|--|--|

| DIWI.     | MIN. | TYP   | MAX. |  |  |

| Α         |      |       | 1.20 |  |  |

| A1        | 0.05 | 0.10  | 0.15 |  |  |

| A2        | 0.95 | 1.00  | 1.05 |  |  |

| D         | 8.80 | 9.00  | 9.20 |  |  |

| D1        | 6.90 | 7.00  | 7.10 |  |  |

| E         | 8.80 | 9.00  | 9.20 |  |  |

| E1        | 6.90 | 7.00  | 7.10 |  |  |

| L         | 0.45 | 0.60  | 0.75 |  |  |

| L1        |      | 1.00  | (0   |  |  |

| Т         | 0.70 | 0.15  | 0.20 |  |  |

| T1        | 0.10 | 0.13  | 1.15 |  |  |

| а         | 0°   | -0/6  | 7°   |  |  |

| b         | 0.17 | 0.22  | 0.27 |  |  |

| b1        | 0.17 | 0.20  | 0.23 |  |  |

| е         |      | 0.500 |      |  |  |

| ccc / ddd | 16   | 0.08  |      |  |  |

**5**//

STHDMI002A

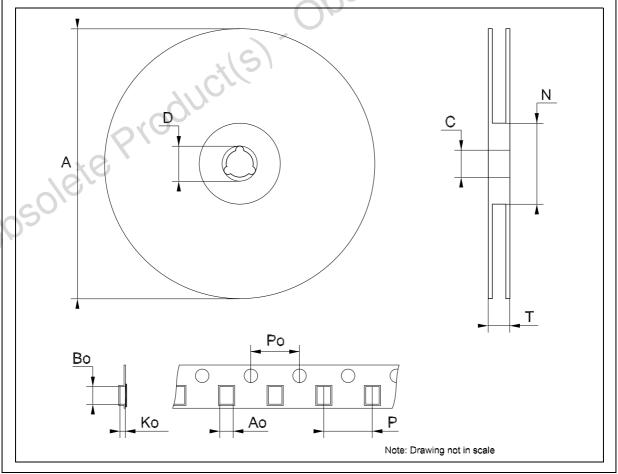

Figure 13. TQFP48 Tape and reel dimensions

# Tape & Reel TQFP48 MECHANICAL DATA

| DIM  |      | mm. |      | inch  |      |        |

|------|------|-----|------|-------|------|--------|

| DIM. | MIN. | ТҮР | MAX. | MIN.  | TYP. | MAX.   |

| А    |      |     | 330  |       |      | 12.992 |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |     |      | 0.795 |      |        |

| N    | 60   |     |      | 2.362 |      | *(8)   |

| Т    |      |     | 22.4 |       | 11   | 0.882  |

| Ao   | 9.5  |     | 9.7  | 0.374 | .00, | 0.382  |

| Во   | 9.5  |     | 9.7  | 0.374 | 2/0  | 0.382  |

| Ko   | 2.1  |     | 2.3  | 0.083 |      | 0.091  |

| Po   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р    | 11.9 |     | 12.1 | 0.468 |      | 0.476  |

23/26

Order codes STHDMI002A

## 11 Order codes

Table 11. Order codes

| Part number   | Temperature range | Package | Packing       |

|---------------|-------------------|---------|---------------|

| STHDMI002ABTR | –65° C to +150° C | TQFP48  | Tape and reel |

Obsolete Product(s). Obsolete Product(s)

STHDMI002A Revision history

# 12 Revision history

Table 12. Revision history

| Date        | Revision | Change        |

|-------------|----------|---------------|

| 10-Oct-2006 | 1        | First release |

Obsolete Product(s). Obsolete Product(s)

5/