# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### +3.3V PROGRAMMABLE LVDS TRANSMITTER 24-BIT FLAT PANEL DISPLAY (FPD) LINK-85MHZ

- 20 TO 85 MHz SHIFT CLOCK SUPPORT

- BEST-IN-CLASS SET & HOLD TIMES ON TxINPUTs

- Tx POWER CONSUMPTION <130 mW (typ) @85MHz GRAYSCALE

- Tx POWER-DOWN MODE <200µW (max)

- SUPPORTS VGA, SVGA, XGA aND SINGLE/ DUAL PIXEL SXGA.

- NARROW BUS REDUCES CABLE SIZE AND COST

- UP TO 2.38 Gbps THROUGHPUT

- UP TO 297.5 Megabytes/sec BANDWIDTH

- 345 mV (typ) SWING LVDS DEVICES FOR LOW EMI

- PLL REQUIRES NO EXTERNAL COMPONENTS

- COMPATIBLE WITH TIA/EIA -644 LVDS STANDARD

#### DESCRIPTION

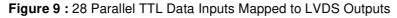

The STLVDS385 transmitter converts 28 bits of LVCMOS/LVTTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS

#### **ORDERING CODES**

link. Every cycle of the transmit clock 28 bits of input data are sampled and transmitted. At a transmit clock frequency of 85 MHz, 24 bits of RGB data and 3 bits of LCD timing and control data (FPLINE, FPFRAME, DRDY) are transmitted at a rate of 595 Mbps per LVDS data channel. Using a 85 MHz clock, the data throughput is 297.5 Mbytes/sec. The transmitter can be programmed for Rising edge strobe or Falling edge strobe through a dedicated pin. A Rising edge or Falling edge strobe transmitter will inter operate with a Falling edge strobe Receiver without any translation logic.

| Туре         | Temperature<br>Range | Package               | Comments            |

|--------------|----------------------|-----------------------|---------------------|

| STLVDS385BTR | -10 to 70°C          | TSSOP56 (Tape & Reel) | 2000 parts per reel |

#### **PIN CONFIGURATION**

| v <sub>cc</sub> | I  | 1  | 56     | ] TxIN4                |

|-----------------|----|----|--------|------------------------|

| TxIN            |    | 2  | 55     | ] TxIN3                |

| TxIN            | .  | 3  | 54     | ] TxIN2                |

| TxIN            |    | 4  | 53     | ] GND                  |

| GND             |    | 5  | 52     | ] TxIN1                |

| TxIN            | .  | 6  | 51     | ] T×IN0                |

| T×IN            |    | 7  | 50     | ] T×IN27               |

| TxIN            | 0  | 8  | 49     | ] LVDS GND             |

| v <sub>cc</sub> |    | 9  | 48     | ] TxOUTO-              |

| TxIN            | 1  | 10 | 47     | ] TxOUTO+              |

| Txin            | 2  | 11 | 46     | ] TxOUT1-              |

| TxiN            | 3  | 12 | 45     | ] Tx0UT1+              |

| GND             |    | 13 | 44     | ] LVDS V <sub>CC</sub> |

| TxIN            | 4  | 14 | 43     | ] LVDS GND             |

| TxIN            | 5  | 15 | 42     | ] TxOUT2-              |

| TxIN            | 6  | 16 | 41     | ] TxOUT2+              |

| R_FI            |    | 17 | 40     | ] TxCLKOUT-            |

| TxIN            | 7  | 18 | 39     | ] TxCLKOUT+            |

| TxIN            | 8  | 19 | 38     | ] TxOUT3-              |

| TxIN            | 9  | 20 | 37     | ] TxOUT3+              |

| GND             |    | 21 | 36     | ] LVDS GND             |

| TxIN            | :0 | 22 | 35     | ] PLL GND              |

| T×IN            | :1 | 23 | 34     | ] PLL V <sub>cc</sub>  |

| TxIN            | 2  | 24 | 33     | ] PLL GND              |

| TxIN            | 3  | 25 | 32     | ] PWR DWN              |

| V <sub>cc</sub> |    | 26 | 31     | ] TxCLK IN             |

| TxIN            | 4  | 27 | 30     | ] TxIN26               |

| TxIN            | 5  | 28 | 29     | ] GND                  |

|                 |    | Lc | S13880 |                        |

|                 |    |    |        |                        |

#### **PIN DESCRIPTION**

| PIN N°                                                                                                            | SYMBOL               | NAME AND FUNCTION                                                                                                                                           |

|-------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9, 26                                                                                                          | V <sub>CC</sub>      | Power Supply pins for TTL Inputs                                                                                                                            |

| 2, 3, 4, 6, 7, 8, 10, 11, 12,<br>14, 15, 16, 18, 19, 20, 22,<br>23, 24, 25, 27, 28, 30, 50,<br>51, 52, 54, 55, 56 | T <sub>X</sub> IN    | TTL level input. This includes: 8 Red, 8 Green, 8 Blue and 4 control lines-<br>FPLINE, FPFRAME, and DRDY (also referred to as HSYNC, VSYNC,<br>Data Enable) |

| 5, 13, 21, 29                                                                                                     | GND                  | Ground pins for TTL Inputs                                                                                                                                  |

| 17                                                                                                                | R_FB                 | Programmable strobe select (See Table 1)                                                                                                                    |

| 31                                                                                                                | TxCLKIN              | TTL level clock input. Pin name TxCLK IN                                                                                                                    |

| 32                                                                                                                | PWRDWN               | TTL level input. When asserted (low input) TRI-STATES the outputs, ensuring low current at power down                                                       |

| 33, 35                                                                                                            | PLL GND              | Ground pins for PLL                                                                                                                                         |

| 34                                                                                                                | PLL V <sub>CC</sub>  | Power Supply pin for PLL                                                                                                                                    |

| 36, 43, 49                                                                                                        | LVDS GND             | Ground pins for LVDS outputs                                                                                                                                |

| 37, 41, 45, 47                                                                                                    | TxOUT+               | Positive LVDS differential data output                                                                                                                      |

| 38, 42, 46, 48                                                                                                    | TxOUT-               | Negative LVDS differential data output                                                                                                                      |

| 39                                                                                                                | TxCLK OUT+           | Positive LVDS differential clock output                                                                                                                     |

| 40                                                                                                                | TxCLK OUT-           | Negative LVDS differential clock output                                                                                                                     |

| 44                                                                                                                | LVDS V <sub>CC</sub> | Power Supply pin for LVDS outputs                                                                                                                           |

| 2/14                                                                                                              |                      |                                                                                                                                                             |

#### **TABLE 1 PROGRAMMABLE TRANSMITTER**

| PIN  | CONDITION              | STROBE STATUS       |

|------|------------------------|---------------------|

| R_FB | R_FB = V <sub>CC</sub> | Rising edge strobe  |

| R_FB | R_FB = GND or NC       | Falling edge strobe |

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                          | Value                           | Unit |

|------------------|------------------------------------|---------------------------------|------|

| V <sub>CC</sub>  | Supply Voltage                     | -0.3 to 4                       | V    |

| VI               | CMOS/TTL Input Voltage             | -0.5 to (V <sub>CC</sub> + 0.3) | V    |

| V <sub>DO</sub>  | LVDS Driver Output Voltage         | -0.3 to (V <sub>CC</sub> + 0.3) | V    |

| I <sub>OSD</sub> | LVDS Output Short Circuit Duration | Continuous                      |      |

| ESD              | НВМ                                | 7                               | KV   |

|                  | EIAJ                               | 500                             | V    |

| ILATCH           | Latch Up Tolerance                 | ± 300                           | mA   |

| ТJ               | Junction Temperature               | +150                            | °C   |

| T <sub>stg</sub> | Storage Temperature Range          | -65 to +150                     | °C   |

Absolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

#### **RECOMMENDED OPERATING CONDITIONS**

| Symbol               | Parameter                      | Min. | Тур. | Max. | Unit             |

|----------------------|--------------------------------|------|------|------|------------------|

| V <sub>CC</sub>      | Supply Voltage                 | 3.0  | 3.3  | 3.6  | V                |

| T <sub>A</sub>       | Operating Free Air Temperature | 0    |      | 70   | °C               |

| $\Delta V_{CC}$      | Supply Noise Voltage           |      |      | 100  | mV <sub>PP</sub> |

| f <sub>TxCLKIN</sub> | TxCLKIN frequency              | 20   |      | 85   | MHz              |

## **RECOMMENDED TRANSMITTER INPUT CHARACTERISTICS** ( $V_{CC}$ = 3.3V, $T_J$ = -10 to 70°C unless otherwise noted. Typical values are referred to $T_A$ = 25°C)

| Symbol           | Parameter                         | Min.  | Тур. | Max.  | Unit |

|------------------|-----------------------------------|-------|------|-------|------|

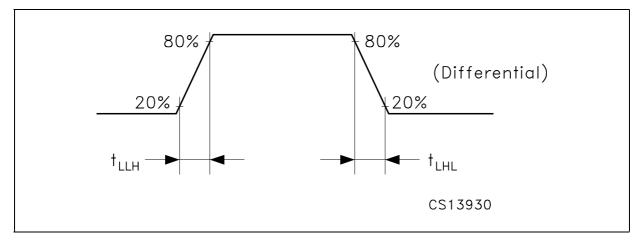

| t <sub>CIT</sub> | TxCLK IN Transition Time (Fig. 5) | 1.0   |      | 6.0   | ns   |

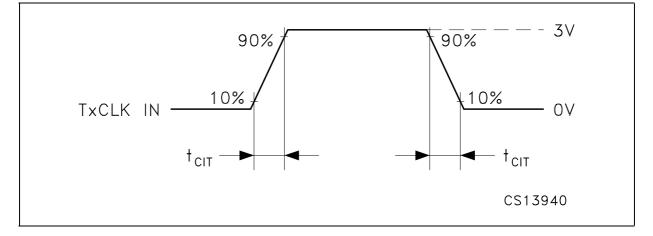

| t <sub>CIP</sub> | TxCLK IN Period (Fig. 6)          | 11.76 | Т    | 50    | ns   |

| t <sub>CIH</sub> | TxCLK IN High Time (Fig. 6)       | 0.35T | 0.5T | 0.65T | ns   |

| t <sub>CIL</sub> | TxCLK IN Low Time (Fig. 6)        | 0.35T | 0.5T | 0.65T | ns   |

| t <sub>XIT</sub> | TxIN Transition Time              | 1.5   |      | 6.0   | ns   |

#### **ELECTRICAL CHARACTERISTICS**

**LVCMOS/LVTTL DC SPECIFICATIONS** ( $V_{CC}$  = 3.3V,  $T_J$  = -10 to 70°C unless otherwise noted. Typical values are referred to  $T_A$  = 25°C)

| Symbol          | Parameter                | Test Conditions                               | Min. | Тур.  | Max.            | Unit |

|-----------------|--------------------------|-----------------------------------------------|------|-------|-----------------|------|

| V <sub>IH</sub> | High Level Input Voltage |                                               | 2.0  |       | V <sub>CC</sub> | mV   |

| V <sub>IL</sub> | Low Level Input Voltage  |                                               | GND  |       | 0.8             | mV   |

| V <sub>CL</sub> | Input Clamp Voltage      | I <sub>CL</sub> = -18mA                       |      | -0.79 | -1.5            | V    |

| l <sub>l</sub>  | Input Current            | V <sub>I</sub> =0.4 V, 2.5 or V <sub>CC</sub> |      |       | 10              | μA   |

|                 |                          | V <sub>I</sub> = GND                          | -10  | 0     |                 | μA   |

|--|

# **LVDS DC SPECIFICATIONS** (V<sub>CC</sub> = 3.3V, T<sub>J</sub> = -10 to 70°C unless otherwise noted. Typical values are referred to T<sub>A</sub> = 25°C)

| Symbol          | Parameter                                                           | Test Conditions                             | Min.  | Тур. | Max.  | Unit |

|-----------------|---------------------------------------------------------------------|---------------------------------------------|-------|------|-------|------|

| V <sub>OD</sub> | Differential Output Voltage                                         | R <sub>L</sub> = 100Ω                       | 250   | 345  | 450   | mV   |

| $\Delta V_{OD}$ | Change in V <sub>OD</sub> between<br>Complimentary Output<br>States | R <sub>L</sub> = 100Ω                       |       |      | 35    | mV   |

| V <sub>OS</sub> | Offset Voltage (Note 2)                                             | R <sub>L</sub> = 100Ω                       | 1.125 | 1.25 | 1.375 | V    |

| $\Delta V_{OS}$ | Change in V <sub>OS</sub> between<br>Complimentary Output<br>States | R <sub>L</sub> = 100Ω                       |       |      | 35    | mV   |

| I <sub>OS</sub> | Output Short Circuit Current                                        | $V_{O} = 0, \qquad R_{L} = 100\Omega$       |       | -3.5 | -5    | mA   |

| I <sub>OZ</sub> | Output Tri-State Current                                            | $POWERDOWN = 0, V_O = 0 \text{ or } V_{CC}$ |       | ±1   | ±10   | μΑ   |

**TRANSMITTER SUPPLY CURRENT** (V<sub>CC</sub> = 3.3V, T<sub>J</sub> = -10 to 70°C unless otherwise noted. Typical values are referred to T<sub>A</sub> = 25°C)

| Symbol | Parameter                                | Test Condition                                             | ons           | Min. | Тур. | Max. | Unit |

|--------|------------------------------------------|------------------------------------------------------------|---------------|------|------|------|------|

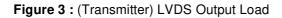

| ICCTW  | Transmitter Supply Current               | $R_{L} = 100\Omega, C_{L} = 5pF,$                          | f = 32.5 MHz  |      | 31   | 45   | mA   |

|        | Worst Case                               | Worst Case Pattern                                         | f = 40 MHz    |      | 32   | 50   |      |

|        |                                          | (Fig. 1, 3)                                                | f = 65 MHz    |      | 37   | 55   |      |

|        |                                          |                                                            | f = 85 MHz    |      | 42   | 60   |      |

| ICCTG  | Transmitter Supply Current               | $R_L = 100\Omega, C_L = 5pF,$                              | f = 32.5 MHz  |      | 29   | 38   | mA   |

|        | 16 Grayscale                             | 16 Grayscale Pattern                                       | f = 40 MHz    |      | 30   | 40   |      |

|        |                                          | (Fig. 1, 3)                                                | f = 65 MHz    |      | 35   | 45   |      |

|        |                                          |                                                            | f = 85 MHz    |      | 39   | 50   |      |

| ICCTZ  | Transmitter Supply Current<br>Power Down | Powerdown = Low<br>Driver Outputs in Tri-Stat<br>Down Mode | e under Power |      | 10   | 55   | μA   |

**TRANSMITTER SWITCHING CHARACTERISTICS** ( $V_{CC}$  = 3.3V,  $T_{J}$  = -10 to 70°C unless otherwise noted. Typical values are referred to  $T_A = 25^{\circ}C$ )

| Symbol            | Parameter                                                        | Test<br>Conditions                     | Min.  | Тур.  | Max.  | Unit |

|-------------------|------------------------------------------------------------------|----------------------------------------|-------|-------|-------|------|

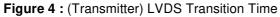

| t <sub>LLHT</sub> | LVDS Low-to-High Transition Time (Fig. 4)                        |                                        |       | 0.75  | 1.5   | ns   |

| t <sub>LLLT</sub> | LVDS High-to-Low Transition Time (Fig. 4)                        |                                        |       | 0.75  | 1.5   | ns   |

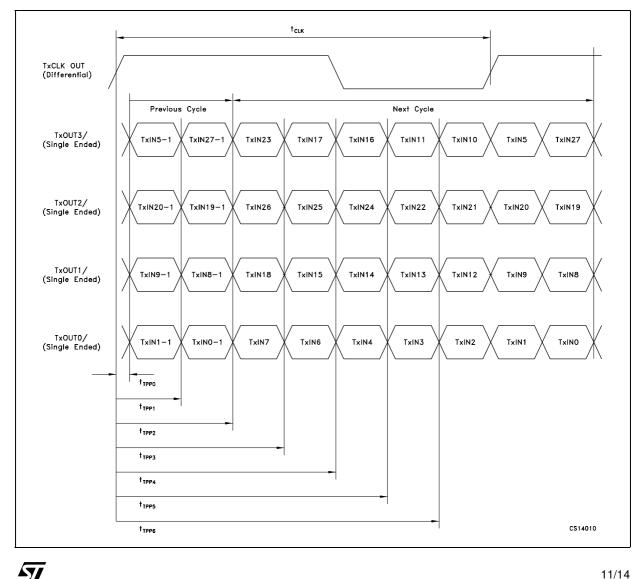

| t <sub>TPP0</sub> | Transmitter Output Pulse Position for BIT 0<br>(Fig.11 - Note 3) | f = 40 MHz                             | -0.25 | 0     | 0.25  | ns   |

| t <sub>TPP1</sub> | Transmitter Output Pulse Position for BIT 1                      |                                        | 3.32  | 3.57  | 3.82  | ns   |

| t <sub>TPP2</sub> | Transmitter Output Pulse Position for BIT 2                      |                                        | 6.89  | 7.14  | 7.39  | ns   |

| t <sub>TPP3</sub> | Transmitter Output Pulse Position for BIT 3                      |                                        | 10.46 | 10.71 | 10.96 | ns   |

| t <sub>TPP4</sub> | Transmitter Output Pulse Position for BIT 4                      |                                        | 14.04 | 14.29 | 14.54 | ns   |

| t <sub>TPP5</sub> | Transmitter Output Pulse Position for BIT 5                      |                                        | 17.61 | 17.86 | 18.11 | ns   |

| t <sub>TPP6</sub> | Transmitter Output Pulse Position for BIT 6                      |                                        | 21.18 | 21.43 | 21.68 | ns   |

| t <sub>TPP0</sub> | Transmitter Output Pulse Position for BIT 0<br>(Fig.11 - Note 3) | f = 65 MHz                             | -0.20 | 0     | 0.20  | ns   |

| t <sub>TPP1</sub> | Transmitter Output Pulse Position for BIT 1                      |                                        | 2.00  | 2.20  | 2.40  | ns   |

| t <sub>TPP2</sub> | Transmitter Output Pulse Position for BIT 2                      |                                        | 4.20  | 4.40  | 4.60  | ns   |

| t <sub>TPP3</sub> | Transmitter Output Pulse Position for BIT 3                      |                                        | 6.39  | 6.59  | 6.79  | ns   |

| t <sub>TPP4</sub> | Transmitter Output Pulse Position for BIT 4                      |                                        | 8.59  | 8.79  | 8.99  | ns   |

| t <sub>TPP5</sub> | Transmitter Output Pulse Position for BIT 5                      |                                        | 10.79 | 10.99 | 11.19 | ns   |

| t <sub>TPP6</sub> | Transmitter Output Pulse Position for BIT 6                      |                                        | 12.99 | 13.19 | 13.99 | ns   |

| t <sub>TPP0</sub> | Transmitter Output Pulse Position for BIT 0<br>(Fig.11 - Note 3) | f = 85 MHz                             | -0.20 | 0     | 0.20  | ns   |

| t <sub>TPP1</sub> | Transmitter Output Pulse Position for BIT 1                      |                                        | 1.48  | 1.68  | 1.88  | ns   |

| t <sub>TPP2</sub> | Transmitter Output Pulse Position for BIT 2                      |                                        | 3.16  | 3.36  | 3.56  | ns   |

| t <sub>TPP3</sub> | Transmitter Output Pulse Position for BIT 3                      |                                        | 4.84  | 5.04  | 5.24  | ns   |

| t <sub>TPP4</sub> | Transmitter Output Pulse Position for BIT 4                      |                                        | 6.52  | 6.72  | 6.92  | ns   |

| t <sub>TPP5</sub> | Transmitter Output Pulse Position for BIT 5                      |                                        | 8.20  | 8.40  | 8.60  | ns   |

| t <sub>TPP6</sub> | Transmitter Output Pulse Position for BIT 6                      |                                        | 9.88  | 10.08 | 10.28 | ns   |

| t <sub>STC</sub>  | TxIN Setup to TxCLK IN (Fig. 6)                                  |                                        | 2.5   |       |       | ns   |

| t <sub>нтс</sub>  | TxIN Hold to TxCLK IN (Fig. 6)                                   |                                        | 0     |       |       | ns   |

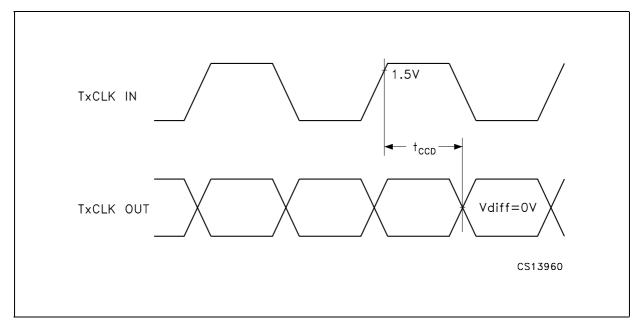

| t <sub>CCD</sub>  | TxCLK IN to TxCLK OUT Delay (Fig. 7)                             | $T_{A} = 25^{\circ}C,$ $V_{CC} = 3.3V$ | 3.8   |       | 6.3   | ns   |

| t <sub>CCD</sub>  | TxCLK IN to TxCLK OUT Delay (Fig. 7)                             |                                        | 2.8   |       | 7.1   | ns   |

| t <sub>JCC</sub>  | Transmitter Jitter Cycle-to-Cycle (Fig. 12 - Note 4)             | f = 85 MHz                             |       | 110   | 150   | ps   |

|                   |                                                                  | f = 65 MHz                             |       | 210   | 230   |      |

|                   |                                                                  | f = 40 MHz                             |       | 350   | 370   |      |

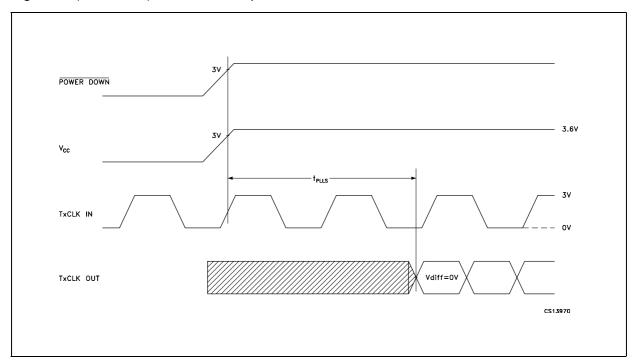

| t <sub>PLLS</sub> | Transmitter Phase Lock Loop Set (Fig. 8)                         |                                        |       |       | 10    | ms   |

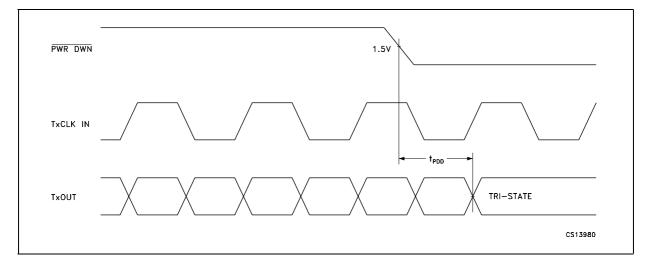

| t <sub>PDD</sub>  | Transmitter Power Down Delay (Fig. 10)                           |                                        |       |       | 100   | ns   |

Note 1: Current into device pins is defined as positive. Current out of device pins is defined as negative. Voltages are referenced to ground unless otherwise specified (except  $V_{OD}$  and  $\Delta V_{OD}$ ). Note 2:  $V_{OS}$  previously referred as  $V_{CM}$ . Note 3: The Minimum and Maximum Limits are based on statistical analysis of the device performance over process, voltage, and temperature range. This parameter is functionality tested only on Automatic Test Equipment (ATE). Note 4: The limits are based on bench characterization of the device's jitter response over the power supply voltage range. Output clock jitter is measured with a cycle-to-cycle jitter of  $\pm$  3ns applied to the input clock signal while data inputs are switching (See Figures 15 and 16). A jitter event of 3ns, represents worse case jump in the clock edge from most graphics controller VGA chips currently available. Note 5: The worst case test pattern produces a maximum toggling of digital circuits, LVDS I/O and CMOS/TTL I/O.

Note 6: The 16 grayscale test pattern provides a maximum rogging of algorithm to and one of the index of the

#### AC TIMING DIAGRAMS

#### Figure 1 : "Worst Case" Test Pattern (Note 5)

|                 |       | SIGNAL FREQUENCY           |

|-----------------|-------|----------------------------|

| DEVICE PIN NAME |       |                            |

| TxIN0/RxOUT0    |       | f/16                       |

| TxIN1/RxOUT1    | R1    | f/8                        |

| TxIN2/RxOUT2    |       | f/4                        |

| TxIN3/RxOUT3    |       | f/2                        |

| TxIN4/RxOUT4    | R4    | Steady State, Low          |

| TxIN5/RxOUT5    | R7    | Steady State, Low          |

| TxIN6/RxOUT6    | R5    | Steady State, Low          |

| TxIN7/RxOUT7    | 60    | Steady State, Low          |

| TxIN8/RxOUT8    | G1    | f/16                       |

| TxIN9/RxOUT9    | G2    | f/8                        |

| TxIN10/RxOUT10  |       | f/4                        |

| TxIN11/RxOUT11  |       | f/2                        |

| TxIN12/RxOUT12  | 63    | Steady State, Low          |

| TxIN13/RxOUT13  | C4    | Steady State, Low          |

| TxIN14/RxOUT14  | 65    | Steady State, Low          |

| TxIN15/RxOUT15  | 80    | Steady State, Low          |

| TxIN16/RxOUT16  | 86    | f/16                       |

| TxIN17/RxOUT17  | 87    | f/8                        |

| TxIN18/RxOUT18  |       | f/4                        |

| TxIN19/RxOUT19  |       | f/2                        |

| TxIN20/RxOUT20  | B3    | <br>  Steady State, Low    |

| TxIN21/RxOUT21  | B4    | Steady State, Low          |

| TxIN22/RxOUT22  | B5    | Steady State, Low          |

| TxIN23/RxOUT23  | RES   | Steady State, Low          |

| TxIN24/RxOUT24  | HSYNC | <br>  Steady State, High   |

| TxIN25/RxOUT25  | VSYNC | <br>  Steady State, High   |

| TxIN26/RxOUT26  | EN    | <br>Steady State, High     |

| TxIN27/RxOUT27  | R6    | <br>Steady State, High<br> |

|                 |       | CS13900                    |

|                 |       |                            |

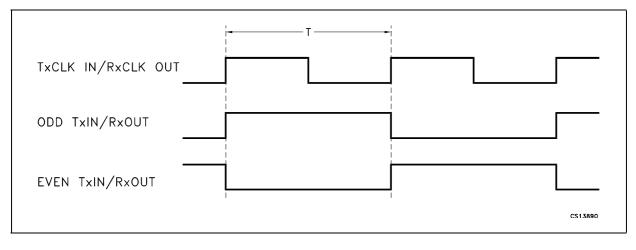

Figure 2 : "16 Grayscale" Test Patter (Notes 6, 7, 8)

Figure 5 : (Transmitter) Input Clock Transition Time

Figure 6 : (Transmitter) Setup/Hold and High/Low Times (Falling Edge Strobe)

Figure 7 : (Transmitter) Clock In to Clock Out Delay

Figure 8 : (Transmitter) Phase Lock Loop Set Time

Figure 10 : Transmitter Power Down Delay

Figure 11 : Transmitter LVDS Output Pulse Position Measurement

11/14

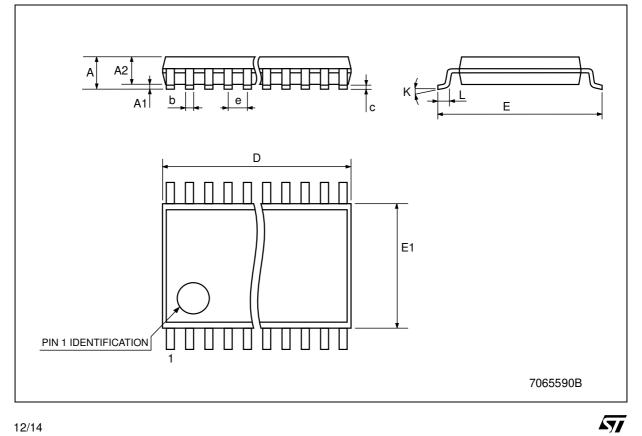

|      | TSSOP56 MECHANICAL DATA |         |      |        |            |        |  |  |  |

|------|-------------------------|---------|------|--------|------------|--------|--|--|--|

| DIM. | mm.                     |         |      | inch   |            |        |  |  |  |

| DIM. | MIN.                    | ТҮР     | MAX. | MIN.   | TYP.       | MAX.   |  |  |  |

| А    |                         |         | 1.2  |        |            | 0.047  |  |  |  |

| A1   | 0.05                    |         | 0.15 | 0.002  |            | 0.006  |  |  |  |

| A2   |                         | 0.9     |      |        | 0.035      |        |  |  |  |

| b    | 0.17                    |         | 0.27 | 0.0067 |            | 0.011  |  |  |  |

| С    | 0.09                    |         | 0.20 | 0.0035 |            | 0.0079 |  |  |  |

| D    | 13.9                    |         | 14.1 | 0.547  |            | 0.555  |  |  |  |

| E    | 7.95                    |         | 8.25 | 0.313  |            | 0.325  |  |  |  |

| E1   | 6.0                     |         | 6.2  | 0.236  |            | 0.244  |  |  |  |

| е    |                         | 0.5 BSC |      |        | 0.0197 BSC |        |  |  |  |

| К    | 0°                      |         | 8°   | 0°     |            | 8°     |  |  |  |

| L    | 0.45                    |         | 0.75 | 0.020  |            | 0.030  |  |  |  |

1

Г

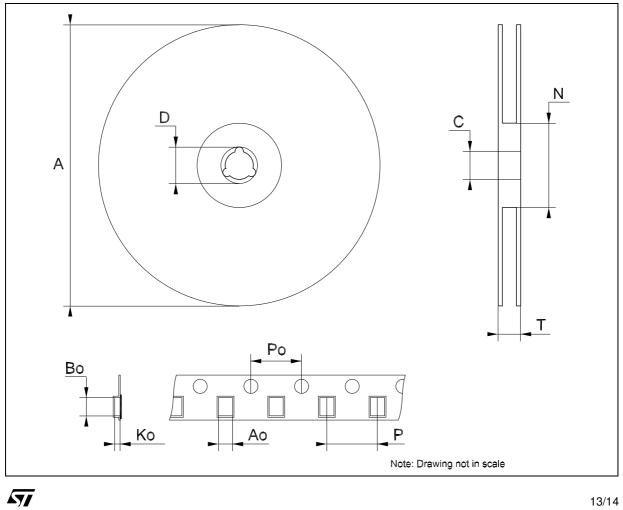

| DIM. | mm.  |     |      | inch  |      |        |

|------|------|-----|------|-------|------|--------|

|      | MIN. | ТҮР | MAX. | MIN.  | TYP. | MAX.   |

| А    |      |     | 330  |       |      | 12.992 |

| С    | 12.8 |     | 13.2 | 0.504 |      | 0.519  |

| D    | 20.2 |     |      | 0.795 |      |        |

| Ν    | 60   |     |      | 2.362 |      |        |

| Т    |      |     | 30.4 |       |      | 1.197  |

| Ao   | 8.7  |     | 8.9  | 0.342 |      | 0.350  |

| Во   | 17.2 |     | 17.4 | 0.677 |      | 0.685  |

| Ko   | 1.4  |     | 1.6  | 0.055 |      | 0.063  |

| Po   | 3.9  |     | 4.1  | 0.153 |      | 0.161  |

| Р    | 11.9 |     | 12.1 | 0.468 |      | 0.476  |

### Tape & Reel TSSOP56 MECHANICAL DATA

13/14

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics All other names are the property of their respective owners

© 2004 STMicroelectronics - All Rights Reserved STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States. http://www.st.com