Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STM32L082KB STM32L082KZ STM32L082CZ

Ultra-low-power 32-bit MCU ARM®-based Cortex®-M0+, up to 192KB Flash, 20KB SRAM, 6KB EEPROM, USB, ADC, DACs, AES

Datasheet - production data

#### **Features**

- Ultra-low-power platform

- 1.65 V to 3.6 V power supply

- -40 to 125 °C temperature range

- 0.29 μA Standby mode (3 wakeup pins)

- 0.43 µA Stop mode (16 wakeup lines)

- 0.86 µA Stop mode + RTC + 20 KB RAM retention

- Down to 93 µA/MHz in Run mode

- 5 μs wakeup time (from Flash memory)

- 41 μA 12-bit ADC conversion at 10 ksps

- Core: ARM<sup>®</sup> 32-bit Cortex<sup>®</sup>-M0+ with MPU

- From 32 kHz up to 32 MHz max.

- 0.95 DMIPS/MHz

- Reset and supply management

- Ultra-safe, low-power BOR (brownout reset) with 5 selectable thresholds

- Ultra-low-power POR/PDR

- Programmable voltage detector (PVD)

- Clock sources

- 1 to 25 MHz crystal oscillator

- 32 kHz oscillator for RTC with calibration

- High speed internal 16 MHz factory-trimmed RC (+/- 1%)

- Internal low-power 37 kHz RC

- Internal multispeed low-power 65 kHz to 4.2 MHz RC

- Internal self calibration of 48 MHz RC for USB

- PLL for CPU clock

- Pre-programmed bootloader

- USB, USART supported

- Development support

- Serial wire debug supported

- Up to 40 fast I/Os (34 I/Os 5V tolerant)

- Memories

- Up to 192 KB Flash memory with ECC (2 banks with read-while-write capability)

- 20KB RAM

- 6 KB of data EEPROM with ECC

- 20-byte backup register

- Sector protection against R/W operation

- Rich Analog peripherals

- 12-bit ADC 1.14 Msps, up to 13 channels (down to 1.65 V)

- 2 x 12-bit channel DACs with output buffers (down to 1.8 V)

- 2x ultra-low-power comparators (window mode and wake up capability, down to 1.65 V)

- Up to 19 capacitive sensing channels supporting touchkey, linear and rotary touch sensors

- 7-channel DMA controller, supporting ADC, SPI, I2C, USART, DAC, Timers, AES

- 11x peripheral communication interfaces

- 1x USB 2.0 crystal-less, battery charging detection and LPM

- 4x USART (2 with ISO 7816, IrDA), 1x UART (low power)

- Up to 6x SPI 16 Mbits/s

- 3x I2C (2 with SMBus/PMBus)

- 11x timers: 2x 16-bit with up to 4 channels, 2x 16-bit with up to 2 channels, 1x 16-bit ultra-low-power timer, 1x SysTick, 1x RTC, 2x 16-bit basic for DAC, and 2x watchdogs (independent/window)

- CRC calculation unit, 96-bit unique ID

- True RNG and firewall protection

- Hardware Encryption Engine AES 128-bit

- All packages are ECOPACK<sup>®</sup>2

Contents STM32L082xx

# **Contents**

| 1 | Intro                                   | duction                                                     | 9 |

|---|-----------------------------------------|-------------------------------------------------------------|---|

| 2 | Desc                                    | cription                                                    | 0 |

|   | 2.1                                     | Device overview                                             | 1 |

|   | 2.2                                     | Ultra-low-power device continuum                            | 3 |

| 3 | Fund                                    | ctional overview1                                           | 4 |

|   | 3.1                                     | Low-power modes                                             | 4 |

|   | 3.2                                     | Interconnect matrix                                         | 9 |

|   | 3.3                                     | ARM® Cortex®-M0+ core with MPU2                             | 0 |

|   | 3.4                                     | Reset and supply management                                 | 1 |

|   |                                         | 3.4.1 Power supply schemes                                  | 1 |

|   |                                         | 3.4.2 Power supply supervisor                               | 1 |

|   |                                         | 3.4.3 Voltage regulator                                     | 2 |

|   | 3.5                                     | Clock management                                            | 2 |

|   | 3.6                                     | Low-power real-time clock and backup registers              | 5 |

|   | 3.7                                     | General-purpose inputs/outputs (GPIOs)                      | 5 |

|   | 3.8                                     | Memories                                                    | 6 |

|   | 3.9                                     | Boot modes                                                  | 6 |

|   | 3.10                                    | Direct memory access (DMA)                                  | 7 |

|   | 3.11                                    | Analog-to-digital converter (ADC)                           | 7 |

|   | 3.12                                    | Temperature sensor                                          | 7 |

|   |                                         | 3.12.1 Internal voltage reference (V <sub>REFINT</sub> )    |   |

|   | 3.13                                    | Digital-to-analog converter (DAC)                           |   |

|   | 3.14                                    | Ultra-low-power comparators and reference voltage           | 9 |

|   | 3.15                                    | Touch sensing controller (TSC)                              |   |

|   | 3.16                                    | AES                                                         |   |

|   | 3.17                                    | Timers and watchdogs                                        |   |

|   | • • • • • • • • • • • • • • • • • • • • | 3.17.1 General-purpose timers (TIM2, TIM3, TIM21 and TIM22) |   |

|   |                                         | 3.17.2 Low-power Timer (LPTIM)                              |   |

|   |                                         | 3.17.3 Basic timer (TIM6, TIM7)                             |   |

|   |                                         | 3.17.4 SysTick timer                                        |   |

STM32L082xx Contents

|   |       | 3.17.5    | Independent watchdog (IWDG)                                        |

|---|-------|-----------|--------------------------------------------------------------------|

|   |       | 3.17.6    | Window watchdog (WWDG)                                             |

|   | 3.18  |           | nication interfaces                                                |

|   |       | 3.18.1    | I2C bus                                                            |

|   |       | 3.18.2    | Universal synchronous/asynchronous receiver transmitter (USART) 34 |

|   |       | 3.18.3    | Low-power universal asynchronous receiver transmitter (LPUART) 34  |

|   |       | 3.18.4    | Serial peripheral interface (SPI)/Inter-integrated sound (I2S)35   |

|   |       | 3.18.5    | Universal serial bus (USB)                                         |

|   | 3.19  | Clock re  | ecovery system (CRS)                                               |

|   | 3.20  | Cyclic r  | edundancy check (CRC) calculation unit                             |

|   | 3.21  | Serial w  | rire debug port (SW-DP)                                            |

| 4 | Pin d | escripti  | ons                                                                |

|   |       | -         |                                                                    |

| 5 | Memo  | ory map   | ping                                                               |

| 6 | Elect | rical cha | aracteristics                                                      |

|   | 6.1   | Parame    | eter conditions                                                    |

|   |       | 6.1.1     | Minimum and maximum values                                         |

|   |       | 6.1.2     | Typical values                                                     |

|   |       | 6.1.3     | Typical curves                                                     |

|   |       | 6.1.4     | Loading capacitor                                                  |

|   |       | 6.1.5     | Pin input voltage                                                  |

|   |       | 6.1.6     | Power supply scheme                                                |

|   |       | 6.1.7     | Current consumption measurement49                                  |

|   | 6.2   | Absolut   | e maximum ratings                                                  |

|   | 6.3   | Operati   | ng conditions 52                                                   |

|   |       | 6.3.1     | General operating conditions                                       |

|   |       | 6.3.2     | Embedded reset and power control block characteristics54           |

|   |       | 6.3.3     | Embedded internal reference voltage55                              |

|   |       | 6.3.4     | Supply current characteristics                                     |

|   |       | 6.3.5     | Wakeup time from low-power mode                                    |

|   |       | 6.3.6     | External clock source characteristics                              |

|   |       | 6.3.7     | Internal clock source characteristics                              |

|   |       | 6.3.8     | PLL characteristics                                                |

|   |       | 6.3.9     | Memory characteristics                                             |

|   |       | 6.3.10    | EMC characteristics                                                |

|   |       |           |                                                                    |

|   |      | 6.3.11    | Electrical sensitivity characteristics82 |

|---|------|-----------|------------------------------------------|

|   |      | 6.3.12    | I/O current injection characteristics83  |

|   |      | 6.3.13    | I/O port characteristics                 |

|   |      | 6.3.14    | NRST pin characteristics                 |

|   |      | 6.3.15    | 12-bit ADC characteristics               |

|   |      | 6.3.16    | DAC electrical specifications            |

|   |      | 6.3.17    | Temperature sensor characteristics       |

|   |      | 6.3.18    | Comparators                              |

|   |      | 6.3.19    | Timer characteristics                    |

|   |      | 6.3.20    | Communications interfaces                |

| 7 | Pack | cage info | ormation                                 |

|   | 7.1  | WLCS      | SP49 package information                 |

|   | 7.2  | LQFP3     | 32 package information                   |

|   | 7.3  | UFQFF     | PN32 package information                 |

|   | 7.4  | Therma    | al characteristics11                     |

|   |      | 7.4.1     | Reference document                       |

| 8 | Part | number    | ring 117                                 |

| 9 | Revi | sion his  | story                                    |

STM32L082xx List of tables

# List of tables

| Table 1.  | Ultra-low-power STM32L082xx device features and peripheral counts           | . 11 |

|-----------|-----------------------------------------------------------------------------|------|

| Table 2.  | Functionalities depending on the operating power supply range               |      |

| Table 3.  | CPU frequency range depending on dynamic voltage scaling                    |      |

| Table 4.  | Functionalities depending on the working mode                               |      |

|           | (from Run/active down to standby)                                           | . 17 |

| Table 5.  | STM32L0xx peripherals interconnect matrix                                   |      |

| Table 6.  | Temperature sensor calibration values                                       |      |

| Table 7.  | Internal voltage reference measured values                                  | . 28 |

| Table 8.  | Capacitive sensing GPIOs available on STM32L082xx devices                   |      |

| Table 9.  | Timer feature comparison                                                    |      |

| Table 10. | Comparison of I2C analog and digital filters                                |      |

| Table 11. | STM32L082xx I <sup>2</sup> C implementation                                 | 33   |

| Table 12. | USART implementation                                                        |      |

| Table 13. | SPI/I2S implementation                                                      | 35   |

| Table 14. | Legend/abbreviations used in the pinout table                               | . 38 |

| Table 15. | STM32L072xxx pin definition                                                 | 39   |

| Table 16. | Alternate functions port A                                                  | 44   |

| Table 17. | Alternate functions port B                                                  | 45   |

| Table 18. | Alternate functions port C                                                  | 46   |

| Table 19. | Alternate functions port H                                                  | 46   |

| Table 20. | Voltage characteristics                                                     | 50   |

| Table 21. | Current characteristics                                                     |      |

| Table 22. | Thermal characteristics                                                     |      |

| Table 23. | General operating conditions                                                |      |

| Table 24. | Embedded reset and power control block characteristics                      |      |

| Table 25. | Embedded internal reference voltage calibration values                      |      |

| Table 26. | Embedded internal reference voltage                                         | 55   |

| Table 27. | Current consumption in Run mode, code with data processing running from     |      |

|           | Flash memory                                                                | 57   |

| Table 28. | Current consumption in Run mode vs code type,                               |      |

|           | code with data processing running from Flash memory                         |      |

| Table 29. | Current consumption in Run mode, code with data processing running from RAM | 59   |

| Table 30. | Current consumption in Run mode vs code type,                               |      |

| T 11 04   | code with data processing running from RAM                                  |      |

| Table 31. | Current consumption in Sleep mode                                           |      |

| Table 32. | Current consumption in Low-power run mode                                   |      |

| Table 33. | Current consumption in Low-power sleep mode                                 |      |

| Table 34. | Typical and maximum current consumptions in Stop mode                       |      |

| Table 35. | Typical and maximum current consumptions in Standby mode                    |      |

| Table 36. | Average current consumption during Wakeup                                   |      |

| Table 37. | Peripheral current consumption in Run or Sleep mode                         |      |

| Table 38. | Peripheral current consumption in Stop and Standby mode                     |      |

| Table 39. | Light around external year clock characteristics                            |      |

| Table 40. | High-speed external user clock characteristics                              |      |

| Table 41. | Low-speed external user clock characteristics                               |      |

| Table 42. | HSE oscillator characteristics                                              |      |

| Table 43. | LSE oscillator characteristics                                              |      |

| Table 44. | 16 MHz HSI16 oscillator characteristics                                     | 73   |

List of tables STM32L082xx

| Table 45. | HSI48 oscillator characteristics                                        |

|-----------|-------------------------------------------------------------------------|

| Table 46. | LSI oscillator characteristics                                          |

| Table 47. | MSI oscillator characteristics                                          |

| Table 48. | PLL characteristics                                                     |

| Table 49. | RAM and hardware registers                                              |

| Table 50. | Flash memory and data EEPROM characteristics                            |

| Table 51. | Flash memory and data EEPROM endurance and retention                    |

| Table 52. | EMS characteristics                                                     |

| Table 53. | EMI characteristics                                                     |

| Table 54. | ESD absolute maximum ratings                                            |

| Table 55. | Electrical sensitivities                                                |

| Table 56. | I/O current injection susceptibility                                    |

| Table 57. | I/O static characteristics                                              |

| Table 58. | Output voltage characteristics                                          |

| Table 59. | I/O AC characteristics                                                  |

| Table 60. | NRST pin characteristics                                                |

| Table 61. | ADC characteristics                                                     |

| Table 62. | R <sub>AIN</sub> max for f <sub>ADC</sub> = 16 MHz91                    |

| Table 63. | ADC accuracy91                                                          |

| Table 64. | DAC characteristics                                                     |

| Table 65. | Temperature sensor calibration values97                                 |

| Table 66. | Temperature sensor characteristics                                      |

| Table 67. | Comparator 1 characteristics                                            |

| Table 68. | Comparator 2 characteristics                                            |

| Table 69. | TIMx characteristics                                                    |

| Table 70. | I2C analog filter characteristics                                       |

| Table 71. | USART/LPUART characteristics                                            |

| Table 72. | SPI characteristics in voltage Range 1                                  |

| Table 73. | SPI characteristics in voltage Range 2                                  |

| Table 74. | SPI characteristics in voltage Range 3                                  |

| Table 75. | USB startup time                                                        |

| Table 76. | USB DC electrical characteristics                                       |

| Table 77. | USB: full speed electrical characteristics                              |

| Table 78. | WLCSP49 - 49-pin, 3.294 x 3.258 mm, 0.4 mm pitch wafer level chip scale |

|           | package mechanical data                                                 |

| Table 79. | WLCSP49 recommended PCB design rules (0.4 mm pitch)                     |

| Table 80. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data |

| Table 81. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat |

|           | package mechanical data                                                 |

| Table 82. | Thermal characteristics115                                              |

| Table 83. | STM32L082xx ordering information scheme                                 |

| Table 84. | Document revision history                                               |

STM32L082xx List of figures

# List of figures

| Figure 1.  | STM32L082xx block diagram                                                                    | 12  |

|------------|----------------------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                                   |     |

| Figure 3.  | STM32L082xx WLCSP49 ballout                                                                  |     |

| Figure 4.  | STM32L082xx LQFP32 pinout                                                                    | 37  |

| Figure 5.  | STM32L082xx UFQFPN32 pinout                                                                  |     |

| Figure 6.  | Memory map                                                                                   |     |

| Figure 7.  | Pin loading conditions                                                                       | 48  |

| Figure 8.  | Pin input voltage                                                                            | 48  |

| Figure 9.  | Power supply scheme                                                                          | 49  |

| Figure 10. | Current consumption measurement scheme                                                       | 49  |

| Figure 11. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

|            | Flash memory, Range 2, HSE, 1WS                                                              | 58  |

| Figure 12. | IDD vs VDD, at TA= 25/55/85/105 °C, Run mode, code running from                              |     |

|            | Flash memory, Range 2, HSI16, 1WS                                                            | 59  |

| Figure 13. | IDD vs VDD, at TA= 25 °C, Low-power run mode, code running                                   |     |

|            | from RAM, Range 3, MSI (Range 0) at 64 KHz, 0 WS                                             | 63  |

| Figure 14. | IDD vs VDD, at TA= 25/55/ 85/105/125 °C, Stop mode with RTC enabled                          |     |

|            | and running on LSE Low drive                                                                 | 64  |

| Figure 15. | IDD vs VDD, at TA= 25/55/85/105/125 °C, Stop mode with RTC disabled,                         |     |

|            | all clocks off                                                                               | 65  |

| Figure 16. | High-speed external clock source AC timing diagram                                           | 71  |

| Figure 17. | Low-speed external clock source AC timing diagram                                            | 72  |

| Figure 18. | HSE oscillator circuit diagram                                                               |     |

| Figure 19. | Typical application with a 32.768 kHz crystal                                                | 74  |

| Figure 20. | HSI16 minimum and maximum value versus temperature                                           |     |

| Figure 21. | VIH/VIL versus VDD (CMOS I/Os)                                                               |     |

| Figure 22. | VIH/VIL versus VDD (TTL I/Os)                                                                |     |

| Figure 23. | I/O AC characteristics definition                                                            |     |

| Figure 24. | Recommended NRST pin protection                                                              | 89  |

| Figure 25. | ADC accuracy characteristics                                                                 |     |

| Figure 26. | Typical connection diagram using the ADC                                                     |     |

| Figure 27. | Power supply and reference decoupling (V <sub>REF+</sub> not connected to V <sub>DDA</sub> ) |     |

| Figure 28. | Power supply and reference decoupling (V <sub>REF+</sub> connected to V <sub>DDA</sub> )     |     |

| Figure 29. | 12-bit buffered/non-buffered DAC                                                             |     |

| Figure 30. | SPI timing diagram - slave mode and CPHA = 0                                                 | 103 |

| Figure 31. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                  | 104 |

| Figure 32. | SPI timing diagram - master mode <sup>(1)</sup>                                              | 104 |

| Figure 33. | USB timings: definition of data signal rise and fall time                                    |     |

| Figure 34. | WLCSP49 - 49-pin, 3.294 x 3.258 mm, 0.4 mm pitch wafer level chip scale                      |     |

| Ü          | package outline                                                                              | 108 |

| Figure 35. | WLCSP49 - 49-pin, 3.294 x 3.258 mm, 0.4 mm pitch wafer level chip scale                      |     |

| Ü          | recommended footprint                                                                        | 109 |

| Figure 36. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                              |     |

| Figure 37. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat recommended footprint                        |     |

| Figure 38. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat                      | . — |

| <b>J</b>   | package outline                                                                              | 113 |

| Figure 39. | UFQFPN32 - 32-pin, 5x5 mm, 0.5 mm pitch ultra thin fine pitch quad flat                      |     |

| Ū          | recommended footprint                                                                        | 114 |

|            | ·                                                                                            |     |

| List of figu | res                | STM32L082xx |

|--------------|--------------------|-------------|

|              |                    |             |

| Figure 40.   | Thermal resistance | <br>115     |

**\7/**

STM32L082xx Introduction

#### 1 Introduction

The ultra-low-power STM32L082xx are offered in 32- and 49-pin packages. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L082xx microcontrollers suitable for a wide range of applications:

- Gas/water meters and industrial sensors

- Healthcare and fitness equipment

- · Remote control and user interface

- · PC peripherals, gaming, GPS equipment

- Alarm system, wired and wireless sensors, video intercom

This STM32L082xx datasheet should be read in conjunction with the STM32L0x2xx reference manual (RM0376).

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M0+ core please refer to the Cortex<sup>®</sup>-M0+ Technical Reference Manual, available from the www.arm.com website.

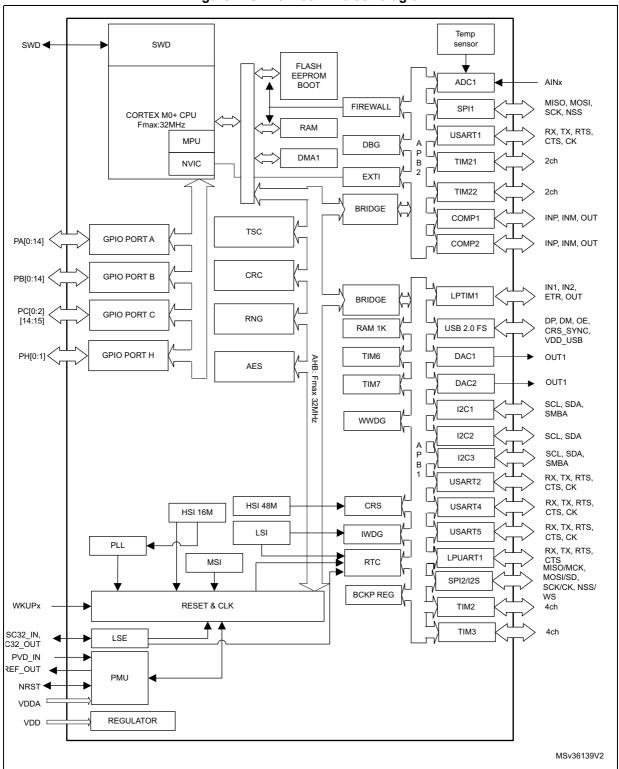

Figure 1 shows the general block diagram of the device family.

Description STM32L082xx

# 2 Description

The ultra-low-power STM32L082xx microcontrollers incorporate the connectivity power of the universal serial bus (USB 2.0 crystal-less) with the high-performance ARM® Cortex®-M0+ 32-bit RISC core operating at a 32 MHz frequency, a memory protection unit (MPU), high-speed embedded memories (up to 192 Kbytes of Flash program memory, 6 Kbytes of data EEPROM and 20 Kbytes of RAM) plus an extensive range of enhanced I/Os and peripherals.

The STM32L082xx devices provide high power efficiency for a wide range of performance. It is achieved with a large choice of internal and external clock sources, an internal voltage adaptation and several low-power modes.

The STM32L082xx devices offer several analog features, one 12-bit ADC with hardware oversampling, two DACs, two ultra-low-power comparators, AES, several timers, one low-power timer (LPTIM), four general-purpose 16-bit timers and two basic timer, one RTC and one SysTick which can be used as timebases. They also feature two watchdogs, one watchdog with independent clock and window capability and one window watchdog based on bus clock.

Moreover, the STM32L082xx devices embed standard and advanced communication interfaces: up to three I2Cs, two SPIs, one I2S, four USARTs, a low-power UART (LPUART), and a crystal-less USB. The devices offer up to 19 capacitive sensing channels to simply add touch sensing functionality to any application.

The STM32L082xx also include a real-time clock and a set of backup registers that remain powered in Standby mode.

The ultra-low-power STM32L082xx devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +125 °C temperature range. A comprehensive set of power-saving modes allows the design of low-power applications.

10/119 DocID027099 Rev 4

STM32L082xx Description

#### 2.1 Device overview

Table 1. Ultra-low-power STM32L082xx device features and peripheral counts

| Peripheral                                 |                  | STM32L082KB                                                                                    | STM32L082KZ       | STM32L082CZ            |  |  |

|--------------------------------------------|------------------|------------------------------------------------------------------------------------------------|-------------------|------------------------|--|--|

| Flash (Kbytes)                             |                  | 128 Kbytes                                                                                     | 192 Kbytes        |                        |  |  |

| Data EEPROM (Kbytes)                       |                  | 6 Kbytes                                                                                       |                   |                        |  |  |

| RAM (Kbytes)                               |                  |                                                                                                | 20 Kbytes         |                        |  |  |

| AES                                        |                  |                                                                                                | 1                 |                        |  |  |

|                                            | General-purpose  |                                                                                                | 4                 |                        |  |  |

| Timers                                     | Basic            |                                                                                                | 2                 |                        |  |  |

|                                            | LPTIMER          |                                                                                                | 1                 |                        |  |  |

| RTC/SYSTICK/IW                             | /DG/WWDG         |                                                                                                | 1/1/1/1           |                        |  |  |

|                                            | SPI/I2S          | 4(3)                                                                                           | <sup>(1)</sup> /0 | 6(4) <sup>(2)</sup> /1 |  |  |

|                                            | I <sup>2</sup> C | 2                                                                                              | 2                 | 3                      |  |  |

| Communication interfaces                   | USART            | :                                                                                              | 4                 |                        |  |  |

|                                            | LPUART           |                                                                                                |                   |                        |  |  |

|                                            | USB/(VDD_USB)    | 1/(0                                                                                           | )) <sup>(3)</sup> | 1/(1)                  |  |  |

| GPIOs                                      |                  | 25 <sup>(3)</sup>                                                                              |                   | 40                     |  |  |

| Clocks: HSE/LSE/HSI/MS                     | SI/LSI           | 0/1/1/1                                                                                        |                   | 1/1/1/1/1              |  |  |

| 12-bit synchronized ADC Number of channels | :                | 1<br>10                                                                                        |                   | 1<br>13                |  |  |

| 12-bit DAC<br>Number of channels           |                  | 2<br>2                                                                                         |                   |                        |  |  |

| Comparators                                |                  |                                                                                                | 2                 |                        |  |  |

| Capacitive sensing channels                |                  | 13 <sup>(3)</sup>                                                                              |                   | 19                     |  |  |

| Max. CPU frequency                         |                  | 32 MHz                                                                                         |                   |                        |  |  |

| Operating voltage                          |                  | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option 1.65 to 3.6 V without BOR option |                   |                        |  |  |

| Operating temperatures                     |                  | Ambient temperature: –40 to +125 °C<br>Junction temperature: –40 to +130 °C                    |                   |                        |  |  |

| Packages                                   |                  | UFQFPN3                                                                                        | 2, LQFP32         | WLCSP49                |  |  |

<sup>1. 3</sup> SPI interfaces are USARTs operating in SPI master mode.

<sup>2. 4</sup> SPI interfaces are USARTs operating in SPI master mode.

<sup>3.</sup> UFQFP32 has 2 GPIOs and 1 capacitive sensing channel less that LQFP32. However, UFQFP32 features a VDD\_USB pin while LQPF32 does not.

Description STM32L082xx

Figure 1. STM32L082xx block diagram

STM32L082xx Description

### 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of core and features, from 8-bit proprietary core up to ARM® Cortex®-M4, including ARM® Cortex®-M3 and ARM® Cortex®-M0+. The STM32Lx series are the best choice to answer your needs in terms of ultra-low-power features. The STM32 ultra-low-power series are the best solution for applications such as gaz/water meter, keyboard/mouse or fitness and healthcare application. Several built-in features like LCD drivers, dual-bank memory, low-power run mode, operational amplifiers, 128-bit AES, DAC, crystal-less USB and many other definitely help you building a highly cost optimized application by reducing BOM cost. STMicroelectronics, as a reliable and long-term manufacturer, ensures as much as possible pin-to-pin compatibility between all STM8Lx and STM32Lx on one hand, and between all STM32Lx and STM32Fx on the other hand. Thanks to this unprecedented scalability, your legacy application can be upgraded to respond to the latest market feature and efficiency requirements.

#### 3 Functional overview

#### 3.1 Low-power modes

The ultra-low-power STM32L082xx support dynamic voltage scaling to optimize its power consumption in Run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71-3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4.2 MHz

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the low-speed clock (max 131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In Low-power run mode, the clock frequency and the number of enabled peripherals are both limited.

#### Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the Run mode with the regulator on.

#### Stop mode with RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSE crystal and HSI RC oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The device can be woken up from Stop mode by any of the EXTI line, in 3.5 µs, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on), it can be the RTC alarm/tamper/timestamp/wakeup events, the USB/USART/I2C/LPUART/LPTIMER wakeup events.

14/119 DocID027099 Rev 4

#### Stop mode without RTC

The Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are disabled.

Some peripherals featuring wakeup capability can enable the HSI RC during Stop mode to detect their wakeup condition.

The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 3.5  $\mu$ s, the processor can serve the interrupt or resume the code. The EXTI line source can be any GPIO. It can be the PVD output, the comparator 1 event or comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB/USART/I2C/LPUART/LPTIMER wakeup events.

#### Standby mode with RTC

The Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSE crystal and HSI RC oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32 KHz oscillator, RCC\_CSR register).

The device exits Standby mode in 60 µs when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note: The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

Table 2. Functionalities depending on the operating power supply range

|                                                | Functionalities depending on the operating power supply range |                                     |                            |                           |  |  |  |

|------------------------------------------------|---------------------------------------------------------------|-------------------------------------|----------------------------|---------------------------|--|--|--|

| Operating power supply range                   | DAC and ADC operation                                         | Dynamic<br>voltage scaling<br>range | I/O operation              | USB                       |  |  |  |

| V <sub>DD</sub> = 1.65 to 1.71 V               | ADC only,<br>conversion time<br>up to 570 ksps                | Range 2 or range 3                  | Degraded speed performance | Not functional            |  |  |  |

| V <sub>DD</sub> = 1.71 to 1.8 V <sup>(1)</sup> | ADC only,<br>conversion time<br>up to 1.14 Msps               | Range 1, range 2<br>or range 3      | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |

| $V_{DD}$ = 1.8 to 2.0 $V^{(1)}$                | Conversion time up to 1.14 Msps                               | Range1, range 2<br>or range 3       | Degraded speed performance | Functional <sup>(2)</sup> |  |  |  |

| V <sub>DD</sub> = 2.0 to 2.4 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |

| V <sub>DD</sub> = 2.4 to 3.6 V                 | Conversion time<br>up to<br>1.14 Msps                         | Range 1, range 2<br>or range 3      | Full speed operation       | Functional <sup>(2)</sup> |  |  |  |

<sup>1.</sup> CPU frequency changes from initial to final must respect "fcpu initial <4\*fcpu final". It must also respect 5  $\mu s$  delay between two changes. For example to switch from 4.2 MHz to 32 MHz, you can switch from 4.2 MHz to 16 MHz, wait 5  $\mu s$ , then switch from 16 MHz to 32 MHz.

Table 3. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                              | Dynamic voltage scaling range |

|--------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws) | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)   | Range 2                       |

| 32 kHz to 4.2 MHz (0ws)                          | Range 3                       |

<sup>2.</sup> To be USB compliant from the I/O voltage standpoint, the minimum  $\rm V_{\rm DD\_USB}$  is 3.0 V.

Table 4. Functionalities depending on the working mode (from Run/active down to standby) <sup>(1)(2)</sup>

|                                           |            | Lov   | Low-         | Low-           |                  | Stop                 | Standby |                      |

|-------------------------------------------|------------|-------|--------------|----------------|------------------|----------------------|---------|----------------------|

| IPs                                       | Run/Active | Sleep | power<br>run | power<br>sleep |                  | Wakeup<br>capability |         | Wakeup<br>capability |

| CPU                                       | Υ          |       | Y            |                |                  |                      |         |                      |

| Flash memory                              | 0          | 0     | 0            | 0              |                  |                      |         |                      |

| RAM                                       | Y          | Y     | Y            | Y              | Υ                |                      |         |                      |

| Backup registers                          | Y          | Y     | Y            | Y              | Υ                |                      | Υ       |                      |

| EEPROM                                    | 0          | 0     | 0            | 0              |                  |                      |         |                      |

| Brown-out reset (BOR)                     | 0          | 0     | 0            | 0              | 0                | 0                    | 0       | 0                    |

| DMA                                       | 0          | 0     | 0            | 0              |                  |                      |         |                      |

| Programmable<br>Voltage Detector<br>(PVD) | 0          | 0     | 0            | 0              | 0                | 0                    | -       |                      |

| Power-on/down<br>reset (POR/PDR)          | Y          | Y     | Y            | Y              | Υ                | Y                    | Υ       | Y                    |

| High Speed<br>Internal (HSI)              | 0          | 0     |              |                | (3)              |                      |         |                      |

| High Speed<br>External (HSE)              | 0          | 0     | 0            | 0              |                  |                      |         |                      |

| Low Speed Internal (LSI)                  | 0          | 0     | 0            | 0              | 0                |                      | 0       |                      |

| Low Speed<br>External (LSE)               | 0          | 0     | 0            | 0              | 0                |                      | 0       |                      |

| Multi-Speed<br>Internal (MSI)             | 0          | 0     | Y            | Y              |                  |                      |         |                      |

| Inter-Connect<br>Controller               | Y          | Y     | Y            | Y              | Υ                |                      |         |                      |

| RTC                                       | 0          | 0     | 0            | 0              | 0                | 0                    | 0       |                      |

| RTC Tamper                                | 0          | 0     | 0            | 0              | 0                | 0                    | 0       | 0                    |

| Auto WakeUp<br>(AWU)                      | 0          | 0     | 0            | 0              | 0                | 0                    | 0       | 0                    |

| USB                                       | 0          | 0     |              |                |                  | 0                    | -       |                      |

| USART                                     | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | I       |                      |

| LPUART                                    | 0          | 0     | 0            | 0              | O <sup>(4)</sup> | 0                    | -       |                      |

| SPI                                       | 0          | 0     | 0            | 0              |                  |                      |         |                      |

| I2C                                       | 0          | 0     | 0            | 0              | O <sup>(5)</sup> | 0                    | -       |                      |

| ADC                                       | 0          | 0     |              |                |                  |                      | -       |                      |

| DAC                                       | 0          | 0     | 0            | 0              | 0                |                      |         |                      |

Table 4. Functionalities depending on the working mode (from Run/active down to standby) (continued)(1)(2)

|                                           |                        |                        | Low-            | Low-              | Stop                                        |                                      | Standby                                      |                                        |

|-------------------------------------------|------------------------|------------------------|-----------------|-------------------|---------------------------------------------|--------------------------------------|----------------------------------------------|----------------------------------------|

| IPs                                       | Run/Active             | Sleep                  | power<br>run    | power<br>sleep    |                                             | Wakeup<br>capability                 |                                              | Wakeup capability                      |

| Temperature sensor                        | 0                      | 0                      | 0               | 0                 | 0                                           |                                      |                                              |                                        |

| Comparators                               | 0                      | 0                      | 0               | 0                 | 0                                           | 0                                    |                                              |                                        |

| 16-bit timers                             | 0                      | 0                      | 0               | 0                 |                                             |                                      |                                              |                                        |

| LPTIMER                                   | 0                      | 0                      | 0               | 0                 | 0                                           | 0                                    |                                              |                                        |

| IWDG                                      | 0                      | 0                      | 0               | 0                 | 0                                           | 0                                    | 0                                            | 0                                      |

| WWDG                                      | 0                      | 0                      | 0               | 0                 |                                             |                                      |                                              |                                        |

| Touch sensing controller (TSC)            | 0                      | 0                      |                 |                   |                                             |                                      |                                              |                                        |

| SysTick Timer                             | 0                      | 0                      | 0               | 0                 |                                             |                                      |                                              |                                        |

| GPIOs                                     | 0                      | 0                      | 0               | 0                 | 0                                           | 0                                    |                                              | 2 pins                                 |

| Wakeup time to Run mode                   | 0 µs                   | 0.36 µs                | 3 µs            | 32 µs             |                                             | 3.5 µs                               | 50 µs                                        |                                        |

|                                           |                        |                        |                 |                   |                                             | 4 μΑ (No<br>) V <sub>DD</sub> =1.8 V |                                              | 28 μΑ (No<br>) V <sub>DD</sub> =1.8 V  |

| Consumption V <sub>DD</sub> =1.8 to 3.6 V | Down to<br>140 μA/MHz  | Down to<br>37 µA/MHz   | Down to<br>8 µA | Down to<br>4.5 μA | 0.8 μA (with<br>RTC) V <sub>DD</sub> =1.8 V |                                      | 0.65 μA (with<br>RTC) V <sub>DD</sub> =1.8 V |                                        |

| (Typ)                                     | (from Flash<br>memory) | (from Flash<br>memory) |                 |                   | 0.4 μA (No<br>RTC) V <sub>DD</sub> =3.0 V   |                                      | 0.29 μA (No<br>RTC) V <sub>DD</sub> =3.0 V   |                                        |

|                                           |                        |                        |                 |                   |                                             | (with RTC)<br>OD=3.0 V               |                                              | 5 μA (with<br>) V <sub>DD</sub> =3.0 V |

Legend:

"Y" = Yes (enable).

"O" = Optional can be enabled/disabled by software)

"-" = Not available

<sup>2.</sup> The consumption values given in this table are preliminary data given for indication. They are subject to slight changes.

<sup>3.</sup> Some peripherals with wakeup from Stop capability can request HSI to be enabled. In this case, HSI is woken up by the peripheral, and only feeds the peripheral which requested it. HSI is automatically put off when the peripheral does not need it anymore.

<sup>4.</sup> UART and LPUART reception is functional in Stop mode. It generates a wakeup interrupt on Start. To generate a wakeup on address match or received frame event, the LPUART can run on LSE clock while the UART has to wake up or keep running the HSI clock.

<sup>5.</sup> I2C address detection is functional in Stop mode. It generates a wakeup interrupt in case of address match. It will wake up the HSI during reception.

#### 3.2 Interconnect matrix

Several peripherals are directly interconnected. This allows autonomous communication between peripherals, thus saving CPU resources and power consumption. In addition, these hardware connections allow fast and predictable latency.

Depending on peripherals, these interconnections can operate in Run, Sleep, Low-power run, Low-power sleep and Stop modes.

Table 5. STM32L0xx peripherals interconnect matrix

| Interconnect source | Interconnect<br>destination | Interconnect action                                                | Run | Sleep | Low-<br>power<br>run | Low-<br>power<br>sleep | Stop |

|---------------------|-----------------------------|--------------------------------------------------------------------|-----|-------|----------------------|------------------------|------|

| COMPx               | TIM2,TIM21,<br>TIM22        | Timer input channel,<br>trigger from analog<br>signals comparison  | Y   | Y     | Y                    | Y                      | -    |

|                     | LPTIM                       | Timer input channel,<br>trigger from analog<br>signals comparison  | Υ   | Υ     | Y                    | Y                      | Y    |

| TIMx                | TIMx                        | Timer triggered by other timer                                     | Y   | Y     | Y                    | Y                      | -    |

| RTC                 | TIM21                       | Timer triggered by Auto wake-up                                    | Y   | Y     | Y                    | Y                      | -    |

|                     | LPTIM                       | Timer triggered by RTC event                                       | Y   | Y     | Υ                    | Υ                      | Υ    |

| All clock<br>source | TIMx                        | Clock source used as input channel for RC measurement and trimming | Y   | Y     | Y                    | Y                      | -    |

| USB                 | CRS/HSI48                   | the clock recovery<br>system trims the HSI48<br>based on USB SOF   | Y   | Y     | -                    | -                      | -    |

|                     | TIM3                        | USB_SOF is channel input for calibration                           | Y   | Y     | -                    | -                      | -    |

| GPIO                | TIMx                        | Timer input channel and trigger                                    | Y   | Y     | Y                    | Y                      | -    |

|                     | LPTIM                       | Timer input channel and trigger                                    | Y   | Y     | Y                    | Y                      | Y    |

|                     | ADC,DAC                     | Conversion trigger                                                 | Υ   | Υ     | Υ                    | Y                      | -    |

## 3.3 ARM® Cortex®-M0+ core with MPU

The Cortex-M0+ processor is an entry-level 32-bit ARM Cortex processor designed for a broad range of embedded applications. It offers significant benefits to developers, including:

- a simple architecture that is easy to learn and program

- ultra-low power, energy-efficient operation

- excellent code density

- deterministic, high-performance interrupt handling

- upward compatibility with Cortex-M processor family

- platform security robustness, with integrated Memory Protection Unit (MPU).

The Cortex-M0+ processor is built on a highly area and power optimized 32-bit processor core, with a 2-stage pipeline Von Neumann architecture. The processor delivers exceptional energy efficiency through a small but powerful instruction set and extensively optimized design, providing high-end processing hardware including a single-cycle multiplier.

The Cortex-M0+ processor provides the exceptional performance expected of a modern 32-bit architecture, with a higher code density than other 8-bit and 16-bit microcontrollers.

Owing to its embedded ARM core, the STM32L082xx are compatible with all ARM tools and software.

#### **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L082xx embed a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels and 4 priority levels.

The Cortex-M0+ processor closely integrates a configurable Nested Vectored Interrupt Controller (NVIC), to deliver industry-leading interrupt performance. The NVIC:

- includes a Non-Maskable Interrupt (NMI)

- provides zero jitter interrupt option

- provides four interrupt priority levels

The tight integration of the processor core and NVIC provides fast execution of Interrupt Service Routines (ISRs), dramatically reducing the interrupt latency. This is achieved through the hardware stacking of registers, and the ability to abandon and restart load-multiple and store-multiple operations. Interrupt handlers do not require any assembler wrapper code, removing any code overhead from the ISRs. Tail-chaining optimization also significantly reduces the overhead when switching from one ISR to another.

To optimize low-power designs, the NVIC integrates with the sleep modes, that include a deep sleep function that enables the entire device to enter rapidly stop or standby mode.

This hardware block provides flexible interrupt management features with minimal interrupt latency.

20/119 DocID027099 Rev 4

#### 3.4 Reset and supply management

#### 3.4.1 Power supply schemes

•  $V_{DD}$  = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- V<sub>SSA</sub>, V<sub>DDA</sub> = 1.65 to 3.6 V: external analog power supplies for ADC reset blocks, RCs and PLL. V<sub>DDA</sub> and V<sub>SSA</sub> must be connected to V<sub>DD</sub> and V<sub>SS</sub>, respectively.

- V<sub>DD\_USB</sub> = 1.65 to 3.6V: external power supply for USB transceiver, USB\_DM (PA11) and USB\_DP (PA12). To guarantee a correct voltage level for USB communication V<sub>DD\_USB</sub> must be above 3.0V. If USB is not used this pin must be tied to V<sub>DD</sub>.

#### 3.4.2 Power supply supervisor

The devices have an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

Two versions are available:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the VDD min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area.

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the start-up time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.

The devices feature an embedded programmable voltage detector (PVD) that monitors the  $V_{DD/VDDA}$  power supply and compares it to the  $V_{PVD}$  threshold. This PVD offers 7 different levels between 1.85 V and 3.05 V, chosen by software, with a step around 200 mV. An interrupt can be generated when  $V_{DD/VDDA}$  drops below the  $V_{PVD}$  threshold and/or when  $V_{DD/VDDA}$  is higher than the  $V_{PVD}$  threshold. The interrupt service routine can then generate a warning message and/or put the MCU into a safe state. The PVD is enabled by software.

#### 3.4.3 Voltage regulator

The regulator has three operation modes: main (MR), low power (LPR) and power down.

- MR is used in Run mode (nominal regulation)

- LPR is used in the Low-power run, Low-power sleep and Stop modes

- Power down is used in Standby mode. The regulator output is high impedance, the kernel circuitry is powered down, inducing zero consumption but the contents of the registers and RAM are lost except for the standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE crystal 32 KHz oscillator, RCC CSR).

#### 3.5 Clock management

The clock controller distributes the clocks coming from different oscillators to the core and the peripherals. It also manages clock gating for low-power modes and ensures clock robustness. It features:

#### • Clock prescaler

To get the best trade-off between speed and current consumption, the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

#### Safe clock switching

Clock sources can be changed safely on the fly in Run mode through a configuration register.

#### • Clock management

To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

#### System clock source

Three different clock sources can be used to drive the master clock SYSCLK:

- 1-25 MHz high-speed external crystal (HSE), that can supply a PLL

- 16 MHz high-speed internal RC oscillator (HSI), trimmable by software, that can supply a PLLMultispeed internal RC oscillator (MSI), trimmable by software, able to generate 7 frequencies (65 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.1 MHz, 4.2 MHz). When a 32.768 kHz clock source is available in the system (LSE), the MSI frequency can be trimmed by software down to a ±0.5% accuracy.

#### Auxiliary clock source

Two ultra-low-power clock sources that can be used to drive the real-time clock:

- 32.768 kHz low-speed external crystal (LSE)

- 37 kHz low-speed internal RC (LSI), also used to drive the independent watchdog.

The LSI clock can be measured using the high-speed internal RC oscillator for greater precision.

#### • RTC clock source

The LSI, LSE or HSE sources can be chosen to clock the RTC, whatever the system clock.

#### USB clock source

A 48 MHz clock trimmed through the USB SOF or LSE supplies the USB interface.

22/119 DocID027099 Rev 4

#### Startup clock

After reset, the microcontroller restarts by default with an internal 2.1 MHz clock (MSI). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

#### Clock security system (CSS)

This feature can be enabled by software. If an HSE clock failure occurs, the master clock is automatically switched to HSI and a software interrupt is generated if enabled. Another clock security system can be enabled, in case of failure of the LSE it provides an interrupt or wakeup event which is generated if enabled.

Clock-out capability (MCO: microcontroller clock output)

It outputs one of the internal clocks for external use by the application.

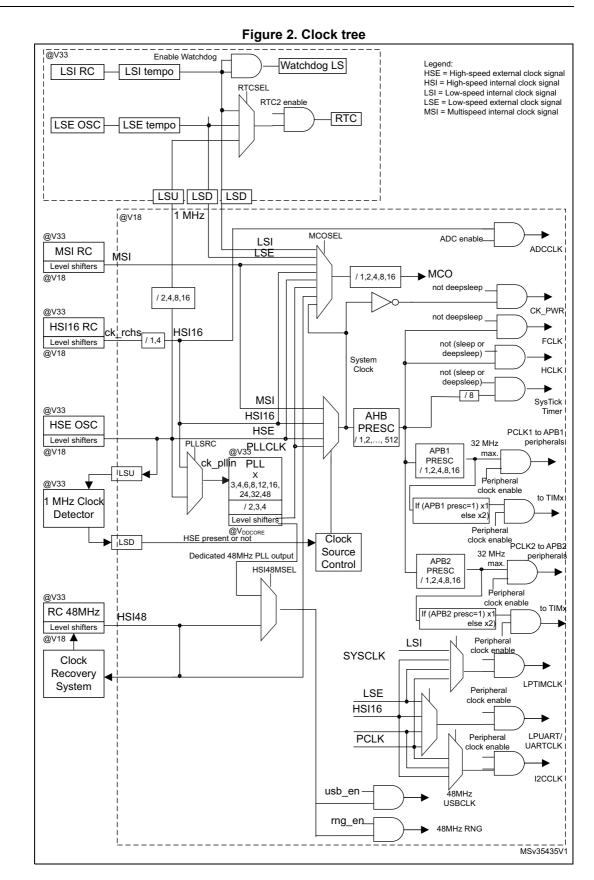

Several prescalers allow the configuration of the AHB frequency, each APB (APB1 and APB2) domains. The maximum frequency of the AHB and the APB domains is 32 MHz. See *Figure 2* for details on the clock tree.

#### 3.6 Low-power real-time clock and backup registers

The real time clock (RTC) and the 5 backup registers are supplied in all modes including standby mode. The backup registers are five 32-bit registers used to store 20 bytes of user application data. They are not reset by a system reset, or when the device wakes up from Standby mode.

The RTC is an independent BCD timer/counter. Its main features are the following:

- Calendar with subsecond, seconds, minutes, hours (12 or 24 format), week day, date, month, year, in BCD (binary-coded decimal) format

- Automatically correction for 28, 29 (leap year), 30, and 31 day of the month

- Two programmable alarms with wake up from Stop and Standby mode capability

- Periodic wakeup from Stop and Standby with programmable resolution and period

- On-the-fly correction from 1 to 32767 RTC clock pulses. This can be used to synchronize it with a master clock.

- Reference clock detection: a more precise second source clock (50 or 60 Hz) can be used to enhance the calendar precision.

- Digital calibration circuit with 1 ppm resolution, to compensate for quartz crystal inaccuracy

- 2 anti-tamper detection pins with programmable filter. The MCU can be woken up from Stop and Standby modes on tamper event detection.

- Timestamp feature which can be used to save the calendar content. This function can be triggered by an event on the timestamp pin, or by a tamper event. The MCU can be woken up from Stop and Standby modes on timestamp event detection.

The RTC clock sources can be:

- A 32.768 kHz external crystal

- A resonator or oscillator

- The internal low-power RC oscillator (typical frequency of 37 kHz)

- The high-speed external clock

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions, and can be individually remapped using dedicated alternate function registers. All GPIOs are high current capable. Each GPIO output, speed can be slowed (40 MHz, 10 MHz, 2 MHz, 400 kHz). The alternate function configuration of I/Os can be locked if needed following a specific sequence in order to avoid spurious writing to the I/O registers. The I/O controller is connected to a dedicated IO bus with a toggling speed of up to 32 MHz.

#### **Extended interrupt/event controller (EXTI)**

The extended interrupt/event controller consists of 29 edge detector lines used to generate interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 40 GPIOs can be connected to the 16 configurable interrupt/event lines. The 13 other lines are connected to PVD, RTC, USB, USARTs, I2C, LPUART, LPTIMER or comparator events.