Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STM32L15xQC STM32L15xRC-A STM32L15xVC-A STM32L15xVC

Ultra-low-power 32b MCU ARM®-based Cortex®-M3, 256KB Flash, 32KB SRAM, 8KB EEPROM, LCD, USB, ADC, DAC

Datasheet - production data

#### **Features**

- Ultra-low-power platform

- 1.65 V to 3.6 V power supply

- -40°C to 105°C temperature range

- 305 nA standby mode (3 wakeup pins)

- 1.15 μA standby mode + RTC

- 0.475 μA stop mode (16 wakeup lines)

- 1.35 µA stop mode + RTC

- 11 μA Low-power run mode

- 230 µA/MHz run mode

- 10 nA ultra-low I/O leakage

- 8 µs wakeup time

- Core: ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit CPU

- From 32 kHz up to 32 MHz max

- 1.25 DMIPS/MHz (Dhrystone 2.1)

- Memory protection unit

- Up to 23 capacitive sensing channels

- CRC calculation unit, 96-bit unique ID

- · Reset and supply management

- Low-power, ultrasafe BOR (brownout reset) with 5 selectable thresholds

- Ultra-low-power POR/PDR

- Programmable voltage detector (PVD)

- Clock sources

- 1 to 24 MHz crystal oscillator

- 32 kHz oscillator for RTC with calibration

- High Speed Internal 16 MHz factorytrimmed RC (+/- 1%)

- Internal low-power 37 kHz RC

- Internal multispeed low-power 65 kHz to 4.2 MHz

- PLL for CPU clock and USB (48 MHz)

- · Pre-programmed bootloader

- USB and USART supported

- Serial wire debug, JTAG and trace

- Up to 116 fast I/Os (102 I/Os 5V tolerant), all mappable on 16 external interrupt vectors

- Memories

- 256 KB Flash with ECC

- 32 KB RAM

- 8 KB of true EEPROM with ECC

- 128-byte backup register

- LCD driver (except STM32L151xC/C-A devices) up to 8x40 segments, contrast adjustment, blinking mode, step-up converter

- Rich analog peripherals (down to 1.8V)

- 2x operational amplifiers

- 12-bit ADC 1 Msps up to 40 channels

- 12-bit DAC 2 ch with output buffers

- 2x ultra-low-power-comparators (window mode and wake up capability)

- DMA controller 12x channels

- 9x peripheral communication interfaces

- 1x USB 2.0 (internal 48 MHz PLL)

- 3x USARTs

- Up to 8x SPIs (2x I2S, 3x 16 Mbit/s)

- 2x I2Cs (SMBus/PMBus)

- 11x timers: 1x 32-bit, 6x 16-bit with up to 4 IC/OC/PWM channels, 2x 16-bit basic timers, 2x watchdog timers (independent and window)

Table 1. Device summary

| Reference     | Part numbers                  |

|---------------|-------------------------------|

| STM32L151QC   | STM32L151QCH6                 |

| STM32L151RC-A | STM32L151RCT6A, STM32L151RCY6 |

| STM32L151VC-A | STM32L151VCT6A                |

| STM32L151ZC   | STM32L151ZCT6                 |

| STM32L152QC   | STM32L152QCH6                 |

| STM32L152RC-A | STM32L152RCT6A                |

| STM32L152VC-A | STM32L152VCT6A                |

| STM32L152ZC   | STM32L152ZCT6                 |

# **Contents**

| 1 | Intro | duction            | 1                                                 | 9   |

|---|-------|--------------------|---------------------------------------------------|-----|

| 2 | Desc  | ription            |                                                   | 10  |

|   | 2.1   | Device             | overview                                          |     |

|   | 2.2   | Ultra-lo           | ow-power device continuum                         | 12  |

|   |       | 2.2.1              | Performance                                       | 12  |

|   |       | 2.2.2              | Shared peripherals                                | 12  |

|   |       | 2.2.3              | Common system strategy                            | 12  |

|   |       | 2.2.4              | Features                                          | 12  |

| 3 | Fund  | tional o           | overview                                          | 13  |

|   | 3.1   | Low-po             | ower modes                                        | 14  |

|   | 3.2   | $ARM^{\mathbb{R}}$ | Cortex®-M3 core with MPU                          | 18  |

|   | 3.3   | Reset              | and supply management                             | 19  |

|   |       | 3.3.1              | Power supply schemes                              | 19  |

|   |       | 3.3.2              | Power supply supervisor                           | 19  |

|   |       | 3.3.3              | Voltage regulator                                 | 20  |

|   |       | 3.3.4              | Boot modes                                        | 20  |

|   | 3.4   | Clock              | management                                        | 21  |

|   | 3.5   | Low-po             | ower real-time clock and backup registers         | 23  |

|   | 3.6   | GPIOs              | s (general-purpose inputs/outputs)                | 23  |

|   | 3.7   | Memo               | ries                                              | 24  |

|   | 3.8   | DMA (              | direct memory access)                             | 24  |

|   | 3.9   | LCD (I             | iquid crystal display)                            | 25  |

|   | 3.10  | ADC (a             | analog-to-digital converter)                      | 25  |

|   |       | 3.10.1             | Temperature sensor                                |     |

|   |       | 3.10.2             | Internal voltage reference (V <sub>REFINT</sub> ) | 26  |

|   | 3.11  | DAC (              | digital-to-analog converter)                      | 26  |

|   | 3.12  | Operat             | tional amplifier                                  | 26  |

|   | 3.13  |                    | ow-power comparators and reference voltage        |     |

|   | 3.14  |                    | n configuration controller and routing interface  |     |

|   | 3.15  | •                  | sensing                                           |     |

|   |       |                    | <b>5</b>                                          | = - |

|        | 3.16                 | Timers                                                                                                                               | and watchdogs                                                                                                                                                                                                                 | . 28                                                                                               |

|--------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

|        |                      | 3.16.1                                                                                                                               | General-purpose timers (TIM2, TIM3, TIM4, TIM5, TIM9, TIM10 and TIM11)                                                                                                                                                        | . 28                                                                                               |

|        |                      | 3.16.2                                                                                                                               | Basic timers (TIM6 and TIM7)                                                                                                                                                                                                  | . 29                                                                                               |

|        |                      | 3.16.3                                                                                                                               | SysTick timer                                                                                                                                                                                                                 | . 29                                                                                               |

|        |                      | 3.16.4                                                                                                                               | Independent watchdog (IWDG)                                                                                                                                                                                                   | . 29                                                                                               |

|        |                      | 3.16.5                                                                                                                               | Window watchdog (WWDG)                                                                                                                                                                                                        | . 29                                                                                               |

|        | 3.17                 | Commi                                                                                                                                | unication interfaces                                                                                                                                                                                                          | . 29                                                                                               |

|        |                      | 3.17.1                                                                                                                               | I <sup>2</sup> C bus                                                                                                                                                                                                          | . 29                                                                                               |

|        |                      | 3.17.2                                                                                                                               | Universal synchronous/asynchronous receiver transmitter (USART) .                                                                                                                                                             | . 29                                                                                               |

|        |                      | 3.17.3                                                                                                                               | Serial peripheral interface (SPI)                                                                                                                                                                                             | . 30                                                                                               |

|        |                      | 3.17.4                                                                                                                               | Inter-integrated sound (I2S)                                                                                                                                                                                                  | . 30                                                                                               |

|        |                      | 3.17.5                                                                                                                               | Universal serial bus (USB)                                                                                                                                                                                                    | . 30                                                                                               |

|        | 3.18                 | CRC (d                                                                                                                               | cyclic redundancy check) calculation unit                                                                                                                                                                                     | . 30                                                                                               |

|        | 3.19                 | Develo                                                                                                                               | pment support                                                                                                                                                                                                                 | . 31                                                                                               |

|        |                      | 3.19.1                                                                                                                               | Serial wire JTAG debug port (SWJ-DP)                                                                                                                                                                                          | . 31                                                                                               |

|        |                      | 3.19.2                                                                                                                               | Embedded Trace Macrocell <sup>TM</sup>                                                                                                                                                                                        | . 31                                                                                               |

| 4      | Pin d                | lescript                                                                                                                             | ions                                                                                                                                                                                                                          | . 32                                                                                               |

| 4<br>5 |                      | •                                                                                                                                    | oping                                                                                                                                                                                                                         |                                                                                                    |

| 5      | Mem                  | ory ma                                                                                                                               |                                                                                                                                                                                                                               | . 54                                                                                               |

| 5      | Mem                  | ory ma <sub>l</sub>                                                                                                                  | oping                                                                                                                                                                                                                         | . 54<br>. 55                                                                                       |

| 5      | Mem<br>Elect         | ory ma <sub>l</sub>                                                                                                                  | aracteristics                                                                                                                                                                                                                 | . <b>54</b><br>. <b>55</b>                                                                         |

|        | Mem<br>Elect         | ory map<br>crical ch                                                                                                                 | ppingaracteristics                                                                                                                                                                                                            | . <b>54</b><br>. <b>55</b><br>. 55                                                                 |

| 5      | Mem<br>Elect         | ory map<br>crical ch<br>Parame<br>6.1.1                                                                                              | pping                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55                                                                       |

| 5      | Mem<br>Elect         | ory map<br>trical ch<br>Parame<br>6.1.1<br>6.1.2                                                                                     | pping                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55 . 55                                                                  |

| 5      | Mem<br>Elect         | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3                                                                            | pping                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55 . 55 . 55                                                             |

| 5      | Mem<br>Elect         | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4                                                                   | paracteristics eter conditions Minimum and maximum values Typical values Typical curves Loading capacitor                                                                                                                     | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55                                                        |

| 5      | Mem<br>Elect         | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5                                                          | pping                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 55 . 55                                              |

| 5      | Mem<br>Elect         | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6                                                 | poping  paracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme                                                                 | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 55 . 55                                              |

| 5      | Mem<br>Elect         | ory map<br>trical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8                               | pring                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 55 . 55 . 57                                         |

| 5      | Mem<br>Elect<br>6.1  | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolu                     | caracteristics eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Optional LCD power supply scheme  Current consumption measurement      | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 55 . 57 . 57                                         |

| 5      | <b>Mem Elect</b> 6.1 | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolu                     | eter conditions  Minimum and maximum values  Typical values  Typical curves  Loading capacitor  Pin input voltage  Power supply scheme  Optional LCD power supply scheme  Current consumption measurement  te maximum ratings | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 56 . 57 . 57 . 58                                    |

| 5      | <b>Mem Elect</b> 6.1 | ory map<br>crical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat          | pring                                                                                                                                                                                                                         | . <b>54</b> . <b>55</b> . 55 . 55 . 55 . 55 . 57 . 57 . 58 . 59                                    |

| 5      | <b>Mem Elect</b> 6.1 | ory map<br>trical ch<br>Parame<br>6.1.1<br>6.1.2<br>6.1.3<br>6.1.4<br>6.1.5<br>6.1.6<br>6.1.7<br>6.1.8<br>Absolut<br>Operat<br>6.3.1 | poping                                                                                                                                                                                                                        | . <b>54</b><br>. <b>55</b><br>. 55<br>. 55<br>. 55<br>. 55<br>. 57<br>. 57<br>. 58<br>. 59<br>. 60 |

| 9 | Revi | sion His  | story                                                                        |

|---|------|-----------|------------------------------------------------------------------------------|

| 8 | Part | number    | ring13                                                                       |

|   |      | 7.6.1     | Reference document                                                           |

|   | 7.6  | Therma    | al characteristics                                                           |

|   | 7.5  | WLCSI     | P64, 0.4 mm pitch wafer level chip scale package information 12              |

|   | 7.4  |           | A132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid ackage information |

|   | 7.3  |           | 34, 10 x 10 mm, 64-pin low-profile quad flat package<br>ation                |

|   | 7.2  | informa   | 00, 14 x 14 mm, 100-pin low-profile quad flat package ation11                |

|   | 7.1  | informa   | 44, 20 x 20 mm, 144-pin low-profile quad flat package ation                  |

| 7 | Pack | cage info | ormation                                                                     |

|   |      | 6.3.22    | LCD controller                                                               |

|   |      | 6.3.21    | Comparator                                                                   |

|   |      | 6.3.20    | Temperature sensor characteristics                                           |

|   |      | 6.3.19    | Operational amplifier characteristics                                        |

|   |      | 6.3.18    | DAC electrical specifications                                                |

|   |      | 6.3.17    | 12-bit ADC characteristics                                                   |

|   |      | 6.3.16    | Communications interfaces                                                    |

|   |      | 6.3.15    | TIM timer characteristics                                                    |

|   |      | 6.3.14    | NRST pin characteristics                                                     |

|   |      | 6.3.13    | I/O port characteristics                                                     |

|   |      | 6.3.12    | I/O current injection characteristics                                        |

|   |      | 6.3.11    | Electrical sensitivity characteristics                                       |

|   |      | 6.3.10    | EMC characteristics                                                          |

|   |      | 6.3.9     | Memory characteristics                                                       |

|   |      | 6.3.8     | PLL characteristics                                                          |

|   |      | 6.3.7     | Internal clock source characteristics                                        |

|   |      | 6.3.6     | External clock source characteristics                                        |

|   |      | 6.3.5     | Wakeup time from low-power mode                                              |

|   |      | 6.3.4     | Supply current characteristics                                               |

# List of tables

| Table 1.  | Device summary                                                                | 1  |

|-----------|-------------------------------------------------------------------------------|----|

| Table 2.  | Ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A device features           |    |

|           | and peripheral counts                                                         | 11 |

| Table 3.  | Functionalities depending on the operating power supply range                 | 15 |

| Table 4.  | CPU frequency range depending on dynamic voltage scaling                      | 16 |

| Table 5.  | Functionalities depending on the working mode (from Run/active down to        |    |

|           | standby)                                                                      | 17 |

| Table 6.  | Timer feature comparison                                                      | 28 |

| Table 7.  | Legend/abbreviations used in the pinout table                                 | 37 |

| Table 8.  | STM32L151xC/C-A and STM32L152xC/C-A pin definitions                           | 37 |

| Table 9.  | Alternate function input/output                                               |    |

| Table 10. | Voltage characteristics                                                       | 58 |

| Table 11. | Current characteristics                                                       |    |

| Table 12. | Thermal characteristics                                                       | 59 |

| Table 13. | General operating conditions                                                  | 59 |

| Table 14. | Embedded reset and power control block characteristics                        | 60 |

| Table 15. | Embedded internal reference voltage calibration values                        | 62 |

| Table 16. | Embedded internal reference voltage                                           | 62 |

| Table 17. | Current consumption in Run mode, code with data processing running from Flash | 64 |

| Table 18. | Current consumption in Run mode, code with data processing running from RAM   |    |

| Table 19. | Current consumption in Sleep mode                                             |    |

| Table 20. | Current consumption in Low-power run mode                                     |    |

| Table 21. | Current consumption in Low-power sleep mode                                   |    |

| Table 22. | Typical and maximum current consumptions in Stop mode                         |    |

| Table 23. | Typical and maximum current consumptions in Standby mode                      |    |

| Table 24. | Peripheral current consumption                                                |    |

| Table 25. | Low-power mode wakeup timings                                                 |    |

| Table 26. | High-speed external user clock characteristics                                |    |

| Table 27. | Low-speed external user clock characteristics                                 |    |

| Table 28. | HSE oscillator characteristics                                                |    |

| Table 29. | LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz)                |    |

| Table 30. | HSI oscillator characteristics                                                |    |

| Table 31. | LSI oscillator characteristics                                                |    |

| Table 32. | MSI oscillator characteristics                                                |    |

| Table 33. | PLL characteristics                                                           |    |

| Table 34. | RAM and hardware registers                                                    |    |

| Table 35. | Flash memory and data EEPROM characteristics                                  |    |

| Table 36. | Flash memory and data EEPROM endurance and retention                          |    |

| Table 37. | EMS characteristics                                                           |    |

| Table 38. | EMI characteristics                                                           |    |

| Table 39. | ESD absolute maximum ratings                                                  |    |

| Table 40. | Electrical sensitivities                                                      |    |

| Table 41. | I/O current injection susceptibility                                          |    |

| Table 42. | I/O static characteristics                                                    |    |

| Table 43. | Output voltage characteristics                                                |    |

| Table 44. | I/O AC characteristics                                                        |    |

| Table 45. | NRST pin characteristics                                                      |    |

| Table 46. | TIMx characteristics                                                          |    |

|           |                                                                               |    |

#### List of tables

| Table 47. | I <sup>2</sup> C characteristics                                               | 94  |

|-----------|--------------------------------------------------------------------------------|-----|

| Table 48. | SCL frequency (f <sub>PCLK1</sub> = 32 MHz, V <sub>DD</sub> = VDD_I2C = 3.3 V) | 95  |

| Table 49. | SPI characteristics                                                            |     |

| Table 50. | USB startup time                                                               | 99  |

| Table 51. | USB DC electrical characteristics                                              | 99  |

| Table 52. | USB: full speed electrical characteristics                                     | 99  |

| Table 53. | I2S characteristics                                                            | 100 |

| Table 54. | ADC clock frequency                                                            | 102 |

| Table 55. | ADC characteristics                                                            | 102 |

| Table 56. | ADC accuracy                                                                   | 104 |

| Table 57. | Maximum source impedance R <sub>AIN</sub> max                                  | 106 |

| Table 58. | DAC characteristics                                                            | 107 |

| Table 59. | Operational amplifier characteristics                                          |     |

| Table 60. | Temperature sensor calibration values                                          | 111 |

| Table 61. | Temperature sensor characteristics                                             | 111 |

| Table 62. | Comparator 1 characteristics                                                   |     |

| Table 63. | Comparator 2 characteristics                                                   | 112 |

| Table 64. | LCD controller characteristics                                                 | 113 |

| Table 65. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package mechanical data     | 115 |

| Table 66. | LQPF100, 14 x 14 mm, 100-pin low-profile quad flat package mechanical data     |     |

| Table 67. | LQFP64, 10 x 10 mm 64-pin low-profile quad flat package mechanical data        | 120 |

| Table 68. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array            |     |

|           | package mechanical data                                                        |     |

| Table 69. | WLCSP64, 0.4 mm pitch wafer level chip scale package mechanical data           |     |

| Table 70. | WLCSP64, 0.4 mm pitch package recommended PCB design rules                     |     |

| Table 71. | Thermal characteristics                                                        |     |

| Table 72. | STM32L151xC/C-A and STM32L152xC/C-A ordering information scheme                |     |

| Table 73. | Document revision history                                                      | 132 |

# List of figures

| Figure 1.  | Ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A block diagram                   | 13  |

|------------|-------------------------------------------------------------------------------------|-----|

| Figure 2.  | Clock tree                                                                          |     |

| Figure 3.  | STM32L15xZC LQFP144 pinout                                                          | 32  |

| Figure 4.  | STM32L15xQC UFBGA132 ballout                                                        | 33  |

| Figure 5.  | STM32L15xVC-A LQFP100 pinout                                                        | 34  |

| Figure 6.  | STM32L15xRC-A LQFP64 pinout                                                         | 35  |

| Figure 7.  | STM32L15xRC WLCSP64 ballout                                                         | 36  |

| Figure 8.  | Memory map                                                                          | 54  |

| Figure 9.  | Pin loading conditions                                                              | 55  |

| Figure 10. | Pin input voltage                                                                   | 55  |

| Figure 11. | Power supply scheme                                                                 | 56  |

| Figure 12. | Optional LCD power supply scheme                                                    | 57  |

| Figure 13. | Current consumption measurement scheme                                              | 57  |

| Figure 14. | High-speed external clock source AC timing diagram                                  | 76  |

| Figure 15. | Low-speed external clock source AC timing diagram                                   |     |

| Figure 16. | HSE oscillator circuit diagram                                                      |     |

| Figure 17. | Typical application with a 32.768 kHz crystal                                       | 80  |

| Figure 18. | I/O AC characteristics definition                                                   |     |

| Figure 19. | Recommended NRST pin protection                                                     | 93  |

| Figure 20. | I <sup>2</sup> C bus AC waveforms and measurement circuit                           |     |

| Figure 21. | SPI timing diagram - slave mode and CPHA = 0                                        | 97  |

| Figure 22. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                         |     |

| Figure 23. | SPI timing diagram - master mode <sup>(1)</sup>                                     | 98  |

| Figure 24. | USB timings: definition of data signal rise and fall time                           |     |

| Figure 25. | I <sup>2</sup> S slave timing diagram (Philips protocol) <sup>(1)</sup>             |     |

| Figure 26. | I <sup>2</sup> S master timing diagram (Philips protocol) <sup>(1)</sup>            | 101 |

| Figure 27. | ADC accuracy characteristics                                                        |     |

| Figure 28. | Typical connection diagram using the ADC                                            |     |

| Figure 29. | Maximum dynamic current consumption on V <sub>REF+</sub> supply pin during ADC      |     |

| · ·        | conversion                                                                          | 106 |

| Figure 30. | 12-bit buffered /non-buffered DAC                                                   |     |

| Figure 31. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline                  |     |

| Figure 32. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package                          |     |

| Ü          | recommended footprint                                                               | 116 |

| Figure 33. | LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package top view example.        |     |

| Figure 34. | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package outline                  |     |

| Figure 35. | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package                          |     |

| Ü          | recommended footprint                                                               | 118 |

| Figure 36. | LQFP100, 14 x 14 mm, 100-pin low-profile quad flat package top view example.        | 119 |

| Figure 37. | LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package outline                    |     |

| Figure 38. | LQFP64, 10 x 10 mm, 64-pin low-profile quad flat package                            |     |

| Ü          | recommended footprint                                                               | 121 |

| Figure 39. | LQFP64 10 x 10 mm, 64-pin low-profile quad flat package top view example            |     |

| Figure 40. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package outline |     |

| Figure 41. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package         |     |

| J          | recommended footprint                                                               | 124 |

| Figure 42. | UFBGA132, 7 x 7 mm, 132-ball ultra thin, fine-pitch ball grid array package         |     |

| J          | top view example                                                                    | 125 |

|            |                                                                                     |     |

# List of figures

### STM32L151xC/C-A STM32L152xC/C-A

| Figure 43. | WLCSP64, 0.4 mm pitch wafer level chip scale package outline          | 126 |

|------------|-----------------------------------------------------------------------|-----|

| Figure 44. | WLCSP64, 0.4 mm pitch wafer level chip scale package                  |     |

|            | recommended footprint                                                 | 127 |

| Figure 45. | WLCSP64, 0.4 mm pitch wafer level chip scale package top view example | 128 |

| Figure 46. | Thermal resistance suffix 6                                           | 130 |

| Figure 47. | Thermal resistance suffix 7                                           | 130 |

### 1 Introduction

This datasheet provides the ordering information and mechanical device characteristics of the STM32L151xC/C-A and STM32L152xC/C-A ultra-low-power ARM<sup>®</sup> Cortex<sup>®</sup>-M3 based microcontroller product line.

The STM32L151xC/C-A and STM32L152xC/C-A microcontrollers feature 256 Kbytes of Flash memory.

The ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A devices are available in 5 different package types: from 64 pins to 144 pins. Depending on the device chosen, different sets of peripherals are included, the description below gives an overview of the complete range of peripherals proposed in this family.

These features make the ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A microcontroller family suitable for a wide range of applications:

- Medical and handheld equipment

- Application control and user interface

- PC peripherals, gaming, GPS and sport equipment

- Alarm systems, wired and wireless sensors, video intercom

- · Utility metering

This STM32L151xC/C-A and STM32L152xC/C-A datasheet should be read in conjunction with the STM32L1xxxx reference manual (RM0038). The application note "Getting started with STM32L1xxxx hardware development" (AN3216) gives a hardware implementation overview. Both documents are available from the STMicroelectronics website www.st.com.

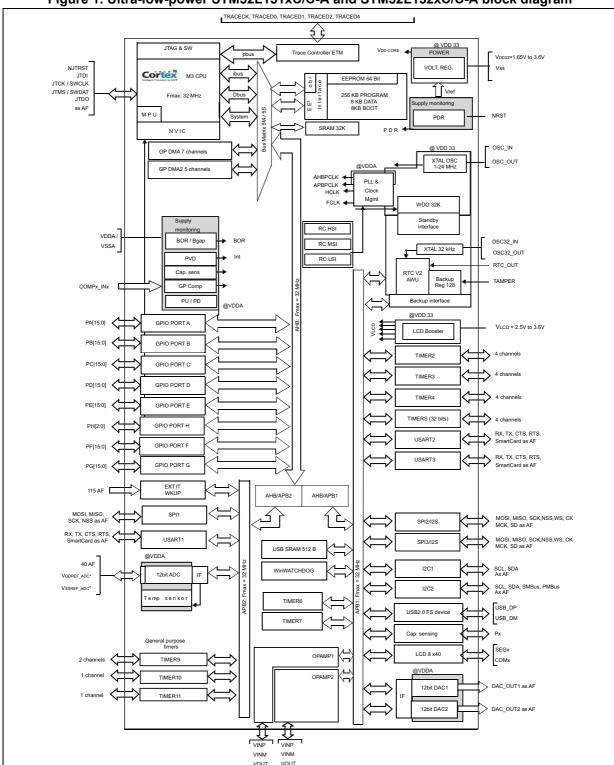

For information on the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core please refer to the ARM<sup>®</sup> Cortex<sup>®</sup>-M3 technical reference manual, available from the www.arm.com website. *Figure 1* shows the general block diagram of the device family.

# 2 Description

The ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A devices incorporate the connectivity power of the universal serial bus (USB) with the high-performance ARM<sup>®</sup> Cortex<sup>®</sup>-M3 32-bit RISC core operating at a frequency of 32 MHz (33.3 DMIPS), a memory protection unit (MPU), high-speed embedded memories (Flash memory up to 256 Kbytes and RAM up to 32 Kbytes), and an extensive range of enhanced I/Os and peripherals connected to two APB buses.

The STM32L151xC/C-A and STM32L152xC/C-A devices offer two operational amplifiers, one 12-bit ADC, two DACs, two ultra-low-power comparators, one general-purpose 32-bit timer, six general-purpose 16-bit timers and two basic timers, which can be used as time bases.

Moreover, the STM32L151xC/C-A and STM32L152xC/C-A devices contain standard and advanced communication interfaces: up to two I2Cs, three SPIs, two I2S, three USARTs, and an USB. The STM32L151xC/C-A and STM32L152xC/C-A devices offer up to 23 capacitive sensing channels to simply add a touch sensing functionality to any application.

They also include a real-time clock and a set of backup registers that remain powered in Standby mode.

Finally, the integrated LCD controller (except STM32L151xC/C-A devices) has a built-in LCD voltage generator that allows to drive up to 8 multiplexed LCDs with the contrast independent of the supply voltage.

The ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A devices operate from a 1.8 to 3.6 V power supply (down to 1.65 V at power down) with BOR and from a 1.65 to 3.6 V power supply without BOR option. They are available in the -40 to +85 °C and -40 to +105 °C temperature ranges. A comprehensive set of power-saving modes allows the design of low-power applications.

10/134 DocID026119 Rev 6

# 2.1 Device overview

Table 2. Ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A device features and peripheral counts

| Peripheral                                    |                     | STM32L15xRC-A                                                                                           | STM32L15xVC-A          | STM32L15xQC      | STM32L15xZC |  |  |

|-----------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------|------------------------|------------------|-------------|--|--|

| Flash (Kbytes)                                |                     | 256                                                                                                     |                        |                  |             |  |  |

| Data EEPRON                                   | /I (Kbytes)         | 8                                                                                                       |                        |                  |             |  |  |

| RAM (Kbytes)                                  |                     |                                                                                                         | 32                     |                  |             |  |  |

|                                               | 32 bit              | 6                                                                                                       |                        |                  |             |  |  |

| Timers                                        | General-<br>purpose |                                                                                                         |                        |                  |             |  |  |

|                                               | Basic               |                                                                                                         | 2                      | 2                |             |  |  |

|                                               | SPI                 |                                                                                                         | 8(3                    | ) <sup>(1)</sup> |             |  |  |

| Communi-                                      | I <sup>2</sup> S    |                                                                                                         | 2                      | 2                |             |  |  |

| cation                                        | I <sup>2</sup> C    |                                                                                                         | 2                      | 2                |             |  |  |

| interraces                                    | USART               | 3                                                                                                       |                        |                  |             |  |  |

|                                               | USB                 | 1                                                                                                       |                        |                  |             |  |  |

| GPIOs                                         |                     | 51                                                                                                      | 83                     | 109              | 115         |  |  |

| Operation am                                  | plifiers            | 2                                                                                                       |                        |                  |             |  |  |

| 12-bit synchronized ADC<br>Number of channels |                     | 1<br>21                                                                                                 | 1<br>25                | 1<br>40          | 1<br>40     |  |  |

| 12-bit DAC<br>Number of ch                    | annels              | 2 2                                                                                                     |                        |                  |             |  |  |

|                                               | 152xx devices       | 1 1                                                                                                     |                        |                  |             |  |  |

| only)<br>COM x SEG                            |                     | 4x32 or 8x28                                                                                            | 2 or 8x28 4x44 or 8x40 |                  |             |  |  |

| Comparators                                   |                     | 2                                                                                                       |                        |                  |             |  |  |

| Capacitive se                                 | nsing channels      | 23                                                                                                      |                        |                  |             |  |  |

| Max. CPU frequency                            |                     | 32 MHz                                                                                                  |                        |                  |             |  |  |

| Operating vol                                 | tage                | 1.8 V to 3.6 V (down to 1.65 V at power-down) with BOR option<br>1.65 V to 3.6 V without BOR option     |                        |                  |             |  |  |

| Operating ten                                 | nperatures          | Ambient operating temperature: -40 °C to 85 °C / -40 °C to 105 °C Junction temperature: -40 to + 110 °C |                        |                  |             |  |  |

| Packages                                      |                     | LQFP64,<br>WLCSP64                                                                                      | LQFP100                | UFBGA132         | LQFP144     |  |  |

<sup>1. 5</sup> SPIs are USART configured in synchronous mode emulating SPI master.

# 2.2 Ultra-low-power device continuum

The ultra-low-power family offers a large choice of cores and features. From proprietary 8-bit to up to Cortex-M3, including the Cortex-M0+, the STM32Lx series are the best choice to answer the user needs, in terms of ultra-low-power features. The STM32 ultra-low-power series are the best fit, for instance, for gas/water meter, keyboard/mouse or fitness and healthcare, wearable applications. Several built-in features like LCD drivers, dual-bank memory, Low-power run mode, op-amp, AES 128-bit, DAC, USB crystal-less and many others will clearly allow to build very cost-optimized applications by reducing BOM.

Note:

STMicroelectronics as a reliable and long-term manufacturer ensures as much as possible the pin-to-pin compatibility between any STM8Lxxxxx and STM32Lxxxxx devices and between any of the STM32Lx and STM32Fx series. Thanks to this unprecedented scalability, the old applications can be upgraded to respond to the latest market features and efficiency demand.

#### 2.2.1 Performance

All the families incorporate highly energy-efficient cores with both Harvard architecture and pipelined execution: advanced STM8 core for STM8L families and ARM Cortex-M3 core for STM32L family. In addition specific care for the design architecture has been taken to optimize the mA/DMIPS and mA/MHz ratios.

This allows the ultra-low-power performance to range from 5 up to 33.3 DMIPs.

### 2.2.2 Shared peripherals

STM8L15xxx, STM32L15xxx and STM32L162xx share identical peripherals which ensure a very easy migration from one family to another:

- Analog peripherals: ADC, DAC and comparators

- Digital peripherals: RTC and some communication interfaces

#### 2.2.3 Common system strategy.

To offer flexibility and optimize performance, the STM8L15xxx, STM32L15xxx and STM32L162xx family uses a common architecture:

- Same power supply range from 1.65 V to 3.6 V

- Architecture optimized to reach ultra-low consumption both in low-power modes and Run mode

- Fast startup strategy from low-power modes

- Flexible system clock

- Ultrasafe reset: same reset strategy including power-on reset, power-down reset, brownout reset and programmable voltage detector

#### 2.2.4 Features

ST ultra-low-power continuum also lies in feature compatibility:

- More than 15 packages with pin count from 20 to 144 pins and size down to 3 x 3 mm

- Memory density ranging from 2 to 512 Kbytes

5/

# 3 Functional overview

Figure 1. Ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A block diagram

# 3.1 Low-power modes

The ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A devices support dynamic voltage scaling to optimize its power consumption in run mode. The voltage from the internal low-drop regulator that supplies the logic can be adjusted according to the system's maximum operating frequency and the external voltage supply.

There are three power consumption ranges:

- Range 1 (V<sub>DD</sub> range limited to 1.71 V 3.6 V), with the CPU running at up to 32 MHz

- Range 2 (full V<sub>DD</sub> range), with a maximum CPU frequency of 16 MHz

- Range 3 (full V<sub>DD</sub> range), with a maximum CPU frequency limited to 4 MHz (generated only with the multispeed internal RC oscillator clock source)

Seven low-power modes are provided to achieve the best compromise between low-power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs. Sleep mode power consumption at 16 MHz is about 1 mA with all peripherals off.

#### Low-power run mode

This mode is achieved with the multispeed internal (MSI) RC oscillator set to the minimum clock (131 kHz), execution from SRAM or Flash memory, and internal regulator in low-power mode to minimize the regulator's operating current. In low-power run mode, the clock frequency and the number of enabled peripherals are both limited.

#### • Low-power sleep mode

This mode is achieved by entering Sleep mode with the internal voltage regulator in Low-power mode to minimize the regulator's operating current. In Low-power sleep mode, both the clock frequency and the number of enabled peripherals are limited; a typical example would be to have a timer running at 32 kHz.

When wakeup is triggered by an event or an interrupt, the system reverts to the run mode with the regulator on.

#### Stop mode with RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents and real time clock. All clocks in the  $V_{CORE}$  domain are stopped, the PLL, MSI RC, HSI RC and HSE crystal oscillators are disabled. The LSE or LSI is still running. The voltage regulator is in the low-power mode.

The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on), it can be the RTC alarm(s), the USB wakeup, the RTC tamper events, the RTC timestamp event or the RTC wakeup.

577

#### Stop mode without RTC

Stop mode achieves the lowest power consumption while retaining the RAM and register contents. All clocks are stopped, the PLL, MSI RC, HSI and LSI RC, LSE and HSE crystal oscillators are disabled. The voltage regulator is in the low-power mode. The device can be woken up from Stop mode by any of the EXTI line, in 8  $\mu$ s. The EXTI line source can be one of the 16 external lines. It can be the PVD output, the Comparator 1 event or Comparator 2 event (if internal reference voltage is on). It can also be wakened by the USB wakeup.

#### Standby mode with RTC

Standby mode is used to achieve the lowest power consumption and real time clock. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI RC and HSE crystal oscillators are also switched off. The LSE or LSI is still running. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC CSR).

The device exits Standby mode in 60 µs when an external reset (NRST pin), an IWDG reset, a rising edge on one of the three WKUP pins, RTC alarm (Alarm A or Alarm B), RTC tamper event, RTC timestamp event or RTC Wakeup event occurs.

#### Standby mode without RTC

Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire  $V_{CORE}$  domain is powered off. The PLL, MSI RC, HSI and LSI RC, HSE and LSE crystal oscillators are also switched off. After entering Standby mode, the RAM and register contents are lost except for registers in the Standby circuitry (wakeup logic, IWDG, RTC, LSI, LSE Crystal 32K osc, RCC\_CSR).

The device exits Standby mode in  $60~\mu s$  when an external reset (NRST pin) or a rising edge on one of the three WKUP pin occurs.

Note:

The RTC, the IWDG, and the corresponding clock sources are not stopped automatically by entering Stop or Standby mode.

Table 3. Functionalities depending on the operating power supply range

|                                                                  | Functionalities depending on the operating power supply range |                |                                   |                            |

|------------------------------------------------------------------|---------------------------------------------------------------|----------------|-----------------------------------|----------------------------|

| Operating power supply range                                     | DAC and ADC operation                                         | USB            | Dynamic voltage scaling range     | I/O operation              |

| V <sub>DD</sub> = V <sub>DDA</sub> = 1.65 to 1.71 V              | Not functional                                                | Not functional | Range 2 or<br>Range 3             | Degraded speed performance |

| V <sub>DD</sub> =V <sub>DDA</sub> = 1.71 to 1.8 V <sup>(1)</sup> | Not functional                                                | Not functional | Range 1, Range 2<br>or Range 3    | Degraded speed performance |

| $V_{DD} = V_{DDA} = 1.8 \text{ to } 2.0 \text{ V}^{(1)}$         | Conversion time up to 500 Ksps                                | Not functional | Range 1, Range 2<br>or<br>Range 3 | Degraded speed performance |

Table 3. Functionalities depending on the operating power supply range (continued)

|                                                    | Functionalities depending on the operating power supply range |                           |                                | er supply range      |

|----------------------------------------------------|---------------------------------------------------------------|---------------------------|--------------------------------|----------------------|

| Operating power supply range                       | DAC and ADC operation                                         | USB                       | Dynamic voltage scaling range  | I/O operation        |

| $V_{DD} = V_{DDA} = 2.0 \text{ to } 2.4 \text{ V}$ | Conversion time up to 500 Ksps                                | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3 | Full speed operation |

| V <sub>DD</sub> =V <sub>DDA</sub> = 2.4 to 3.6 V   | Conversion time up to 1 Msps                                  | Functional <sup>(2)</sup> | Range 1, Range 2<br>or Range 3 | Full speed operation |

CPU frequency changes from initial to final must respect "F<sub>CPU</sub> initial < 4\*F<sub>CPU</sub> final" to limit V<sub>CORE</sub> drop due to current consumption peak when frequency increases. It must also respect 5 μs delay between two changes. For example to switch from 4.2 MHz to 32 MHz, the user can switch from 4.2 MHz to 16 MHz, wait 5 μs, then switch from 16 MHz to 32 MHz.

Table 4. CPU frequency range depending on dynamic voltage scaling

| CPU frequency range                                | Dynamic voltage scaling range |

|----------------------------------------------------|-------------------------------|

| 16 MHz to 32 MHz (1ws)<br>32 kHz to 16 MHz (0ws)   | Range 1                       |

| 8 MHz to 16 MHz (1ws)<br>32 kHz to 8 MHz (0ws)     | Range 2                       |

| 2.1MHz to 4.2 MHz (1ws)<br>32 kHz to 2.1 MHz (0ws) | Range 3                       |

16/134 DocID026119 Rev 6

<sup>2.</sup> Should be USB compliant from I/O voltage standpoint, the minimum  $\rm V_{\rm DD}$  is 3.0 V.

Table 5. Functionalities depending on the working mode (from Run/active down to standby)

| lps                                       | Run/Active | Sleep | Low-         | Low-<br>power<br>Sleep | Stop |                   | Standby |                   |

|-------------------------------------------|------------|-------|--------------|------------------------|------|-------------------|---------|-------------------|

|                                           |            |       | power<br>Run |                        |      | Wakeup capability |         | Wakeup capability |

| CPU                                       | Y          |       | Y            |                        |      |                   |         |                   |

| Flash                                     | Y          | Υ     | Y            | Y                      |      |                   | -       |                   |

| RAM                                       | Υ          | Υ     | Y            | Y                      | Υ    |                   |         |                   |

| Backup Registers                          | Y          | Υ     | Y            | Y                      | Υ    |                   | Υ       |                   |

| EEPROM                                    | Υ          | Y     | Y            | Y                      | Υ    |                   |         |                   |

| Brown-out rest (BOR)                      | Y          | Υ     | Y            | Y                      | Υ    | Y                 | Υ       |                   |

| DMA                                       | Y          | Υ     | Y            | Υ                      |      |                   |         |                   |

| Programmable<br>Voltage Detector<br>(PVD) | Y          | Υ     | Y            | Y                      | Υ    | Y                 | Y       |                   |

| Power On Reset<br>(POR)                   | Y          | Y     | Y            | Y                      | Υ    | Y                 | Υ       |                   |

| Power Down Rest<br>(PDR)                  | Y          | Y     | Y            | Y                      | Υ    |                   | Υ       |                   |

| High Speed<br>Internal (HSI)              | Y          | Υ     |              |                        |      |                   | -       |                   |

| High Speed<br>External (HSE)              | Y          | Υ     |              |                        |      |                   | -       |                   |

| Low Speed Internal (LSI)                  | Υ          | Υ     | Y            | Y                      | Υ    |                   | Υ       |                   |

| Low Speed<br>External (LSE)               | Υ          | Υ     | Y            | Y                      | Υ    |                   | Υ       |                   |

| Multi-Speed<br>Internal (MSI)             | Y          | Υ     | Y            | Y                      |      |                   |         |                   |

| Inter-Connect<br>Controller               | Y          | Υ     | Y            | Y                      |      |                   |         |                   |

| RTC                                       | Y          | Υ     | Y            | Υ                      | Υ    | Y                 | Υ       |                   |

| RTC Tamper                                | Y          | Υ     | Y            | Υ                      | Υ    | Y                 | Υ       | Y                 |

| Auto WakeUp<br>(AWU)                      | Y          | Υ     | Y            | Y                      | Υ    | Y                 | Υ       | Y                 |

| LCD                                       | Υ          | Υ     | Y            | Y                      | Υ    |                   | -       |                   |

| USB                                       | Y          | Υ     |              |                        |      | Y                 |         |                   |

| USART                                     | Υ          | Υ     | Y            | Y                      | Υ    | (1)               |         |                   |

| SPI                                       | Y          | Υ     | Y            | Υ                      |      |                   |         |                   |

| I2C                                       | Y          | Υ     | Y            | Y                      |      | (1)               |         |                   |

| Table 5. F | unctionalities de | epending on th<br>standby) | • | • | om Run/active | down to |

|------------|-------------------|----------------------------|---|---|---------------|---------|

|            |                   |                            |   |   | Stop          | Stand   |

| lps                                             | Run/Active                            | Sleep                                | Low-<br>power<br>Run | Low-<br>power<br>Sleep | Stop                                          |                                                | Standby                                        |                                                |

|-------------------------------------------------|---------------------------------------|--------------------------------------|----------------------|------------------------|-----------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

|                                                 |                                       |                                      |                      |                        |                                               | Wakeup capability                              |                                                | Wakeup capability                              |

| ADC                                             | Υ                                     | Y                                    |                      |                        |                                               |                                                |                                                |                                                |

| DAC                                             | Y                                     | Y                                    | Y                    | Y                      | Υ                                             |                                                |                                                |                                                |

| Tempsensor                                      | Y                                     | Y                                    | Y                    | Y                      | Υ                                             |                                                |                                                |                                                |

| OP amp                                          | Y                                     | Y                                    | Y                    | Y                      | Υ                                             |                                                |                                                |                                                |

| Comparators                                     | Y                                     | Y                                    | Y                    | Y                      | Υ                                             | Y                                              |                                                |                                                |

| 16-bit and 32-bit<br>Timers                     | Y                                     | Y                                    | Y                    | Y                      |                                               |                                                |                                                |                                                |

| IWDG                                            | Y                                     | Y                                    | Υ                    | Y                      | Υ                                             | Y                                              | Υ                                              | Υ                                              |

| WWDG                                            | Y                                     | Υ                                    | Y                    | Y                      |                                               |                                                |                                                |                                                |

| Touch sensing                                   | Y                                     | Y                                    |                      |                        |                                               |                                                |                                                |                                                |

| Systic Timer                                    | Y                                     | Y                                    | Y                    | Y                      |                                               |                                                |                                                |                                                |

| GPIOs                                           | Y                                     | Y                                    | Y                    | Y                      | Υ                                             | Y                                              |                                                | 3 pins                                         |

| Wakeup time to Run mode                         | 0 μs                                  | 0.4 µs                               | 3 µs                 | 46 µs                  | < 8 µs                                        |                                                | 58 µs                                          |                                                |

| Consumption V <sub>DD</sub> =1.8 to 3.6 V (Typ) | Down to 230<br>μA/MHz (from<br>Flash) | Down to 43<br>μΑ/ΜΗz (from<br>Flash) | Down to<br>11 μA     | Down to<br>4.4 μA      | 0.475 μA<br>(no RTC)<br>V <sub>DD</sub> =1.8V |                                                | 0.305 μA<br>(no RTC)<br>V <sub>DD</sub> =1.8V  |                                                |

|                                                 |                                       |                                      |                      |                        | 1.1 μA<br>(with RTC)<br>V <sub>DD</sub> =1.8V |                                                | 0.82 μA<br>(with RTC)<br>V <sub>DD</sub> =1.8V |                                                |

|                                                 |                                       |                                      |                      |                        | 0.475 μA<br>(no RTC)<br>V <sub>DD</sub> =3.0V |                                                | 0.305 μA<br>(no RTC)<br>V <sub>DD</sub> =3.0V  |                                                |

|                                                 |                                       |                                      |                      |                        | (v                                            | 1.35 µA<br>(with RTC)<br>V <sub>DD</sub> =3.0V |                                                | 1.15 µA<br>(with RTC)<br>V <sub>DD</sub> =3.0V |

The startup on communication line wakes the CPU which was made possible by an EXTI, this induces a delay before entering run mode.

# 3.2 ARM<sup>®</sup> Cortex<sup>®</sup>-M3 core with MPU

The ARM® Cortex®-M3 processor is the industry leading processor for embedded systems. It has been developed to provide a low-cost platform that meets the needs of MCU implementation, with a reduced pin count and low-power consumption, while delivering outstanding computational performance and an advanced system response to interrupts.

The ARM® Cortex®-M3 32-bit RISC processor features exceptional code-efficiency, delivering the high-performance expected from an ARM core in the memory size usually associated with 8- and 16-bit devices.

18/134 DocID026119 Rev 6

The memory protection unit (MPU) improves system reliability by defining the memory attributes (such as read/write access permissions) for different memory regions. It provides up to eight different regions and an optional predefined background region.

Owing to its embedded ARM core, the STM32L151xC/C-A and STM32L152xC/C-A devices are compatible with all ARM tools and software.

#### **Nested vectored interrupt controller (NVIC)**

The ultra-low-power STM32L151xC/C-A and STM32L152xC/C-A devices embed a nested vectored interrupt controller able to handle up to 56 maskable interrupt channels (not including the 16 interrupt lines of ARM® Cortex®-M3) and 16 priority levels.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of *late arriving*, higher-priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.3 Reset and supply management

#### 3.3.1 Power supply schemes

- $V_{DD}$  = 1.65 to 3.6 V: external power supply for I/Os and the internal regulator. Provided externally through  $V_{DD}$  pins.

- $V_{SSA}$ ,  $V_{DDA}$  = 1.65 to 3.6 V: external analog power supplies for ADC, reset blocks, RCs and PLL (minimum voltage to be applied to  $V_{DDA}$  is 1.8 V when the ADC is used).  $V_{DDA}$  and  $V_{SSA}$  must be connected to  $V_{DD}$  and  $V_{SS}$ , respectively.

### 3.3.2 Power supply supervisor

The device has an integrated ZEROPOWER power-on reset (POR)/power-down reset (PDR) that can be coupled with a brownout reset (BOR) circuitry.

The device exists in two versions:

- The version with BOR activated at power-on operates between 1.8 V and 3.6 V.

- The other version without BOR operates between 1.65 V and 3.6 V.

After the  $V_{DD}$  threshold is reached (1.65 V or 1.8 V depending on the BOR which is active or not at power-on), the option byte loading process starts, either to confirm or modify default thresholds, or to disable the BOR permanently: in this case, the  $V_{DD}$  min value becomes 1.65 V (whatever the version, BOR active or not, at power-on).

When BOR is active at power-on, it ensures proper operation starting from 1.8 V whatever the power ramp-up phase before it reaches 1.8 V. When BOR is not active at power-up, the

power ramp-up should guarantee that 1.65 V is reached on  $V_{DD}$  at least 1 ms after it exits the POR area

Five BOR thresholds are available through option bytes, starting from 1.8 V to 3 V. To reduce the power consumption in Stop mode, it is possible to automatically switch off the internal reference voltage ( $V_{REFINT}$ ) in Stop mode. The device remains in reset mode when  $V_{DD}$  is below a specified threshold,  $V_{POR/PDR}$  or  $V_{BOR}$ , without the need for any external reset circuit.

Note:

The start-up time at power-on is typically 3.3 ms when BOR is active at power-up, the start-up time at power-on can be decreased down to 1 ms typically for devices with BOR inactive at power-up.