Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## STM8S005C6 STM8S005K6

# Value line, 16 MHz STM8S 8-bit MCU, 32 Kbytes Flash, data EEPROM, 10-bit ADC, timers, UART, SPI, I<sup>2</sup>C

Datasheet - production data

## **Features**

#### Core

- Max f<sub>CPU</sub>: 16 MHz

- Advanced STM8 core with Harvard architecture and 3-stage pipeline

- · Extended instruction set

#### **Memories**

- Medium-density Flash/EEPROM

- Program memory: 32 Kbytes of Flash memory; data retention 20 years at 55 °C after 100 cycles

- Data memory: 128 bytes true data EEPROM; endurance up to 100 k write/erase cycles

- RAM: 2 Kbytes

#### Clock, reset and supply management

- 2.95 V to 5.5 operating voltage

- Flexible clock control, 4 master clock sources

- Low-power crystal resonator oscillator

- External clock input

- Internal, user-trimmable 16 MHz RC

- Internal low-power 128 kHz RC

- Clock security system with clock monitor

- Power management

- Low-power modes (wait, active-halt, halt)

- Switch-off peripheral clocks individually

- Permanently active, low-consumption power-on and power-down reset

#### Interrupt management

- Nested interrupt controller with 32 interrupts

- Up to 37 external interrupts on 6 vectors

#### **Timers**

- 2x 16-bit general purpose timers, with 2+3 CAPCOM channels (IC, OC or PWM)

- Advanced control timer: 16-bit, 4 CAPCOM channels, 3 complementary outputs, dead-time insertion and flexible synchronization

- 8-bit basic timer with 8-bit prescaler

- Auto wakeup timer

- Window and independent watchdog timers

#### **Communications interfaces**

- UART with clock output for synchronous operation, SmartCard, IrDA, LIN

- SPI interface up to 8 Mbit/s

- I<sup>2</sup>C interface up to 400 Kbit/s

#### Analog to digital converter (ADC)

10-bit ADC, ± 1 LSB ADC with up to 10 multiplexed channels, scan mode and analog watchdog

## I/Os

- Up to 38 I/Os on a 48-pin package including 16 high-sink outputs

- Highly robust I/O design, immune against current injection

### **Development support**

Embedded single-wire interface module (SWIM) for fast on-chip programming and nonintrusive debugging

## **Contents**

| 1 | Introduction |                                                           |      |  |  |  |

|---|--------------|-----------------------------------------------------------|------|--|--|--|

| 2 | Description  |                                                           |      |  |  |  |

| 3 | Bloc         | k diagram                                                 | . 11 |  |  |  |

| 4 | Prod         | uct overview                                              | . 12 |  |  |  |

|   | 4.1          | Central processing unit STM8                              | . 12 |  |  |  |

|   | 4.2          | Single wire interface module (SWIM) and debug module (DM) | . 13 |  |  |  |

|   | 4.3          | Interrupt controller                                      | . 13 |  |  |  |

|   | 4.4          | Flash program and data EEPROM memory                      | . 13 |  |  |  |

|   | 4.5          | Clock controller                                          | . 15 |  |  |  |

|   | 4.6          | Power management                                          | . 16 |  |  |  |

|   | 4.7          | Watchdog timers                                           | . 16 |  |  |  |

|   | 4.8          | Auto wakeup counter                                       | . 17 |  |  |  |

|   | 4.9          | Beeper                                                    | . 17 |  |  |  |

|   | 4.10         | TIM1 - 16-bit advanced control timer                      | . 17 |  |  |  |

|   | 4.11         | TIM2, TIM3 - 16-bit general purpose timers                | . 17 |  |  |  |

|   | 4.12         | TIM4 - 8-bit basic timer                                  | . 18 |  |  |  |

|   | 4.13         | Analog-to-digital converter (ADC1)                        | . 18 |  |  |  |

|   | 4.14         | Communication interfaces                                  | . 18 |  |  |  |

|   |              | 4.14.1 UART2                                              | 19   |  |  |  |

|   |              | 4.14.2 SPI                                                | 20   |  |  |  |

|   |              | 4.14.3 I <sup>2</sup> C                                   | 20   |  |  |  |

| 5 | Pino         | uts and pin descriptions                                  | . 21 |  |  |  |

|   | 5.1          | Alternate function remapping                              | . 25 |  |  |  |

| 6 | Mem          | ory and register map                                      | . 26 |  |  |  |

|   | 6.1          | Memory map                                                | . 26 |  |  |  |

|   | 6.2          | Register map                                              |      |  |  |  |

| 7 | Inter        | rupt vector mapping                                       | . 37 |  |  |  |

| 8  | Optio | on bytes  | s                                                 | 38 |

|----|-------|-----------|---------------------------------------------------|----|

| 9  | Elect | trical ch | naracteristics                                    | 42 |

|    | 9.1   | Parame    | eter conditions                                   | 42 |

|    |       | 9.1.1     | Minimum and maximum values                        | 42 |

|    |       | 9.1.2     | Typical values                                    | 42 |

|    |       | 9.1.3     | Typical curves                                    | 42 |

|    |       | 9.1.4     | Typical current consumption                       | 42 |

|    |       | 9.1.5     | Pin loading conditions                            | 43 |

|    |       | 9.1.6     | Loading capacitor                                 | 43 |

|    |       | 9.1.7     | Pin input voltage                                 | 43 |

|    | 9.2   | Absolu    | te maximum ratings                                | 44 |

|    | 9.3   | Operat    | ing conditions                                    | 46 |

|    |       | 9.3.1     | VCAP external capacitor                           | 48 |

|    |       | 9.3.2     | Supply current characteristics                    | 48 |

|    |       | 9.3.3     | External clock sources and timing characteristics | 58 |

|    |       | 9.3.4     | Internal clock sources and timing characteristics | 60 |

|    |       | 9.3.5     | Memory characteristics                            | 62 |

|    |       | 9.3.6     | I/O port pin characteristics                      | 63 |

|    |       | 9.3.7     | Reset pin characteristics                         | 72 |

|    |       | 9.3.8     | SPI serial peripheral interface                   | 74 |

|    |       | 9.3.9     | I <sup>2</sup> C interface characteristics        | 77 |

|    |       | 9.3.10    | 10-bit ADC characteristics                        | 79 |

|    |       | 9.3.11    | EMC characteristics                               | 82 |

| 10 | Pack  | age info  | ormation                                          | 85 |

|    | 10.1  | LQFP4     | 8 package information                             | 85 |

|    | 10.2  |           | 32 package information                            |    |

|    | 10.3  | Therma    | al characteristics                                | 91 |

|    |       | 10.3.1    | Reference document                                |    |

|    |       | 10.3.2    | Selecting the product temperature range           |    |

| 11 | Part  | number    | ring                                              | 93 |

| 12 | STM   | 8 develo  | opment tools                                      | 94 |

|    | 12.1  | Emulat    | ion and in-circuit debugging tools                | 94 |

| ^-  |     |     |

|-----|-----|-----|

| u.n | nie | nts |

## STM8S005C6 STM8S005K6

| 13 | Revis | ion hist | ory96                       |

|----|-------|----------|-----------------------------|

|    | 12.3  | Progran  | nming tools                 |

|    |       | 12.2.2   | C and assembly toolchains95 |

|    |       | 12.2.1   | STM8 toolset95              |

|    | 12.2  | Software | e tools                     |

|    |       |          |                             |

577

## List of tables

| Table 1.  | STM8S005C6/K6 value line features                                                                   | 10 |

|-----------|-----------------------------------------------------------------------------------------------------|----|

| Table 2.  | Peripheral clock gating bit assignments in CLK_PCKENR1/2 registers                                  | 15 |

| Table 3.  | TIM timer features                                                                                  |    |

| Table 4.  | Legend/abbreviations for STM8S005C6/K6 pin descriptions table                                       | 22 |

| Table 5.  | STM8S005C6 and STM8S005K6 pin descriptions                                                          |    |

| Table 6.  | Flash, Data EEPROM and RAM boundary addresses                                                       |    |

| Table 7.  | I/O port hardware register map                                                                      |    |

| Table 8.  | General hardware register map                                                                       |    |

| Table 9.  | CPU/SWIM/debug module/interrupt controller registers                                                |    |

| Table 10. | Interrupt mapping                                                                                   |    |

| Table 11. | Option bytes                                                                                        |    |

| Table 12. | Option byte description                                                                             |    |

| Table 13. | Description of alternate function remapping bits [7:0] of OPT2                                      |    |

| Table 14. | Voltage characteristics                                                                             |    |

| Table 15. | Current characteristics                                                                             |    |

| Table 16. | Thermal characteristics                                                                             |    |

| Table 17. | General operating conditions                                                                        |    |

| Table 18. | Operating conditions at power-up/power-down                                                         |    |

| Table 19. | Total current consumption with code execution in run mode at $V_{DD} = 5 \text{ V} \dots$           |    |

| Table 20. | Total current consumption with code execution in run mode at $V_{DD} = 3.3 \text{ V} \dots$         | 50 |

| Table 21. | Total current consumption in wait mode at V <sub>DD</sub> = 5 V                                     |    |

| Table 22. | Total current consumption in wait mode at $V_{DD} = 3.3 \text{ V}$                                  |    |

| Table 23. | Total current consumption in active halt mode at V <sub>DD</sub> = 5 V, T <sub>A</sub> -40 to 85° C |    |

| Table 24. | Total current consumption in active halt mode at V <sub>DD</sub> = 3.3 V                            |    |

| Table 25. | Total current consumption in halt mode at V <sub>DD</sub> = 5 V, T <sub>A</sub> -40 to 85° C        | 53 |

| Table 26. | Total current consumption in halt mode at V <sub>DD</sub> = 3.3 V                                   | 53 |

| Table 27. | Wakeup times                                                                                        |    |

| Table 28. | Total current consumption and timing in forced reset state                                          |    |

| Table 29. | Peripheral current consumption                                                                      |    |

| Table 30. | HSE user external clock characteristics                                                             |    |

| Table 31. | HSE oscillator characteristics                                                                      |    |

| Table 32. | HSI oscillator characteristics                                                                      |    |

| Table 33. | LSI oscillator characteristics                                                                      |    |

| Table 34. | RAM and hardware registers                                                                          | 62 |

| Table 35. | Flash program memory/data EEPROM memory                                                             |    |

| Table 36. | I/O static characteristics                                                                          |    |

| Table 37. | Output driving current (standard ports)                                                             | 65 |

| Table 38. | Output driving current (true open drain ports)                                                      | 65 |

| Table 39. | Output driving current (high sink ports)                                                            |    |

| Table 40. | NRST pin characteristics                                                                            |    |

| Table 41. | SPI characteristics                                                                                 |    |

| Table 42. | I <sup>2</sup> C characteristics                                                                    | 77 |

| Table 43. | ADC characteristics                                                                                 |    |

| Table 44. | ADC accuracy with $R_{AIN}$ < 10 k $\Omega$ , $V_{DDA}$ = 5 $V$                                     |    |

| Table 45. | ADC accuracy with $R_{AIN}$ < 10 k $\Omega$ $R_{AIN}$ , $V_{DDA}$ = 3.3 V                           | 80 |

| Table 46. | EMS data                                                                                            |    |

| Table 47. | EMI data                                                                                            |    |

| Table 48. | ESD absolute maximum ratings                                                                        | 83 |

## List of tables

## STM8S005C6 STM8S005K6

| Table 49. | Electrical sensitivities                                                | . 84 |

|-----------|-------------------------------------------------------------------------|------|

| Table 50. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package mechanical data | . 86 |

| Table 51. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package mechanical data | . 89 |

| Table 52. | Thermal characteristics                                                 | . 91 |

| Table 53. | Document revision history                                               | . 96 |

## **List of figures**

| Figure 1.  | STM8S005C6/K6 value line block diagram                                                            | 11 |

|------------|---------------------------------------------------------------------------------------------------|----|

| Figure 2.  | Flash memory organisation                                                                         | 14 |

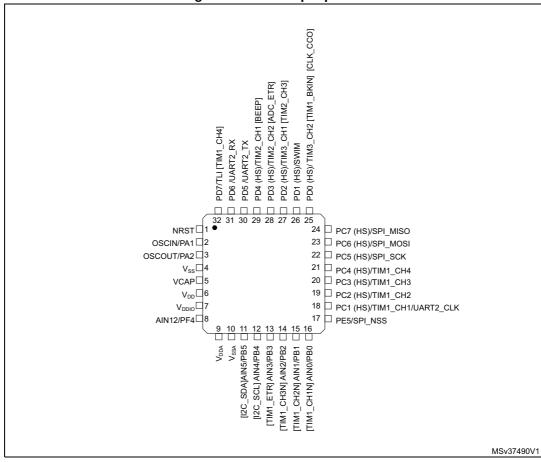

| Figure 3.  | LQFP 48-pin pinout                                                                                | 21 |

| Figure 4.  | LQFP 32-pin pinout                                                                                | 22 |

| Figure 5.  | Memory map                                                                                        | 26 |

| Figure 6.  | Supply current measurement conditions                                                             | 42 |

| Figure 7.  | Pin loading conditions                                                                            | 43 |

| Figure 8.  | Pin input voltage                                                                                 | 43 |

| Figure 9.  | f <sub>CPUmax</sub> versus V <sub>DD</sub>                                                        |    |

| Figure 10. | External capacitor C <sub>EXT</sub>                                                               |    |

| Figure 11. | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSE user external clock, f <sub>CPU</sub> = 16 MHz |    |

| Figure 12. | Typ. I <sub>DD(RUN)</sub> vs V <sub>DD</sub> , HSE user external clock, V <sub>DD</sub> = 5 V     | 55 |

| Figure 13. | Typ. I <sub>DD(WFI)</sub> vs V <sub>DD</sub> , HSE user external clock, f <sub>CPU</sub> = 16 MHz |    |

| Figure 14. | Typ. $I_{DD(WFI)}$ vs $V_{DD}$ , HSE user external clock, $V_{DD} = 5 \text{ V} \dots \dots$      |    |

| Figure 15. | Typ. $I_{DD(RUN)}$ vs $V_{DD}$ , HSI RC osc, $f_{CPU} = 16$ MHz                                   |    |

| Figure 16. | Typ. I <sub>DD(WFI)</sub> vs V <sub>DD</sub> , HSI RC osc, f <sub>CPU</sub> = 16 MHz              |    |

| Figure 17. | HSE external clock source                                                                         |    |

| Figure 18. | HSE oscillator circuit diagram                                                                    |    |

| Figure 19. | Typical HSI frequency variation vs V <sub>DD</sub> at 3 temperatures                              |    |

| Figure 20. | Typical LSI frequency variation vs V <sub>DD</sub> @ 25 °C                                        |    |

| Figure 21. | Typical V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 3 temperatures                   |    |

| Figure 22. | Typical pull-up resistance vs V <sub>DD</sub> @ 3 temperatures                                    |    |

| Figure 23. | Typical pull-up current vs V <sub>DD</sub> @ 3 temperatures                                       |    |

| Figure 24. | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (standard ports)                                                   |    |

| Figure 25. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (standard ports)                                   |    |

| Figure 26. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 5 V (true open drain ports)                              |    |

| Figure 27. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (true open drain ports)                            |    |

| Figure 28. | Typ. $V_{OL}$ @ $V_{DD}$ = 5 V (high sink ports)                                                  |    |

| Figure 29. | Typ. V <sub>OL</sub> @ V <sub>DD</sub> = 3.3 V (high sink ports)                                  |    |

| Figure 30. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 5 V (standard ports)                                        |    |

| Figure 31. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (standard ports)                                      |    |

| Figure 32. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 5 V (high sink ports)                                       |    |

| Figure 33. | Typ. $V_{DD}$ - $V_{OH}$ @ $V_{DD}$ = 3.3 V (high sink ports)                                     |    |

| Figure 34. | Typical NRST V <sub>IL</sub> and V <sub>IH</sub> vs V <sub>DD</sub> @ 3 temperatures              |    |

| Figure 35. | Typical NRST pull-up resistance vs V <sub>DD</sub> @ 3 temperatures                               |    |

| Figure 36. | Typical NRST pull-up current vs V <sub>DD</sub> @ 3 temperatures                                  |    |

| Figure 37. | Recommended reset pin protection                                                                  | 74 |

| Figure 38. | SPI timing diagram - slave mode and CPHA = 0                                                      | 75 |

| Figure 39. | SPI timing diagram - slave mode and CPHA = 1 <sup>(1)</sup>                                       | 75 |

| Figure 40. | SPI timing diagram - master mode <sup>(1)</sup>                                                   | 76 |

| Figure 41. | Typical application with I <sup>2</sup> C bus and timing diagram                                  | 78 |

| Figure 42. | ADC accuracy characteristics                                                                      |    |

| Figure 43. | Typical application with ADC                                                                      |    |

| Figure 44. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat package outline                                   | 85 |

| Figure 45. | LQFP48 - 48-pin, 7 x 7 mm low-profile quad flat recommended footprint                             |    |

| Figure 46. | LQFP48 marking example (package top view)                                                         |    |

| Figure 47. | LQFP32 - 32-pin, 7 x 7 mm low-profile quad flat package outline                                   |    |

| Figure 48. | LQFP32 - 32-pin, 7 x 7 mm low-profile guad flat recommended footprint                             |    |

| List | of | fig | ures |

|------|----|-----|------|

|------|----|-----|------|

## STM8S005C6 STM8S005K6

| Figure 49. | LQFP32 marking example (package top view)                           | 90 |

|------------|---------------------------------------------------------------------|----|

| Figure 50. | STM8S005C6/K6 value line ordering information scheme <sup>(1)</sup> | 93 |

## 1 Introduction

This datasheet contains the description of the STM8S005C6/K6 value line features, pinout, electrical characteristics, mechanical data and ordering information.

- For complete information on the STM8S microcontroller memory, registers and peripherals, please refer to the STM8S and STM8A microcontroller families reference manual (RM0016).

- For information on programming, erasing and protection of the internal Flash memory please refer to the PM0051 (How to program STM8S and STM8A Flash program memory and data EEPROM).

- For information on the debug and SWIM (single wire interface module) refer to the STM8 SWIM communication protocol and debug module user manual (UM0470).

- For information on the STM8 core, please refer to the STM8 CPU programming manual (PM0044).

## 2 Description

The STM8S005C6/K6 value line 8-bit microcontrollers offer 32 Kbytes Flash program memory, plus 128 bytes of data EEPROM. They are referred to as medium-density devices in the STM8S microcontroller family reference manual (RM0016).

All devices of STM8S005C6/K6 value line provide the following benefits: performance, robustness, reduced system cost and short development cycles.

Device performance and robustness are ensured by true data EEPROM supporting up to 100000 write/erase cycles, advanced core and peripherals made in a state-of-the-art technology at 16 MHz clock frequency, robust I/Os, independent watchdogs with separate clock source, and a clock security system.

The system cost is reduced thanks to a high system integration level with internal clock oscillators, watchdog, and brown-out reset.

The common family product architecture with compatible pinout, memory map and modular peripherals allow application scalability and reduced development cycles.

All products operate from a 2.95 V to 5.5 V supply voltage.

Full documentation is offered as well as a wide choice of development tools.

STM8S005C6 **Features** STM8S005K6 Pin count 48 32 25 Max. number of GPIOs (I/O) 38 External interrupt pins 35 23 Timer CAPCOM channels 9 8 Timer complementary outputs 3 3 A/D converter channels 10 7 High-sink I/Os 16 12 High-density Flash program 32 K 32 K memory (bytes) Data EEPROM (bytes) 128 128 2 K 2 K RAM (bytes) Advanced control timer (TIM1), general purpose timers (TIM2 Peripheral set and TIM3), basic timer (TIM4), SPI, I2C, UART, Window WDG, independent WDG, ADC

Table 1. STM8S005C6/K6 value line features

**47**/

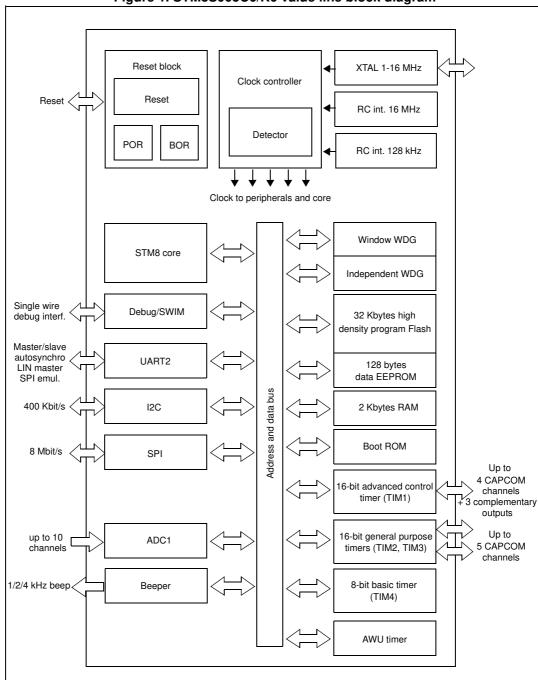

## 3 Block diagram

Figure 1. STM8S005C6/K6 value line block diagram

## 4 Product overview

The following section intends to give an overview of the basic features of the STM8S005C6/K6 value line functional modules and peripherals.

For more detailed information please refer to the corresponding family reference manual (RM0016).

## 4.1 Central processing unit STM8

The 8-bit STM8 core is designed for code efficiency and performance.

It contains six internal registers which are directly addressable in each execution context, 20 addressing modes including indexed indirect and relative addressing and 80 instructions.

## Architecture and registers

- Harvard architecture

- 3-stage pipeline

- 32-bit wide program memory bus single cycle fetching for most instructions

- X and Y 16-bit index registers enabling indexed addressing modes with or without offset and read-modify-write type data manipulations

- 8-bit accumulator

- 24-bit program counter 16-Mbyte linear memory space

- 16-bit stack pointer access to a 64 K-level stack

- 8-bit condition code register 7 condition flags for the result of the last instruction

## Addressing

- 20 addressing modes

- Indexed indirect addressing mode for look-up tables located anywhere in the address space

- Stack pointer relative addressing mode for local variables and parameter passing

### Instruction set

- 80 instructions with 2-byte average instruction size

- Standard data movement and logic/arithmetic functions

- 8-bit by 8-bit multiplication

- 16-bit by 8-bit and 16-bit by 16-bit division

- Bit manipulation

- Data transfer between stack and accumulator (push/pop) with direct stack access

- Data transfer using the X and Y registers or direct memory-to-memory transfers

57

## 4.2 Single wire interface module (SWIM) and debug module (DM)

The single wire interface module and debug module permits non-intrusive, real-time incircuit debugging and fast memory programming.

#### **SWIM**

Single wire interface module for direct access to the debug module and memory programming. The interface can be activated in all device operation modes. The maximum data transmission speed is 145 bytes/ms.

#### **Debug module**

The non-intrusive debugging module features a performance close to a full-featured emulator. Beside memory and peripherals, also CPU operation can be monitored in real-time by means of shadow registers.

- R/W to RAM and peripheral registers in real-time

- R/W access to all resources by stalling the CPU

- Breakpoints on all program-memory instructions (software breakpoints)

- Two advanced breakpoints, 23 predefined configurations

## 4.3 Interrupt controller

- Nested interrupts with three software priority levels

- 32 interrupt vectors with hardware priority

- Up to 33 external interrupts on six vectors including TLI

- Trap and reset interrupts

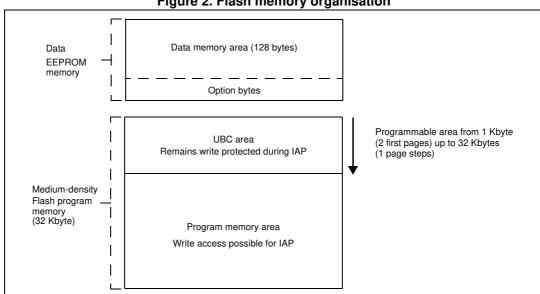

## 4.4 Flash program and data EEPROM memory

- 32 Kbytes of high density Flash program single voltage Flash memory

- 128 bytes true data EEPROM

- Read while write: Writing in data memory possible while executing code in program memory.

- User option byte area

## Write protection (WP)

Write protection of Flash program memory and data EEPROM is provided to avoid unintentional overwriting of memory that could result from a user software malfunction.

There are two levels of write protection. The first level is known as MASS (memory access security system). MASS is always enabled and protects the main Flash program memory, data EEPROM and option bytes.

To perform in-application programming (IAP), this write protection can be removed by writing a MASS key sequence in a control register. This allows the application to write to data EEPROM, modify the contents of main program memory or the device option bytes.

A second level of write protection, can be enabled to further protect a specific area of memory known as UBC (user boot code). Refer to *Figure 2*.

14/97

The size of the UBC is programmable through the UBC option byte (Table 12), in increments of 1 page (512 bytes) by programming the UBC option byte in ICP mode.

This divides the program memory into two areas:

- Main program memory: 32 Kbytes minus UBC

- User-specific boot code (UBC): Configurable up to 32 Kbytes

The UBC area remains write-protected during in-application programming. This means that the MASS keys do not unlock the UBC area. It protects the memory used to store the boot program, specific code libraries, reset and interrupt vectors, the reset routine and usually the IAP and communication routines.

Figure 2. Flash memory organisation

## Read-out protection (ROP)

The read-out protection blocks reading and writing the Flash program memory and data EEPROM memory in ICP mode (and debug mode). Once the read-out protection is activated, any attempt to toggle its status triggers a global erase of the program and data memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

DocID022186 Rev 4

## 4.5 Clock controller

The clock controller distributes the system clock (f<sub>MASTER)</sub> coming from different oscillators to the core and the peripherals. It also manages clock gating for low power modes and ensures clock robustness.

#### **Features**

- **Clock prescaler:** To get the best compromise between speed and current consumption the clock frequency to the CPU and peripherals can be adjusted by a programmable prescaler.

- **Safe clock switching:** Clock sources can be changed safely on the fly in run mode through a configuration register. The clock signal is not switched until the new clock source is ready. The design guarantees glitch-free switching.

- **Clock management:** To reduce power consumption, the clock controller can stop the clock to the core, individual peripherals or memory.

- Master clock sources: Four different clock sources can be used to drive the master clock:

- 1-16 MHz high-speed external crystal (HSE)

- Up to 16 MHz high-speed user-external clock (HSE user-ext)

- 16 MHz high-speed internal RC oscillator (HSI)

- 128 kHz low-speed internal RC (LSI)

- **Startup clock:** After reset, the microcontroller restarts by default with an internal 2 MHz clock (HSI/8). The prescaler ratio and clock source can be changed by the application program as soon as the code execution starts.

- Clock security system (CSS): This feature can be enabled by software. If an HSE clock failure occurs, the internal RC (16 MHz/8) is automatically selected by the CSS and an interrupt can optionally be generated.

- Configurable main clock output (CCO): This outputs an external clock for use by the application.

Table 2. Peripheral clock gating bit assignments in CLK PCKENR1/2 registers

| Bit     | Peripheral clock |

|---------|------------------|---------|------------------|---------|------------------|---------|------------------|

| PCKEN17 | TIM1             | PCKEN13 | UART2            | PCKEN27 | Reserved         | PCKEN23 | ADC              |

| PCKEN16 | TIM3             | PCKEN12 | Reserved         | PCKEN26 | Reserved         | PCKEN22 | AWU              |

| PCKEN15 | TIM2             | PCKEN11 | SPI              | PCKEN25 | Reserved         | PCKEN21 | Reserved         |

| PCKEN14 | TIM4             | PCKEN10 | I <sup>2</sup> C | PCKEN24 | Reserved         | PCKEN20 | Reserved         |

#### 4.6 Power management

For efficent power management, the application can be put in one of four different lowpower modes. You can configure each mode to obtain the best compromise between lowest power consumption, fastest start-up time and available wakeup sources.

- Wait mode: In this mode, the CPU is stopped, but peripherals are kept running. The wakeup is performed by an internal or external interrupt or reset.

- Active halt mode with regulator on: In this mode, the CPU and peripheral clocks are stopped. An internal wakeup is generated at programmable intervals by the auto wake up unit (AWU). The main voltage regulator is kept powered on, so current consumption is higher than in active halt mode with regulator off, but the wakeup time is faster. Wakeup is triggered by the internal AWU interrupt, external interrupt or reset.

- Active halt mode with regulator off: This mode is the same as active halt with regulator on, except that the main voltage regulator is powered off, so the wake up time is slower.

- Halt mode: In this mode the microcontroller uses the least power. The CPU and peripheral clocks are stopped, the main voltage regulator is powered off. Wakeup is triggered by external event or reset.

#### 4.7 Watchdog timers

The watchdog system is based on two independent timers providing maximum security to the applications.

Activation of the watchdog timers is controlled by option bytes or by software. Once activated, the watchdogs cannot be disabled by the user program without performing a reset.

### Window watchdog timer

The window watchdog is used to detect the occurrence of a software fault, usually generated by external interferences or by unexpected logical conditions, which cause the application program to abandon its normal sequence.

The window function can be used to trim the watchdog behavior to match the application perfectly.

The application software must refresh the counter before time-out and during a limited time window.

A reset is generated in two situations:

- Timeout: at 16 MHz CPU clock the time-out period can be adjusted between 75 μs up

- 2. Refresh out of window: The downcounter is refreshed before its value is lower than the one stored in the window register.

DocID022186 Rev 4 16/97

## Independent watchdog timer

The independent watchdog peripheral can be used to resolve processor malfunctions due to hardware or software failures.

It is clocked by the 128 kHz LSI internal RC clock source, and thus stays active even in case of a CPU clock failure

The IWDG time base spans from 60 µs to 1 s.

## 4.8 Auto wakeup counter

- Used for auto wakeup from active halt mode

- Clock source: Internal 128 kHz internal low frequency RC oscillator or external clock

- LSI clock can be internally connected to TIM3 input capture channel 1 for calibration

## 4.9 Beeper

The beeper function outputs a signal on the BEEP pin for sound generation. The signal is in the range of 1, 2 or 4 kHz.

The beeper output port is only available through the alternate function remap option bit AFR7.

## 4.10 TIM1 - 16-bit advanced control timer

This is a high-end timer designed for a wide range of control applications. With its complementary outputs, dead-time control and center-aligned PWM capability, the field of applications is extended to motor control, lighting and half-bridge driver

- 16-bit up, down and up/down autoreload counter with 16-bit prescaler

- Four independent capture/compare channels (CAPCOM) configurable as input capture, output compare, PWM generation (edge and center aligned mode) and single pulse mode output

- · Synchronization module to control the timer with external signals

- Break input to force the timer outputs into a defined state

- Three complementary outputs with adjustable dead time

- Encoder mode

- Interrupt sources: 3 x input capture/output compare, 1 x overflow/update, 1 x break

## 4.11 TIM2, TIM3 - 16-bit general purpose timers

- 16-bit autoreload (AR) up-counter

- 15-bit prescaler adjustable to fixed power of 2 ratios 1...32768

- Timers with 3 or 2 individually configurable capture/compare channels

- PWM mode

- Interrupt sources: 2 or 3 x input capture/output compare, 1 x overflow/update

## 4.12 TIM4 - 8-bit basic timer

• 8-bit autoreload, adjustable prescaler ratio to any power of 2 from 1 to 128

Clock source: CPU clock

Interrupt source: 1 x overflow/update

Table 3. TIM timer features

| Timer | Counter<br>size<br>(bits) | Prescaler                      | Counting mode | CAPCOM channels | Complem. outputs | Ext.<br>trigger | Timer<br>synchr-<br>onization/<br>chaining |

|-------|---------------------------|--------------------------------|---------------|-----------------|------------------|-----------------|--------------------------------------------|

| TIM1  | 16                        | Any integer from 1 to 65536    | Up/down       | 4               | 3                | Yes             |                                            |

| TIM2  | 16                        | Any power of 2 from 1 to 32768 | Up            | 3               | 0                | No              | No                                         |

| TIM3  | 16                        | Any power of 2 from 1 to 32768 | Up            | 2               | 0                | No              | INU                                        |

| TIM4  | 8                         | Any power of 2 from 1 to 128   | Up            | 0               | 0                | No              |                                            |

## 4.13 Analog-to-digital converter (ADC1)

STM8S005C6/K6 value line products contain a 10-bit successive approximation A/D converter (ADC1) with up to 10 multiplexed input channels and the following main features:

- Input voltage range: 0 to V<sub>DDA</sub>

- Conversion time: 14 clock cycles

- Single and continuous, buffered continuous conversion modes

- Buffer size (10 x 10 bits)

- Scan mode for single and continuous conversion of a sequence of channels

- Analog watchdog capability with programmable upper and lower thresholds

- Analog watchdog interrupt

- External trigger input

- Trigger from TIM1 TRGO

- End of conversion (EOC) interrupt

Note:

Additional AIN12 analog input is not selectable in ADC scan mode or with analog watchdog. Values converted from AIN12 are stored only into the ADC\_DRH/ADC\_DRL registers.

## 4.14 Communication interfaces

The following communication interfaces are implemented:

- UART2: full feature UART, synchronous mode, SPI master mode, SmartCard mode, IrDA mode, IIN2.1 master/slave capability

- SPI: full and half-duplex, 8 Mbit/s

- I<sup>2</sup>C: up to 400 Kbit/s

#### 4.14.1 UART2

#### **Main features**

- 1 Mbit/s full duplex SCI

- SPI emulation

- High precision baud rate generator

- Smartcard emulation

- IrDA SIR encoder decoder

- LIN master mode

- Single wire half duplex mode

## Asynchronous communication (UART mode)

- Full duplex communication NRZ standard format (mark/space)

- Programmable transmit and receive baud rates up to 1 Mbit/s (f<sub>CPU</sub>/16) and capable of following any standard baud rate regardless of the input frequency

- Separate enable bits for transmitter and receiver

- Two receiver wakeup modes:

- Address bit (MSB)

- Idle line (interrupt)

- Transmission error detection with interrupt generation

- Parity control

## Synchronous communication

- Full duplex synchronous transfers

- SPI master operation

- 8-bit data communication

- Maximum speed: 1 Mbit/s at 16 MHz (f<sub>CPU</sub>/16)

#### LIN master mode

- Emission: generates 13-bit synch. break frame

- Reception: detects 11-bit break frame

#### LIN slave mode

- Autonomous header handling one-single interrupt per valid message header

- Automatic baud rate synchronization maximum tolerated initial clock deviation ± 15%

- Synch. delimiter checking

- 11-bit LIN synch. break detection break detection always active

- Parity check on the LIN identifier field

- LIN error management

- Hot plugging support

## 4.14.2 SPI

- Maximum speed: 8 Mbit/s (f<sub>MASTER</sub>/2) both for master and slave

- Full duplex synchronous transfers

- Simplex synchronous transfers on two lines with a possible bidirectional data line

- Master or slave operation selectable by hardware or software

- CRC calculation

- 1 byte Tx and Rx buffer

- Slave/master selection input pin

## 4.14.3 $I^2C$

- I2C master features

- Clock generation

- Start and stop generation

- I<sup>2</sup>C slave features

- Programmable I<sup>2</sup>C address detection

- Stop bit detection

- Generation and detection of 7-bit/10-bit addressing and general call

- Supports different communication speeds

- Standard speed (up to 100 kHz)

- Fast speed (up to 400 kHz)

## 5 Pinouts and pin descriptions

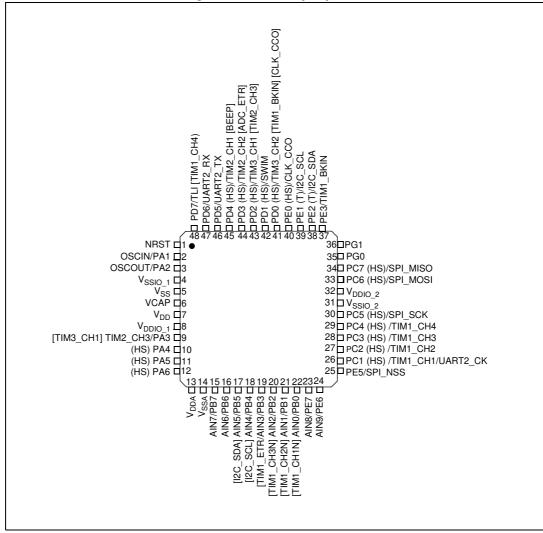

Figure 3. LQFP 48-pin pinout

- 1. (HS) high sink capability.

- 2. (T) True open drain (P-buffer and protection diode to  $V_{DD}$  not implemented).

- 3. [] alternate function remapping option (If the same alternate function is shown twice, it indicates an exclusive choice not a duplication of the function).

Figure 4. LQFP 32-pin pinout

Table 4. Legend/abbreviations for STM8S005C6/K6 pin descriptions table

| Туре             | I = input, O = output, S = power supply                                                                                                                                                      |                                                      |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--|--|

| Level            | Input                                                                                                                                                                                        | CM = CMOS                                            |  |  |

| Level            | Output                                                                                                                                                                                       | HS = high sink                                       |  |  |

| Output speed     | O1 = slow (up to 2 MHz) O2 = fast (up to 10 MHz) O3 = fast/slow programmability with slow as default state after reset O4 = fast/slow programmability with fast as default state after reset |                                                      |  |  |

| Port and control | Input                                                                                                                                                                                        | float = floating, wpu = weak pull-up                 |  |  |

| configuration    | Output                                                                                                                                                                                       | T = true open drain, OD = open drain, PP = push pull |  |  |

| Reset state      | Bold <u>x</u> (pin state after internal reset release) Unless otherwise specified, the pin state is the same during the reset phase and after the internal reset release.                    |                                                      |  |  |

Table 5. STM8S005C6 and STM8S005K6 pin descriptions

| Pin nu | ımber  |                                    |      | Input    |          |                |           | Out   | put |    | _                              |                                   |                                                      |

|--------|--------|------------------------------------|------|----------|----------|----------------|-----------|-------|-----|----|--------------------------------|-----------------------------------|------------------------------------------------------|

| LQFP48 | LQFP32 | Pin name                           | Туре | floating | ndw      | Ext. interrupt | High sink | Speed | ОО  | dd | Main function<br>(after reset) | Default<br>alternate<br>function  | Alternate<br>function<br>after remap<br>[option bit] |

| 1      | 1      | NRST                               | I/O  |          | <u>X</u> |                |           |       |     |    | Reset                          |                                   |                                                      |

| 2      | 2      | PA1/OSCIN                          | I/O  | <u>X</u> | Х        |                |           | O1    | Х   | Х  | Port A1                        | Resonator/<br>crystal in          |                                                      |

| 3      | 3      | PA2/OSCOUT                         | I/O  | <u>x</u> | Х        | Χ              |           | 01    | X   | Х  | Port A2                        | Resonator/<br>crystal out         |                                                      |

| 4      | -      | V <sub>SSIO_1</sub>                | S    |          |          |                |           |       |     |    | I/O ground                     |                                   |                                                      |

| 5      | 4      | $V_{SS}$                           | S    |          |          |                |           |       |     |    | Digital gro                    | ound                              |                                                      |

| 6      | 5      | VCAP                               | S    |          |          |                |           |       |     |    | 1.8 V reg                      | ulator capacitor                  |                                                      |

| 7      | 6      | $V_{DD}$                           | S    |          |          |                |           |       |     |    | Digital po                     | wer supply                        |                                                      |

| 8      | 7      | V <sub>DDIO_1</sub>                | S    |          |          |                |           |       |     |    | I/O power supply               |                                   |                                                      |

| 9      | -      | PA3/TIM2_CH3                       | I/O  | <u>X</u> | Х        | Χ              |           | 01    | Χ   | Х  | Port A3                        | Timer 2 -<br>channel3             | TIM3_CH1<br>[AFR1]                                   |

| 10     | -      | PA4                                | I/O  | <u>X</u> | Х        | Х              | HS        | О3    | Χ   | Χ  | Port A4                        |                                   |                                                      |

| 11     | -      | PA5                                | I/O  | <u>X</u> | Χ        | Χ              | HS        | О3    | Х   | Χ  | Port A5                        |                                   |                                                      |

| 12     | -      | PA6                                | I/O  | <u>X</u> | X        | Χ              | HS        | О3    | X   | Χ  | Port A6                        |                                   |                                                      |

| -      | 8      | PF4/AIN12 <sup>(1)</sup>           | I/O  | <u>X</u> | X        |                |           | 01    | X   | X  | Port F4                        | Analog input<br>12 <sup>(2)</sup> |                                                      |

| 13     | 9      | $V_{DDA}$                          | S    |          |          |                |           |       |     |    | Analog power supply            |                                   |                                                      |

| 14     | 10     | V <sub>SSA</sub>                   | S    |          |          |                |           |       |     |    | Analog ground                  |                                   |                                                      |

| 15     | -      | PB7/AIN7                           | I/O  | <u>X</u> | X        | Χ              |           | 01    | Χ   | Х  | Port B7                        | Analog<br>input 7                 |                                                      |

| 16     | -      | PB6/AIN6                           | I/O  | <u>X</u> | Х        | Х              |           | 01    | X   | Х  | Port B6                        | Analog<br>input 6                 |                                                      |

| 17     | 11     | PB5/AIN5<br>[I <sup>2</sup> C_SDA] | I/O  | <u>X</u> | X        | Х              |           | 01    | X   | Х  | Port B5                        | Analog<br>input 5                 | I <sup>2</sup> C_SDA<br>[AFR6]                       |

| 18     | 12     | PB4/AIN4<br>[I <sup>2</sup> C_SCL] | I/O  | <u>X</u> | X        | X              |           | 01    | X   | X  | Port B4                        | Analog<br>input 4                 | I <sup>2</sup> C_SCL<br>[AFR6]                       |

| 19     | 13     | PB3/AIN3<br>[TIM1_ETR]             | I/O  | <u>X</u> | Х        | X              |           | 01    | X   | X  | Port B3                        | Analog<br>input 3                 | TIM1_ETR<br>[AFR5]                                   |

| 20     | 14     | PB2/AIN2<br>[TIM1_CH3N]            | I/O  | <u>X</u> | Х        | X              |           | 01    | Х   | Х  | Port B2                        | Analog<br>input 2                 | TIM1_<br>CH3N<br>[AFR5]                              |

| 21     | 15     | PB1/AIN1<br>[TIM1_CH2N]            | I/O  | <u>x</u> | X        | X              |           | O1    | X   | Х  | Port B1                        | Analog<br>input 1                 | TIM1_<br>CH2N<br>[AFR5]                              |

Table 5. STM8S005C6 and STM8S005K6 pin descriptions (continued)

| Pin number |        |                           |      |          | Inpu | t              |           | Out   | put              |    | _                              |                                                         |                                                      |

|------------|--------|---------------------------|------|----------|------|----------------|-----------|-------|------------------|----|--------------------------------|---------------------------------------------------------|------------------------------------------------------|

| LQFP48     | LQFP32 | Pin name                  | Туре | floating | ndw  | Ext. interrupt | High sink | Speed | ОО               | dd | Main function<br>(after reset) | Default<br>alternate<br>function                        | Alternate<br>function<br>after remap<br>[option bit] |

| 22         | 16     | PB0/AIN0 [TIM1_<br>CH1N]  | I/O  | <u>x</u> | Х    | Х              |           | O1    | х                | Х  | Port B0                        | Analog<br>input 0                                       | TIM1_<br>CH1N<br>[AFR5]                              |

| 23         | -      | PE7/AIN8                  | I/O  | <u>X</u> | Χ    | Х              |           | 01    | Х                | Χ  | Port E7                        | Analog input 8                                          |                                                      |

| 24         | -      | PE6/AIN9                  | I/O  | <u>X</u> | Χ    | Х              |           | 01    | Х                | Χ  | Port E6                        | Analog input 9                                          |                                                      |

| 25         | 17     | PE5/SPI_NSS               | I/O  | <u>x</u> | X    | X              |           | O1    | Х                | Χ  | Port E5                        | SPI<br>master/slave<br>select                           |                                                      |

| 26         | 18     | PC1/TIM1_CH1/<br>UART2_CK | I/O  | <u>x</u> | Х    | х              | HS        | О3    | x                | X  | Port C1                        | Timer 1 -<br>channel<br>1/UART2<br>synchronous<br>clock |                                                      |

| 27         | 19     | PC2/TIM1_CH2              | I/O  | <u>X</u> | X    | Х              | HS        | О3    | Х                | Х  | Port C2                        | Timer 1-<br>channel 2                                   |                                                      |

| 28         | 20     | PC3/TIM1_CH3              | I/O  | <u>x</u> | Х    | Х              | HS        | О3    | Х                | Х  | Port C3                        | Timer 1 -<br>channel 3                                  |                                                      |

| 29         | 21     | PC4/TIM1_CH4              | I/O  | <u>x</u> | Х    | Х              | HS        | О3    | Х                | Х  | Port C4                        | Timer 1 -<br>channel 4                                  |                                                      |

| 30         | 22     | PC5/SPI_SCK               | I/O  | <u>X</u> | Х    | Х              | HS        | О3    | Х                | Χ  | Port C5                        | SPI clock                                               |                                                      |

| 31         | -      | V <sub>SSIO_2</sub>       | S    |          |      |                |           |       |                  |    | I/O groun                      | d                                                       |                                                      |

| 32         | -      | V <sub>DDIO_2</sub>       | S    |          |      |                |           |       |                  |    | I/O power supply               |                                                         |                                                      |

| 33         | 23     | PC6/SPI_MOSI              | I/O  | <u>X</u> | X    | X              | HS        | О3    | X                | X  | Port C6                        | SPI master<br>out/slave in                              |                                                      |

| 34         | 24     | PC7/SPI_MISO              | I/O  | <u>X</u> | Χ    | Χ              | HS        | О3    | Χ                | Х  | Port C7                        | SPI master in/<br>slave out                             |                                                      |

| 35         | -      | PG0                       | I/O  | <u>X</u> | Х    |                |           | O1    | Х                | Χ  | Port G0                        |                                                         |                                                      |

| 36         | -      | PG1                       | I/O  | <u>X</u> | Χ    |                |           | 01    | Χ                | Χ  | Port G1                        |                                                         |                                                      |

| 37         | ı      | PE3/TIM1_BKIN             | I/O  | <u>X</u> | X    | Χ              |           | 01    | X                | Χ  | Port E3                        | Timer 1 -<br>break input                                |                                                      |

| 38         | -      | PE2/I <sup>2</sup> C_SDA  | I/O  | <u>X</u> |      | Х              |           | 01    | T <sup>(3)</sup> |    | Port E2                        | I <sup>2</sup> C data                                   |                                                      |

| 39         | -      | PE1/I <sup>2</sup> C_SCL  | I/O  | <u>X</u> |      | Х              |           | 01    | T <sup>(3)</sup> |    | Port E1                        | I <sup>2</sup> C clock                                  |                                                      |

| 40         | -      | PE0/CLK_CCO               | I/O  | <u>x</u> | Х    | Х              | HS        | О3    | Х                | Х  | Port E0                        | Configurable clock output                               |                                                      |

| Pin number |        |                                          |      | Input    |          |                | Output    |       |    |    | _                              |                                  |                                                      |

|------------|--------|------------------------------------------|------|----------|----------|----------------|-----------|-------|----|----|--------------------------------|----------------------------------|------------------------------------------------------|

| LQFP48     | LQFP32 | Pin name                                 | Туре | floating | ndw      | Ext. interrupt | High sink | Speed | ао | dd | Main function<br>(after reset) | Default<br>alternate<br>function | Alternate<br>function<br>after remap<br>[option bit] |

| 41         | 25     | PD0/TIM3_CH2<br>[TIM1_BKIN]<br>[CLK_CCO] | I/O  | <u>x</u> | Х        | Х              | HS        | О3    | Х  | х  | Port D0                        | Timer 3 -<br>channel 2           | TIM1_BKIN<br>[AFR3]/<br>CLK_CCO<br>[AFR2]            |

| 42         | 26     | PD1/SWIM <sup>(4)</sup>                  | I/O  | Х        | <u>x</u> | Х              | HS        | 04    | Х  | Х  | Port D1                        | SWIM data interface              |                                                      |

| 43         | 27     | PD2/TIM3_CH1<br>[TIM2_CH3]               | I/O  | <u>x</u> | Х        | Х              | HS        | О3    | Х  | Х  | Port D2                        | Timer 3 -<br>channel 1           | TIM2_CH3<br>[AFR1]                                   |

| 44         | 28     | PD3/TIM2_CH2<br>[ADC_ETR]                | I/O  | <u>x</u> | Х        | Х              | HS        | О3    | Х  | х  | Port D3                        | Timer 2 -<br>channel 2           | ADC_ETR<br>[AFR0]                                    |

| 45         | 29     | PD4/TIM2_CH1<br>[BEEP]                   | I/O  | <u>x</u> | Х        | Х              | HS        | О3    | Х  | Х  | Port D4                        | Timer 2 -<br>channel 1           | BEEP output<br>[AFR7]                                |

| 46         | 30     | PD5/ UART2_TX                            | I/O  | <u>x</u> | Х        | X              |           | 01    | Х  | Х  | Port D5                        | UART2 data<br>transmit           |                                                      |

| 47         | 31     | PD6/ UART2_RX                            | I/O  | <u>x</u> | Х        | Х              |           | 01    | Х  | х  | Port D6                        | UART2 data receive               |                                                      |

| 48         | 32     | PD7/TLI<br>[TIM1_CH4]                    | I/O  | <u>X</u> | Х        | Х              |           | O1    | Х  | Х  | Port D7                        | Top level interrupt              | TIM1_CH4<br>[AFR4]                                   |

Table 5. STM8S005C6 and STM8S005K6 pin descriptions (continued)

## 5.1 Alternate function remapping

As shown in the rightmost column of the pin description table, some alternate functions can be remapped at different I/O ports by programming one of eight AFR (alternate function remap) option bits. Refer to *Section 8: Option bytes*. When the remapping option is active, the default alternate function is no longer available.

To use an alternate function, the corresponding peripheral must be enabled in the peripheral registers.

Alternate function remapping does not effect GPIO capabilities of the I/O ports (see the GPIO section of the family reference manual, RM0016).

<sup>1.</sup> A pull-up is applied to PF4 during the reset phase. This pin is input floating after reset release.

<sup>2.</sup> AIN12 is not selectable in ADC scan mode or with analog watchdog.

In the open-drain output column, 'T' defines a true open-drain I/O (P-buffer, weak pull-up, and protection diode to V<sub>DD</sub> are not implemented).

<sup>4.</sup> The PD1 pin is in input pull-up during the reset phase and after the internal reset release.