# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STNRGPF01

# Three-channel interleaved CCM PFC digital controller

# Features

- Interleaved boost PFC

- Up to 3 interleaved channels

- CCM, fixed frequency

- Average current control, cycle-by-cycle

- Inrush current control

- Burst mode support

- Overcurrent and thermal protection

- Soft start-up

- Flexible phase-shedding strategy

- High operating frequency with small PFC inductor, suitable for high power-density applications

- Low ripple current (input/output)

- Simpler integration with other applications

#### Datasheet - production data

- Flexible design customization to meet specific customer needs

- Firmware

- Turnkey solution for quick design

- eDesign Suite graphical user interface (GUI) for application configuration

- Embedded memory data retention 15 years with ECC

- Communication interfaces

- UART asynchronous protocol for bootloader support

- Operating temperature: -40 °C to 105 °C

# **Applications**

• Suitable for welding, industrial motors, UPS, battery chargers, power supplies, air conditioners

#### Table 1. Device summary

| Order code  | Packing       |  |  |

|-------------|---------------|--|--|

| STNRGPF01   | Tube          |  |  |

| STNRGPF01TR | Tape and reel |  |  |

This is information on a product in full production.

# Contents

| 1 | Desc  | ription . |                                |

|---|-------|-----------|--------------------------------|

| 2 | STNF  | RGPF01    | control architecture           |

| 3 | STNF  | RGPF01    | block diagram                  |

|   | 3.1   | Voltage   | and current loop               |

|   | 3.2   | Measur    | ements section                 |

|   | 3.3   | Analog    | input section                  |

|   | 3.4   | Driving   | and interleaving               |

|   | 3.5   | Program   | nming section                  |

|   | 3.6   | Status i  | ndicator                       |

|   | 3.7   | Start-up  | o function                     |

|   |       | 3.7.1     | Inrush current limiter         |

|   |       | 3.7.2     | PFC soft power-on              |

|   | 3.8   | Fan cor   | ntrol                          |

| 4 | Pinou | ut and p  | in description                 |

|   | 4.1   | Pinout    |                                |

|   | 4.2   | Pin des   | cription                       |

| 5 | Elect | rical ch  | aracteristics                  |

|   | 5.1   | Parame    | eter conditions                |

|   |       | 5.1.1     | Minimum and maximum values     |

|   |       | 5.1.2     | Typical values                 |

|   |       | 5.1.3     | Typical curves                 |

|   |       | 5.1.4     | Typical current consumption    |

|   |       | 5.1.5     | Loading capacitors             |

|   |       | 5.1.6     | Pin output voltage             |

|   | 5.2   | Absolut   | e maximum ratings 24           |

|   | 5.3   | Operati   | ng conditions                  |

|   |       | 5.3.1     | VCOUT external capacitor       |

|   |       | 5.3.2     | Supply current characteristics |

|   |       | 5.3.3     | Memory characteristics         |

DocID030377 Rev 2

|    |       | 5.3.4    | Input/output specifications   | 27 |

|----|-------|----------|-------------------------------|----|

|    |       | 5.3.5    | I/O port pin characteristics  | 28 |

|    |       | 5.3.6    | Typical output level curves   | 29 |

|    |       | 5.3.7    | Reset pin characteristics     | 32 |

|    | 5.4   | Analog i | nput characteristics          | 32 |

|    |       | 5.4.1    | Measurement section           | 32 |

|    |       | 5.4.2    | Analog section                | 33 |

|    | 5.5   | EMC cha  | aracteristics                 | 33 |

|    |       | 5.5.1    | Electrostatic discharge (ESD) | 33 |

|    |       | 5.5.2    | Static latch-up               | 34 |

| 6  | Therm | nal data |                               | 35 |

| 7  | Packa | ige info | rmation                       | 36 |

|    | 7.1   | TSSOP    | 88 package information        | 36 |

| 8  | STNR  | GPF01    | development tools3            | 38 |

| 9  | Order | ing info | rmation                       | 39 |

| 10 | Revis | ion hist | ory                           | 39 |

# 1 Description

The STNRGPF01 is a digital controller designed specifically for interleaved PFC boost topologies and intended for use in high power applications.

The controller is capable of driving up to 3 interleaved channels, generating the proper signals in each condition. Moreover, it implements a flexible phase shedding strategy that enables the correct number of PFC channels based on the actual load condition. With this function, the STNRGPF01 is always able to guarantee the highest power efficiency across a wide range of load current requirements.

The device works in CCM at fixed frequency with average current mode control, and implements mixed signal (analog/digital) control. The inner current loop is performed by hardware, ensuring cycle-by-cycle regulation. The outer voltage loop is performed by a digital PI controller with fast dynamic response.

The controller implements several functions: inrush current control, soft start-up, burst mode cooling management and status indicators.

It also features a full set of embedded protections against overvoltage, overcurrent, and thermal faults.

The STNRGPF01 is configured through a visual dedicated software tool (eDesignSuite) to match a wide range of specific applications. Using eDesignSuite, the user can customize the PFC conversion configuration and all the relevant electrical components. As a result, the tool will automatically generate a full schematic which includes a complete list of material and the final binary object code (FW) to be downloaded to the STNRGPF01.

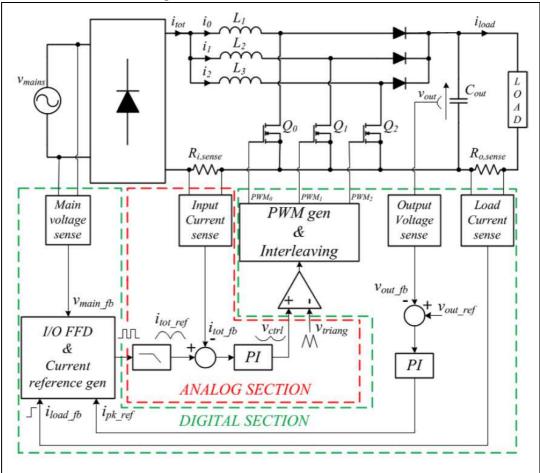

# 2 STNRGPF01 control architecture

The STNRGPF01 implements mixed signal (analog/digital) control. The inner current loop is performed by hardware and the outer voltage loop is performed by a digital PI controller.

The device performs cascaded control for voltage and current loops to regulate the output voltage by acting on the total average inductor current.

*Figure 1* shows the STNRGPF01 control scheme. As can be observed, the difference between the output voltage feedback  $V_{out\_fb}$  and reference  $V_{out\_ref}$  is sent to a digital PI controller, which calculates the peak of the input average total current  $i_{pk\_ref}$ . (internal digital section, green line).

The PFC current reference is internally generated and is output from the I/O FFD block as the PWM signal. After filtering it becomes the total average sinusoidal input current reference  $i_{tot\_ref}$  for the inner current loop (external analog section, red line). The difference between the current reference  $i_{tot\_ref}$  and the input current feedback  $i_{tot\_fb}$  is sent to the analog PI controller.

Thus the master PWM signal is generated by comparing the analog PI output V<sub>ctrl</sub> and a triangular wave V<sub>triang</sub> at switching frequency. Finally, an interleaving operation is performed and three 120° phase-shifted PWM signals (180° for two channels only) drive the three power switches.

Moreover, the digital section includes the input voltage and load feed-forward for fast transient response when the main voltage changes suddenly or a load step current occurs, preventing large over or undervoltage on the output capacitor  $C_{out}$ .

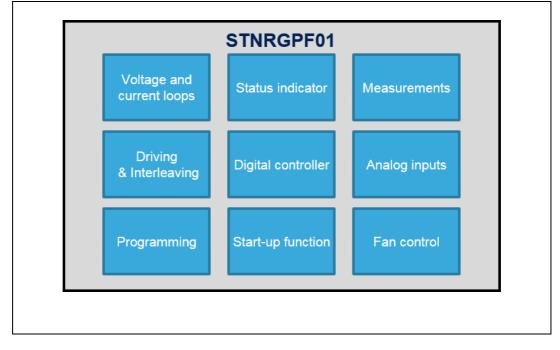

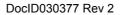

# 3 STNRGPF01 block diagram

The block diagram of the STNRGPF01 device is shown in *Figure 2*.

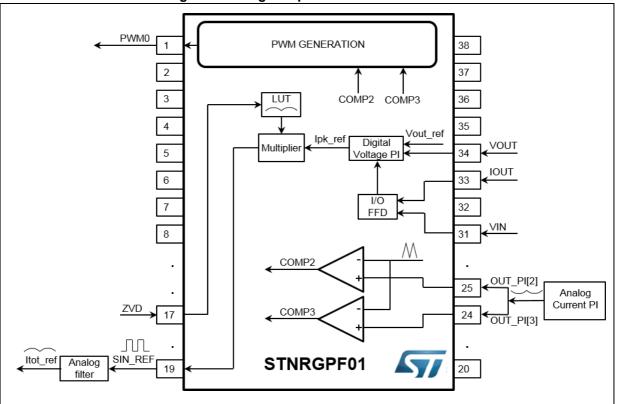

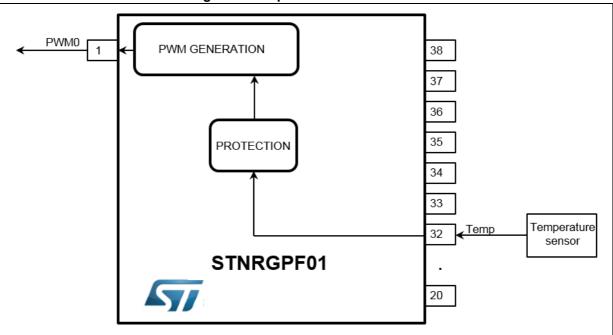

## 3.1 Voltage and current loop

The STNRGPF01 implements mixed signal average current control. The task of the digital voltage loop is to regulate the output voltage of the PFC. The VIN and IOUT measurements are used to implement the input/output feed-forward (I/O FFD), so load steps or input voltage variations are quickly compensated for by acting on digital PI output calculations. This function allows keeping the output voltage at the set point value and as constant as possible (see *Figure 3*).

The output of the digital PI controller is the peak current reference. In order to obtain a sinusoidal current reference, the  $I_{pk\_ref}$  is multiplied by a lookup table (LUT). The LUT is synchronized with the input voltage thanks to the ZVD signal (pin 17). The output of the multiplier is a PWM signal with a sinusoidal duty cycle that is configured on pin 19 SIN REF. An analog filter is used to obtain the final sinusoidal current reference for the external current loop ( $i_{tot\_ref}$ ). The analog PI current compares the reference  $i_{tot\_ref}$  with the total input current feedback ( $i_{tot\_fb}$ ) and generates the duty cycle wave for the PWM modulation. The master PWM signal is obtained by comparing (COMP2,3) the output of the PI current with a triangular wave at switching frequency (see *Figure 6: Analog comparators section* and *Section 3.4: Driving and interleaving*).

## 3.2 Measurements section

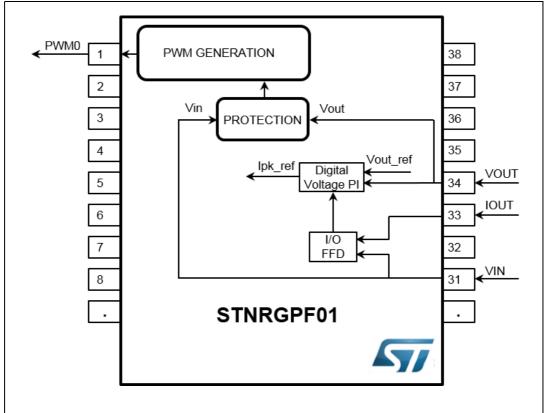

The STNRGPF01 includes 4 input measurement channels. These inputs are defined from pin 31 to pin 34 and they are specified below.

- Pin 31. VIN: RMS input voltage

- Pin 32. Temp: ambient temperature

- Pin 33. IOUT: PFC output current

- Pin 34: VOUT: PFC output voltage

#### Pin 31, VIN

This is the input of the RMS line voltage and also implements the voltage input feed-forward. The input voltage feed-forward modifies the PI output, compensating rapidly the effect of the line voltage changes. See *Figure 5*.

#### Pin 32, Temp

This is the input for the board temperature measurement. An external ST temperature sensor, STLM20, measures the board temperature. The PWM activity will be stopped when the temperature exceeds the user-defined threshold. See *Figure 4*.

#### Figure 4. Temperature measurement

### Pin 33, IOUT

Output current sensing. The measurement of this pin voltage allows implementation of the following functions:

- Load feed-forward. The input current reference is modified proportionally to the load, in order to provide a faster response versus the load transient.

- Channel power management. Each channel can be enabled or disabled based on the output current level. For example, up to 30% of the load, only one channel may be enabled, from 30% to 60% of the load, two configuration channels can be selected and at full load all channels may be activated.

#### Pin 34, VOUT

Output voltage sensing. This feedback input is connected via a voltage divider to the boost output voltage. This measurement allows implementation of the following functions:

- Output voltage regulation

- Overvoltage protection

In *Figure 5* the block scheme of the VIN, IOUT and VOUT is shown.

## 3.3 Analog input section

The STNRGPF01 device includes four fast analog comparators, from COMP0 to COMP3.

COMP3 and COMP2 have external reference voltages and are used to define the duty cycle of the PWM[0] master.

COMP1 and COMP0 have internal reference voltage and are used to implement the overcurrent protection features.

Figure 6. Analog comparators section

The positive inputs of COMP3 and COMP2 are on pin 24 and pin 25. Moreover, these comparators use a common external triangular reference voltage connected to pin 26.

The positive inputs of COMP1 and COMP0 are configured on pin 27 and pin 28.

DocID030377 Rev 2

A description of the comparator pins is given below:

- Pin 24 OUT\_PI[3]: positive input of the COMP3. It receives the output of the analog PI current.

- Pin 25 OUT\_PI[2]: positive input of the COMP2. It receives the output of the analog PI current.

- Pin 26 OSC: negative common input analog COMP2, 3. It receives the reference triangular waveform.

- Pin 27: positive input of the COMP1. It receives the sensing signal of the total input current.

- Pin 28: positive input of the COMP0. It receives the sensing signal of all switch currents. COMP0 stops driving when an overcurrent occurs in any switch.

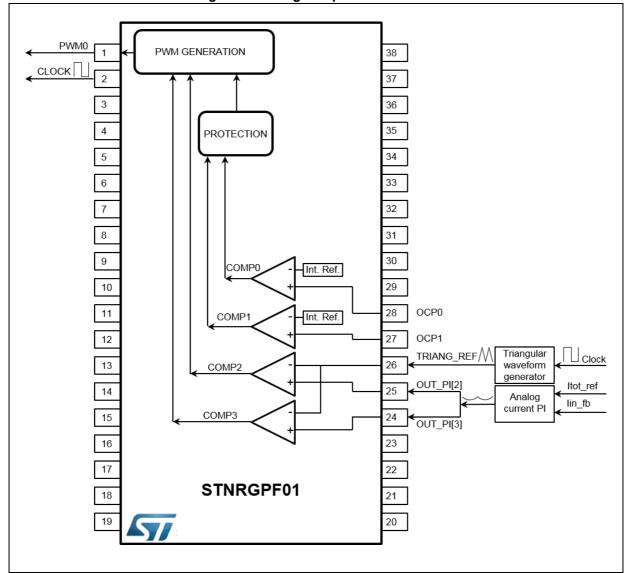

## 3.4 Driving and interleaving

The STNRGPF01 PWMs for channel driving are pins: 1, 4, 5, 8 and 16. *Figure 7* shows the configuration for PWM generation.

#### Figure 7. VIN, IOUT and VOUT measurement

DocID030377 Rev 2

The output level of COMP3 and COMP2 are used to generate the master PWM[0]. The SYNCR[1] and SYNCR[2] inputs are triggered respectively on the rising and falling edge of the PWM[0]. These trigger signals are sent to interleaving blocks which generate the phase shifted (120°/180° and 240°) ON/OFF signals for the other channels.

The SET[1], SET[2], RESET[1] and RESET[2] (pins: 4, 5, 8, 16) signals must be connected to external devices (for example two flip-flops) in order to obtain the driving signals PWM1 and PWM2.

The ENABLE input (pin 18) performs a protection function. The connection to the CLOCK signal (pin 2 at switching frequency) prevents undesired commutation of the PWM[0] and consequently on the other channels.

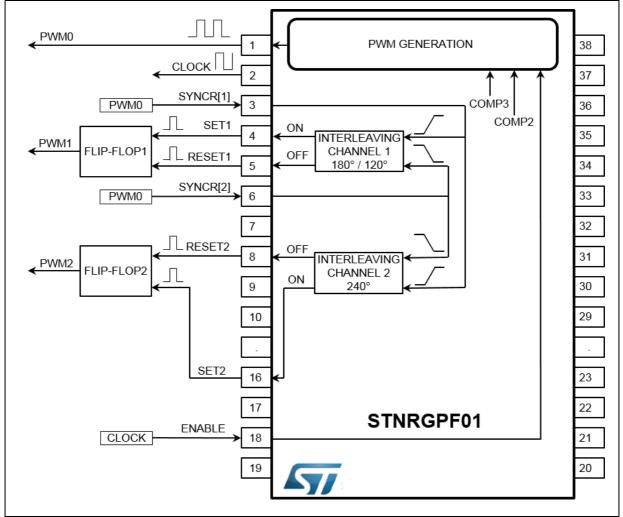

## 3.5 Programming section

Device programming is done by using a PC with dedicated loader software (STNRG LOADER), an FTDI cable and an adapter board (see *Figure 8*).

Figure 8. Programming section

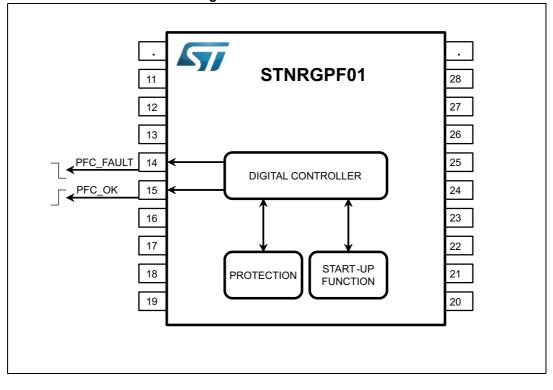

## 3.6 Status indicator

The STNRGPF01 device includes two pins to identify the running or fault status. These functions are defined on pin 14 and pin 15 (see *Figure 9*).

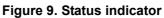

# 3.7 Start-up function

The start-up function is divided into two logical parts. The first is the inrush current limiter and the second part a PFC soft power-on. In *Figure 10* the timing of this function is shown.

## 3.7.1 Inrush current limiter

The device includes the possibility to perform the inrush current limiter function. Pin 21 gives a CMOS/TTL signal that becomes high after a settable time.

### 3.7.2 PFC soft power-on

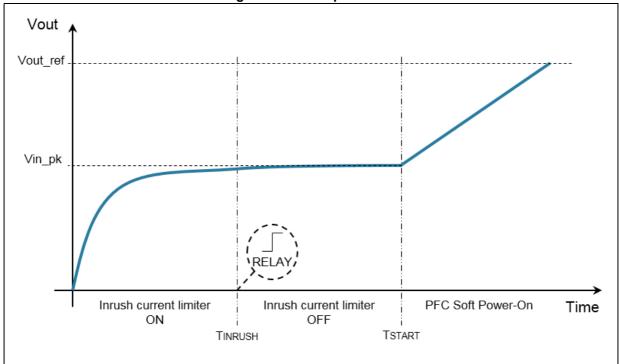

After the inrush current limiter phase the PFC switching activity on the master channel starts using the integrated function named soft power-on. Thanks to a controlled loop regulation the PFC output voltage will increase up to the set point ( $V_{out\_ref}$ ). The soft power-on function will be activated only in the conditions indicated below:

- No load condition. In this case the master channel enters into burst mode regulation. The PFC output voltage will oscillate between two settable levels (V<sub>burst\_min</sub> and V<sub>burst\_max</sub>). See *Figure 11*. These levels can be defined during device customization.

- Light load condition (below 5%). The PFC operates as in the no load condition.

- Load condition (down to 10%). In this case the PFC enters in the run mode and the output voltage will be regulated to the nominal value V<sub>out ref</sub>. See *Figure 11*.

When the PFC output voltage is controlled (burst mode or run mode - see conditions 1, 2, and 3) the soft power-on function will be completed and the PFC\_OK pin will be activated.

At the end of this phase the PFC is ready to work at the full load.

DocID030377 Rev 2

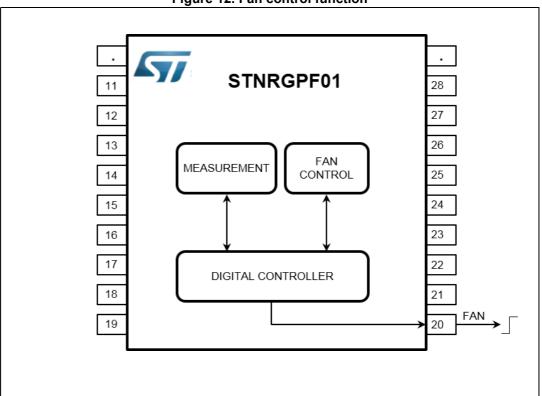

## 3.8 Fan control

The device offers the possibility to implement a fan control function. The customer defines the power level for activation of this function. Pin 20 provides a CMOS/TTL signal that becomes high for a power level higher than the specified threshold. See *Figure 12*.

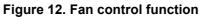

# 4 Pinout and pin description

# 4.1 Pinout

# 4.2 Pin description

| No. | . Type <sup>(1)</sup> Name Pin description |           |                                                                                                                                                                                                                                                                                                                                            |  |  |

|-----|--------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1   | OP                                         | PWM[0]    | This pin generates the PWM[0] for the master channel CH0.                                                                                                                                                                                                                                                                                  |  |  |

| 2   | 0                                          | CLOCK     | This pin generates a PWM signal at selected working frequency with a duty cycle of 50%. This signal is used to generate triangular waveforms at switching frequency by means of an external op-amp. The CLOCK signal is also used to implement protection against undesired commutations.                                                  |  |  |

| 3   | I                                          | SYNCR[1]  | This pin receives the PWM[0] signal in order to synchronize the other channels. The rising edge of the PWM[0] signal is used to trigger ON the slave channels CH1 and CH2.                                                                                                                                                                 |  |  |

| 4   | OP                                         | SET[1]    | This pin generates a pulse in order to set to ON the CH1 channel with the right out-<br>of-phase. This out-of-phase will be 120° electrical degrees when three channels are<br>activated and 180° when only two channels work. This pin is connected to a SET pin<br>of an external flip-flop in order to start the conduction of the CH1. |  |  |

| 5   | OP                                         | RESET[1]  | This pin generates a pulse in order to set OFF the CH1 channel with the right out-of-<br>phase. This out-of-phase will be 120° electrical degrees when three channels are<br>activated and 180° when only two channels work. This pin is connected to a RESET<br>pin of an external flip-flop in order to stop the conduction of the CH1.  |  |  |

| 6   | I                                          | SYNCR[2]  | This pin receives the PWM[0] signal in order to synchronize the other channels. The falling edge of the PWM[0] signal is used to trigger OFF the slave channels CH1 and CH2.                                                                                                                                                               |  |  |

| 7   | NC                                         | NC[1]     | Reserved                                                                                                                                                                                                                                                                                                                                   |  |  |

| 8   | OP                                         | RESET[2]  | This pin generates a pulse in order to set OFF the CH2 channel with out-of-phase of 240°. This pin is connected to a RESET pin of an external flip-flop in order to stop the conduction of the CH2.                                                                                                                                        |  |  |

| 9   | NC                                         | NC[2]     | Reserved                                                                                                                                                                                                                                                                                                                                   |  |  |

| 10  | I/O                                        | NRST      | Reset                                                                                                                                                                                                                                                                                                                                      |  |  |

| 11  | PS                                         | VDD       | Supply voltage                                                                                                                                                                                                                                                                                                                             |  |  |

| 12  | PS                                         | VSS       | Ground                                                                                                                                                                                                                                                                                                                                     |  |  |

| 13  | PS                                         | VCOUT     | Supply voltage of the digital section. An external capacitor must be connected to the VCOUT pin.                                                                                                                                                                                                                                           |  |  |

| 14  | 0                                          | PFC_FAULT | During normal operation this pin is high. If a fault condition occurs it is forced low.                                                                                                                                                                                                                                                    |  |  |

| 15  | 0                                          | PFC_OK    | When the PFC has completed the start-up procedure, this pin is forced low. During the start-up phase or when in fault condition, this pin is high.                                                                                                                                                                                         |  |  |

| 16  | OP                                         | SET[2]    | This pin generates a pulse in order to set ON the CH2 channel with out-of-phase of 240°. This pin is connected to a SET pin of an external flip-flop in order to start the conduction of the CH2.                                                                                                                                          |  |  |

| 17  | I                                          | ZVD       | This pin receives a square wave signal synchronized with input AC voltage. The rising edge of the square wave signal is used by the STNRGPF01 to detect the ZVD instant.                                                                                                                                                                   |  |  |

| 18  | I                                          | ENABLE    | This pin receives the CLOCK signal in order to avoid undesired commutation.                                                                                                                                                                                                                                                                |  |  |

| ι   | 1                                          |           | 1                                                                                                                                                                                                                                                                                                                                          |  |  |

#### Table 2. Pin description

| No. | Type <sup>(1)</sup> | Name          | Pin description                                                                                                                                                                                   |

|-----|---------------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19  | OP                  | SIN_REF       | This pin generates a PWM signal with the sinusoidal duty cycle. This PWM signal must be filtered in order to have the current sinusoidal reference that is synchronized with input voltage mains. |

| 20  | 0                   | FAN           | It generates a CMOS/TTL signal that is low until the PFC output power is below a threshold defined during device customization.                                                                   |

| 21  | 0                   | RELAY         | It generates a CMOS/TTL signal. This signal becomes high after a settable time defined during device customization. It is useful to perform the inrush current limiter function.                  |

| 22  | 0                   | PTX           | Programming data transmit                                                                                                                                                                         |

| 23  | I                   | PRX           | Programming data receive                                                                                                                                                                          |

| 24  | AI                  | OUT_PI[3]     | Positive input of the internal analog comparator 3. It receives the out of the analog PI current.                                                                                                 |

| 25  | AI                  | OUT_PI[2]     | Positive input of the internal analog comparator 3. It receives the out of the analog PI current.                                                                                                 |

| 26  | AI                  | TRIANG<br>REF | Negative input analog comparators 3 and 2. It receives the voltage triangular waveform.                                                                                                           |

| 27  | AI                  | OCP[0]        | Input overcurrent protection                                                                                                                                                                      |

| 28  | AI                  | OCP[1]        | Inductor overcurrent protection                                                                                                                                                                   |

| 29  | PS                  | VDDA          | Analog supply voltage                                                                                                                                                                             |

| 30  | PS                  | VSSA          | Analog ground                                                                                                                                                                                     |

| 31  | MI                  | VIN           | This pin measures the RMS input voltage.                                                                                                                                                          |

| 32  | MI                  | TEMP          | This pin measures the ambient board temperature. This measurement is performed using the STLM20 device, which gives an output voltage proportional to temperature.                                |

| 33  | MI                  | IOUT          | This pin measures the PFC output current.                                                                                                                                                         |

| 34  | MI                  | VOUT          | This pin measures the PFC output voltage.                                                                                                                                                         |

| 35  | RI                  | RI[1]         | Reserved. This pin must be pulled down by means a 10 k $\Omega$ resistor.                                                                                                                         |

| 36  | RI                  | RI[2]         | Reserved. This pin must be pulled down by means a 10 k $\Omega$ resistor.                                                                                                                         |

| 37  | RI                  | RI[3]         | Reserved. This pin must be pulled down by means a 10 k $\Omega$ resistor.                                                                                                                         |

| 38  | RI                  | RI[4]         | Reserved. This pin must be pulled down by means a 10 k $\Omega$ resistor.                                                                                                                         |

1. In *Table 3* a legend describing pin type is provided.

| Туре | Pin identification    |  |  |

|------|-----------------------|--|--|

| OP   | PWM driver            |  |  |

| 0    | Digital output        |  |  |

| I    | Digital input         |  |  |

| I/O  | Digital bidirectional |  |  |

| PS   | Power supply          |  |  |

| AI   | Analog input          |  |  |

| MI   | Measure input         |  |  |

Table 3. Pin identification legend

# 5 Electrical characteristics

## 5.1 Parameter conditions

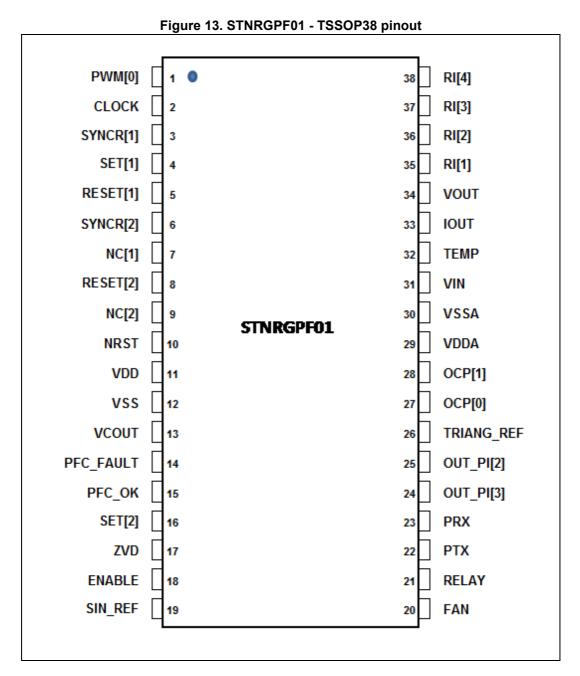

Unless otherwise specified, all voltages are referred to V<sub>SS</sub>. V<sub>DDA</sub> and V<sub>DD</sub> must be connected to the same voltage value. V<sub>SS</sub> and V<sub>SSA</sub> must be connected together with the shortest wire loop.

#### 5.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with the ambient temperature at  $T_A = 25$  °C and  $T_A = T_A$  max. (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated according to each table specific notes and are not tested in production.

### 5.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD}$  and  $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested. For the measurement section the accuracy is determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range.

### 5.1.3 Typical curves

Unless otherwise specified, all typical curves are given as design guidelines only and are not tested.

### 5.1.4 Typical current consumption

For typical current consumption measurements,  $V_{DD}$  and  $V_{DDA}$  are connected as shown in *Figure 14*.

Figure 14. Supply current measurement conditions

## 5.1.5 Loading capacitors

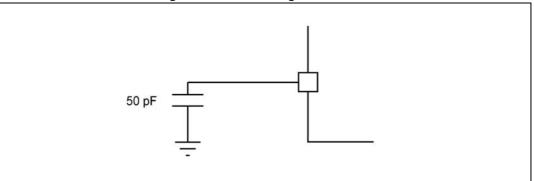

The loading conditions used for pin parameter measurement are shown in *Figure 15*.

## 5.1.6 Pin output voltage

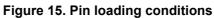

The input voltage measurement on a pin is described in *Figure 16*.

## Figure 16. Pin input voltage

# 5.2 Absolute maximum ratings

Stresses above those listed as 'absolute maximum ratings' may cause permanent damage to the device. This is a stress rating only and the functional operation of the device under these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect the device reliability.

| Symbol                             | Ratings                                                 | Min.                          | Max.                  | Unit |  |

|------------------------------------|---------------------------------------------------------|-------------------------------|-----------------------|------|--|

| $V_{DDX}$ - $V_{SSX}$              | Supply voltage <sup>(1)</sup>                           | -0.3                          | 6.5                   | V    |  |

| V <sub>IN</sub>                    | Input voltage on any other pin <sup>(2)</sup>           | V <sub>SS</sub> - 0.3         | V <sub>DD</sub> + 0.3 | v    |  |

| V <sub>DD</sub> - V <sub>DDA</sub> | Variation between different power pins                  | -                             | 50                    | mV   |  |

| $V_{SS}$ - $V_{SSA}$               | Variation between all the different ground $pins^{(3)}$ | -                             | 50                    | IIIV |  |

| V <sub>ESD</sub>                   | Electrostatic discharge voltage                         | Refer to Table 15 on page 33. |                       |      |  |

| Table 4. Voltage | characteristics |

|------------------|-----------------|

|------------------|-----------------|

All power V<sub>DDX</sub> (V<sub>DD</sub>, V<sub>DDA</sub>) and ground V<sub>SSX</sub> (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

2. I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>.

3.  $V_{SS}$  and  $V_{SSA}$  signals must be interconnected together with a short wire loop.

#### Table 5. Current characteristics

| Symbol                                                                 | Ratings                                              | Max. <sup>(1)</sup> | Unit |

|------------------------------------------------------------------------|------------------------------------------------------|---------------------|------|

| I <sub>VDDX</sub>                                                      | Total current into VDDX power lines <sup>(2)</sup>   | 100                 |      |

| I <sub>VSSX</sub>                                                      | Total current out of VSSX power lines <sup>(2)</sup> | 100                 |      |

|                                                                        | Output current sunk by any I/Os and control pin      | Ref. to Table 12 on | mA   |

| IIO                                                                    | Output current source by any I/Os and control pin    | page 28             | ШA   |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> , <sup>(4)</sup>                  | Injected current on any pin                          | ± 4                 |      |

| I <sub>INJ(TOT)</sub> <sup>(3)</sup> , <sup>(4)</sup> , <sup>(5)</sup> | Sum of injected currents                             | ± 20                |      |

1. Data based on characterization results, not tested in production.

2. All power V<sub>DDX</sub> (V<sub>DD</sub>, V<sub>DDA</sub>) and ground V<sub>SSX</sub> (V<sub>SS</sub>, V<sub>SSA</sub>) pins must always be connected to the external power supply.

I<sub>INJ(PIN)</sub> must never be exceeded. This is implicitly insured if V<sub>IN</sub> maximum is respected. If V<sub>IN</sub> maximum cannot be respected, the injection current must be limited externally to the I<sub>INJ(PIN)</sub> value. A positive injection is induced by V<sub>IN</sub> > V<sub>DD</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>.

4. Negative injection disturbs the analog performance of the device.

5. When several inputs are submitted to a current injection, the maximum I<sub>INJ(PIN)</sub> is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterization with the I<sub>INJ(PIN)</sub> maximum current injection on four I/O port pins of the device.

#### Table 6. Thermal characteristics

| Symbol | Ratings                              | Max. | Unit |

|--------|--------------------------------------|------|------|

| TSTG   | Storage temperature range -65 to 150 |      | °C   |

| TJ     | Maximum junction temperature         | 150  | C    |

# 5.3 Operating conditions

The device must be used in operating conditions that respect the parameters listed in *Table 7*. In addition, a full account must be taken for all physical capacitor characteristics and tolerances.

| Symbol                               | Parameter                                                             | Conditions  | Min.          | Тур.               | Max. | Unit |

|--------------------------------------|-----------------------------------------------------------------------|-------------|---------------|--------------------|------|------|

| V <sub>DD1</sub> , V <sub>DDA1</sub> | Operating voltages                                                    | -           | 3             | -                  | 5.5  |      |

| V <sub>DD</sub> , V <sub>DDA</sub>   | Nominal operating voltages                                            | -           | -             | 5                  | -    | V    |

|                                      | Core digital power supply                                             | -           | -             | 1.8 <sup>(1)</sup> | -    |      |

| V <sub>COUT</sub>                    | C <sub>VCOUT</sub> : capacitance of external capacitor <sup>(2)</sup> | at 1 MHz    | 470           | -                  | 3300 | nF   |

|                                      | ESR of external capacitor <sup>(1)</sup>                              |             | at 1 MHz 0.05 | -                  | 0.2  | Ω    |

|                                      | ESL of external capacitor <sup>(1)</sup>                              |             | -             | -                  | 15   | nH   |

| $\Theta_{JA}^{(3)}$                  | FR4 multilayer PCB                                                    | TSSOP38     | -             | 80                 | -    | °C/W |

| T <sub>A</sub>                       | Ambient temperature                                                   | Pd = 100 mW | -40           | -                  | 105  | °C   |

Table 7. General operating conditions

1. Internal core power supply voltage.

2. Care should be taken when the capacitor is selected due to its tolerance, its dependency on temperature, DC bias and frequency.

3. To calculate  $P_{Dmax}$  (T<sub>A</sub>), use the formula  $P_{Dmax}$  = (T<sub>Jmax</sub> - T<sub>A</sub>)/ $\Theta_{JA}$ .

| Symbol                | Parameter                 | Conditions             | Min. <sup>(1)</sup> | Тур. | Max. <sup>(1)</sup>  | Unit |

|-----------------------|---------------------------|------------------------|---------------------|------|----------------------|------|

| t <sub>VDD</sub>      | VDD rise time rate        | -                      | 2 µs/V              | -    | 1 s/V <sup>(2)</sup> |      |

|                       | VDD fall time rate        | -                      | 2 µs/V              | -    | 1 s/V <sup>(2)</sup> |      |

| t <sub>TEMP</sub>     | Reset release delay       | V <sub>DD</sub> rising | -                   | 3    | -                    | ms   |

| V <sub>IT+</sub>      | Power-on reset threshold  | -                      | 2.65                | 2.8  | 2.98                 | V    |

| V <sub>IT-</sub>      | Brownout reset threshold  | -                      | 2.58                | 2.73 | 2.88                 |      |

| V <sub>HYS(BOR)</sub> | Brownout reset hysteresis | -                      | -                   | 70   | -                    | mV   |

#### Table 8. Operating conditions at power-up/power-down

1. Guaranteed by design, not tested in production.

2. The power supply ramp must be monotone.