# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# STP1612PW05

# 16-channel LED driver with 16-bit PWM, 8-bit gain and full LED error detection

Preliminary data

### Features

- 16 constant current output channels

- Supply voltage: 3.3 V or 5 V

- Two PWM selectable counters 12/16-bit of grayscale

- Selectable enhanced PWM for ghost effect reduction

- Open and short LED detection

- 8-bit current gain control by means of 256 steps in two selectable ranges

- Single resistor to set the current from 3 mA to 60 mA

- Programmable progressive output delay

- Thermal protection and thermal flag

- UVLO

- Schmitt trigger input

- Selectable 16-bit or 256-bit serial data-in format

- Max clock frequency: 30 MHz

- ESD protection 2.5 kV HBM, 200 V MM

- Drop-in compatible with STP16CP\S\DP05 series

- Available in high thermal efficiency TSSOP exposed pad

### **Applications**

- Video display LED panels

- RGB backlighting

- Special lighting

- Table 1. Device summary

# Description

The STP1612PW05 is a 16-channel constant current sink LED driver. The maximum output current value for all the 16 channels is set by a single resistor from 3 mA to 60 mA. The device features 8-bit gain (256 steps) for global LED brightness adjustment with two selectable ranges. This function is accessible via a serial interface. The device has an individual adjustable PWM brightness control for each output channel. The PWM counters are selectable via a serial interface with 4096 or 65536 steps (12 or 16 bit). The STP1612PW05 also provides enhanced pulse-width modulation counting algorithms called e-PWM to reduce flickering effects (ghost visual effects) improving the overall image quality. The device has a dual size 16-bit or 256-bit shift register. All the control and the shift register read back data are accessible via serial interface. The STP1612PW05 has the capability to detect open and short LED failure and overtemperature, reporting the status through SPI line. The device guarantees a 20 V output driving capability, allowing the user to connect more LEDs in series.

| Order code      | Package             | Packaging           |

|-----------------|---------------------|---------------------|

| STP1612PW05QTR  | QFN-24              | 4000 parts per reel |

| STP1612PW05MTR  | SO-24               | 1000 parts per reel |

| STP1612PW05TTR  | TSSOP24             | 2500 parts per reel |

| STP1612PW05XTTR | TSSOP24 exposed pad | 2500 parts per reel |

February 2011

#### Doc ID 15819 Rev 5

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# Contents

| 1  | Block diagram                                                                                          |  |  |  |  |

|----|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| 2  | Summary description52.1Pin connection and description6                                                 |  |  |  |  |

| 3  | Electrical ratings73.1Absolute maximum ratings73.2Thermal data73.3Recommended operating conditions8    |  |  |  |  |

| 4  | Electrical characteristics9                                                                            |  |  |  |  |

| 5  | Timing waveform                                                                                        |  |  |  |  |

| 6  | Principle of operation                                                                                 |  |  |  |  |

| 7  | Configuration register 16                                                                              |  |  |  |  |

| 8  | Grey scales data loading 17                                                                            |  |  |  |  |

| 9  | Setting the PWM gray scale counter189.1PWM data synchronization189.2Synchronization for PWM counting19 |  |  |  |  |

| 10 | Error detection conditions 20                                                                          |  |  |  |  |

| 11 | Setting output current 22                                                                              |  |  |  |  |

| 12 | Constant current 23                                                                                    |  |  |  |  |

| 13 | Current gain adjustment 24                                                                             |  |  |  |  |

| 14 | Delay time of staggered output 25                                                                      |  |  |  |  |

| 15 | Thermal protection                                                                                     |  |  |  |  |

### STP1612PW05

| 16 | Time-out alert of GCLK disconnection |

|----|--------------------------------------|

| 17 | Application information              |

|    | 17.1 LED supply voltage (VLED) 27    |

|    | 17.2 Setting grayscale brightness 29 |

|    | 17.3 Multi device application 30     |

| 18 | Package mechanical data 31           |

| 19 | Revision history                     |

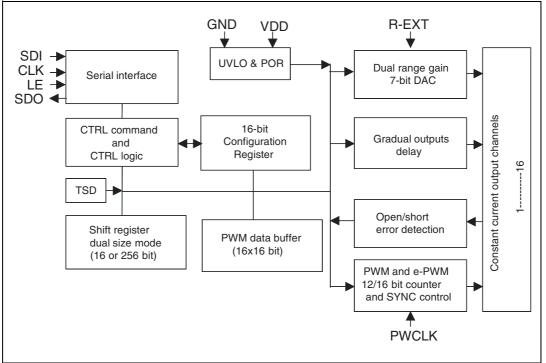

# 1 Block diagram

# 2 Summary description

### Table 2.Typical current accuracy at 5 V

| Output voltage | Current<br>accuracy | Output current | V <sub>DD</sub> | temp. |  |

|----------------|---------------------|----------------|-----------------|-------|--|

|                | Between ICs         |                |                 |       |  |

| ≥ 1.0          | ± 6%                | 15 to 60       | 5 V             | 25 °C |  |

| ≥ 0,2          | ± 6%                | 3 to 15        | 5 V             | 25 0  |  |

#### Table 3.Typical current accuracy at 3.3 V

| Output voltage | Current<br>accuracy<br>Between ICs | accuracy Output current |        | temp. |

|----------------|------------------------------------|-------------------------|--------|-------|

| ≥ 1.0          | ± 6%                               | 15 to 60                | 2.2.1/ | of °C |

| ≥ 0,3          | ± 6%                               | 3 to 15                 | 3.3 V  | 25 °C |

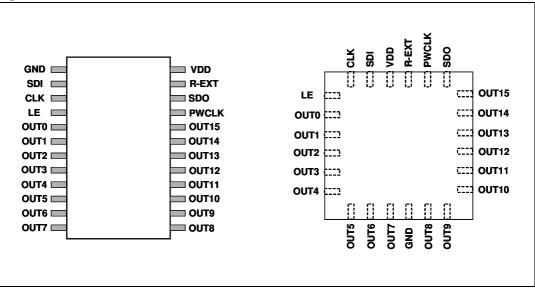

### 2.1 Pin connection and description

*Note:* The exposed pad should be electrically connected to a metal land electrically isolated or connected to ground

#### Table 4. Pin description

| Pin n° | Symbol          | Name and function                                                                                           |  |  |

|--------|-----------------|-------------------------------------------------------------------------------------------------------------|--|--|

| 1      | GND             | Ground terminal                                                                                             |  |  |

| 2      | SDI             | Serial data input terminal                                                                                  |  |  |

| 3      | CLK             | Clock input terminal used to shift data on rising edge and carries command information when LE is asserted. |  |  |

| 4      | LE              | Data strobe terminal and controlling command with CLK                                                       |  |  |

| 5-20   | OUT 0-15        | Output terminals                                                                                            |  |  |

| 21     | PWCLK           | Gray scale clock terminal.<br>Reference clock for grey scale PWM counter.                                   |  |  |

| 22     | SDO             | Serial data out terminal                                                                                    |  |  |

| 23     | R-EXT           | Input terminal of an external resistor for constant current programing                                      |  |  |

| 24     | V <sub>DD</sub> | Supply voltage terminal                                                                                     |  |  |

#### **Electrical ratings** 3

#### Absolute maximum ratings 3.1

Stressing the device above the rating listed in the Table 5 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Symbol           | Parameter                      | Value                   | Unit |

|------------------|--------------------------------|-------------------------|------|

| V <sub>DD</sub>  | Supply voltage                 | 0 to 7                  | V    |

| Vo               | Output voltage                 | -0.5 to 20              | V    |

| Ι <sub>Ο</sub>   | Output current                 | 60                      | mA   |

| VI               | Input voltage                  | -0.4 to V <sub>DD</sub> | V    |

| I <sub>GND</sub> | GND terminal current           | 1300                    | mA   |

| f <sub>CLK</sub> | Clock frequency                | 50                      | MHz  |

| TJ               | Junction temperature range (1) | -40 to + 170            | °C   |

Table 5. Absolute maximum ratings

1. Such absolute value is based on the thermal shutdown protection.

#### 3.2 **Thermal data**

| Table 6.           | Thermal data                             |                                       |             |      |

|--------------------|------------------------------------------|---------------------------------------|-------------|------|

| Symbol             | Parameter                                |                                       | Value       | Unit |

| T <sub>A</sub>     | Operating free-air temperature rang      | e                                     | -40 to +125 | °C   |

| T <sub>J-OPR</sub> | Operating thermal junction temperat      | ture range                            | -40 to +150 | °C   |

| T <sub>STG</sub>   | Storage temperature range                | -55 to +150                           | °C          |      |

|                    |                                          | SO-24                                 | 42.7        | °C/W |

|                    | Thermal resistance junction-             | TSSOP24                               | 55          | °C/W |

| R <sub>thJA</sub>  | R <sub>thJA</sub> ambient <sup>(1)</sup> | TSSOP24 <sup>(2)</sup><br>Exposed pad | 37.5        | °C/W |

|                    |                                          |                                       | 55          | °C/W |

1. According to Jedec standard 51-7B

2. The exposed pad should be soldered directly to the PCB to realize the thermal benefits.

# 3.3 Recommended operating conditions

| Table 7.              | Recommended operating conditions at 25 °C |                                       |                     |      |                     |      |

|-----------------------|-------------------------------------------|---------------------------------------|---------------------|------|---------------------|------|

| Symbol                | Parameter                                 | Test conditions                       | Min.                | Тур. | Max.                | Unit |

| $V_{DD}$              | Supply voltage                            |                                       | 3.0                 | -    | 5.5                 | V    |

| Vo                    | Output voltage                            |                                       |                     | -    | 20                  | V    |

| Ι <sub>Ο</sub>        | Output current, OUTn                      |                                       | 3                   | -    | 60                  | mA   |

| I <sub>OH,SDO</sub>   | Output current, SDO                       |                                       |                     | -    | +1                  | mA   |

| I <sub>OL,SDO</sub>   | Output current, SDO                       |                                       |                     | -    | -1                  | mA   |

| V <sub>IH</sub>       | Input voltage                             |                                       | 0.7 V <sub>DD</sub> | -    | V <sub>DD</sub>     | V    |

| V <sub>IL</sub>       | Input voltage                             |                                       | GND                 | -    | 0.3 V <sub>DD</sub> | V    |

| t <sub>wLAT</sub>     | LE pulse width                            |                                       | 20                  | -    |                     | ns   |

| t <sub>wCLK</sub>     | CLK pulse width                           |                                       | 10                  | -    |                     | ns   |

| t <sub>wEN</sub>      | PWCLK pulse width                         | • V <sub>DD</sub> = 3.3 V to 5.0 V    | 20                  | -    |                     | ns   |

| t <sub>SETUP(D)</sub> | Setup time for DATA                       | $v_{\rm DD} = 3.3 \ v \ 10 \ 3.0 \ v$ | 5                   | -    |                     | ns   |

| t <sub>HOLD(D)</sub>  | Hold time for DATA                        |                                       | 5                   | -    |                     | ns   |

| t <sub>SETUP(L)</sub> | Setup time for LATCH                      |                                       | 5                   | -    |                     | ns   |

| f <sub>CLK</sub>      | Clock frequency                           | Cascade operation <sup>(1)</sup>      |                     | -    | 30                  | MHz  |

Table 7.

Recommended operating conditions at 25 °C

1. If the device is connected in cascade, it may not be possible achieve the maximum data transfer. Please considered the timings carefully.

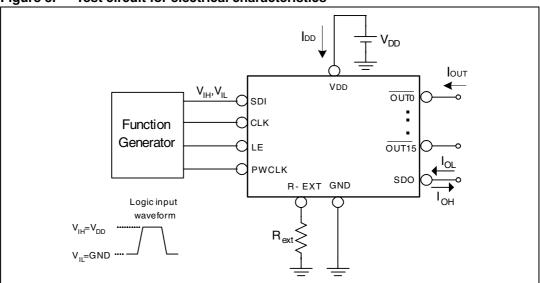

# 4 Electrical characteristics

$V_{DD}$  = 3.3 V  $\pm$  10%,  $V_{DD}$  = 5 V  $\pm$  10%,  $T_A$  = 25 °C unless otherwise specified

Symbol Characteristics **Test conditions** Min. Typ. Max. Unit OUT0 ~ OUT15 ٧ Vo Maximum output voltage 20 OUT0~OUT115  $V_{O} = 2V$ IOUT 3 60 Output SDO -8 mΑ I<sub>OH,SDO</sub> current SDO 8 I<sub>OL.SDO</sub> Input voltage "H" level 0.7 \* V<sub>DD</sub> V  $V_{H}$  $V_{DD}$ Input voltage "L" level GND 0.3 \* V<sub>DD</sub> V  $V_{IL}$ Output leakage current  $V_{O} = 20 V$ 1 IOH μΑ  $I_{OL} = +8 \text{ mA}$ 0.4 v VOL Output voltage SDO I<sub>OH</sub> = -8 mA  $V_{OH}$ ٧ V<sub>DD</sub> - 0.4  $I_{OUT} = 3mA, V_O = 0.3V,$ dl<sub>OUT1</sub>  $R_{EXT} = 238.2 k\Omega$ Current skew (channel) ±1.5 % ±3  $I_{OUT} = 20mA, V_{O} = 1V,$ dl<sub>OUT1</sub>  $R_{EXT} = 34.7 k\Omega$  $I_{OUT} = 3mA, V_{O} = 0.3V,$ dl<sub>OUT2</sub>  $R_{EXT} = 238.2 k\Omega$ Current skew (IC) % ±З ±6  $I_{OUT} = 20mA, V_{O} = 1V,$ dI<sub>OUT2</sub>  $R_{FXT} = 34.7 k\Omega$ V<sub>O</sub> within 1.0 V and 3.0 V, Output current vs. output voltage %/dV<sub>O</sub> ±0.1  $\pm 0.5$ %/V regulation R<sub>ext</sub> = 34.7 kΩ @ 20 mA Output current vs. supply voltage  $V_{DD}$  within 4.5 V and 5.5 V %/dV<sub>DD</sub> ±1.0  $\pm 5.0$ %/V regulation Pull-down resistor LE 150 200 250 kΩ R<sub>IN(down)</sub> Rext = Open, 8 11 I<sub>DD(off)</sub> 1  $\overline{OUT0} \sim \overline{OUT15} = Off$ I<sub>O</sub> = 3 mA, Supply current "Off" 8.5 11 I<sub>DD(off) 2</sub>  $\overline{OUTO} \sim \overline{OUT15} = Off$  $I_{O} = 60 \text{ mA},$ 11 15 mΑ IDD(off) 3  $\overline{OUT0} \sim \overline{OUT15} = Off$  $I_{O} = 3 \text{ mA},$ 8 11.5 IDD(on) 1  $\overline{OUT0} \sim \overline{OUT15} = On$ Supply current "On"  $I_{O} = 60 \text{ mA},$ 11.5 15 I<sub>DD(on) 2</sub>  $\overline{OUTO} \sim \overline{OUT15} = On$

Table 8.Electrical characteristics

Figure 3. Test circuit for electrical characteristics

Doc ID 15819 Rev 5

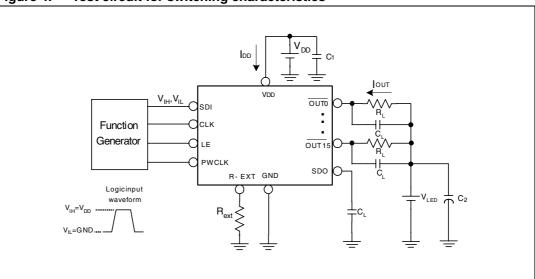

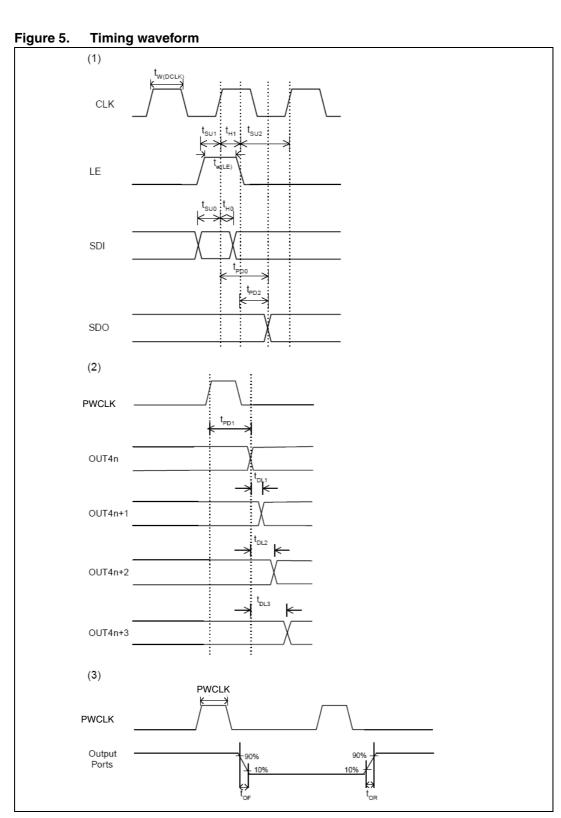

| Table 9.              | Switching characteristics ( $V_{DD} = 5.0$ V) $T_A = -40 \approx 125$ |                                   |                                                    |      |      |      |      |

|-----------------------|-----------------------------------------------------------------------|-----------------------------------|----------------------------------------------------|------|------|------|------|

| Symbol                | Characteristics                                                       | Conditio                          | ons                                                | Min. | Тур. | Max. | Unit |

| t <sub>SU0</sub>      |                                                                       | SDI - CLK ↑                       |                                                    | 1    |      |      | ns   |

| t <sub>SU1</sub>      | Setup time                                                            | $LE \uparrow - DCLK \uparrow$     |                                                    | 1    |      |      | ns   |

| t <sub>SU2</sub>      |                                                                       | LE $\downarrow$ – DCLK $\uparrow$ |                                                    | 5    |      |      | ns   |

| t <sub>H0</sub>       | Lold time                                                             | CLK↑ - SDI                        |                                                    | 3    |      |      | ns   |

| t <sub>H1</sub>       | - Hold time                                                           | CLK ↑ - LE $\downarrow$           |                                                    | 7    |      |      | ns   |

| t <sub>PD0</sub>      |                                                                       | CLK - SDO                         | V <sub>DD</sub> = 5.0 V                            |      | 30   | 40   | ns   |

| t <sub>PD1</sub>      | Propagation<br>delay time                                             | PWCLK-OUTn4 <sup>(1)</sup>        | $V_{IH} = V_{DD}$<br>$V_{IL} = GND$                |      | 100  |      | ns   |

| t <sub>PD2</sub>      |                                                                       | LE – SDO <sup>(2)</sup>           | $R_{ext} = 460 \Omega$                             |      | 30   | 40   | ns   |

| t <sub>DL1</sub>      |                                                                       | OUTn4 + 1 <sup>(1)</sup>          | V <sub>LED</sub> = 4.5 V<br>R <sub>I</sub> = 152 Ω |      | 40   |      | ns   |

| t <sub>DL2</sub>      | Stagger delay                                                         | OUTn4 + 2 <sup>(1)</sup>          | CL = 10 pF                                         |      | 80   |      | ns   |

| t <sub>DL3</sub>      |                                                                       | OUTn4 +3 (1)                      | C1 = 100 nF<br>C2 = 10 μF                          |      | 120  |      | ns   |

| t <sub>w(L)</sub>     |                                                                       | LE                                | $I_0 = 20 \text{ mA}$                              | 5    |      |      | ns   |

| t <sub>w( CLK)</sub>  | Pulse width                                                           | CLK                               |                                                    | 20   |      |      | ns   |

| t <sub>w(PWCLK)</sub> | _                                                                     | PWCLK                             |                                                    | 20   |      |      | ns   |

| t <sub>ON</sub>       | Output rise time of                                                   | Dutput rise time of output ports  |                                                    |      | 10   |      | ns   |

| t <sub>OFF</sub>      | Output fall time of                                                   | output ports                      |                                                    |      | 6    |      | ns   |

| t <sub>EDD</sub>      | Error detection m                                                     | inimum duration <sup>(3)</sup>    |                                                    |      | 1    |      | μs   |

Table 9. Switching characteristics ( $V_{DD}$  = 5.0 V)  $T_A$  = -40 ~ 125 ° C

1. Refer to the timing waveform, where n = 0, 1, 2, 3.

In timing of "read configuration" and "read error status code", the next CLK rising edge should be t<sub>PD2</sub> after the falling edge of LE.

3. Refer to *Figure 5 on page 13*.

| Symbol                | Characteristics                  | Conditio                         | ons                                  | Min. | Тур. | Max. | Unit |

|-----------------------|----------------------------------|----------------------------------|--------------------------------------|------|------|------|------|

| t <sub>SU0</sub>      |                                  | SDI - DCLK ↑                     |                                      | 1    |      |      | ns   |

| t <sub>SU1</sub>      | Setup time                       | $LE \uparrow - DCLK \uparrow$    |                                      | 1    |      |      | ns   |

| t <sub>SU2</sub>      | _                                | $LE \downarrow - DCLK \uparrow$  |                                      | 5    |      |      | ns   |

| t <sub>H0</sub>       | - Hold time                      | CLK↑ - SDI                       |                                      | 3    |      |      | ns   |

| t <sub>H1</sub>       |                                  | $CLK \uparrow$ - $LE \downarrow$ |                                      | 7    |      |      | ns   |

| t <sub>PD0</sub>      |                                  | CLK - SDO                        | V <sub>DD</sub> = 3.3 V              |      | 45   | 40   | ns   |

| t <sub>PD1</sub>      | Propagation delay time           | PWCLK-OUTn4 <sup>(1)</sup>       | $V_{IH} = V_{DD}$<br>$V_{II} = GND$  |      | 120  |      | ns   |

| t <sub>PD2</sub>      |                                  | LE – SDO <sup>(2)</sup>          | $R_{ext} = 460 \Omega$               |      | 45   | 40   | ns   |

| t <sub>DL1</sub>      |                                  | OUTn4 + 1 <sup>(1)</sup>         | $V_{LED} = 4.5 V$                    |      | 40   |      | ns   |

| t <sub>DL2</sub>      | Stagger delay                    | OUTn4 + 2 <sup>(1)</sup>         | R <sub>L</sub> = 152 Ω<br>CL = 10 pF |      | 80   |      | ns   |

| t <sub>DL3</sub>      |                                  | OUTn4 +3 (1)                     | C1 = 100  nF                         |      | 120  |      | ns   |

| t <sub>w(L)</sub>     |                                  | LE                               | C2 = 10 μF                           | 5    |      |      | ns   |

| t <sub>w(CLK)</sub>   | Pulse width                      | CLK                              |                                      | 20   |      |      | ns   |

| t <sub>w(PWCLK)</sub> | _                                | PWCLK                            |                                      | 20   |      |      | ns   |

| t <sub>ON</sub>       | Output rise time of output ports |                                  |                                      |      | 11.6 |      | ns   |

| t <sub>OFF</sub>      | Output fall time of output ports |                                  |                                      |      | 7    |      | ns   |

| t <sub>DEC</sub>      | Error detection dur              | ation                            |                                      |      | 0.5  | 1    | μs   |

Table 10. Switching characteristics (V<sub>DD</sub> = 3.3 V)

1. Refer to the timing waveform *Figure 4*, where n = 0, 1, 2, 3.

In timing of "read configuration" and "read error status code", the next CLK rising edge should be t<sub>PD2</sub> after the falling edge of LE.

Figure 4. Test circuit for switching characteristics

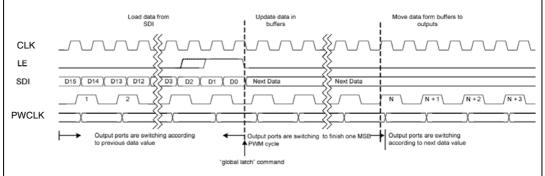

# 5 Timing waveform

Doc ID 15819 Rev 5

# 6 Principle of operation

|                                          | Signals combination |                                                     | Description                                                       |  |  |

|------------------------------------------|---------------------|-----------------------------------------------------|-------------------------------------------------------------------|--|--|

| Command name                             | LE                  | Number of CLK<br>rising edge when<br>LE is asserted | The action after a falling edge of LE                             |  |  |

| Data latch                               | High                | 1                                                   | Serial data are transferred to the buffers                        |  |  |

| Global latch                             | High                | 2 or 3                                              | Buffer data are transferred to the comparators                    |  |  |

| Read configuration                       | High                | 4 or 5                                              | Move out "configuration register" to the shift register           |  |  |

| Enable "error detection"                 | High                | 6 or 7                                              | Detect the status of each output's LED                            |  |  |

| Read "error status code"                 | High                | 8 or 9                                              | Move out "error status code" of 16 outputs to the shift registers |  |  |

| Write configuration                      | High                | 10 or 11                                            | Serial data are transferred to the<br>"configuration register"    |  |  |

| Reset to 16-bit shift<br>register length | High                | 12 or 13                                            | Set to 16-bit the shift register length                           |  |  |

#### Table 11. Control command

| Figure  | 6. Timing diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Data L  | atch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CLK     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDI     | MSB<br>D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 Next Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDO     | Previous Data XD15 XD14 X D13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Global  | Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLK     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LE      | MSB //                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| SDI     | MSB         MSB |

| SDO     | Previous Data XD15 XD14 X D13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bead (  | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLK     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LE      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SDO     | Previous Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Write C | Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLK     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| LE      | /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SDI     | F X E X D X C X B X A X 9 X 8 X 7 X 6 X 5 X 4 X 3 X 2 X 1 X 0 X Next Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SDO     | Previous Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Figure 6. Timing diagram

# 7 Configuration register

| Bit   | Attribute  | Definition                                                                                                                 | Value                                                                                            | Function                                                                               | Default<br>value |  |  |  |

|-------|------------|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|--|--|--|

| 15    | Read/Write | Shift register                                                                                                             | 0                                                                                                | 16 bit shift register                                                                  | 0                |  |  |  |

| 15    | neau/write | length                                                                                                                     | 1                                                                                                | 256 bit shift register                                                                 | U                |  |  |  |

| 14    | Read       | Thermal error                                                                                                              | 0                                                                                                | Temperature OK                                                                         | 0                |  |  |  |

| 14    | neau       | flag                                                                                                                       | 1                                                                                                | Over temperature (>150°C typ.)                                                         | U                |  |  |  |

| 13    | Read/Write | PWM counter                                                                                                                | 0                                                                                                | 0 12 bit Grayscale PWM counter                                                         |                  |  |  |  |

| 13    | neau/write | (12/16 bit)                                                                                                                | 1                                                                                                | 16 bit Grayscale PWM counter                                                           | 0                |  |  |  |

|       | Read/Write |                                                                                                                            | 00                                                                                               | 64 times of $MSB^{(1)}$ 6-bit PWM counting plus once of $LSB^{(1)}$ 6-bit PWM          |                  |  |  |  |

| 12-11 |            | PWM counting mode                                                                                                          | 01                                                                                               | 16 times of MSB 6-bit PWM counting by 1/4<br>PWCLK plus once of LSB 6-bit PWM counting | 11               |  |  |  |

|       |            | selection                                                                                                                  | 10     4 times of MSB 6-bit PWM counting by 1/16       PWCLK plus once of LSB 6-bit PWM counting |                                                                                        |                  |  |  |  |

|       |            |                                                                                                                            | 11                                                                                               | PWM counting                                                                           | 1                |  |  |  |

|       | -          | PWM data                                                                                                                   |                                                                                                  | Auto-synchronization                                                                   |                  |  |  |  |

| 10    | Read/Write | synchronizatio<br>n mode                                                                                                   | 1                                                                                                | Manual synchronization                                                                 | 1                |  |  |  |

| 9-2   | Read/Write | ead/Write Current gain Adjust the current value set by R-EXT over 256 Adjust the current value set by R-EXT over 256 steps |                                                                                                  | 8b 10101011                                                                            |                  |  |  |  |

|       |            | Thermal                                                                                                                    | 0                                                                                                | Disable                                                                                |                  |  |  |  |

| 1     | Read/Write | Shutdown<br>function                                                                                                       | 1                                                                                                | Enable <sup>(2)</sup> (output channels OFF if temperature overcomes 150°C)             | 0                |  |  |  |

|       |            | Time-out alert                                                                                                             | 0                                                                                                | Enable <sup>(3)</sup>                                                                  |                  |  |  |  |

| 0     | Read/Write | for PWCLK<br>disconnection                                                                                                 | 1                                                                                                | Disable                                                                                | 0                |  |  |  |

#### Table 12. Configuration register

1. Please refer to "setting the PWM counting mode" section.

2. Please refer to "TSD" thermal error flag and thermal shutdown "section.

3. Please refer to "time-out alert of PWCLK disconnection" section.

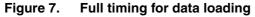

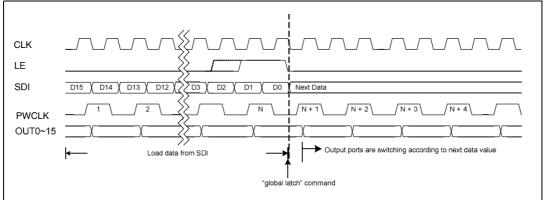

## 8 Grey scales data loading

The STP1612PW05 is able to manage a gray-scale depth of 12 or 16 bits for each output, exploiting an e-PWM algorithm.

The bit D of the configuration register is used to select the grey-scale loading. Its value can be set to "0" for 12 bits or "1" for 16 bits. By default, D is set to "0".

Loading of the data is performed through the serial input on a dedicated buffer and two different methods can be used.

With both methods, the first incoming data packet is relative to the output 15; the following packet is relative to the output 14 and so on up to the output 0.

If F="0", when a data packet has been loaded, the latch signal (LE) must become active for one CLK cycle (data latch). When the last data packet, relative to the output 0, has been loaded, the latch signal must be active for two CLK cycles (global latch) and all the data will be transferred to the e-PWM registers starting from the MSB.

If F="1" all data packets (12 or 16 bits x16) are loaded and then the global latch signal must be active and all the data will be transferred to the e-PWM registers starting from the MSB.

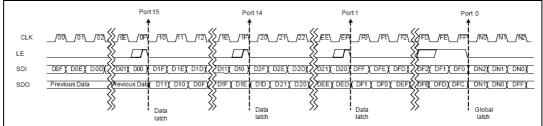

## 9 Setting the PWM gray scale counter

STP1612PW05 provides a 12-bit or 16-bit PWM color depth. Each serial data input will be implemented according to the e-PWM algorithm.

### 9.1 **PWM data synchronization**

STP1612PW05 defines the different counting algorithms that support e-PWM, technology, (scrambled PWM). With e-PWM, the total PWM cycles can be broken down into MSB (most significant bits) and LSB (least significant bits) of gray scale cycles, and the MSB information can be dithered across many refresh cycles to achieve overall same high bit resolution. STP1612PW05 also allows changing different counting algorithms and provides the best output linearity when there are fewer transitions of output.

| PWCLK              | PWCLK<br>₩                              | LSB 6-bit PWM countin  |

|--------------------|-----------------------------------------|------------------------|

|                    | ► 64 times of MSB 6-bit PWM Counting    | <b>→</b>               |

|                    | MSB 6-bit PWM Counting:<br>252 GCLKs    | LSB 6-bit PWM counting |

| PWCLK              |                                         |                        |

|                    | ◄ 16 times of MSB 6-bit PWM Counting    |                        |

|                    | MSB 6-bit PWM Counting:<br>1008 GCLKs   | LSB 6-bit PWM Counting |

| PWCLK              |                                         |                        |

|                    | ◀ 4 times of MSB 6-bit PWM Counting     |                        |

| PWCLK              | 12-bit PWM Counting:<br>4096 GCLKs<br>◀ | <b>&gt;</b>            |

|                    | Once of 12-bit PWM Counting             |                        |

| : Output ports are | "on".                                   |                        |

Figure 8. 12-bit e-PWM operation example

### 9.2 Synchronization for PWM counting

The data synchronization between the incoming data flow and the output channels is managed through the bit A within the configuration register.

If the bit A is set to "0" the device performs itself the data synchronization: when all the new data are loaded with a "global latch", the device wait until all the PWM counter completes the counting cycle before updating them with the new data, at the next CLK rising edge.

Conversely, if bit A is set to "1" (default), the data synchronization is not performed by the device and is managed by the microcontroller, which has to take care of the data and signals. If this is not done, there might be artefacts on the output image.

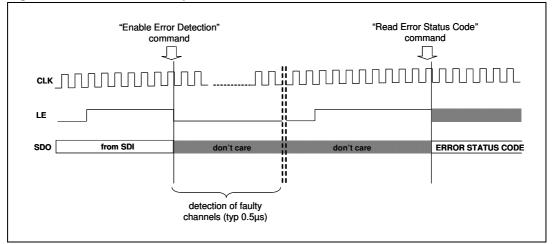

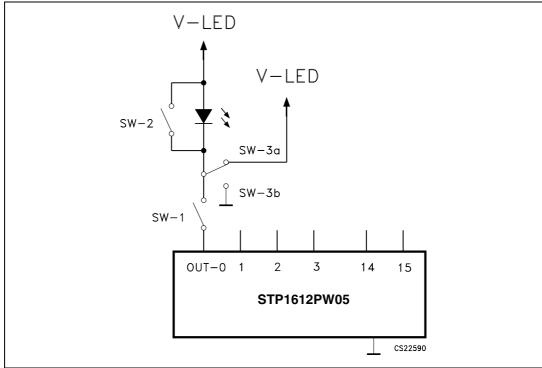

# **10** Error detection conditions

The STP1612PW05 can detect open channels (OD) and LED short-circuits (SD).

The detection circuitry performs open- and short-circuit detection simultaneously and needs that all channels must be on. However the short test duration (0.5  $\mu$ s typ) does not impact the image quality.

According to *Table 11*, the command "Enable Error Detection" starts the diagnostic process. After 0.5  $\mu$ s (typ) the faults detection has already been carried out and, through the command "Read Error Status Code", the status is available on the serial output (SDO).

A bit set to "1" in the Error Status Code represents a channel considered good, whereas a "0" represents a failed output (open/short).

*Figure 11* describes the error detection process.

Figure 11. Error detection process

The *Table 13* and *Figure 12* explains the fault conditions detected by the diagnostic circuitry and how the detection is performed.

Table 13. Detection conditions ( $V_{DD}$  = 3.3 to 5 V temp. range -40 to 125 °C)

| SW-1 or<br>SW-3b | Open line or output short to GND detected | ==> l <sub>ODEC</sub> ⊴0.5 x l <sub>O</sub> |  |  |  |  |

|------------------|-------------------------------------------|---------------------------------------------|--|--|--|--|

| SW-2 or<br>SW-3a | Short on LED or short to V-LED detected   | ==> $V_0 \ge 2.3 V$                         |  |  |  |  |

*Note:* Where:  $I_O$  = the output current programmed by the R<sub>EXT</sub>,  $I_{ODEC}$  = the detected output current in detection mode

## **11** Setting output current

The output current (I<sub>OUT</sub>) is set by an external resistor, R<sub>ext</sub>.

It is calculated from the equation:

$V_{R-EXT} = 1.24 \text{ x G}; I_{OUT} = (V_{R-EXT}/R_{ext}) \text{ x 560}$

Whereas R<sub>ext</sub> is the resistance of the external resistor connected to R-EXT terminal and V<sub>R-EXT</sub> is its voltage. G is the digital current gain, which is set by the bit9 – bit2 of the configuration register. The default value of G is 1. For your information, the output current is about 20 mA when R<sub>ext</sub> = 34.70 k $\Omega$  and 10 mA when R<sub>ext</sub> = 69.6 k $\Omega$  if G is set to default value 1. The formula and setting for G are described in next section.

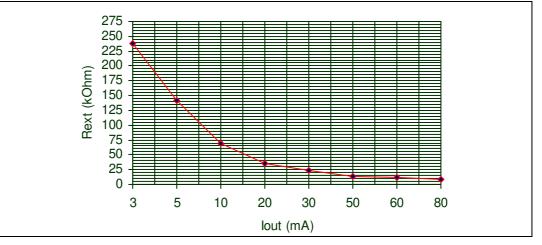

Figure 13. Rext vs output current

Table 14.Rext vs output current (1)

| lout (mA) | Rext (kΩ) |

|-----------|-----------|

| 3         | 238.2     |

| 5         | 142.2     |

| 10        | 69.6      |

| 20        | 34.70     |

| 30        | 22.94     |

| 50        | 13.72     |

| 60        | 11.40     |

| 80        | 8.63      |

1.  $T_A = 25 \text{ °C}, V_{dd} = 3.3 \text{ V}; 5.0 \text{ V}, V_{Led} = 3.0 \text{ V}, V_{drop} = 1.5 \text{ V}, \text{ HC} = 0101011 \text{ (default)}$

5

## 12 Constant current

The STP1612PW05 assures nearly no variation in current both from channel to channel and from IC to IC.

The typical variation of the current between channels of the same IC is  $\pm 1.5\%$ , whereas the variation between ICs is around  $\pm 3\%$ .

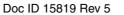

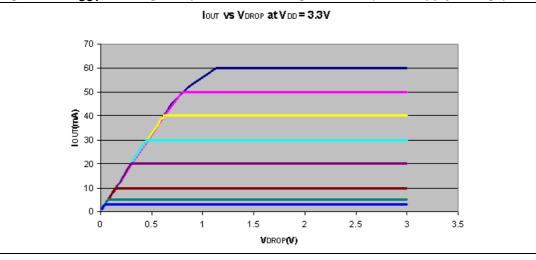

Moreover the current characteristic of the output stage is flat (see *Figure 14* and *Figure 15*). This contributes to keep the current constant regardless of the variation of the LEDs forward voltage ( $V_F$ ) and consequently guarantees uniformity of brightness.

Figure 14. I<sub>OUT</sub>vs voltage drop across current generators (3.3 V supply voltage)

Figure 15. I<sub>OUT</sub> vs voltage drop across current generators (5 V supply voltage)

The typical characteristics in *Figure 14* and *Figure 15* also show the minimum voltage drop required to assure that the current generators regulate the desired current.

This must be taken into account when choosing the suitable value of the LED supply voltage (see dedicated section).

Doc ID 15819 Rev 5

# 13 Current gain adjustment

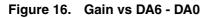

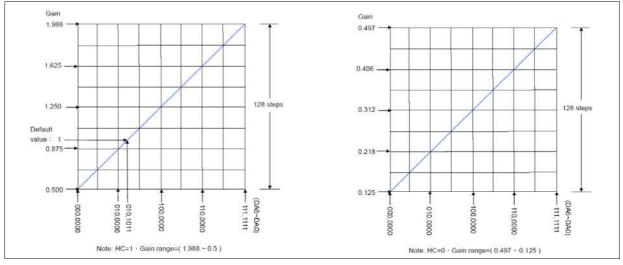

The bit 9 to bit 2 of the configuration register set the gain of output current, i.e., G. Being 8bit in total, ranging from 8'b00000000 to 8'b11111111, these bits allow the user to set the output current gain up to 256 levels. These bits can be further defined in the configuration register as follows:

### **Configuration register**

| MSB |   |   |   |   |   |    |     |     |     |     |     |     |     |   | LSB |

|-----|---|---|---|---|---|----|-----|-----|-----|-----|-----|-----|-----|---|-----|

| F   | Е | D | С | В | А | 9  | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1 | 0   |

| -   | - | - | - | - | - | HC | DA6 | DA5 | DA4 | DA3 | DA2 | DA1 | DA0 | - | -   |

- 1. Bit 9 is HC bit. The setting is in the low current range when HC=0, and in the high current range when HC=1.

- 2. Bit 8 to bit 2 are DA6 ~ DA0.

The relationship between these bits and current gain G is:

HC = 1, D = (256G-128)/3

HC = 0, D = (1024G-128)/3

and D in the above decimal numeration can be converted to its equivalent in binary form by the following equation:

$D = DA6x2^{6} + DA5x2^{5} + DA4x2^{4} + DA3x2^{3} + DA2x2^{2} + DA1x2^{1} + DA0x2^{0}$

In other words, these bits can be looked as a floating number with 1-bit exponent HC and 7-bit mantissa DA6~DA0.

For example,

HC = 1, G = 1.25, D = (256x1.25-128)/3 = 64

the D in binary form would be:

$D = 64 = 1x2^{6} + 0x2^{5} + 0x2^{4} + 0x2^{3} + 0x2^{2} + 0x2^{1} + 0x2^{0}$

The bit 9 to bit 2 of the configuration register are set to 8'b1100,0000.

### 14 Delay time of staggered output

This feature prevents large inrush current from the power line and reduces the bypass capacitors.

The outputs are organized in four groups OUT4n, OUT4n+1, OUTn4+2, OUT4n+3 and each group has 40 ns delay between the previous one.

E.g.: OUT4n has no delay, OUTn4+1 has 40ns delay, OUTn4+2 has 80ns delay, OUTn4+3 has 120 ns delay.

## 15 Thermal protection

Thermal flag provides an indication about the status of the junction temperature. When the junction temperature reaches 150 °C the bit E of the configuration register is set to "1", signaling dangerous operating condition. This flag is useful when thermal shutdown function is disabled.

The thermal shutdown function, if activated by configuration register (bit "1" set to 1), turnsoff all output channels if the junction exceeds 150 °C. As soon as the junction temperature is below 140 °C the outputs channels will be turned ON. In thermal shutdown mode, the digital core is active and data flow is guaranteed.