Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **STV2050A**

# AUTOMATIC MULTISCAN DIGITAL CONVERGENCE PROCESSOR

- Multiscan 1H, 2H, HDTV and SVGA applications

- 6 Convergence channels

- 14-bit embedded DACs

- 1 Focus channel

- Second order interpolation in vertical direction

- Digital filtering in horizontal direction

- On-chip PLL

- On-chip video pattern generator

- Automatic compensation of temperature drift and aging of external components

- Pattern and synchronisation signals for optional optical sensor support

- Adjustable horizontal and vertical size

- Up to 7 different data sets

- Self-controlled power-on sequence

Figure 1. Functional Block Diagram

September 2003

# **Table of Contents** —

| 1 | GEN  | ERAL OVERVIEW                              | . 5 |

|---|------|--------------------------------------------|-----|

|   | 1.1  | SYSTEM BLOCK DIAGRAM                       | . 5 |

|   | 1.2  | DEVICE BLOCK DIAGRAM                       | . 6 |

|   | 1.3  | APPLICATION CIRCUIT                        | . 7 |

|   | 1.4  | PIN DESCRIPTION AND PINOUT DIAGRAM         | . 8 |

| 2 | STRU | JCTURE OF THE PROGRAMMING SYSTEM           | 11  |

|   |      | DATA STORAGE                               |     |

|   | 2.2  | OVERVIEW OF EMBEDDED RAM ORGANIZATION      | 12  |

|   | 2.3  | ADJUSTMENT DATA SETS                       | 13  |

| 3 | SLA\ | /E I <sup>2</sup> C BUS INTERFACE          | 14  |

|   | 3.1  | FEATURES                                   |     |

|   |      | 3.1.1 ADS0: IC Address and PLL Mode        |     |

|   |      | 3.1.2 SCLS Bus Clock                       |     |

|   |      | 3.1.3 SDAI Bus Data Input                  |     |

|   | 3.2  | 3.1.4 SDAO Bus Data Output                 |     |

|   |      | WRITE COMMANDS                             |     |

|   |      | READ COMMANDS                              |     |

|   |      | I <sup>2</sup> C I/O LINES                 |     |

| 4 |      | ALLOCATION                                 |     |

| • |      | CONVERGENCE CORRECTION VALUES              |     |

|   |      | 4.1.1 Dynamic Correction Values            |     |

|   |      | 4.1.2 Common Correction Values             |     |

|   | 4.2  | I <sup>2</sup> C REGISTERS                 | 18  |

|   |      | 4.2.1 Registers Storable in the EEPROM     |     |

| _ |      | 4.2.2 Registers Not Storable in the EEPROM |     |

| 5 |      | BASES                                      |     |

|   |      | LINE LOCKED PLL AND SYSTEM CLOCK           |     |

|   |      | SYNCHRONIZATION INPUTS                     |     |

|   | 5.3  | HORIZONTAL TIMEBASE                        |     |

|   |      | 5.3.1 Horizontal DAC Phase                 |     |

|   |      | 5.3.2 Horizontal Width Adjustment          |     |

|   | 5.4  | VERTICAL TIME BASE                         |     |

|   |      | 5.4.1 Vertical Synchronization Signal      |     |

| 1 |      | 5.4.2 Field Parity Recognition             |     |

|   |      | 5.4.3 Field Counter                        |     |

|   |      | 5.4.4 Convergence Correction Frame Retrace |     |

| 6 |      | TER I'C BUS INTERFACE                      |     |

|   | 6.1  | READ OPERATION MODES                       |     |

|   | 6.2  |                                            | _   |

|   |      | POWER-ON SEQUENCE                          |     |

|   |      | SECURITY FEATURE DURING DATA TRANFERS      |     |

|   | 6.5  | STATUS INFORMATION                         | 28  |

# Table of Contents

| 6.6   | DATA TRANSFER BETWEEN RAM AND EEPROM                | 29 |

|-------|-----------------------------------------------------|----|

| 6.7   | MASTER CLOCK FREQUENCY                              | 30 |

| 7 VID | EO PATTERN GENERATOR                                | 31 |

| 7.1   | GENERAL FUNCTIONS                                   | 32 |

|       | 7.1.1 Pattern Selection                             | 32 |

|       | 7.1.2 Pattern Visibility Adjustment                 | 33 |

| 7.2   | CROSS-HATCH GRID                                    | 34 |

|       | 7.2.1 Horizontal Grid Adjustment                    | 34 |

|       | 7.2.2 Vertical Grid Adjustment                      |    |

| 7.3   | CURSOR                                              |    |

|       | 7.3.1 Cursor Size                                   |    |

|       | 7.3.2 Cursor Position                               |    |

| 7.4   | BORDER LINES                                        |    |

|       | 7.4.1 Border Lines: Left / Right                    |    |

| 7.5   | 7.4.2 Border Lines: Bottom / Top                    |    |

| 7.5   | GAIN ADJUSTMENT LINES                               |    |

|       | 7.5.1 Video Pattern for Horizontal Gain Cursor      |    |

| 7.6   | AUTO-ALIGNMENT PATTERN                              |    |

|       | NKING OF VIDEO SIGNALS                              |    |

|       | HORIZONTAL BLANKING                                 |    |

|       | VERTICAL BLANKING                                   |    |

|       | BLANKING FOR AUTO-ALIGNMENT PATTERN                 |    |

|       | FAST BLANKING                                       |    |

|       |                                                     |    |

|       | NVERGENCE                                           |    |

| 9.1   | GLOBAL ADJUSTMENTS - COMMON PARAMETERS              |    |

|       | 9.1.1 Position Offset (also called "static")        |    |

|       | 9.1.2 Gain Correction                               |    |

| 92    | P DYNAMIC VALUES                                    |    |

|       | INTERLACE                                           |    |

|       | CALIBRATION                                         |    |

|       | INTERPOLATION                                       |    |

| 9.5   | 9.5.1 Vertical Filter                               |    |

|       | 9.5.2 Horizontal Filter                             |    |

| 9.6   |                                                     |    |

| 1     | MANUFACTURING, AFTER-SALES SERVICE, LAB TRIAL MODES |    |

| 0.7   | 9.7.1 Output of Field Offset Values                 |    |

|       | 9.7.2 Gain and Offset Measuring Line                |    |

|       | 9.7.3 Gain Cursor Mode                              |    |

|       | 9.7.4 Field Offset Cursor Mode                      |    |

| 9.8   | CONVERGENCE OUTPUTS                                 | 50 |

| 10 DY | NAMIC FOCUS                                         | 52 |

| 10.   | .1 PARABOLA CURVE                                   | 52 |

#### STV2050A -

| 10.2 FOCUS OUTPUTS                                          | 53 |

|-------------------------------------------------------------|----|

| 11 ELECTRICAL LOOP                                          | 54 |

| 11.1 PRINCIPLE OF OPERATION                                 | 54 |

| 11.2 LOOP PARAMETER REGISTER                                | 55 |

| 11.3 LOOP STATUS REGISTER                                   | 55 |

| 11.4 OPERATION OF THE ELECTRICAL LOOP                       | 56 |

| 11.5 OUTPUT/INPUT PADS                                      | 56 |

| 11.5.1PORA, PORB and PORC Pins                              | 56 |

| 11.5.2OGAH and OGAV Pins                                    |    |

| 12 OPTICAL LOOP                                             |    |

| 12.1 PRINCIPAL OF OPERATION                                 |    |

| 12.2 OPTT SENSOR PORT CONTROL                               | 58 |

| 12.2.1OPTT Pin used as an Input                             |    |

| 12.2.2OPTT Pin used as an Output                            |    |

| 12.3 OPTI SENSOR STATUS PORT                                |    |

| 13 CURRENT REFERENCE                                        |    |

| 14 SECURITIES                                               |    |

| 14.1 OVERVIEW                                               |    |

| 14.2 HAMMING ENCODING                                       |    |

| 14.3 SECURITY OUTPUT                                        |    |

| 15 BOOT SEQUENCE                                            |    |

| 16 IC STATUS REGISTERS                                      |    |

| 17 BUS EXPANDER                                             |    |

| 18 ABSOLUTE MAXIMUM RATINGS                                 |    |

| 19 RECOMMANDED OPERATING CONDITIONS                         |    |

| 20.1 GENERAL                                                |    |

| 20.2 CURRENT REFERENCE                                      |    |

| 20.3 VIDEO PATTERN OUTPUTS                                  |    |

| 20.3.1DACs for RGB                                          |    |

| 20.3.1 DACs for RGB                                         |    |

| 20.4 FOCUS DACS                                             |    |

| 20.4.1Focus Reference                                       |    |

| 20.4.2Focus Signal                                          |    |

| 20.5 CONVERGENCE DACS                                       |    |

| 20.6 PLL                                                    | 66 |

| 20.7 MASTER I <sup>2</sup> C TIME BASE                      | 66 |

| 20.8 HORIZONTAL AND VERTICAL SYNCHRONIZATION INPUTS         | 67 |

| 20.9 TBU OUTPUTS                                            | 67 |

| 20.10ELECTRICAL LOOP PADS                                   | 67 |

| 21 PACKAGE MECHANICAL DATA                                  |    |

| 22 ELECTRICAL PIN CONFIGURATION                             |    |

| 23 12C BUS REGISTER VARIABLE GLOSSARY AND REGISTER LOCATION |    |

| _ | _  |    | _ | _        | _ | _ |  |

|---|----|----|---|----------|---|---|--|

| _ | T۱ | 'n | n | <b>F</b> | n | Λ |  |

| _ | ·  | ız | u | - 1      | u | _ |  |

#### **1 GENERAL OVERVIEW**

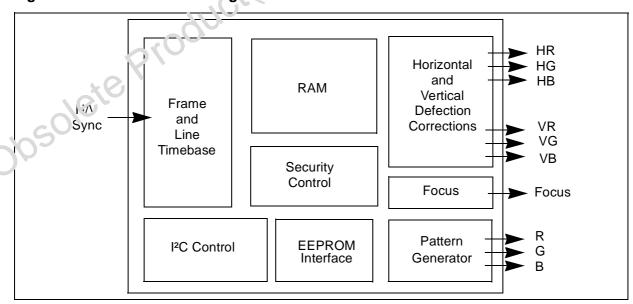

#### 1.1 SYSTEM BLOCK DIAGRAM

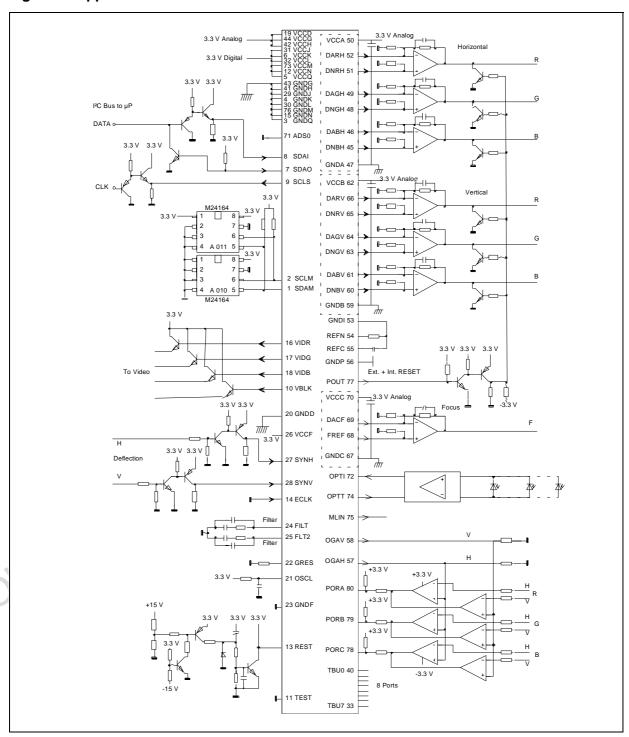

Figure 2. TV Set Convergence System Diagram

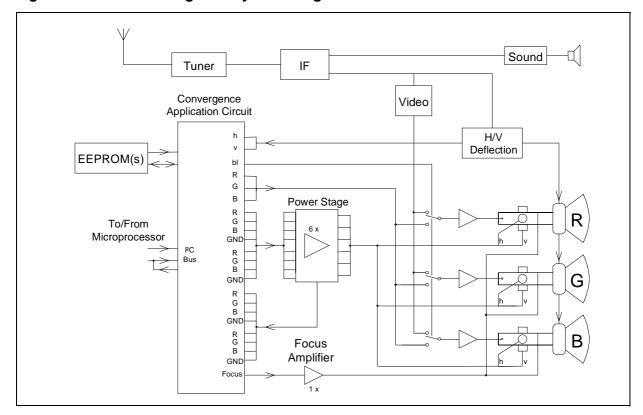

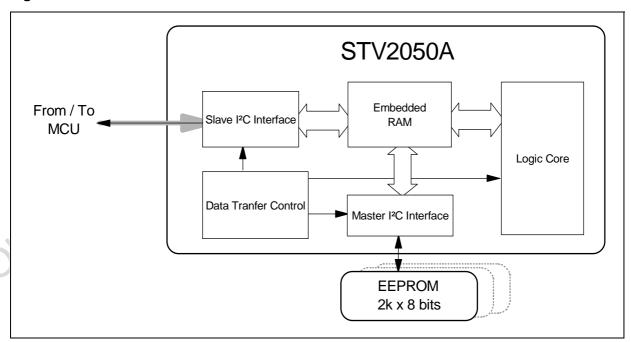

# 1.2 DEVICE BLOCK DIAGRAM

Figure 3. STV2050A Block Diagram

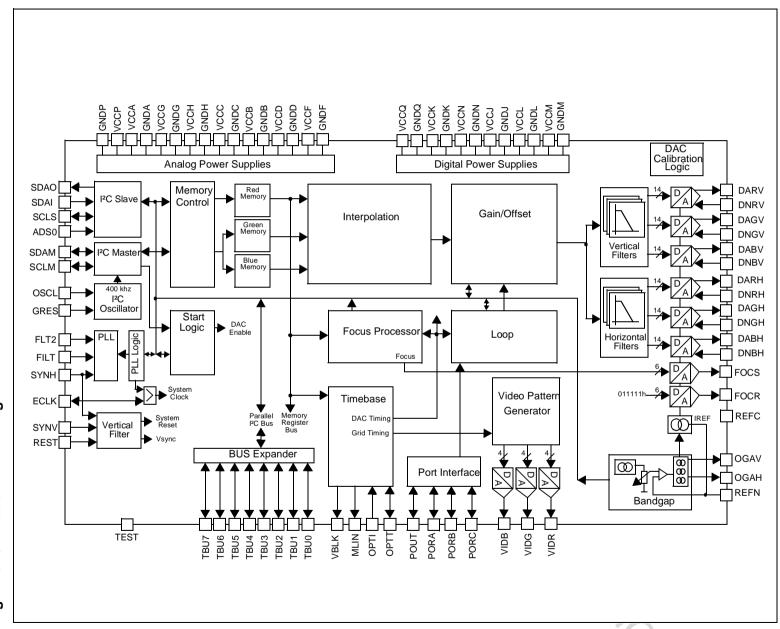

#### 1.3 APPLICATION CIRCUIT

An application circuit with 2nd EEPROM, Electrical Offset and Gain Adjustment Loop and Optical Sensors is shown in the following figure.

Figure 4. Application Circuit

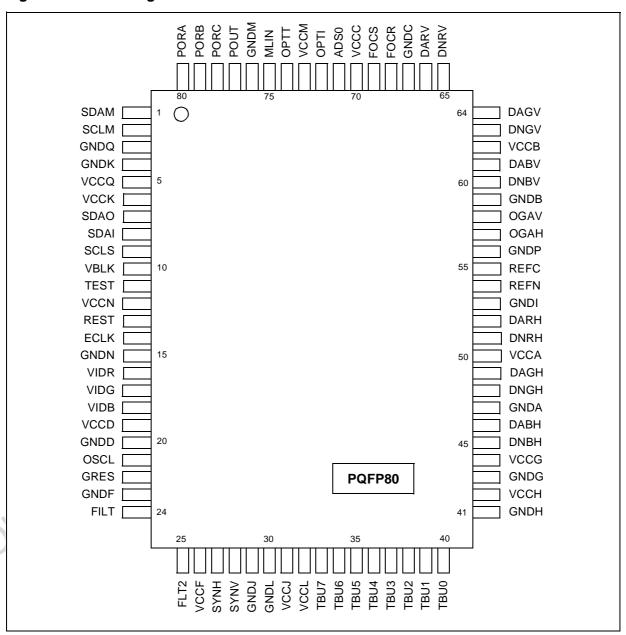

#### 1.4 PIN DESCRIPTION AND PINOUT DIAGRAM

The following legend applies to the Pin Description Table below:

X = Undefined HZ = High Impedance "0" = Low Level Output "1" = High Level Output

**Table 1. Pin Description**

| Pin No. | Pin Name | Reset Status and Remarks | Description                         |

|---------|----------|--------------------------|-------------------------------------|

| 1       | SDAM     | HZ                       | Master Bus: "Data"                  |

| 2       | SCLM     |                          | Master Bus: "Clock"                 |

| 3       | GNDQ     |                          | Digital Supply: Ground              |

| 4       | GNDK     |                          | Digital Supply: Ground              |

| 5       | VCCQ     |                          | Core / RAM Digital Supply: 3.3 V    |

| 6       | VCCK     |                          | Core / Digital Supply: 3.3 V        |

| 7       | SDAO     | "0"                      | Slave Bus: "Data" output            |

| 8       | SDAI     |                          | Slave Bus: "Data" input             |

| 9       | SCLS     |                          | Slave Bus: "Clock"                  |

| 10      | VBLK     |                          | Video Pattern Blanking              |

| 11      | TEST     | Must be grounded         | Reserved                            |

| 12      | VCCN     |                          | Shield Supply Digital Supply: 3.3 V |

| 13      | REST     | "0"                      | Reset                               |

| 14      | ECLK     | Must be grounded         | Reserved                            |

| 15      | GNDN     |                          | Digital Supply: "Ground"            |

| 16      | VIDR     | 0 Volts                  | Video Pattern Output: "Red"         |

| 17      | VIDG     | 0 Volts                  | Video Pattern Output: "Green"       |

| 18      | VIDB     | 0 Volts                  | Video Pattern Output: "Blue"        |

| 19      | VCCD     |                          | Video Generator Supply: 3.3 V       |

| 20      | GNDD     |                          | Video Generator Supply: Ground      |

| 21      | OSCL     | HZ                       | RC for internal oscillator          |

| 22      | GRES     | HZ                       | R for internal oscillator           |

| 23      | GNDF     |                          | PLL Supply: Ground                  |

| 24      | FILT     | HZ                       | Filter for PLL                      |

| 25      | FLT2     | HZ                       | Filter for PLL                      |

| 26      | VCCF     |                          | Supply PLL: 3.3 V                   |

| 27      | SYNH     |                          | Horizontal Synchronization input    |

| 28      | SYNV     |                          | Vertical Synchronization input      |

| 29      | GNDJ     |                          | Digital Supply: Ground              |

| 30      | GNDL     |                          | Digital Supply: Ground              |

| 31      | VCCJ     |                          | Core Digital Supply: 3.3 V          |

| 32      | VCCL     |                          | Ring / Buffer Digital Supply: 3.3 V |

| 33      | TBU7     | X                        | I <sup>2</sup> C BUS Expander       |

| 34      | TBU6     | Х                        | I <sup>2</sup> C BUS Expander       |

| 35      | TBU5     | Х                        | I <sup>2</sup> C BUS Expander       |

| 36      | TBU4     | Х                        | I <sup>2</sup> C BUS Expander       |

## **STV2050A - GENERAL OVERVIEW**

| Pin No. | Pin Name | Reset Status and Remarks         | Description                                                                                                           |

|---------|----------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| 37      | TBU3     | X                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 38      | TBU2     | X                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 39      | TBU1     | X                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 40      | TBU0     | X                                | I <sup>2</sup> C BUS Expander                                                                                         |

| 41      | GNDH     |                                  | Analog Supply: Ground                                                                                                 |

| 42      | VCCH     |                                  | D/A Interface Analog Supply: 3.3 V                                                                                    |

| 43      | GNDG     |                                  | Analog Supply: Ground                                                                                                 |

| 44      | VCCG     |                                  | Analog Supply: 3.3 V                                                                                                  |

| 45      | DNBH     | HZ                               | Horiz. Convergence Output: Blue, negative                                                                             |

| 46      | DABH     | HZ                               | Horiz. Convergence Output: Blue, positive                                                                             |

| 47      | GNDA     |                                  | Horiz. Convergence Output Supply: Ground                                                                              |

| 48      | DNGH     | HZ                               | Horiz. Convergence Output: Green, negative                                                                            |

| 49      | DAGH     | HZ                               | Horiz. Convergence Output: Green, positive                                                                            |

| 50      | VCCA     | HZ                               | Horiz. Convergence Output Supply: 3.3 V                                                                               |

| 51      | DNRH     | HZ                               | Horiz. Convergence Output: Red, negative                                                                              |

| 52      | DARH     | HZ                               | Horiz. Convergence Output: Red, positive                                                                              |

| 53      | GNDI     |                                  | Floating GND for bandgap filter                                                                                       |

| 54      | REFN     | Reference Current<br>Code 0(hex) | I <sub>REF</sub> Loop for H&V Convergence & Focus                                                                     |

| 55      | REFC     | Х                                | Filter pin for I <sub>REF</sub> current                                                                               |

| 56      | GNDP     |                                  | I <sub>REF</sub> GND for Bandgap                                                                                      |

| 57      | OGAH     | HZ                               | Horiz. Reference output for electrical loop                                                                           |

| 58      | OGAV     | HZ                               | Vert. Reference output for electrical loop                                                                            |

| 59      | GNDB     | HZ                               | Vert. Convergence Output Supply: Ground                                                                               |

| 60      | DNBV     | HZ                               | Vert. Convergence Output: Blue, negative                                                                              |

| 61      | DABV     | HZ                               | Vert. Convergence Output: Blue, positive                                                                              |

| 62      | VCCB     |                                  | Vert. Convergence Output Supply: 3.3 V                                                                                |

| 63      | DNGV     | HZ                               | Vert. Convergence Output: Green, negative                                                                             |

| 64      | DAGV     | HZ                               | Vert. Convergence Output: Green, positive                                                                             |

| 65      | DNRV     | HZ                               | Vert. Convergence Output: Red, negative                                                                               |

| 66      | DARV     | HZ                               | Vert. Convergence Output: Red, positive                                                                               |

| 67      | GNDC     |                                  | Focus Supply: Ground                                                                                                  |

| 68      | FOCR     |                                  | Focus Reference Output                                                                                                |

| 69      | FOCS     |                                  | Focus Signal Output                                                                                                   |

| 70      | VCCC     |                                  | Focus Supply                                                                                                          |

| 71      | ADS0     |                                  | I <sup>2</sup> C Slave Bus Address Selection                                                                          |

| 72      | OPTI     |                                  | Input for optical sensor support                                                                                      |

| 73      | VCCM     |                                  | Ring / Inputs Digital Supply: 3.3 V                                                                                   |

| 74      | OPTT     | Input                            | I pin: Latched at measuring line or with sys. clock;<br>O pin: Push/pull, output can be switched to high<br>impedance |

| 75      | MLIN     | "0"                              | Measuring Line Signal Output                                                                                          |

| 76      | GNDM     |                                  | Digital Supply: Ground                                                                                                |

| Pin No. | Pin Name | Reset Status<br>and Remarks | Description                                                                                      |

|---------|----------|-----------------------------|--------------------------------------------------------------------------------------------------|

| 77      | POUT     | HZ                          | Protection Pin Control                                                                           |

| 78      | PORC     |                             | Name allowed for all attitudes for all and a second                                              |

| 79      | PORB     | Input                       | Normally used for electrical loop feedback detection. Can also be set as an inpout or an output. |

| 80      | PORA     |                             | tion. Our also so set as an inpout of an output.                                                 |

Figure 5. Pinout Diagram

<u>57</u>

#### 2 STRUCTURE OF THE PROGRAMMING SYSTEM

#### 2.1 DATA STORAGE

The STV2050A is a programmable device. Some of the data, mainly the convergence parameters, must be able to be easily changed during TV set alignment or by the user, and must be memorized when the TV set is switched off in order to be recovered when switched back on. This data must therefore be stored in EEPROM.

The STV2050A has an **embedded RAM** for storing data used "in real time" at a high speed. In order to simplify the microcontroller software, and to ensure a quick startup, the STV2050A directly controls one or more (or up to seven) EEPROMs.

The STV2050A has 2 ports for I2C connections:

- The first one is used only for "SLAVE" connections: it is used to interface with a microcontroller in order to control the IC (customer adjustments,...). The microcontroller can write and read the embedded RAM via this slave port.

- The second one is used only for "MASTER" connections: it is used to interface the STV2050A with the EEPROM that stores the convergence data and some user adjustments.

The transfer of data between the EEPROM and the embedded RAM is fully managed by the STV2050A.

Figure 6. I<sup>2</sup>C BUS Data Transfer

#### 2.2 OVERVIEW OF EMBEDDED RAM ORGANIZATION

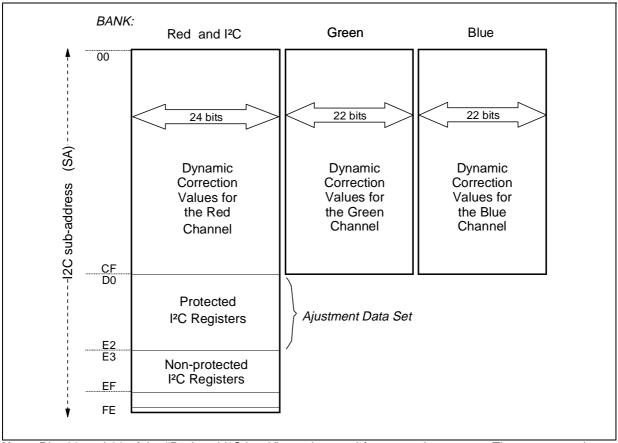

The RAM consists of 3 banks:

The first one, the "Red and I<sup>2</sup>C Bank", uses 24-bit words. The two other banks, the "Green Bank" and "Blue Bank", both use 22-bit words. Each bank has 208 words with addresses from 00(hex) to CF(hex).

These 3 x 208 words are allocated to the "dynamic" convergence parameters. (Refer to Section 4.1 "CONVERGENCE CORRECTION VALUES" on page 18.)

The "Red and I<sup>2</sup>C Bank" has 33 additional words: addresses from D0(hex) to EF(hex) and FE(hex). These words are used to buffer the I<sup>2</sup>C Bus registers.

As shown in this figure, each word can be pointed to by a sub-address (SA). Thus, each sub-address points to 24- (or 22-, depending on the bank) bit wide words. A word virtually consists of three bytes (24-bits) named D0, D1 and D2 as shown in the following figure. The bit order is named as follows: D0[7] is the MSB and D2[0] is the LSB

|     | M       | SB |   |   |   |   |   |         |   |   |   |   |   |   |   |         |   |   |   |   |   |   | LS | В |

|-----|---------|----|---|---|---|---|---|---------|---|---|---|---|---|---|---|---------|---|---|---|---|---|---|----|---|

|     | D0 Byte |    |   |   |   |   |   | D1 Byte |   |   |   |   |   |   |   | D2 Byte |   |   |   |   |   |   |    |   |

| Bit | 7       | 6  | 5 | 4 | 3 | 2 | 1 | 0       | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0 |

**Note**: Bit D0[7:6] is not physically implemented in the "Green" and "Blue" banks.

#### STV2050A - STRUCTURE OF THE PROGRAMMING SYSTEM

Figure 7. Color Banks

**Note:** Bits 22 and 23 of the "Red and I<sup>2</sup>C bank" may be used for general purposes. They are stored together with the convergence data in the external EEPROM.

#### 2.3 ADJUSTMENT DATA SETS

The set of data stored at addresses D0 to E2 is called an ADS (Adjustment Data Set).

The STV2050A can store up to three ADSs in one standard EEPROM. Refer to Section 6 "MASTER I<sup>2</sup>C BUS INTERFACE" on page 28.

#### 3 SLAVE I2C BUS INTERFACE

#### 3.1 FEATURES

The I2C interface is controlled by 4 pins:

#### 3.1.1 ADS0: IC Address and PLL Mode

The level at this pin corresponds to bit 1 in the first byte in bus transmissions.

- If ADS0 is connected to GND, the analog outputs will be automatically switched on after the reset sequence, and once the internal PLL is activated.

- If the pin is connected to VCC, the DACs will remain in high impedance. The internal PLL is inhibited, and the IC must use an external PLL.

#### 3.1.2 SCLS Bus Clock

The polarity and timing for this pin comply with I<sup>2</sup>C Bus specifications.

#### 3.1.3 SDAI Bus Data Input

The polarity and timing for this pin comply with I<sup>2</sup>C Bus specifications.

#### 3.1.4 SDAO Bus Data Output

The polarity reversal and timing for this pin comply with I<sup>2</sup>C Bus specifications.

Abbreviations used:

S = Start condition

P = Stop condition

DA = Device address

DR = Device address for read

DW = Device address for write

SA = Sub-address

D0, D1,... Dn= Data bytes

The slave accepts the following DA subaddresses depending on the hardware configuration defined on pin ADS0.

| ADS0 0 (grounded, international 1 (3.3 Volt, externational 2) | nal PLL only) DR = 39, DW = 38<br>Il PLL only) DR = 3B, DW = 3A |

|---------------------------------------------------------------|-----------------------------------------------------------------|

|---------------------------------------------------------------|-----------------------------------------------------------------|

For the 00 to CF address range (RAM), an autoincrement function can be enabled using the AIE (Auto Increment Enable) bit in the E7 register.

| AIE | 0 = Autoincrement disabled<br>1 = Autoincrement enabled |

|-----|---------------------------------------------------------|

|-----|---------------------------------------------------------|

#### STV2050A - SLAVE I2C BUS INTERFACE

If the autoincrement function is enabled, the internal address is automatically incremented after 3 bytes are either written or read. When the autoincrement counter reaches the CF address, the counter stops counting and any additional data will be written to or read from the CF address.

#### 3.2 COLOR BANK SELECTION

As previously mentioned, the embedded RAM is mapped in 3 banks called the "Red and I<sup>2</sup>C Bank", "Green Bank" and the "Blue Bank". A bank is selected using the CBS[1:0] (Color Bank Selection) bits located in the E7 register address.

| CBS[1:0] | 00 = Red and I <sup>2</sup> C bank selected<br>01 = Green bank selected<br>10 = Blue bank selected<br>11 = Red and I <sup>2</sup> C bank selected |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|

However, sub-addresses D0 to EF and FE (physically mapped in the "Red and I<sup>2</sup>C Bank") are independent of the actual bank selection.

#### 3.3 WRITE COMMANDS

Three formats of write commands are supported:

- 5-byte write commands to any valid sub-address

S DW SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at SA+1 after the command, otherwise it is still at SA.

2-byte write commands for defining a sub-address cursor position or for changing the current sub-address without transmitting data.

S DW SA P

The sub-address is at SA after the command.

- Auto-increment write commands for sub-address range 00 to CF

If the auto-increment function is enabled, the internal address counter is incremented each time 3 bytes are written:

S DW SA<sub>i</sub> D<sub>i</sub>0 D<sub>i</sub>1 D<sub>i</sub>2 D<sub>i+1</sub>0 D<sub>i+1</sub>1 D<sub>i+1</sub>2... Dn P

otherwise every group of 3 bytes is written to SA and the sub-address does not change.

When a group of three data bytes within the 00 to E2 address range has been received, the slave will store them in the appropriate embedded RAM location. Only complete groups of three data bytes are stored. I<sup>2</sup>C registers start to be updated when the first data byte is received. Only complete bytes are written.

All write commands which do not comply with the formats described above are rejected.

#### 3.4 READ COMMANDS

Read commands may access the IC internal RAM as well as all I<sup>2</sup>C registers. Read commands in the 00 to CF range read from the RAM bank that is defined by the two CBS bits that have been previously transmitted to the E7 register by a write command.

Addresses in the D0 to E2 range are mapped to the corresponding section of the red color RAM if the RRP bit in the EF register is '0'. Otherwise the corresponding internal register values are transmitted.

If the SA is in the 00 to CF address range, the position of the cursor is implicitly defined by the SA. An access to any other SAs will switch off the cursor. It will be switched on again if an address in the 00 to CF range is selected.

Three formats of read commands are supported:

#### - Random read commands from any valid IC internal address

S DW SA S DR SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at the SA+1 after the command, otherwise it is still at the SA.

#### - Read commands from the actual internal address

S DR SA D0 D1 D2 P

If the auto-increment function is enabled, the internal address is at the SA+1 after the command, otherwise it is still at the SA.

#### Auto-increment read commands from addresses within the 00 to CF address range with random start address.

S DW SA S DR SA D0 D1 D2..... Dn P

If the auto-increment function is enabled, the internal address counter is incremented after 3 bytes are read, otherwise the SA is always read and the internal address does not change.

When the last byte of the CF address has been transmitted, the IC internal auto-increment address counter stops counting and the CF value will be read out again.

#### 3.5 I2C I/O LINES

Digital filters suppress pulses that are less than 1 or 2 clock pulses at the SDAI and SCLS inputs.

#### **4 RAM ALLOCATION**

#### **4.1 CONVERGENCE CORRECTION VALUES**

The convergence correction values are either dedicated to each correction point of each red/blue/green channel, or common for all points of each channel. (Refer to Section 9 "CONVERGENCE" on page 45.)

The values are grouped into 2 families:

- Dynamic correction values

- Common correction values

#### 4.1.1 Dynamic Correction Values

The dynamic values are stored as described in Section 2.2 "Overview OF EMBEDDED RAM ORGANIZATION" on page 13.

For each Red, Green and Blue channel, the following can be stored in the embedded RAM:

- 13 horizontal "dynamic" correction values on 10 bits, plus 1 parity bit

- Up to 16 vertical "dynamic" correction values on 10 bits, plus 1 parity bit

For each correction point there is one corresponding word in the 00(hex) to CF(hex) sub-address range. Bits are stored in the corresponding "Red Bank", "Green Bank" and "Blue Bank" as follows:

|     | M       | ISB                     |   |   |   |   |   |   |         |   |   |   |   |   |   |   |         |       |    |      |       |      | LS | SB |

|-----|---------|-------------------------|---|---|---|---|---|---|---------|---|---|---|---|---|---|---|---------|-------|----|------|-------|------|----|----|

|     | BYTE D0 |                         |   |   |   |   |   |   | BYTE D1 |   |   |   |   |   |   |   | BYTE D2 |       |    |      |       |      |    |    |

| Bit | 7       | 6                       | 5 | 4 | 3 | 2 | 1 | 0 | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 7       | 6     | 5  | 4    | 3     | 2    | 1  | 0  |

|     |         | Horizontal Correction[9 |   |   |   |   |   |   |         |   |   |   |   |   |   |   | Ver     | tical | Со | rrec | tion[ | 9:0] |    |    |

- Bit D1[3] is the horizontal correction parity bit

- Bit D1[2] is the vertical correction parity bit

- Bits D1[3:2] are generated by the STV2050A. Their value can be read out only.

**Note**: The STV2050A automatically checks the parity bits of each convergence value before applying them to the DACs. Refer to Section 14 "SECURITIES" on page 62.

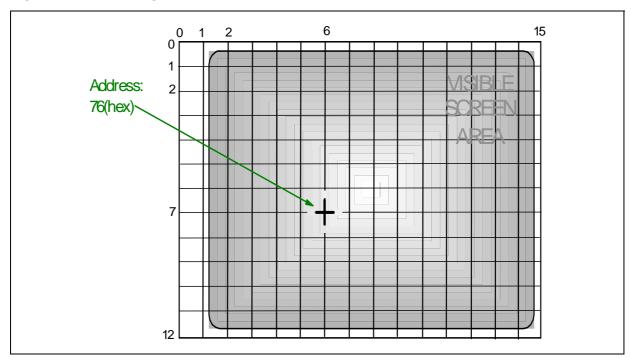

The sub-address corresponds to the coordinates of the point on the screen where the vertical and horizontal lines meet, as shown in the following figure:

Figure 8. Addressing a Correction Point

#### **4.1.2 Common Correction Values**

The common correction values are stored in the "adjustment data sets" of the Red and I<sup>2</sup>C channel. See Figure 7 "Color Banks" on page 14 and Section 9.1 "GLOBAL ADJUSTMENTS - COMMON PARAMETERS" on page 45.

#### 4.2 I2C REGISTERS

All I<sup>2</sup>C registers are implemented in the "Red and I<sup>2</sup>C Bank" of the embedded RAM. As it can be useful to store some of the I<sup>2</sup>C register content in the EEPROM, the embedded RAM allocation is divided into two parts:

- From sub-address D0 to E2 (included), contents can be stored in the EEPROM, and can then be restored.

- From sub-addresses E3 to EF and FE, contents are lost when the STV2050A is switched off.

# **4.2.1 Registers Storable in the EEPROM**

|    | М                     | MSB              |                   |                  |                   |                   |          |         |          |            |          |                   |          |           |                  |           |               |                   |     |       |        |       |   |   |

|----|-----------------------|------------------|-------------------|------------------|-------------------|-------------------|----------|---------|----------|------------|----------|-------------------|----------|-----------|------------------|-----------|---------------|-------------------|-----|-------|--------|-------|---|---|

|    | BYTE D0               |                  |                   |                  |                   |                   | BYTE D1  |         |          |            |          |                   |          |           | BYTE D2          |           |               |                   |     |       |        |       |   |   |

| SA | 7                     | 6                | 5                 | 4                | 3                 | 2                 | 1        | 0       | 7        | 6          | 5        | 4                 | 3        | 2         | 1                | 0         | 7             | 6                 | 5   | 4     | 3      | 2     | 1 | 0 |

| D0 |                       |                  |                   | RFH              | [7:0]             |                   |          |         | GFH[7:0] |            |          |                   |          |           |                  |           |               | !                 | BFH | [7:0] |        |       |   |   |

| D1 |                       |                  |                   | RFV              | [7:0]             |                   |          |         | GFV[7:0] |            |          |                   |          |           |                  |           |               |                   |     | BFV   | [7:0]  |       |   |   |

| D2 |                       |                  |                   | ORH              | [7:0]             |                   |          |         |          |            |          | OGF               | I[7:0]   |           |                  |           |               |                   | (   | OBH   | l[7:0] |       |   |   |

| D3 |                       |                  |                   | ORV              | [7:0]             |                   |          |         |          |            |          | OGV               | /[7:0]   |           |                  |           |               |                   | (   | OBV   | [7:0]  |       |   |   |

| D4 | х                     | PD<br>C          | PD<br>B           | PD<br>A          | х                 | PO<br>C           | PO<br>B  | PO<br>A | Х        | PL<br>T    | GO<br>S  | HV<br>M           | G/<br>[1 | AV<br>:0] | G/<br>[1         | ΑΗ<br>:0] | Х             | Х                 | Х   | Х     | Х      | Х     | Х | Х |

| D5 | PR<br>S               | 0                | AM<br>S[0         | M<br>[0 BGA[4:0] |                   |                   | PM<br>H  | PM<br>V | Х        | x x x x ML |          |                   |          |           | MLN[8:0]         |           |               |                   |     |       |        |       |   |   |

| D6 |                       | PBH              | PBH[3:0] PBV[3:0] |                  |                   |                   | HB<br>E  | HA<br>E | HVB[5:0] |            |          |                   |          | VB<br>E   | VB VA E VVB[5:0] |           |               |                   |     |       |        |       |   |   |

| D7 | х                     |                  | HGP[6:0]          |                  |                   |                   |          |         | TV<br>H  | TV<br>V    | BPH[5:0] |                   |          |           |                  | FA<br>S   | A ST BPV[5:0] |                   |     |       |        |       |   |   |

| D8 | AC<br>W               | х                |                   | HGD[5:0]         |                   |                   |          |         | ACL      | [1:0<br>]  | HRD[5:0] |                   |          |           |                  | AFS       | [1:0<br>]     | ASP[2:0] FS HIF[1 |     |       |        | [1:0] |   |   |

| D9 | VGP[7:0]              |                  |                   |                  |                   | VG<br>P           | VF<br>P  |         | VGD[5:0] |            |          |                   |          | VFP[7:0]  |                  |           |               |                   |     |       |        |       |   |   |

| DA | IIE                   | E IFA x ICV[5:0] |                   |                  |                   |                   | VST[7:0] |         |          |            |          |                   |          | FSB[7:0]  |                  |           |               |                   |     |       |        |       |   |   |

| DB | DC<br>T[8] HDP[6:0]   |                  |                   |                  |                   | DCT[7:0]          |          |         |          |            |          |                   | DCB[7:0] |           |                  |           |               |                   |     |       |        |       |   |   |

| DC | CRH[7:0]              |                  |                   |                  |                   | CGH[7:0]          |          |         |          |            |          |                   | CBH[7:0] |           |                  |           |               |                   |     |       |        |       |   |   |

| DD | CRV[7:0]              |                  |                   |                  |                   | CGV[7:0]          |          |         |          |            |          |                   | CBV[7:0] |           |                  |           |               |                   |     |       |        |       |   |   |

| DE | FV1[5:0]              |                  |                   |                  | FV2[5:0] FV3[5:0] |                   |          |         |          |            | [5:0]    | FVR[5:0]          |          |           |                  |           |               |                   |     |       |        |       |   |   |

| DF | OL GL FIN DI DI X X X |                  |                   | NOM[7:0]         |                   |                   |          |         |          |            | TOL[7:0] |                   |          |           |                  |           |               |                   |     |       |        |       |   |   |

| E0 | RCH[3:0] RCV[3:0]     |                  |                   |                  |                   | GCH[3:0] GCV[3:0] |          |         |          |            |          | BCH[3:0] BCV[3:0] |          |           |                  |           |               |                   |     |       |        |       |   |   |

| E1 | SRH[7:0]              |                  |                   |                  |                   | SGH[7:0]          |          |         |          |            |          |                   | SBH[7:0] |           |                  |           |               |                   |     |       |        |       |   |   |

| E2 | SRV[7:0]              |                  |                   |                  |                   | SGV[7:0]          |          |         |          |            |          |                   | SBV[7:0] |           |                  |           |               |                   |     |       |        |       |   |   |

## 4.2.2 Registers Not Storable in the EEPROM

|     | N        | MSB           |                 |         |         |         |            |                      |                                |                    |         |         |          |              |                   |           |         |         |          |          |         |     | LS  | ЗB      |

|-----|----------|---------------|-----------------|---------|---------|---------|------------|----------------------|--------------------------------|--------------------|---------|---------|----------|--------------|-------------------|-----------|---------|---------|----------|----------|---------|-----|-----|---------|

|     | BYTE D0  |               |                 |         |         |         |            | BYTE D1              |                                |                    |         |         |          |              |                   | BYTE D2   |         |         |          |          |         |     |     |         |

| ADD | 7        | 6             | 5               | 4       | 3       | 2       | 1          | 0                    | 7                              | 6                  | 5       | 4       | 3        | 2            | 1                 | 0         | 7       | 6       | 5        | 4        | 3       | 2   | 1   | 0       |

| E3  | ST<br>L  | Х             | Х               | GC<br>D | DH<br>V | PP<br>L | CD<br>O    | CD<br>N              | STV2050A code = 30(hex)        |                    |         |         |          | S0<br>1      | S1<br>9           | R         | ESE     | RVED    |          | S0<br>2  | S0<br>3 |     |     |         |

| E4  | Х        | PD<br>C       | PD<br>B         | PD<br>A | Х       | PO<br>C | PO<br>B    | PO<br>A              | Х                              | PL<br>T            | GO<br>S | HV<br>M | G/<br>[1 | 4V<br>:0]    | G/<br>[1          | ΑΗ<br>:0] | S0<br>1 | S1<br>9 | MS<br>Y  | EL<br>O  | Х       | PIC | PIB | PIA     |

| E5  | OP<br>I  | OD<br>S       | 00<br>S         | OD<br>T | Х       | Х       | Х          | Х                    | S09 [3:0] S10 [3:0] S0 S1 S0 S |                    |         |         |          | S1<br>1      | S12 [3:0]         |           |         |         |          |          |         |     |     |         |

| E6  | Х        | Х             | Х               | Х       | Х       | Х       | Х          | Х                    | S13[7:0] S14[7:0]              |                    |         |         |          |              |                   |           |         |         |          |          |         |     |     |         |

| E7  | AIE      | Х             | Х               | Х       | Х       | Х       | CI<br>[1   | 3S<br>:0]            | Х                              | Х                  | Х       | Х       | Х        | Х            | Х                 | Х         | Х       | Х       | Х        | Х        | Х       | Х   | Х   | TE<br>1 |

| E8  | MVR[7:0] |               |                 |         |         |         | MVG[7:0]   |                      |                                |                    |         |         |          | MVB[7:0]     |                   |           |         |         |          |          |         |     |     |         |

| E9  |          | EPRO<br>dd [2 |                 |         |         |         | S[1:0<br>] | RWM [2:0] X HAM[3:0] |                                |                    |         |         |          | S0<br>1      | S1                |           |         |         | STX[3:0] |          |         |     |     |         |

| EA  | Х        | Х             | Х               | Х       | VD<br>C | C       | OV[2       | :0]                  | GC<br>P                        | GC VH X PAS[4:0] X |         |         |          | Х            | Х                 | Х         | Х       | Х       | Х        | Х        |         |     |     |         |

| EB  | Х        | Х             | HO1 [5:0]       |         |         |         |            | HG1[3:0] X X         |                                |                    |         |         |          |              | HO2               | [5:0]     |         |         | HG2[3:0] |          |         |     |     |         |

| EC  | Х        | Х             | VO1[5:0]        |         |         |         |            | VG1[3:0]             |                                |                    |         | Х       | Х        |              | VO2[5:0] VG2[3:0] |           |         |         |          |          |         |     |     |         |

| ED  | Х        | Х             | HO3[5:0]        |         |         |         |            | HG3[3:0]             |                                |                    |         | Х       | Х        |              | HO4[5:0] HG4[3:0] |           |         |         |          | [3:0]    |         |     |     |         |

| EE  | Х        | Х             | VO3[5:0]        |         |         |         |            | VG3[3:0]             |                                |                    |         | Х       | Х        | VO4[5:       |                   |           | [5:0]   |         |          | VG4[3:0] |         |     |     |         |

| EF  | Х        | Х             | Х               | Х       | Х       | RU<br>E | RU<br>1    | RU<br>2              | Х                              | Х                  | Х       | Х       | TE<br>2  | TE<br>3      | TE<br>4           | RR<br>P   | Х       | Х       | Х        | х        | Х       | Х   | 0   | 0       |

| FE  | Х        | SS<br>E       | SS DT 0 0 0 0 0 |         |         |         | 0          | 0                    | 0                              | 0                  | 0       | 0       | 0        | 0 0 TBU[7:0] |                   |           |         |         |          |          |         |     |     |         |

**Note**: X = Don't care, 0 or 1: The corresponding bit MUST be set to this value for normal operation.

#### **5 TIMEBASES**

#### 5.1 LINE LOCKED PLL AND SYSTEM CLOCK

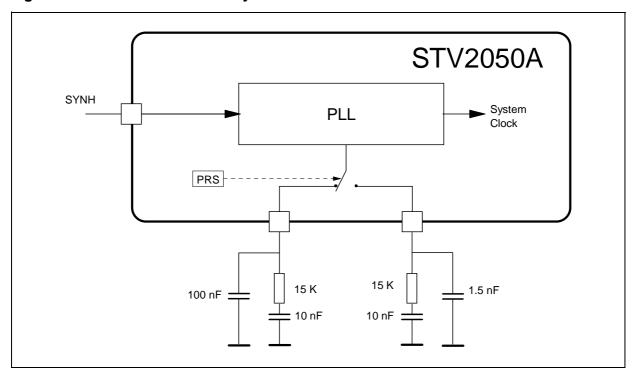

A frequency-multiplying PLL derives the internal *system clock* from the incoming signal at the SYNH pin. This signal is derived from horizontal deflection.

Figure 9. Line-Locked PLL and System Clock

The PLL is designed to drive 1H, 2H, HDTV and SVGA applications. Two loop filters can be implemented using the FILT (pin 24) and FLT2 (pin 25) pads. The selection can be forced by the PRS bit in the D5 register.

| PRS  0 = FILT selected (2H and above range operation recommende 1 = FLT2 selected (1H range operation recommended) | d) |

|--------------------------------------------------------------------------------------------------------------------|----|

|--------------------------------------------------------------------------------------------------------------------|----|

The horizontal deflection is often turned off when switching TV set modes. Therefore the PLL provides a base frequency when the external sync signal is missing (both H and V sync signals are missing).

The  $N_{(clk/line)}$  ratio between the system clock and the incoming sync signal is calculated using the HGD[5:0] and HRD[5:0] values in the D8 register. (Refer to Section 7.2.1 "Horizontal Grid Adjustment" on page 35):

$$N_{(clk/line)} = 14*(HGD+1) + 2*(HRD+1)$$

where:

$$N_{(clk/line)} < 512$$

$$HGD > 15$$

$$HRD > 15$$

For all modes, in normal operation, the incoming timing signal at the SYNH pin will not have a phase deviation greater than  $\pm$  2 µs from line to line. Greater phase deviations may occur when switching modes or changing channels. The PLL is expected to recover from these events and lock within one vertical field of consistent phase that is within the normal horizontal operation limits.

#### **5.2 SYNCHRONIZATION INPUTS**

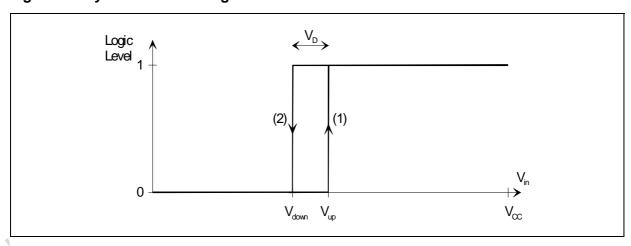

The two synchronization inputs, SYNH (pin 27) and SYNV (pin 28) slice the Line or the Frame Flyback, respectively, via a Schmitt trigger.

This also ensures a very stable detection of the synchronization signals, regardless of the temperature.

Figure 10. Synchronisation Signals

#### **5.3 HORIZONTAL TIMEBASE**

The horizontal timing is based on the built-in PLL.

#### 5.3.1 Horizontal DAC Phase

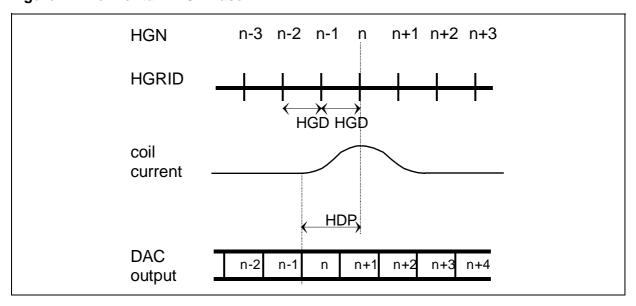

In order to compensate the delay of the external amplifiers and the response time of the convergence coils (t<sub>d</sub>), the values for convergence correction are given out prior to the corresponding horizontal video position. The time delay between video position and the output of

#### STV2050A - TIMEBASES

the corresponding convergence correction value is defined by the Horizontal DAC phase HDP[6:0] value in the DB register.

The following range for the horizontal DAC phase is allowed:

$$0 \le HDP \le 2 \times HGD$$

The timing of the DAC output leads the most if HDP is equal to zero.

Figure 11. Horizontal DAC Phase

#### 5.3.2 Horizontal Width Adjustment

In order to fit the video pattern into the full visible area of the screen, the width of the pattern may be adjusted. Horizontal width adjustment is done by changing the number of clock cycles between the vertical grid lines during retrace and the visible grid. The timing for the corresponding DAC values is changed accordingly. Refer to Section 7.2.1 "Horizontal Grid Adjustment" on page 35.

#### 5.3.3 Auto-Calibration of DACs

All the DACs of the STV2050A can be automatically calibrated. This feature ensures a high matching stability in both time and temperature. The process involves the sequential calibration of 120 cells.

To ensure optimal results, each cell must be calibrated at least every 4 ms.

The duration of one cell calibration must be greater than 2us. This duration is controlled by the internal "calibration clock". The calibration clock is generated using a divider of the system clock. (Refer to Section 5.1 "LINE LOCKED PLL AND SYSTEM CLOCK" on page 22). The division ratio is programmable via the ACL[1:0] bits in D8.

| ACL[1:0] | 00: No calibration 01: Division by 16 10: Division by 32 11: Division by 48 |

|----------|-----------------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------------|

Autocalibration can take place either during the full line, or during the line retrace only. This is controlled by the ACW bit in the D8 register.

| ACW 0: During line retrace only 1: During the full line |  |

|---------------------------------------------------------|--|

|---------------------------------------------------------|--|

If the "During Line Retrace Only" autocalibration is selected, the number of DAC cells calibrated during each line retrace is defined by the AFS[1:0] value in the D8 register.

| AFS[1:0] | 00: 1 cell / line<br>01: 2 cells / line<br>10: 3 cells / line |

|----------|---------------------------------------------------------------|

|          | 11: 4 cells / line                                            |

Two autocalibration modes can be selected by the AMS[0] bit in the D5 register.

| AMS[0] | 0: The autocalibration process is not synchronized to vertical timing<br>1: The autocalibration is synchronized to vertical IC timing. The counter<br>which selects the DAC cells that are to be calibrated is reset on each<br>frame retrace. |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

The time interval for auto-calibration is normally centred to the retrace. But it is possible to adjust the start point by programming the ASP[2:0] bits in the D8 register. One step corresponds to one system clock cycle.

#### **5.4 VERTICAL TIME BASE**

#### 5.4.1 Vertical Synchronization Signal

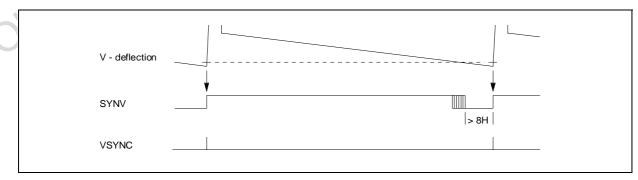

The vertical timing is based on the vertical deflection signal. A debounce filter is implemented to prevent interference on the SYNV signal caused by crosstalk, mainly from horizontal deflection. This filter accepts a rising edge of the SYNV signal only when SYNV is 'LOW' for a time  $\geq$  8 TV lines (determined by 8 pulses at the SYNH input).

Figure 12. Vertical Synchronization Signal

<u> 57</u>