# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## SX1230 - Integrated Transmitter IC

#### Narrow/wideband 315 MHz, 434 MHz 868 MHz and 915 MHz band Transmitter

#### **GENERAL DESCRIPTION**

The SX1230 is a fully integrated transmitter which can operate in the 315, 434, 868 and 915 MHz licence free ISM bands.

The transmitter has two modes of operation, a conventional MCU controlled mode and a 'stand-alone' mode which enables the SX1230 to download configuration and messages from an  $E^2$ PROM in response to a user input.

Stand-alone mode makes the SX1230 ideal for miniaturized or low cost remote keyless entry (RKE) applications. It also offers the unique advantage of narrow-band and wide-band communication in a range of modulation formats.

The SX1230 offers high RF output power and channelized operation suited for the European (ETSI EN 300-220-1), North American (FCC part 15.231, 15.247 and 15.249) and Japanese (ARIB T-67) regulatory standards.

#### **ORDERING INFORMATION**

| Part Number   | Temperature Range | Qty. per Reel | Package         |

|---------------|-------------------|---------------|-----------------|

| SX1230I066TRT | -40 °C to +85 °C  | 3000          | MLPQ-24 (4x4mm) |

Pb-free, Halogen free, RoHS/WEEE compliant product MLPQ-24 4x4mm Package - Operating Range [-40;+85°C]

#### APPLICATIONS

- Remote Keyless Entry (RKE)

- Remote Control / Security Systems

- Voice and Data RF Communication Links

- Process and building / home control

- Active RFID

- AMR / AMI Platforms

#### **KEY PRODUCT FEATURES**

- +17 dBm to -18 dBm Programmable output power.

- Bit rates up to 600 kbits / sec.

- FSK, GFSK, MSK, GMSK and OOK modulation.

- Stand-alone mode: No need for a host MCU.

- Consistent RF performance over a 1.8 to 3.7 V range.

- Low phase noise (-95 dBc/Hz at 50 kHz) with automated PLL calibration and fully integrated VCO and loop filter.

- On chip RC timer for timer / wake-up applications.

- Low battery detection.

### Table of contents

#### Section

| 1. | Genera   | I Description                           | 4  |

|----|----------|-----------------------------------------|----|

|    | 1.1. Sir | mplified Block Diagram                  | 4  |

|    | 1.2. Pir | n Diagram                               | 5  |

|    | 1.3. Pii | n Description                           | 6  |

| 2. | Electric | al Characteristics                      | 7  |

|    | 2.1. ES  | SD Notice                               | 7  |

|    | 2.2. Ab  | solute Maximum Ratings                  | 7  |

|    | 2.3. Op  | perating Range                          | 7  |

|    | 2.4. Ele | ectrical Specifications                 | 8  |

| 3. | Timing   | Characteristics                         | 9  |

| 4. | Working  | g Modes of the SX1230                   | 10 |

|    | 4.1. Op  | perating Modes                          | 10 |

|    | 4.2. Ap  | plication Modes                         | 10 |

|    | 4.2.1.   | Stand Alone Mode                        | 10 |

|    | 4.2.2.   | MCU Mode                                | 11 |

| 5. | Operati  | on of the SX1230                        | 12 |

|    | 5.1. Ma  | ain Parameters                          | 12 |

|    | 5.1.1.   | Center Frequency                        | 12 |

|    | 5.1.2.   | Frequency Deviation                     | 12 |

|    | 5.1.3.   | Bit Rate                                | 12 |

|    | 5.2. Sy  | nthesizer                               | 13 |

|    | 5.3. Th  | e Power Amplifier                       | 14 |

| 6. |          | Control and Interface                   |    |

|    | •        | and Alone Mode                          |    |

|    | 6.1.1.   | State Machine Description               |    |

|    | 6.1.2.   | Memory Organization of the E2PROM       |    |

|    | 6.1.3.   | Periodic mode                           |    |

|    | 6.1.4.   | Low Battery Indicator: Stand Alone Mode |    |

|    | 6.1.5.   | Low Battery Indicator: MCU Mode         |    |

|    |          | CU Mode                                 |    |

|    | 6.2.1.   | SPI Operation                           |    |

|    | 6.2.2.   | Data and Data Clock Usage               |    |

|    |          | X1230 Register Description              |    |

| 7. |          | O Application Circuits                  |    |

|    | 7.1. SX  | (1230 E2PROM Mode Application Circuit   | 27 |

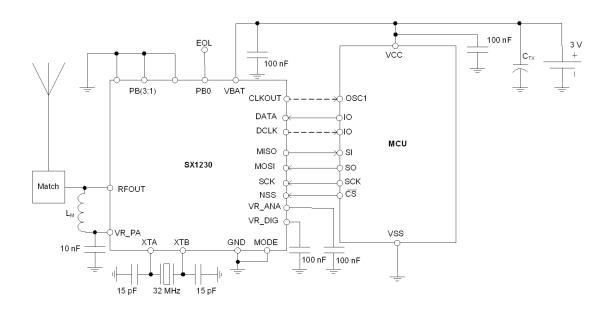

|    | 7.2. SX  | (1230 MCU Mode Application Circuit      | 28 |

|    | 7.3. Co  | mplete RKE Application Circuit          |    |

|    |          |                                         |    |

# SX1230

DATASHEET

#### Page

#### Table of contents

#### Section

| -   | 7.4. | Wake-up Times                                               | 29  |

|-----|------|-------------------------------------------------------------|-----|

| -   | 7.5. | Reset Pin Timing                                            | 29  |

| -   | 7.6. | Operation with 17 dBm Output Power                          |     |

| -   | 7.7. | Matching for 13 dBm Output Power and Below                  | 33  |

| -   | 7.8. | TCXO Connection                                             | 34  |

| -   | 7.9. | PCB Layout Considerations                                   | 34  |

| 8.  | Refe | erence Design                                               |     |

| 9.  | Refe | erence Design Performance                                   | 36  |

| ę   | 9.1. | Power Output versus Consumption                             | 36  |

| ę   | 9.2. | Power Output Flatness versus Temperature and Supply Voltage | 37  |

| 9   | 9.3. | Phase Noise                                                 | .38 |

| ę   | 9.4. | SX1230 Baseband Filtering                                   | .40 |

| 9   | 9.5. | Adjacent Channel Power                                      |     |

| 10. | Pac  | kaging Information                                          | .43 |

| 11. | Pac  | kage Marking                                                | .43 |

| 12. |      | ommended PCB Land Pattern                                   |     |

| 13. | Sold | ering Profile                                               | 45  |

# SX1230

# DATASHEET

Page

#### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

This product datasheet contains a detailed description of the SX1230 performance and functionality. Please consult the Semtech website for the latest updates or errata (www.semtech.com).

#### 1. General Description

The SX1230 is a multi-band, single chip transmitter IC capable of (G)FSK, (G)MSK, and OOK modulation of an input data stream. It can transmit this modulated signal in any of the license free ISM bands from 290 MHz to 1020 MHz.

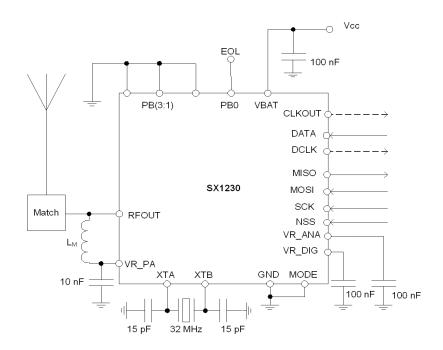

#### 1.1. Simplified Block Diagram

Figure 1. SX1230 Simplified Block Diagram

The general architecture of the SX1230 is shown in Figure 1. The frequency synthesizer generating the LO frequency is a third-order fractional-N sigma-delta PLL. The PLL is capable of fast auto-calibration and offers fast switching and settling times. For frequency modulation ((G)FSK and (G)MSK), the modulation is performed within the PLL bandwidth. Optional pre-filtering of the bit stream may also be enabled to reduce the power delivered to adjacent channels.

Amplitude modulation (OOK), is performed via a DAC driving the reference of the regulator of the PA. Note that pre-filtering of the bit stream is also available in this mode. The VCO works at 2, 4 or 6 times the RF output frequency to improve the quadrature precision and reduce pulling effects during transmission.

The PA of the SX1230 is comprised of two amplifiers - one high power, one low power. This enables the SX1230 to deliver a wide range, over 30 dB, of output powers - up to +13 dBm in single PA configuration. However, with an appropriate output impedance transformation, in dual PA mode, this can be increased to +17 dBm.

#### DATASHEET

**ADVANCED COMMUNICATIONS & SENSING**

The SX1230 also includes two timing references; an RC oscillator, for sleep mode operation of the SPI interface (in MCU mode), and a 32 MHz crystal oscillator, which serves as the low-noise frequency reference of the PLL. The references and supply voltages are provided by the power distribution system which includes several regulators allowing true battery powered operation.

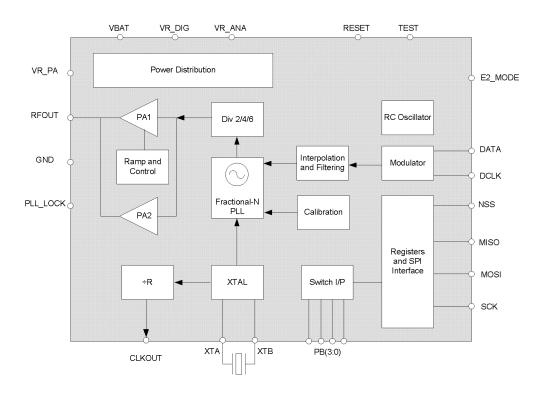

#### 1.2. Pin Diagram

The following diagram shows the pinouts of the 4x4 mm MLPQ-24 package.

Figure 2. SX1230 Pin diagram (top view)

**ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### 1.3. Pin Description

Table 1Description of the SX1230 Pinouts

| Number | Name     | Туре | Description MCU Mode              | Description Stand Alone Mode         |  |  |

|--------|----------|------|-----------------------------------|--------------------------------------|--|--|

| 0      | GROUND   | -    | Global ground (bottom of package) |                                      |  |  |

| 1      | E2_MODE  | I    | Mode select '0' = MCU mode        | Mode select '1' = Stand alone mode   |  |  |

| 2      | VR_ANA   | I/O  | Regulated supply volt             | age for analog circuitry             |  |  |

| 3      | ХТВ      | I/O  | Crystal c                         | connection                           |  |  |

| 4      | ХТА      | I    | Crystal c                         | connection                           |  |  |

| 5      | RESET    | I/O  | Reset, a                          | ctive high                           |  |  |

| 6      | PB(0)    | I    | Low battery indicator output      | Push-button input 0, active high     |  |  |

| 7      | PB(1)    | I    | Connect to GROUND                 | Push-button input 1, active high     |  |  |

| 8      | PB(2)    | I    | Connect to GROUND                 | Push-button input 2, active high     |  |  |

| 9      | PB(3)    | I    | Connect to GROUND                 | Push-button input 3, active high     |  |  |

| 10     | VR_DIG   | I    | Regulated supply                  | for digital circuitry                |  |  |

| 11     | CLKOUT   | 0    | Reference clock output for MCU    | Reference clock output               |  |  |

| 12     | PLL_LOCK | 0    | PLL lock detection, active high   | Transmission of frame OK, active low |  |  |

| 13     | DCLK     | 0    | Output data clock                 | NC                                   |  |  |

| 14     | DATA     | I    | Modulation input data             | NC                                   |  |  |

| 15     | SCK      | I    | SPI Clock input                   | SPI Clock output                     |  |  |

| 16     | MISO     | I/O  | SPI Data output                   | SPI Data input                       |  |  |

| 17     | MOSI     | I/O  | SPI Data input                    | SPI Data output                      |  |  |

| 18     | NSS      | I/O  | SPI Chip select input             | SPI Chip select output               |  |  |

| 19     | TEST     | I    | Connect to                        | GROUND                               |  |  |

| 20     | GND      | -    | RFG                               | Ground                               |  |  |

| 21     | RFOUT    | 0    | RFC                               | Dutput                               |  |  |

| 22     | GND      | -    | RFG                               | Ground                               |  |  |

| 23     | VR_PA    | I/O  | Regulated                         | supply for PA                        |  |  |

| 24     | VBAT     | I    | Main supply voltage from battery  |                                      |  |  |

#### 2. Electrical Characteristics

#### 2.1. ESD Notice

The SX1230 is an electrostatic discharge sensitive device. It satisfies:

- Class 1C of the JEDEC standard JESD22-A114-B (human body model) on pins 2, 10, 21 and 23.

- Class 2 of the JEDEC standard JESD22-A114-B (human body model) on all other pins.

#### 2.2. Absolute Maximum Ratings

Stresses above the values listed below may cause permanent device failure. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### Table 2 Absolute Maximum Ratings

| Symbol | Description    | Min  | Max | Unit |

|--------|----------------|------|-----|------|

| VDDmr  | Supply Voltage | -0.5 | 3.9 | V    |

| Tmr    | Temperature    | -55  | 115 | °C   |

#### 2.3. Operating Range

Operating ranges define the limits for functional operation and the parametric characteristics of the device as described in this section. Functionality outside these limits is not implied.

Table 3 Operating Range

| Symbol | Description                       | Min | Мах | Unit |

|--------|-----------------------------------|-----|-----|------|

| VDDop  | Supply voltage                    | 1.8 | 3.7 | V    |

| Тор    | Operational temperature range     | -40 | 85  | °C   |

| Clop   | Load capacitance on digital ports | -   | 25  | pF   |

## SX1230 Integrated Transmitter IC

Integrated Transmitter IC

#### **ADVANCED COMMUNICATIONS & SENSING**

SX1230

#### 2.4. Electrical Specifications

The table below gives the electrical specifications of the transmitter under the following conditions: Supply voltage = 3.3 V, temperature = 25 °C,  $f_{XOSC}$  = 32 MHz,  $f_{RF}$  = 915 MHz, 2-level FSK modulation without prefiltering, Df = 5 kHz, bit rate = 4.8 kbit/s and output power = 13 dBm terminated in a matched 50 ohm impedance, unless otherwise specified.

#### Table 4 Transmitter Specifications

| Symbol    | Description                                                                                 | Conditions                                                                                      | Min               | Тур                  | Max                | Unit                 |

|-----------|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------------------|----------------------|--------------------|----------------------|

| Current C | Consumption                                                                                 |                                                                                                 |                   |                      |                    |                      |

| IDDSL     | Supply current in sleep mode                                                                |                                                                                                 | -                 | 0.5                  | 1                  | μA                   |

| IDDST     | Supply current in standby mode                                                              | Crystal oscillator enabled                                                                      | -                 | 0.9                  | 1.2                | mA                   |

| IDDFS     | Supply current in synthesiser mode                                                          |                                                                                                 | -                 | 8                    | -                  | mA                   |

| IDDT      | Supply current in transmit mode<br>with appropriate external match-<br>ing (see Section 7). | RF Power o/p = 17 dBm<br>RF Power o/p = 13 dBm<br>RF Power o/p = 10 dBm<br>RF Power o/p = 0 dBm |                   | 95<br>45<br>33<br>20 | -<br>-<br>40<br>25 | mA<br>mA<br>mA<br>mA |

| RF and B  | aseband Specifications                                                                      |                                                                                                 |                   |                      |                    |                      |

| BRF       | Bit rate, FSK                                                                               | Programmable.                                                                                   | 1.2               | -                    | 600                | kbps                 |

| BRO       | Bit rate, OOK                                                                               | Programmable.                                                                                   | 1.2               | -                    | 32                 | kbps                 |

| FDA       | Frequency deviation, FSK                                                                    | Programmable                                                                                    | 0.6               | -                    | 300                | kHz                  |

| RFOP      | RF output power in 50 ohms                                                                  | Programmable with 1 dB steps.<br>Max<br>Min                                                     | 10<br>-21         | 13<br>-18            |                    | dBm<br>dBm           |

| PHN       | Transmitter phase noise                                                                     | 50 kHz Offset from carrier                                                                      | -                 | -95                  | -                  | dBc/<br>Hz           |

| RFOPH     | Max RF output power with an external impedance transforma-<br>tion                          | With external match to 50 ohms.                                                                 | 14                | 17                   | -                  | dBm                  |

| ACP       | Transmitter adjacent channel<br>power (measured at 25 kHz off-<br>set)                      | Pre-filter enabled. Measurement<br>conditions as defined by EN 300<br>220-1 V2.1.1.             | -                 | -                    | -37                | dBm                  |

| FR        | Synthesizer Frequency Range                                                                 | Programmable.<br>FBand 1<br>FBand 2<br>FBand 3                                                  | 290<br>431<br>862 | -<br>-<br>-          | 340<br>510<br>1020 | MHz<br>MHz<br>MHz    |

| FSTEP     | Frequency synthesizer step                                                                  | FXOSC/2 <sup>19</sup>                                                                           | -                 | 61                   | -                  | Hz                   |

| FRC       | RC Oscillator frequency range                                                               |                                                                                                 | 45                | 65                   | 85                 | kHz                  |

| Timing S  | pecifications                                                                               |                                                                                                 |                   |                      |                    |                      |

| TS_FS     | Frequency synthesizer wake up time                                                          | Crystal oscillator Enabled.                                                                     | -                 | 100                  | 150                | μs                   |

#### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

| Symbol | Description                     | Conditions                                                                                                      | Min | Тур | Max  | Unit |

|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| TS_TR  | Transmitter wake-up time        | Frequency synthesizer enabled.<br>Note, depends upon bit rate and<br>ramp time, please refer to Section<br>7.4. | -   | 120 | -    | μs   |

| TS_OS  | Crystal oscillator wake-up time |                                                                                                                 | -   | 300 | 500  | μs   |

| FXOSC  | Crystal oscillator frequency    |                                                                                                                 | 26  | 32  | 32   | MHz  |

| TS_TT  | Total Wake up time              | Sleep to transmit, automated. Note,<br>depends upon bit rate and ramp<br>time, please refer to Section 7.4.     | -   | 450 | -    | μs   |

| T_DATA | Data set-up time                |                                                                                                                 | -   | -   | 0.25 | μs   |

#### 3. Timing Characteristics

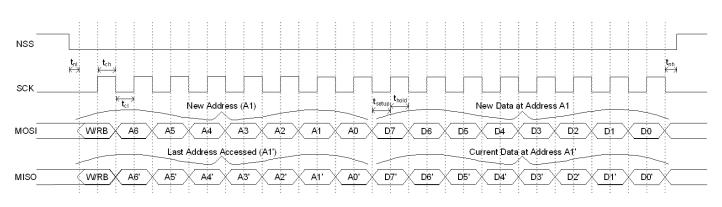

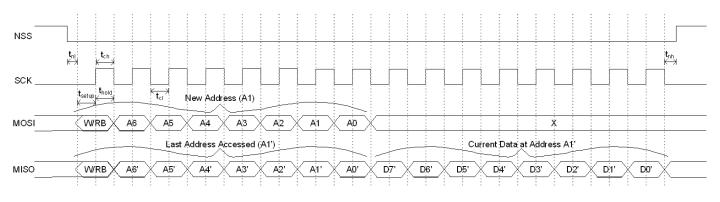

The following table gives the operating specifications for the SPI interface of the SX1230. *Table 5* SPI Timing Specifications

| Symbol             | Description     | Conditions                                   | Min | Тур | Max | Unit |

|--------------------|-----------------|----------------------------------------------|-----|-----|-----|------|

| f <sub>SCK</sub>   | SCK Frequency   |                                              | -   | -   | 10  | MHz  |

| t <sub>ch</sub>    | SCK High time   |                                              | 50  | -   | -   | ns   |

| t <sub>cl</sub>    | SCK Low time    |                                              | 50  | -   | -   | ns   |

| t <sub>rise</sub>  | SCK rise time   |                                              | -   | 5   | -   | ns   |

| t <sub>fall</sub>  | SCK Fall time   |                                              | -   | 5   | -   | ns   |

| t <sub>setup</sub> | MOSI Setup time | From MOSI transition to SCK rising edge      | 30  | -   | -   | ns   |

| t <sub>hold</sub>  | MOSI hold time  | From SCK rising edge to MOSI tran-<br>sition | 20  | -   | -   | ns   |

| t <sub>nl</sub>    | NSS setup time  | From NSS falling edge to SCK rising edge     | 30  |     | -   | ns   |

| t <sub>nh,n</sub>  | NSS Hold time   | From SCK falling edge to NSS rising edge.    | 30  | -   | -   | ns   |

For explanatory diagrams of the timing characteristic parameters, please see Figure 7 and Figure 8.

DATASHEET

#### 4. Working Modes of the SX1230

#### 4.1. Operating Modes

The four operating modes of the SX1230 are shown in Table 6. Each of these may be selected via the SPI bus by writing the corresponding bits to Mode(2:0). A key feature of the SX1230 is that the transition from one operating mode to the next is automatically optimized. For example, if the transmit operating mode is selected whilst in sleep operating mode then, in a pre-defined time-optimized sequence, each of the intermediate modes is engaged sequentially without the need to issue any further SPI commands. For more information on timing and optimization please see Section 7.4.

Table 6 SX1230 Operating Modes

| MODE(2:0) | Selected Mode | Enabled Blocks |     |          |              |    |  |

|-----------|---------------|----------------|-----|----------|--------------|----|--|

|           | Selected Mode | RC Osc         | SPI | Xtal Osc | Freq. Synth. | PA |  |

| 000       | Sleep mode    | Optional       | х   |          |              |    |  |

| 001       | Stand-by mode | Optional       | х   | х        |              |    |  |

| 010       | FS mode       | Optional       | х   | х        | x            |    |  |

| 011       | Transmit mode | Optional       | х   | х        | x            | х  |  |

#### 4.2. Application Modes

The SX1230 has two application modes, selected by applying an external logical level to the E2\_MODE input (pin 6). The first, MCU mode (E2\_Mode= '0'), configures the SX1230 as an SPI slave. This permits the configuration of the circuit by an external microprocessor via the SPI interface of the SX1230 and the data to be applied via the DATA input (pin 14). The second application mode, stand-alone mode (E2\_Mode = 0), sees the SX1230 configured as SPI master. In the stand-alone application mode the SX1230 can download its configuration from an external SPI E<sup>2</sup>PROM. Moreover, in response to an input on the GPIO pins, a specific configuration can be programmed and a payload transmitted.

Note that this mode selection process is performed at start up (or POR) of the circuit. Thus the hardware mode cannot be dynamically changed without resetting the chip. This may be achieved either by power down or by issuing an active high POR signal to the Reset input (pin 5). For reset signal timing please see the diagram of Figure 13 and accompanying description.

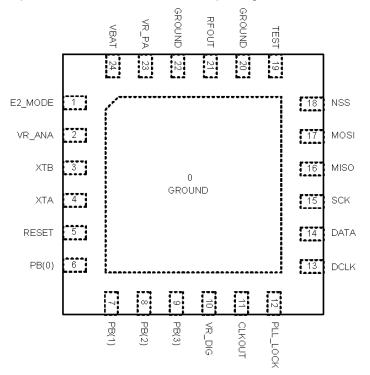

#### 4.2.1. Stand Alone Mode

In stand alone mode (E2\_Mode = '1') the SX1230 will operate as a stand-alone SPI master which can download both register settings and data payload from an SPI  $E^2$ PROM. Four debounced GPIO inputs are available in stand alone mode, in this application mode the SX1230 remains in sleep operating mode until either a single or combination of button presses are detected. SX1230 can then be dynamically reconfigured and / or transmit a data sequence stored within the  $E^2$ PROM.

The SX1230 can accommodate SPI E<sup>2</sup>PROM sizes up to 8 kbit and uses industry standard SPI commands. For a full description of E<sup>2</sup>PROM use with SX1230 and the associated application circuits, please see Section 6.1. The application circuit for stand-alone operation is shown in Figure 3, note that both matching and L<sub>M</sub> are band specific whilst  $C_{TX}$  is application specific.

Integrated Transmitter IC

#### ADVANCED COMMUNICATIONS & SENSING

DATASHEET

SX1230

Figure 3. SX1230 Stand-Alone Application Circuit

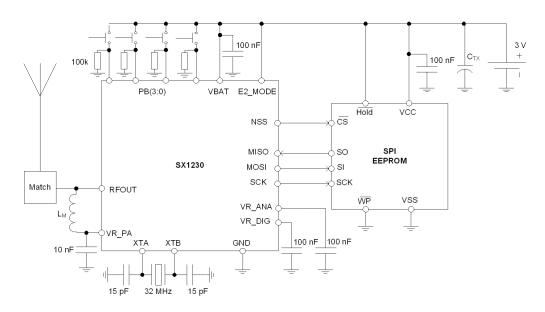

#### 4.2.2. MCU Mode

The SX1230 is also capable of operating in a conventional MCU controlled mode. Figure 4 shows the SX1230 operating in MCU mode and connected to an external microcontroller. Note that CLKOUT provides the oscillator signal for the MCU, thus negating the need for two crystal oscillators. The DCLK connection is also optional - only being required if the data rate is to be determined by SX1230 or transmit filtering is to be used.

DATASHEET

#### 5. Operation of the SX1230

The SX1230 is an integrated ISM band transmitter and features a fully integrated frequency synthesizer, modulator and power amplifier. This section describes the operation of the SX1230 and the functionality of these blocks.

#### 5.1. Main Parameters

#### 5.1.1. Center Frequency

The carrier output center frequency,  $f_{RF}$  of the SX1230 is programmable via the SPI interface. It is determined by the following equation:

$$f_{RF} = \frac{\text{freq}_rf(23:0) \cdot f_{XOSC}}{2^{19}}$$

where freq\_rf(23:0) is the decimal value of the 24 bit number stored in configuration registers FrfMsb, FrfMid and FrfLsb and  $f_{XOSC}$  is the frequency of the crystal oscillator. If the optimal value of 32 MHz is selected for the crystal oscillator, then this results in a programmable frequency resolution of 61.035 Hz.

Note that RF output frequencies are only valid in the bands 290-340 MHz, 431-510 MHz and 862-1020 MHz. Note also, that for ease of use, the band selection process is performed automatically.

#### 5.1.2. Frequency Deviation

The frequency deviation of the SX1230 in FSK mode is given by the following equation:

$$\Delta f = \frac{f_{XOSC} \cdot df\_coeff(13:0)}{2^{19}}$$

where df\_coeff is the decimal value of the 14 bit contents of the FdevLsb and FdevMsb configuration registers.

#### 5.1.3. Bit Rate

The bit rate (or, depending upon coding, the chip rate) of the SX1230 is given by the following equation:

$$R_B = \frac{f_{XOSC}}{\text{br_ratio}(15:0)}$$

where  $f_{XOSC}$  is the crystal oscillator frequency, br\_ratio is the decimal value of the 16 bit contents of registers BrMsb and BrLsb. Note that for OOK modulation the maximum bit rate is 32.7 kbps which corresponds to a br\_ratio(15:0) of 979. The table below gives examples of some of the standard data rates accessible with SX1230.

DATASHEET

| Table 7 | Example Standard | Bitrates and their | Corresponding | Register Settings. |

|---------|------------------|--------------------|---------------|--------------------|

|---------|------------------|--------------------|---------------|--------------------|

| Туре                                | BrMSB | BrLSB | (G)FSK, (G)MSK | ООК         | Rb Actual (to 7s.f.) |

|-------------------------------------|-------|-------|----------------|-------------|----------------------|

| Classical modem baud rates          | 0x68  | 0x2B  | 1.2 kbps       | 1.2 kbps    | 1200.015             |

| (multiples of 1.2 kbps)             | 0x34  | 0x15  | 2.4 kbps       | 2.4 kbps    | 2400.060             |

|                                     | 0x1A  | 0x0B  | 4.8 kbps       | 4.8 kbps    | 4799.760             |

|                                     | 0x0D  | 0x05  | 9.6 kbps       | 9.6 kbps    | 9600.960             |

|                                     | 0x06  | 0x83  | 19.2 kbps      | 19.2 kbps   | 19196.16             |

|                                     | 0x03  | 0x41  | 38.4 kbps      |             | 38415.36             |

|                                     | 0x01  | 0xA1  | 76.8 kbps      |             | 76738.60             |

|                                     | 0x00  | 0xD0  | 153.6 kbps     |             | 153846.1             |

| Classical modem baud rates          | 0x02  | 0x2C  | 57.6 kbps      |             | 57553.95             |

| (multiples of 0.9 kbps)             | 0x01  | 0x16  | 115.2 kbps     |             | 115107.9             |

| Round bit rates                     | 0x0A  | 0x00  | 12.5 kbps      | 12.5 kbps   | 12500.00             |

| (multiples of 12.5, 25 and 50 kbps) | 0x05  | 0x00  | 25 kbps        | 25 kbps     | 25000.00             |

|                                     | 0x80  | 0x00  | 50 kbps        |             | 50000.00             |

|                                     | 0x01  | 0x40  | 100 kbps       |             | 100000.0             |

|                                     | 0x00  | 0xD5  | 150 kbps       |             | 150234.7             |

|                                     | 0x00  | 0xA0  | 200 kbps       |             | 200000.0             |

|                                     | 0x00  | 0x80  | 250 kbps       |             | 250000.0             |

|                                     | 0x00  | 0x6B  | 300 kbps       |             | 299065.4             |

| Watch Xtal frequency                | 0x03  | 0xD1  | 32.768 kbps    | 32.768 kbps | 32753.32             |

#### 5.2. Synthesizer

The frequency synthesizer of the SX1230 is a fully integrated fractional-N third-order sigma-delta phase-locked loop and VCO. Also incorporated are fully integrated third-order and low pass filters which determine the loop bandwidth. All of these features are fully automated and derived from the user bitrate and frequency deviation settings, as described in Sections 5.1.1 to 5.1.3.

To ensure the frequency accuracy of the PLL output it is necessary to perform calibration. The calibration process is performed automatically upon power up of the SX1230. However, the calibration feature is also accessible to the user via the SPI configuration register, PIIStat (address 0x0A). The calibration is performed by setting bit 2 (pII\_cal) high. This ensures that the frequency output accuracy is limited only by the frequency error of the crystal oscillator, the calibration procedure lasts 500 µs, during which time pII\_cal\_done (bit 4 of address 0x0A) is set low. Once complete pII\_cal\_done is set high and confirmation of a successful calibration can be obtained by reading pII\_cal\_ok.

## OOK

ADVANCED COMMUNICATIONS & SENSING

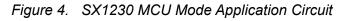

#### Figure 5. Simplified Schematic of the SX1230 Power Amplifier

The mode of operation of the PA's is determined by the register setting pa select(1:0) which is configured as shown in Table 8, below. The output power of the PA is determined by the value of the register pow val(4:0), with a single PA enabled the output power is set by:

#### Pout = -18 dBm + pow val(4:0)

The default setting for this register is 13 dBm. The expressions for the output power with other combinations of power amplifier enabled are shown in Table 8. Note also that the power amplifier current limiter, over current protection (OCP), feature of SX1230 can also limit the output power. To ensure correct operation at 17 dBm ensure that trim ocp(3:0) is set to 105 mA ('1100

#### Table 8 Powe

01

10

11

| The ramp and power control features of the PA     | , determine the regulato | or output voltage which is used to power the |

|---------------------------------------------------|--------------------------|----------------------------------------------|

| amplifiers, this must be done through an external | ₹F choke.                |                                              |

-18 to 13 dBm

-13 to 17 dBm

-18 dBm + pow val(4:0)

-13 dBm + pow val(4:0)

| 0')       |                |                |             |              |

|-----------|----------------|----------------|-------------|--------------|

| <i>er</i> | Amplifier Mode | Selection Trut | h Table     |              |

|           | pa_select(1:0) | Mode           | Power Range | Pout Formula |

|           | 00             | invalid        | -           |              |

PA1 enabled

PA2 enabled

Dual PA

#### 5.3. The Power Amplifier

A simplified schematic of the dual power amplifiers of the SX1230 is shown in Figure 5. PA 1 comprises a pair of amplifiers: One dedicated for low power use, LPA, for programmed powers from -18 to -3 dBm: The second for high power use, HPA, for programmed powers from -2 to 13 dBm. PA 2 is a single high power amplifier and may be used in conjunction with PA 1 to deliver the full 17 dBm of output power.

Integrated Transmitter IC

DATASHEET

SX1230

DATASHEET

#### 6. Digital Control and Interface

The SX1230 has several operating modes, configuration parameters and internal status indicators which are stored in internal registers. In MCU mode, all of these registers can be accessed by an external microcontroller via the SPI interface. In stand alone mode, both the configuration information and the data to be transmitted, are stored in an external  $E^2$ PROM. The way that both the configuration and payload information is stored in the  $E^2$ PROM must match the way the configuration is defined in the internal registers. For a full description see Section 6.1.2.

#### 6.1. Stand Alone Mode

#### 6.1.1. State Machine Description

The stand alone mode is activated when the pin E2\_Mode is tied to VDD. The SX1230 SPI interface is then configured in master mode. The internal state machine of the SX1230 then carries out the following operations:

1) Immediately after power-up, the SPI interface reads the main configuration section in the E<sup>2</sup>PROM and then goes into the 'sleep' operating mode (i.e. all blocks off).

2) Whilst in 'sleep' operating mode, when an edge is detected on any of the push-buttons PB[3:0], the chip wakes-up and starts the RC oscillator (typical startup time ~100  $\mu$ s).

3) The RC oscillator is used to clock a debounce timer which gives the logical push button input value after the programmed delay. The frame section corresponding to the button value (1 to 15) is read from the E<sup>2</sup>PROM. At this point additional, button specific, configuration information may be loaded. Otherwise, the configuration settings of 1) are used. Using the appropriate configuration, the payload corresponding to the detected button press is then transmitted. The payload transmission may be repeated up to 254 times.

4) When the frame has been transmitted, the pad PLL\_LOCK goes low and the chip goes into SLEEP mode.

#### 6.1.2. Memory Organization of the E<sup>2</sup>PROM

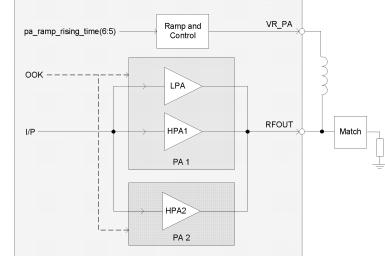

The memory map for stand alone mode is shown in Figure 6. The configuration information occupies the first 77 bytes, the format of the configuration is {ADDR; VALUE} - therefore allowing up to 38 registers to be defined. Each push button configuration is mapped directly to a location in the  $E^2PROM$  - determined by the mappings given in Table 9 and the variable section\_size(5:0). The purpose of this variable, push button specific, section size is to allow the optimum use of different sizes of external memory. Note that the maximum frame length is 64 bytes - this equates to a maximum  $E^2PROM$  size of 8 kbit. The influence of the section\_size variable is illustrated in Figure 6.

The mapping of Table 9 permits up to 15 frames to be defined. Each section may contain both write\_registers commands and the payload to be transmitted. Thus allowing the dynamic configuration of settings such as output power and frequency in response to a button push. Each section within the E<sup>2</sup>PROM must conform to the following format: {FIFO\_ADDR; REPEAT; LENGTH; VALUE\_1; VALUE\_2;...;VALUE\_N}. Where VALUE\_1... N is the user defined payload, REPEAT is the number of times the frame is to be transmitted, LENGTH defines the number of bytes in the message and FIFO\_ADDR = 0x95.

The push-buttons may need to be debounced before being read. The debouncer time constant is programmed by the debounce\_time(2:0) register which allows a range of debounce timer values to be accessed from 470 ms to 480 ms. An

DATASHEET

ADVANCED COMMUNICATIONS & SENSING

option for no debouncing is also available. Note that time constants are process and temperature dependent and may vary by +/- 15%.

Figure 6. Memory Mapping in Stand Alone Mode

The table below gives the push button mappings for the determination of  $E^2$ PROM memory locations. Note that the combinations PB[3:0] = '0001', '0010', '0100' and '1000' are mapped to the four lowest locations in memory. This mapping allows the use of a simple four button interface with the minimum memory size.

Table 9

Push Button Combination to E<sup>2</sup>PROM Memory Location Mapping

| PB[3:0] | PB_MAPPING(3:0)              | PB[3:0] | PB_MAPPING(3:0)  |

|---------|------------------------------|---------|------------------|

| 0000    | None (no active push-button) | 1000    | 3                |

| 0001    | 0                            | 1001    | 7                |

| 0010    | 1                            | 1010    | 8                |

| 0011    | 4                            | 1011    | 11               |

| 0100    | 2                            | 1100    | 9                |

| 0101    | 5                            | 1101    | 12               |

| 0110    | 6                            | 1110    | 13               |

| 0111    | 10                           | 1111    | 14 / Low Battery |

The commands in the  $E^2$ PROM are written as instructions thus bit 7 is set high - equivalent to adding 0x80 to the register address to be programmed. As was shown in Figure 6, the first 77 bytes are used for configuration. Note that registers only require programming if they hold a value other than the default value (see table 11 for default register settings).

DATASHEET

**ADVANCED COMMUNICATIONS & SENSING**

The following table gives an example snippet of  $E^2$ PROM contents, here for each location in  $E^2$ PROM memory the first 13 bytes of the available 77 (0x4C) bytes are occupied with configuration. The remaining bytes are left in their default 0xFF setting. The first push-button memory location is at 0x4D. Here we see that the periodic mode timer (see following section for a full description) is configured and a 10 byte payload follows. Subsequent push buttons are configured at the locations determined by the section size, see Figure 6.

# Table 10 Example External SPI E2PROM Contents for SX1230 Configuration Address Content Address Content

| Address   | Content | Comment                    | Address | Content | Comment                |

|-----------|---------|----------------------------|---------|---------|------------------------|

| 0x00      | 0x81    | Start-up config. (address) | 0x4C    | 0xFF    | Empty                  |

| 0x01      | 0x05    | Start-up config. (data)    | 0x4D    | 0x97    | PB[0] config (address) |

| 0x02      | 0x82    | Start-up config. (address) | 0x4E    | 0x00    | PB[0] config (data)    |

| 0x03      | 0x00    | Start-up config. (data)    | 0x4F    | 0x95    | FIFO address           |

| 0x04      | 0x83    | Start-up config. (address) | 0x50    | 0x0A    | Repeat                 |

| 0x05      | 0x03    | Start-up config. (data)    | 0x51    | 0x0A    | Length                 |

| 0x06      | 0x84    | Start-up config. (address) | 0x52    | 0x55    | Start of PB[0] Payload |

| 0x07      | 0x33    | Start-up config. (data)    | 0x53    | 0x55    | PB[0] Payload: Byte 1  |

| 0x08      | 0x85    | Start-up config. (address) | 0x54    | 0x55    | PB[0] Payload: Byte 2  |

| 0x09      | 0xE3    | Start-up config. (data)    | 0x55    | 0x55    | PB[0] Payload: Byte 3  |

| 0x0A      | 0x90    | Start-up config. (address) | 0x56    | 0xAA    | PB[0] Payload: Byte 4  |

| 0x0B      | 0x0F    | Start-up config. (data)    | 0x57    | 0x0A    | PB[0] Payload: Byte 5  |

| 0x0C      | 0x93    | Start-up config. (address) | 0x58    | 0x0B    | PB[0] Payload: Byte 6  |

| 0x0D      | 0x1C    | Start-up config. (data)    | 0x59    | 0x0C    | PB[0] Payload: Byte 7  |

| 0x0E      | 0xFF    | Empty                      | 0x5A    | 0x20    | PB[0] Payload: Byte 8  |

| 0x0F      | 0xFF    | Empty                      | 0x5B    | 0x00    | PB[0] Payload: Byte 9  |

| 0x10-0x4B | 0xFF    | 0x10 to 0x4B Empty         | 0x5C    | 0x97    | PB[1] config (address) |

Subsequent button push button configuration and payload could follow at address 0x5C, respecting the  $E^2$ PROM section size constraint. Note that if register 0x00 is configured, care should be taken to enable transmit mode - mode(2:0) to ensure reliable transition to transmit mode.

#### 6.1.3. Periodic mode

Periodic mode is a sub-mode of stand alone mode wherein the SX1230 will periodically sense the push button inputs for activity. If a push button input is high then the payload according to that input is transmitted. The wake-up interval,  $T_{wakeup}$ , is defined by periodic\_n(3:0) and periodic\_d(3:0) values.

$$T_{wakeup} = 2 \cdot T_{RC} \cdot (\text{periodic}_n(3:0) + 1) \cdot 2^{\text{periodic}_d(3:0) + 9}$$

DATASHEET

#### **ADVANCED COMMUNICATIONS & SENSING**

where  $T_{RC}$  is the RC oscillator period, periodic\_n is programmable between 0 and 15 and periodic\_d may take values between 0 and 10. The maximum period is hence approximately 125 s when the frequency of the RC oscillator is 67 kHz. Push button mode is enabled when the value of D is non-zero and, when activated, all stand alone mode functionality is available. It is important to note that if there is no push button pressed, then no message will be transmitted.

#### 6.1.4. Low Battery Indicator: Stand Alone Mode

The low battery indicator may be used in stand alone mode to detect the battery voltage and send a low battery message to the receiver. It is enabled by setting the eol\_frame\_mode bit 'high' (register 0x12). The low battery state is determined by comparing the supply voltage with a 1.695 V to 2.185 V programmable threshold (threshold trim\_eol(2:0), address 0x12). Following detection, the following actions are performed depending upon the exact mode of operation:

**Normal Operation (Non-Periodic):** The battery end-of-life condition is checked during the normal frame. If it is true, then a single extra frame #14 (see Table 9) is automatically sent after the normal frame.

**Stand-Alone Periodic Mode Operation:** The battery end-of-life condition is checked during the normal frame. If it is true, then the next frame, sent at the next timer tick is frame #14 (see Table 9), the frame is sent only once.

#### 6.1.5. Low Battery Indicator: MCU Mode

In MCU mode the low battery status indicator may be accessed and configured via the SPI register EolCtrl. Alternatively, the active high low battery indication is mapped to the PBO pin allowing the independent generation of hardware interrupts.

#### 6.2. MCU Mode

#### 6.2.1. SPI Operation

The first byte in any data transfer over the SPI is the address read/write byte. It comprises:

- 1. W/RB bit, which is 1 for write access and 0 for read access

- 2. 7 bits of address, MSB first.

A transfer always starts by the NSS (not slave select) signal going low whilst SCK is high. MOSI (master out - slave in) is generated by the master on the next falling edge of SCK and is sampled by the slave on the next rising edge of SCK. MISO is generated by the slave on the falling edge of SCK and is high impedance when NSS is high. By convention, all bytes are sent MSB first.

MCU mode is activated when pad E2\_Mode is tied to GND (ground). In this mode the SX1230 is configured as SPI slave and its internal configuration registers can be written following the format shown in Figure 7.

An 'address write-byte' followed by a data byte is sent for a write access. Where multiple sequential registers are to be written, the NSS input may be kept low after this first address-byte plus data-byte have been sent. In this state sequential data-bytes may be written, the address is automatically incremented after the reception of each additional data-byte. This allows the sequential data-bytes to be written without the need for an address byte. NSS must then be set 'high' after the last byte transfer.

**ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

Figure 7. Register Write Access

Figure 8. Register Read Access

Similarly, the configuration registers of the SX1230 can be read by issuing an 'address read-byte' (see Figure 8) the corresponding register contents are then transferred over the MISO line. As above, the contents of each subsequent register can be transferred by holding the NSS input low.

A summary of all of the registers of the SX1230 are given in Table 11, this is followed by detailed descriptions of each of the registers in Table 12.

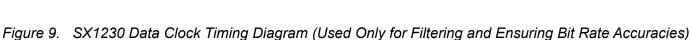

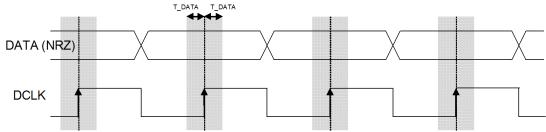

6.2.2. Data and Data Clock Usage

In MCU mode the data to be transmitted is applied exclusively via the DATA input. The DATA input is sampled at the crystal frequency, fxosc. Where the MCU mediates the data rate and no gaussian or bit filtering is required, then the use of the data clock signal is optional. However, where filtering is to be used or the specified data rate accuracy is to be achieved, then the rising edge of the data clock, DCLK, signal must be used to clock the data into the SX1230 DATA input.

DATASHEET

SX1230

Integrated Transmitter IC

**ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### 6.3. SX1230 Register Description

Table 11 SX1230 Register Summary

| Address | Register Name | Description                                         |

|---------|---------------|-----------------------------------------------------|

| 0x00    | Mode          | Operating and modulation mode settings.             |

| 0x01    | BrMsb         | Bit rate setting.                                   |

| 0x02    | BrLsb         |                                                     |

| 0x03    | FdevMsb       | Frequency Deviation (FSK).                          |

| 0x04    | FdevLsb       |                                                     |

| 0x05    | FrfMsb        | RF centre frequency setting.                        |

| 0x06    | FrfMid        |                                                     |

| 0x07    | FrfLsb        |                                                     |

| 0x08    | PaCtrl        | PA selection and power control.                     |

| 0x09    | PaFskRamp     | PA rise and fall timing (FSK).                      |

| 0x0A    | PllStat       | PLL status register.                                |

| 0x0B    | VcoCtrl1      | VCO calibration values.                             |

| 0x0C    | VcoCtrl2      |                                                     |

| 0x0D    | VcoCtrl3      |                                                     |

| 0x0E    | VcoCtrl4      |                                                     |

| 0x0F    | ClockCtrl     | Clock output pin settings.                          |

| 0x10    | Eeprom        | Stand alone mode E <sup>2</sup> PROM configuration. |

| 0x11    | ClockSel      | Selection between RC or crystal oscillator.         |

| 0x12    | EolCtrl       | Low battery indicator settings.                     |

| 0x13    | PaOcpCtrl     | PA Over current protection - limits PA current.     |

| 0x14    | unused        | -                                                   |

| 0x15    | unused        | -                                                   |

| 0x16    | unused        | -                                                   |

| 0x17    | PerDivider    | Periodic mode wake-up timer control.                |

| 0x18    | BtnDeb        | Push button debouncer setting.                      |

#### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### Table 12 SX1230 SPI Register Description

| Addr. | Register Name | Default | Bits | Variable Name     | Mode | Description                                                                                                                                                                                                                                                                                             |

|-------|---------------|---------|------|-------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00  | Mode          | 0x10    | 7    | -                 | rw   | unused                                                                                                                                                                                                                                                                                                  |

|       |               |         | 6:4  | mode(2:0)         | rw   | Operating mode:<br>000 sleep mode (SLEEP)<br>001 stand-by mode (STDBY)<br>010 frequency synthesizer mode (FS)<br>011 transmit mode (TX)<br>others reserved<br>Read value is always chip actual mode                                                                                                     |

|       |               |         | 3:2  | modul_type(1:0)   | rw   | Modulation type:<br>00 FSK<br>01 OOK<br>Others reserved                                                                                                                                                                                                                                                 |

|       |               |         | 1:0  | data_shaping(1:0) | rw   | Data shaping:<br>In FSK:<br>00 no shaping<br>01 Gaussian filter with BT = 1.0<br>10 Gaussian filter with BT = 0.5<br>11 Gaussian filter with BT = 0.3<br>In OOK:<br>00 no shaping<br>01 filtering with fcutoff = bit rate<br>10 filtering with fcutoff = 2 * bit rate<br>(BR <= 32 kb/s)<br>11 reserved |

| 0x01  | BrMsb         | 0x1A    | 7:0  | br_ratio(15:8)    | rw   | Bit rate MSB (chip rate if Manchester encoding)                                                                                                                                                                                                                                                         |

| 0x02  | BrLsb         | 0x0B    | 7:0  | br_ratio(7:0)     | rw   | Bit rate LSB (chip rate if Manchester encoding)<br>$R_B = \frac{f_{XOSC}}{\text{br_ratio}(15:0)}$ Default value is 0x1A0B = 4.8 kbps                                                                                                                                                                    |

| 0x03  | FdevMsb       | 0x00    | 7:6  | -                 | -    | unused                                                                                                                                                                                                                                                                                                  |

|       |               |         | 5:0  | fdev_coeff(13:8)  | rw   | Deviation frequency MSB                                                                                                                                                                                                                                                                                 |

| 0x04  | FdevLsb       | 0x52    | 7:0  | fdev_coeff(7:0)   | rw   | Deviation Frequency LSB<br>$\Delta f = \frac{f_{XOSC} \cdot df\_coeff(13:0)}{2^{19}}$ Default = 0x0052 = 82, gives 5 kHz                                                                                                                                                                                |

| 0x05  | FrfMsb        | 0xE4    | 7:0  | freq_rf(23:16)    | rw   | RF carrier frequency MSB                                                                                                                                                                                                                                                                                |

| 0x06  | FrfMid        | 0xC0    | 7:0  | freq_rf(15:8)     | rw   | RF carrier centre bits                                                                                                                                                                                                                                                                                  |

#### **ADVANCED COMMUNICATIONS & SENSING**

| Addr. | Register Name | Default | Bits | Variable Name            | Mode | Description                                                                                                                                                                                                                                                                                           |

|-------|---------------|---------|------|--------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x07  | FrfLsb        | 0x00    | 7:0  | freq_rf(7:0)             | rw   | RF carrier frequency LSB<br>$f_{RF} = \frac{\text{freq}_rf(23:0) \cdot f_{XOSC}}{2^{19}}$ For $f_{XOSC}$ = 32 MHz, resolution = 61.035 Hz<br>Default = 0xE4C000, gives 915 MHz                                                                                                                        |

| 0x08  | PaCtrl        | 0x3F    | 7    | -                        | r    | unused                                                                                                                                                                                                                                                                                                |

|       |               |         | 6:5  | pa_select                | rw   | Selects between PA1 and PA2<br>00 = unused<br>01 = PA1 selected (d)<br>10 = reserved<br>11 = PA1 and PA2 selected.                                                                                                                                                                                    |

|       |               |         | 4:0  | pow_val(4:0)             | rw   | Output power<br>Pout = -18 dBm + pow_val<br>Default is 13 dBm.                                                                                                                                                                                                                                        |

| 0x09  | PaFskRamp     | 0x08    | 7:4  | -                        | r    | unused                                                                                                                                                                                                                                                                                                |

|       |               |         | 3:0  | pa_ramp_rising_time(3:0) | rw   | Rise/fall time ramping (FSK only)<br>0000 = 2  ms<br>0001 = 1  ms<br>0010 = 500  us<br>0011 = 250  us<br>0100 = 125  us<br>0101 = 100  us<br>0110 = 62  us<br>0111 = 50  us<br>1000 = 40  us (d)<br>1001 = 31  us<br>1011 = 25  us<br>1010 = 20  us<br>1100 = 15  us<br>1110 = 10  us<br>1111 = 8  us |

#### **ADVANCED COMMUNICATIONS & SENSING**

| Addr. | Register Name | Default | Bits | Variable Name   | Mode | Description                                                                                                                                                                                                                                                                                                                                                      |

|-------|---------------|---------|------|-----------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0A  | PIIStat       | 0x10    | 7:6  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 5    | pll_lock_detect | r    | PLL lock status:<br>0 = PLL not locked<br>1 = PLL locked                                                                                                                                                                                                                                                                                                         |

|       |               |         | 4    | pll_cal_done    | r    | PLL calibration status<br>0 = Calibration on-going<br>1 = Calibration performed<br>Note: Reset to 0 in sleep mode irrespective of<br>calibration state.                                                                                                                                                                                                          |

|       |               |         | 3    | pll_cal_ok      | r    | PLL Calibration Result<br>0 = Calibration procedure failed<br>1= Calibration procedure successful<br>Note: Reset to 0 in sleep mode irrespective of<br>calibration state                                                                                                                                                                                         |

|       |               |         | 2    | pll_cal_start   | w    | Triggers PLL calibration, always read as 0.                                                                                                                                                                                                                                                                                                                      |

|       |               |         | 1:0  | pll_divr(1:0)   | rw   | PLL division ratio<br>00 = Automatic<br>Others, PLL divider = PLL_divr                                                                                                                                                                                                                                                                                           |

| 0x0B  | VcoCtrl1      | NA      | 7:5  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 4:0  | SB1(4:0)        | rw   | VCO band first calibration value                                                                                                                                                                                                                                                                                                                                 |

| 0x0C  | VcoCtrl2      | NA      | 7:5  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 4:0  | SB2(4:0)        | rw   | VCO band second calibration value                                                                                                                                                                                                                                                                                                                                |

| 0x0D  | VcoCtrl3      | NA      | 7:5  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 4:0  | SB3(4:0)        | rw   | VCO band third calibration value                                                                                                                                                                                                                                                                                                                                 |

| 0x0E  | VcoCtrl4      | NA      | 7:5  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 4:0  | SB4(4:0)        | rw   | VCO band fourth calibration value                                                                                                                                                                                                                                                                                                                                |

| 0x0F  | ClockCtrl     | 0x05    | 7:4  | -               | r    | unused                                                                                                                                                                                                                                                                                                                                                           |

|       |               |         | 3    | rc_enable       | rw   | Enables RC oscillator. RC oscillator is also<br>automatically switched on in E <sup>2</sup> PROM mode.<br>0 = RC oscillator off<br>1 = RC oscillator on                                                                                                                                                                                                          |

|       |               |         | 2:0  | clkout_select   | rw   | Selects CLKOUT source:<br>$000 = f_{XOSC}$ (32 MHz)<br>$001 = f_{XOSC} / 2$ (16 MHz)<br>$010 = f_{XOSC} / 4$ (8 MHz)<br>$011 = f_{XOSC} / 8$ (4 MHz)<br>$100 = f_{XOSC} / 16$ (2 MHz)<br>$101 = f_{XOSC} / 32$ (1 MHz) (d)<br>110 = RC clock (65 kHz)<br>111 = Clock output off.<br>Note: Switching from RC to $f_{XOSC}$ or vice versa<br>can generate glitches |

#### **ADVANCED COMMUNICATIONS & SENSING**

| Addr. | Register Name | Default | Bits | Variable Name     | Mode | Description                                                                                                                                                                                                                                                                                                                            |

|-------|---------------|---------|------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x10  | Eeprom        | 0x10    | 7:6  | -                 | -    | unused                                                                                                                                                                                                                                                                                                                                 |

|       |               |         | 5:0  | section_size(5:0) | rw   | Section size, used in E <sup>2</sup> PROM mode only.                                                                                                                                                                                                                                                                                   |

| 0x11  | ClockSel      | 0x11    | 7:5  | -                 | r    | unused                                                                                                                                                                                                                                                                                                                                 |

|       |               |         | 4    | xosc_ck_ext_sel   | rw   | Selects external clock instead of xosc<br>0 = use xosc<br>1 = use external clock                                                                                                                                                                                                                                                       |

|       |               |         | 3:0  | -                 | r/w  | unused                                                                                                                                                                                                                                                                                                                                 |

| 0x12  | EolCtrl       | 0x12    | 7:5  | -                 | r    | unused                                                                                                                                                                                                                                                                                                                                 |

|       |               |         | 4    | q_eol             | r    | Battery end of life flag<br>0 = VBAT < VTHR (Battery is flat)<br>1 = VBAT > VTHR                                                                                                                                                                                                                                                       |

|       |               |         | 3    | on_eol            | rw   | Enables EOL<br>0 = EOL disabled<br>1 = EOL enabled                                                                                                                                                                                                                                                                                     |

|       |               |         | 2:0  | vthr_eol(2:0)     | rw   | Battery end of life threshold<br>000 = 1.695 V<br>001 = 1.764 V<br>010 = 1.835 V (default setting)<br>011 = 1.905 V<br>100 = 1.976 V<br>101 = 2.045 V<br>110 = 2.116 V<br>111 = 2.185 V                                                                                                                                                |

| 0x13  | PaOcpCtrl     | 0x11    | 7:5  | -                 | r    | unused                                                                                                                                                                                                                                                                                                                                 |

|       |               |         | 4    | on_ocp            | rw   | Enables power amplifier current limiter:<br>0 = OCP disabled<br>1 = OCP enabled                                                                                                                                                                                                                                                        |

|       |               |         | 3:0  | trim_ocp(3:0)     | rw   | PA OCP DC load current threshold:<br>0000 = 45 mA<br>0001 = 50 mA<br>0010 = 55 mA<br>0011 = 60 mA<br>0100 = 65 mA<br>0101 = 70 mA<br>0110 = 75 mA<br>0111 = 80 mA<br>1000 = 85 mA<br>1001 = 90 mA<br>1011 = 100 mA (default setting)<br>1100 = 105 mA (recommended +17 dBm setting)<br>1101 = 110 mA<br>1110 = 115 mA<br>1111 = 120 mA |

| 0x14  | Unused        | -       | -    | -                 | -    | unused                                                                                                                                                                                                                                                                                                                                 |