# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# SX1231SKB

# USER GUIDE

# **Table of Contents**

| Table of Contents                                                       |    |

|-------------------------------------------------------------------------|----|

| Index of Figures                                                        |    |

| Index of Tables                                                         | 3  |

| 1 Introduction                                                          | 4  |

| 2 Getting Started                                                       | 5  |

| 2.1 Evaluation Kit Contents                                             | 5  |

| 2.2 Installation                                                        |    |

| 2.3 SX1231SKB Overview                                                  |    |

| 3 SX1231 Quick Start Guide                                              |    |

| 4 SX1231SKB Software Description                                        |    |

| 4.1 Overview                                                            |    |

| 4.2 Menu Tool Bar                                                       |    |

| 4.2.1 File Menu                                                         |    |

| 4.2.2 Action Menu                                                       |    |

| 4.2.3 Tools Menu                                                        |    |

| 4.2.4 Help Menu                                                         |    |

| 4.3 Window Toolbar                                                      |    |

| 4.4 Status Bar                                                          |    |

| 4.5 Operating Modes Control Box                                         |    |

| 4.6 Irg Status Indicator                                                |    |

| 5 Configuration Registers Tabs                                          |    |

| 5.1 Common Configuration Registers Tab                                  | 12 |

| 5.1.1 Modulation Mode Window                                            |    |

| 5.2 Transmitter Configuration Register Tab                              |    |

| 5.3 Receiver Configuration Register Tab                                 |    |

| 5.3.1 Rx Bandwidth                                                      |    |

| 5.3.2 LNA Gain Window                                                   |    |

| 5.3.3 AFC / FEI                                                         |    |

| 5.3.4 RSSI                                                              |    |

| 5.3.5 Continuous-Time Digital AGC                                       |    |

| 5.4 Irq & Mapping Configuration Register Tab                            | 17 |

| 5.5 Packet Handler Configuration Register Tab                           |    |

| 5.5.1 Sync Word                                                         |    |

| 5.5.2 AutoMode Operation                                                |    |

| 5.5.3 Packet Log                                                        |    |

| 5.5.4 Packet Handler GUI Limitations                                    |    |

| 5.6 Temperature Configuration Register Tab                              | 21 |

| 6 Registers Display Window                                              |    |

| 7 Advanced Operating Modes                                              |    |

| 7 Advanced Operating Modes                                              |    |

| 7.1.1 Transmitter Mode Configuration.                                   |    |

| 7.1.2 Receiver Mode Configuration                                       |    |

| 0                                                                       |    |

| <ul> <li>7.2 Test Mode Window</li> <li>7.3 Verification Mode</li> </ul> |    |

|                                                                         |    |

| <ul> <li>7.4 RSSI Analyzer</li> <li>7.5 Spectrum Analyzer</li> </ul>    |    |

|                                                                         |    |

| 8 Compatibility with Earlier Silicon Revisions                          |    |

# **Index of Figures**

| Figure 1: SM1231 Application Schematic                  | 4  |

|---------------------------------------------------------|----|

| Figure 2: SM1231 Module Mounted on USB Bridge           | 5  |

| Figure 3: SX1231SKB GUI Overview                        | 7  |

| Figure 4: File Menu Options                             | 8  |

| Figure 5: Action Menu Options                           | 8  |

| Figure 6: Tools Menu Options                            | 9  |

| Figure 7: Help Menu Options                             |    |

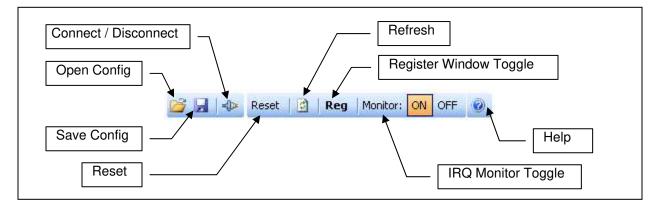

| Figure 8: Windows Toolbar Menu                          | 9  |

| Figure 9: Example Configuration File Text Editor Output | 10 |

| Figure 10: Status Bar                                   | 11 |

| Figure 11: Operating Modes Control Window               | 11 |

| Figure 12: Irq Status Indicator                         | 12 |

| Figure 13: Common Configuration Register Tab            |    |

| Figure 14: Dialog Box Error Messages                    | 13 |

| Figure 15: Modulation Mode and Shaping Options          | 14 |

| Figure 16: Transmitter Configuration Register Tab       | 14 |

| Figure 17: Receiver Configuration Register Tab          | 15 |

| Figure 18: Rx Bandwidth Window                          |    |

| Figure 19: LNA Gain Window                              | 16 |

| Figure 20: AFC / FEI Window                             | 16 |

| Figure 21: RSSI Window                                  | 17 |

| Figure 22: DAGC Window                                  | 17 |

| Figure 23: Irq & Mapping Configuration Register Tab     | 19 |

| Figure 24: Packet Handler Configuration Register Tab    | 19 |

| Figure 25: Packet Logger Window                         | 20 |

| Figure 26: Packet Log CSV File Format                   | 20 |

| Figure 27: Temperature Calibration Dialog Box           |    |

| Figure 28: Calibrated Temperature Sensor Tab            | 22 |

| Figure 29: SX1231 Registers Display Window              |    |

| Figure 30: Test Mode Window                             |    |

| Figure 31: RSSI Analyzer Window                         | 26 |

| Figure 32: RSSI Analyzer Window                         | 26 |

# **Index of Tables**

| Table 1: Continuous Mode DIO Mappings | 18 |

|---------------------------------------|----|

| Table 2: Packet Mode DIO Mappings     | 18 |

| Table 3: Packet Log Descriptors       |    |

# 1 Introduction

The SX1231 is a single-chip integrated circuit ideally suited for today's high performance ISM band RF applications. The advanced feature set, including state of the art packet engine greatly simplifies system design whilst the high level of integration reduces the external BOM to a handful of passive decoupling and matching components. It is intended for use as high-performance, low-cost FSK and OOK RF transceiver for robust frequency agile, half-duplex bi-directional RF links, and where stable and constant RF performance is required over the full operating range of the device down to 1.8V.

The SX1231 is intended for applications over a wide frequency range, including the 433 MHz and 868 MHz European and the 902-928 MHz North American ISM bands. Coupled with a link budget in excess of 135 dB, the advanced system features of the SX1231 include a 66 byte TX/RX FIFO, configurable automatic packet handler, listen mode, temperature sensor and configurable DIOs which greatly enhance system flexibility whilst at the same time significantly reducing MCU requirements.

The SX1231 complies with both ETSI and FCC regulatory requirements and is available in a 5x5 mm QFN 24 lead package

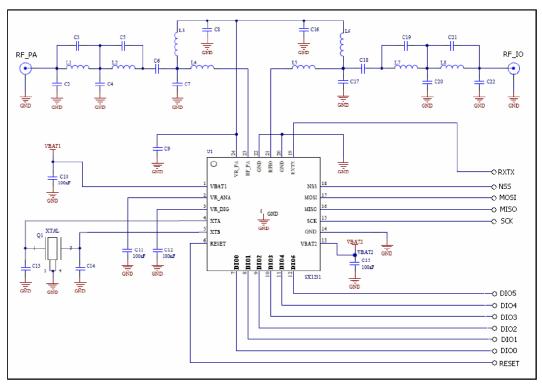

The SX1231-31SKB is a USB based evaluation tool designed to allow simple and easy evaluation of the suitability of the SX1231 for a given application. The low component count reference design implemented in the SM1231 reference design is illustrated below in Figure 1.

It I recommended that this user guide be read in conjunction with the SX1231 datasheet (http://www.semtech.com/images/datasheet/sx1231.pdf)

Figure 1: SM1231 Application Schematic

# 2 Getting Started

# 2.1 Evaluation Kit Contents

The SX1231-31SKB evaluation kit consists of:

- 2 x SM1231 modules

- 2 x USB bridge modules

- 2 x <sup>1</sup>/<sub>4</sub> wave monopole antennas

- Installation CD or insert sheet

- 2 x USB cables

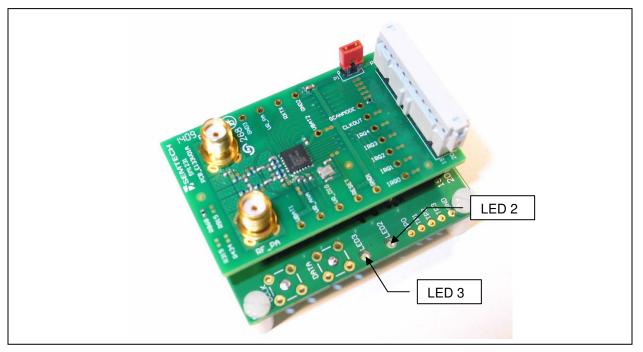

Figure 2: SM1231 Module Mounted on USB Bridge

EMTECH

#### 2.2 Installation

- 1. Put the CDROM in your computer and browse the contents of the CD, open the "sx1231starterkitsetup.exe" manually. It can be found in the \Installers sub directory of the CD-ROM

- 2. If the evaluation kit is supplied with an insert sheet, follow the instruction on the insert sheet and download the latest version of the software from the weblink provided

- 3. Follow the on-screen installation guidelines until the process is completed. Please note that .NET Framework 3.5 and the FTDI USB driver will be automatically installed if not detected on your computer

- 4. Connect one SX1231SKB board to the PC via the USB interface. The SM1231 module and USB bridge are powered via the USB

- 5. Launch "SX1231SKB" from the Start menu

- 6. Click on "Connect" button in toolbar or in File menu

- 7. SX1231SKB is now installed and ready to be used

# 2.3 SX1231SKB Overview

The SX1231SKB features the SM1231 reference design and is also interfaced via the FTDI USB Bridge to the USB type 'A' interface of a host PC.

Transmission and reception is indicated by a pair of LEDs on the USB Bridge.

# 3 SX1231 Quick Start Guide

It is recommended that this user guide is read in conjunction with the SX1231 datasheet.

- 1. Plug the SX1231SKB into the USB port of the computer. The USB power LED on the bridge should be illuminated

- 2. Run the SX1231 User Interface software: Start > All Programs > SX1231SKB > SX1231SKB

- The SX1231SKB should connect automatically to the User Interface Software. If not, click on the USB connect button, located in the top left hand corner of the window toolbar, as illustrated in Figure 4, below

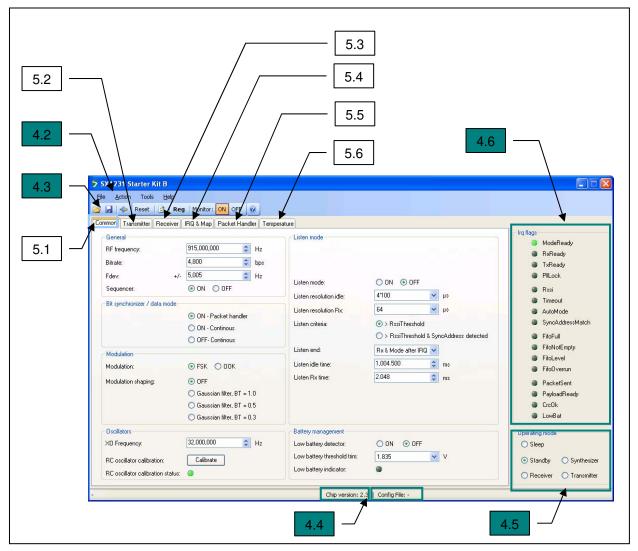

- 4. Once connected the SX1231SKB shows the default configuration of the SX1231 register settings upon power-up, as illustrated in Figure 3. If the EVK is not connected, the GUI screen is grayed out and an error message is displayed in the bottom left hand corner of the status bar.

# 4 SX1231SKB Software Description

#### 4.1 Overview

Figure 3 illustrates the SX1231SKB graphical user interface (GUI). Each of the numbered captions corresponds to a proceeding chapter within the sections which corresponds to the description of that GUI feature.

Figure 3: SX1231SKB GUI Overview

# 4.2 Menu Tool Bar

The Menu toolbar contains four drop down menus, File Menu, Action Menu, Tools Menu and Help Menu.

#### 4.2.1 File Menu

*Connect / Disconnect* allows for the connection or disconnection of the USB bridge from the host PC. This functionality may also be accessed through the short cut buttons of the Window Toolbar (see Section 4.3).

*Open Config...* allows for the opening of SX1231SKB configuration files (.cfg). This is implemented through a standard Windows file dialog box and may also be accessed through the short cut buttons of the Window Toolbar.

*Save Config* allows for SX1231SKB configuration files (.cfg) to be saved. This is implemented through a standard Windows file dialog box. The default file name is the last config file saved.

*Save Config as...* prompts for a new file name before saving, allowing for multiple configuration files to be saved and may also be accessed through the short cut buttons of the Window Toolbar.

*Exit* closes the application.

| File |                |

|------|----------------|

| -\$⊳ | Disconnect     |

| 1    | Open Config    |

|      | Save Config    |

| ۵    | Save Config As |

|      | Exit           |

Figure 4: File Menu Options

#### 4.2.2 Action Menu

*Reset* resets the SX1231 configuration registers to the recommended default values.

*Refresh* reads the status of the all registers.

*Show registers* toggles the SX1231 Registers display window and may also be accessed through the short cut buttons of the Window Toolbar. The register display window indicates the status of SX1231 configuration registers as detailed in the SX1231 datasheet. Refer to Section for further information.

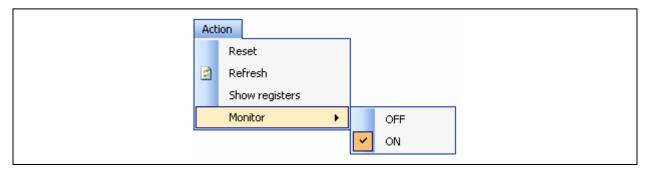

*Monitor ON* allows the GUI to constantly scan the status of the Irq registers *RegIrqFlags1* and *RegIrqFlags2* at addresses 0x27 and 0x28 respectively, and displays the status on the right hand side of the GUI (see Section 4.6 for further details). *Monitor OFF* disables the monitor function.

Figure 5: Action Menu Options

#### 4.2.3 Tools Menu

*RSSI analyzer* provides a graphical representation of the signal level at the antenna port measured within the RX filter channel bandwidth, RxBw, at the programmed RF frequency. Refer to See Section 7.4 for further details.

*Spectrum Analyzer* provides a simple spectrum analyzer function based upon RSSI level within the programmable RX filter channel bandwidth, RxBw. Please refer to Section 7.5 for further details.

|  | Тоо | ls                |

|--|-----|-------------------|

|  |     | RSSI analyser     |

|  |     | Spectrum analyser |

#### Figure 6: Tools Menu Options

#### 4.2.4 Help Menu

*Help* provides an online description of GUI commands

User's Guide... opens a PDF version of this document.

About... provides details of the GUI revision. The latest version of the SX1231 GUI can be downloaded from the Semtech website.

| <u>H</u> elp |                           |

|--------------|---------------------------|

| 🕜 Helj       | lp                        |

| Use          | er's Guide                |

| 🔁 Abo        | out SX1231 Evaluation Kit |

Figure 7: Help Menu Options

#### 4.3 Window Toolbar

The Windows Toolbar provides three buttons that provide shortcuts to some of the functions accessed from the File drop-down menu.

*Open Config* button opens a Windows file dialog box to allow access to a previously saved SX1231SKB configuration file (.cfg). Note that saved configuration files are designed to be a useful tool for embedded software development. The file can be opened in any text editor or within a spreadsheet to display the programmed register name, address and contents, as illustrated below in Figure 9.

| SX1231SKB915.cfg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | X1231SKB915.cfg - Notepad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <u>Eile Edit Format View E</u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Edit Format View Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| <pre>#Type Register N REG RegoFife 0x REG RegOpMode REG RegOpMode REG RegDataMod REG RegBitrate REG RegFreMid REG RegFreMid REG RegFrFMid REG RegFrFMid REG RegCop 0x REG RegListen2 REG RegVerSion REG RegVerSion REG RegVerSion REG RegVerSion REG RegVerSion REG Reserved14 REG Reserved15 REG Reserved15 REG Reserved15 REG Reserved15 REG RegVerVefI4 REG RegVerVefI4 REG Reserved15 REG RegVerVefI4 REG Reserved15 REG RegVerVefI4 REG RegVefI5 REG REGVEf</pre> | Performance         Address[Hex]         Value           Regiftro X000         0x000         RegoMode         0x01         0x10           RegoMode         0x01         0x10         0x00         RegoAnde         0x01         0x10           RegoAndedul         0x02         0x00         RegoAnde         0x01         0x1A         RegoAnde         0x02         0x00           RegoAndedul         0x02         0x04         0x08         0x00         RegoAnde         0x01         0x1A         RegoAnde         0x02         0x00         RegoAnde         0x02         0x00         RegoAnde         0x02         0x04         0x08         0x00         RegoAnde         0x02         0x04         0x00         RegoAnde         0x04         0x04         0x04         0x04         0x04         0x04         0x04         0x11         0x95 | re [Hex] |

Figure 9: Example Configuration File Text Editor Output

Save Config button saves and will prompt if overwriting an existing configuration file.

Connect / Disconnect button allows the user to manage manually connection and disconnection of the kit.

*Reset* resets the SX1231 configuration registers to the recommended default values.

*Refresh* reads the status of all registers.

*Register Window Toggle* toggles the SX1231 Registers display window and may also be accessed through the short cut buttons of the Window Toolbar. The register display window indicates the status of SX1231 configuration registers as detailed in the SX1231 datasheet. Refer to Section 6 for further information.

*IRQ Monitor Toggle* toggles the scanning of the status of Irq registers *RegIrqFlags1* and *RegIrqFlags2* at addresses 0x27 and 0x28 respectively, and displays the status on the right hand side of the GUI (see Section 4.6 for further details).

Help provides an online description of GUI commands.

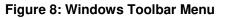

#### 4.4 Status Bar

The Status Bar provides details of the SX1231 revision version and current user configuration file. For further information concerning the IC revision, please refer to the SX1231 datasheet.

Figure 10: Status Bar

# 4.5 Operating Modes Control Box

The Operating Mode control box allows the user to change the operating mode of the SX1231 by clicking on the radio button corresponding to the desired mode. Note that the transition between modes is applied as soon as the radio button is accessed.

When the SX1231 is configured to RX operating mode LED 2 on the USB Bridge is illuminated. When the SX1231 is configured to TX mode both LED 2 and LED 3 are illuminated.

| <ul> <li>Sleep</li> <li>Standby</li> <li>Synthesizer</li> <li>Receiver</li> <li>Transmitter</li> </ul> | Operating mode             |

|--------------------------------------------------------------------------------------------------------|----------------------------|

|                                                                                                        | 🚫 Sleep                    |

| 🔘 Receiver 🔵 Transmitter                                                                               | 💿 Standby 🛛 🔿 Synthesizer  |

|                                                                                                        | 🔘 Receiver 🛛 🔿 Transmitter |

Figure 11: Operating Modes Control Window

# 4.6 Irq Status Indicator

The Irq Status Flag indicator provides an indication of the status of the Irq registers. When the indicator next to the Irq description is illuminated, the Irq condition is true.

Please refer to the SX1231 datasheet for further information and a more detailed description of the Irq register flags.

| Irq flags |              |

|-----------|--------------|

|           | Ready        |

| BxBe      |              |

| TxRe      |              |

| PILo      |              |

| Rssi      |              |

| Time      | out          |

|           | Mode         |

| Sync      | AddressMatch |

| FifoF     | ull          |

|           | otEmpty      |

| FifoL     |              |

| FifoO     | verrun       |

| Pack      | etSent       |

|           | oadReady     |

| CrcO      |              |

| Lowe      |              |

| UCWE      | jat          |

Figure 12: Irq Status Indicator

# 5 Configuration Registers Tabs

Unless otherwise stated all registers are updated as soon as they are written. It is recommended to cycle through Standby Mode when changing the contents of configuration registers.

# 5.1 Common Configuration Registers Tab

The Common Configuration Registers tab is illustrated on the following page in Figure 13. Please refer to the SX1231 for a full description of the configuration register functions.

| General                           |                             | Listen mode                 |                                          |

|-----------------------------------|-----------------------------|-----------------------------|------------------------------------------|

| RF frequency:                     | 915,000,000 🗘 Hz            |                             |                                          |

| Bitrate:                          | 4,800 🗘 bps                 |                             |                                          |

| Fdev: +/-                         | 5,005 🗘 Hz                  |                             | 0.011 0.055                              |

| Sequencer:                        | 💿 ON  🔿 OFF                 | Listen mode:                | ON ⊙ OFF 4'100 v us                      |

| Bit synchronizer / data mode-     |                             | Listen resolution idle:     |                                          |

|                                   | ON - Packet handler         | Listen resolution Rx:       | 64 μs                                    |

|                                   | ON - Continous              | Listen criteria:            | <ul> <li>&gt; RssiThreshold</li> </ul>   |

|                                   | 🔘 OFF- Continous            |                             | O > RssiThreshold & SyncAddress detected |

| Modulation                        |                             | Listen end:                 | Rx & Mode after IRQ 🔽                    |

| Modulation:                       | ⊙ FSK () 00K                | Listen idle time:           | 1,004.500 🗘 ms                           |

| Modulation shaping:               | ⊙ OFF                       | Listen Rx time:             | 2.048 🗢 ms                               |

| 1                                 | 🔘 Gaussian filter, BT = 1.0 |                             |                                          |

| -/                                | 🔘 Gaussian filter, BT = 0.5 |                             |                                          |

|                                   | 🚫 Gaussian filter, BT = 0.3 |                             |                                          |

| - Oscillators                     |                             | Battery management          |                                          |

| X0 Frequency:                     | 32,000,000 🗘 Hz             | Low battery detector:       | 🔿 DN 💿 OFF                               |

| RC oscillator calibration:        | Calibrate                   | Low battery threshold trim: | 1.835 V                                  |

| RC oscillator calibration status: |                             | Low battery indicator:      |                                          |

Figure 13: Common Configuration Register Tab

Configuration register value entries can be selected from the drop down menus within the tab or entered manually within the tab fields. Note that an invalid register entry will be highlighted by an orange background and the GUI will automatically flag a warning exclamation. A valid register entry that leads to an incorrect operating setting will result in that entry to be highlighted in red. Hovering a mouse or cursor over the warning provides an explanation for the flag, as illustrated in Figure 14.

Values entered manually that do not coincide with an exact configuration will be automatically updated by the GUI to the next valid register configuration and write that value to the appropriate configuration register.

| General       |     |             |             |                                                                       |

|---------------|-----|-------------|-------------|-----------------------------------------------------------------------|

| RF frequency: |     | 915,000,000 | 🗘 H:        | z                                                                     |

| Bitrate:      |     | 4,800       | 🗘 Бр        | ps                                                                    |

| Fdev:         | +/- | 1,160       | 🗘 Ha        | z 🟮                                                                   |

| Sequencer:    |     | 💿 ON 🔘 OFF  |             | The modulation index is out of range.<br>The valid range is [0.5, 10] |

| ⊂ General     |     |             |             |                                                                       |

| RF frequency: |     | 915,000,000 | <b>\$</b> H | Iz                                                                    |

| Bitrate:      |     | 4,800       | 🗘 bp        | ps                                                                    |

| Fdev:         | +/- | 488         | ÷H          | Iz 🕕                                                                  |

| Sequencer:    |     | 💿 ON  🔿 OFF |             | The frequency deviation is out of range.                              |

Figure 14: Dialog Box Error Messages

#### 5.1.1 Modulation Mode Window

Clicking on the OOK radio button within the Modulation window will access the modulation shaping options for the OOK modulation mode.

| ~ Modulation        |                                                                                                                                  | Modulation          |                                                                                                       |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------------------------------------------------------------------------------|

| Modulation:         | 💿 FSK 🔿 DOK                                                                                                                      | Modulation:         | 🔿 FSK 💿 OOK                                                                                           |

| Modulation shaping: | <ul> <li>OFF</li> <li>Gaussian filter, BT = 1.0</li> <li>Gaussian filter, BT = 0.5</li> <li>Gaussian filter, BT = 0.3</li> </ul> | Modulation shaping: | <ul> <li>OFF</li> <li>Filtering with fCutOff = BR</li> <li>Filtering with fCutOff = 2 * BR</li> </ul> |

Figure 15: Modulation Mode and Shaping Options

#### 5.2 Transmitter Configuration Register Tab

The Transmitter Configuration Register Tab is illustrated below in Figure 16. Please refer to the SX1231 datasheet for a full description of the configuration register functions. Configuration register value entries can be selected from the drop down menus within the tab or entered manual within the tab fields. If values are entered manually that do not coincide with an exact configuration, the GUI will automatically update the displayed value to the next valid register configuration and write that value to the appropriate configuration register.

It should be noted that the output power settings are the nominal values determined by the configuration registers and does not refer to measured output power. Please refer to the Application Information within the SX1230 datasheet for further information concerning measured output power vs. programmed power.

| Transmitter |                         |            |       |  |  |

|-------------|-------------------------|------------|-------|--|--|

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

| Powe        | er Amplifier            |            |       |  |  |

|             | ⊙ PA0 -> Transmits on   | pin RFIO   |       |  |  |

|             | O PA1 -> Transmits on   |            |       |  |  |

|             | 🔘 PA1 + PA2 -> Transi   |            |       |  |  |

| PA ra       | mp:                     | 40         | 🖌 με  |  |  |

| Outp        | ut power                |            |       |  |  |

|             |                         | 13         | ᅌ dBm |  |  |

| Over        | load current protection |            |       |  |  |

|             |                         | ⊙ ON ○ OFF |       |  |  |

| Trimo       | ning:                   | 95         | 🗢 mA  |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

|             |                         |            |       |  |  |

Figure 16: Transmitter Configuration Register Tab

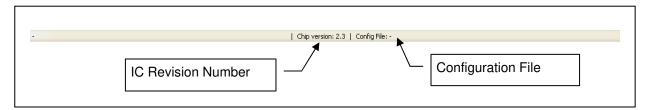

### 5.3 Receiver Configuration Register Tab

The Transmitter Configuration Register Tab is illustrated below. Please refer to the SX1231 for a full description of the configuration register functions.

Configuration register value entries can be selected from the drop down menus within the tab or entered manual within the tab fields. If values are entered manually that do not coincide with an exact configuration, the GUI will automatically update the displayed value to the next valid register configuration and write that value to the appropriate configuration register.

Figure 17: Receiver Configuration Register Tab

#### 5.3.1 Rx Bandwidth

The Rx Bandwidth, RxBw, window is illustrated below. For optimum performance in FSK mode when operating with a modulation index  $\geq$  2, the DCC frequency is recommended to be approximately 4% of the receiver bandwidth, RxBw. The GUI will automatically set the appropriate DCC frequency based upon the setting of RX filter bandwidth.

| Rx bandwidth         |        |      |

|----------------------|--------|------|

| DCC frequency:       | 414    | 🗘 Hz |

| Rx filter bandwidth: | 10,417 | 🗘 Hz |

| AFC bandwidth        |        |      |

| DCC frequency:       | 497    | 🗘 Hz |

| Rx filter bandwidth: | 50,000 | 🗘 Hz |

|                      |        |      |

Figure 18: Rx Bandwidth Window

For operation with low modulation index signals, it is recommended that the user follows the recommendations for setting the correct DCC bandwidth that can be found in the SX1231 datasheet.

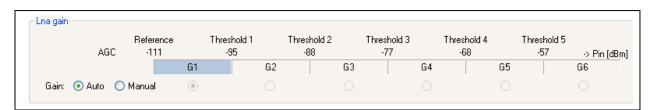

#### 5.3.2 LNA Gain Window

The LNA gain window provides the status of the configured LNA gain. The gain can be configured automatically or manually. In automatic mode the LNA gain is set based upon the RSSI value. In manual mode, the gain should be set according to the expected signal power.

Note that the AGC reference threshold is set according to:

AgcRef = [-174 + NF + 10\*log(2\*RxBw) + DemodSNR + FadingMargin]dBm

Figure 19: LNA Gain Window

#### 5.3.3 AFC / FEI

The AFC / FEI (Frequency Error Indicator) window is illustrated below. Note that when AFC is activated (either AFC auto "ON" or manually), the RF frequency in the General window of the Common Configuration Register Tab does not update, although a measure of frequency error can be obtained by clicking on the FEI Read button to verify correct AFC operation.

Enabling AFC low beta implements a double AFC function to offset the local oscillator of the SX1231 to ensure that the central tone at  $f_0$  associated with low modulation index signals is not unduly attenuated by the cut-off frequency of the DCC.

Please refer to the optimized set up for low modulation index systems section of the SX1231 datasheet for further details.

| AFC / FEI            |      |       |   |    |

|----------------------|------|-------|---|----|

| AFC low beta:        | 🔿 ON | 💿 OFF |   |    |

| AFC low beta offset: | 0    | *     |   | Hz |

| AFC auto clear:      | 🔿 ON | 💿 OFF |   |    |

| AFC auto:            | 🔿 ON | 💿 OFF |   |    |

| AFC: Start Clear     | 0    |       | ۲ | Hz |

| FEI: Read            | 0    |       | 0 | Hz |

Figure 20: AFC / FEI Window

#### 5.3.4 RSSI

The RSSI window provides access to the RSSI timeout and timeout threshold functions and enable either automatic or manual RSSI detection threshold values to be programmed. Note that the RSSI threshold (which should not be confused with the LNA or AGC threshold) can be calculated from and equates to the effective noise floor of the receiver for a given filter bandwidth.

RSSIthres = [-174 + NF + 10\*log(2\*RxBw) + DemodSNR]dBm

| RSSI               |                     |     |

|--------------------|---------------------|-----|

| Timeout Bx start:  | 0                   | ms  |

| Timeout threshold: | 0                   | ms  |

| Auto threshold:    | 💿 ON  🔿 OFF         |     |

| Threshold:         | -116.0              | dBm |

| Value:             | -127.5 🥥            | dBm |

| Phase: Restart Rx  | ) 💿 Auto i 🔘 Manual |     |

Figure 21: RSSI Window

#### 5.3.5 Continuous-Time Digital AGC

The AGC dynamic range can be enhanced in V2c silicon (chip version 2.3) with the default mode of operation of DAGC enabled. Note that the DAGC mode of operation is automatically configured by the GUI depending upon whether AFC low beta is enabled (see section 5.3.3).

Pease refer to the SX1231 datasheet for further information on the implementation of the continuous-time DAGC function.

| - DAGC |            |

|--------|------------|

| DAGC:  | 💿 ON 🔘 OFF |

|        |            |

Figure 22: DAGC Window

# 5.4 Irq & Mapping Configuration Register Tab

The Irq & Mapping Configuration Register Tab is illustrated in Figure 23. Please refer to the SX1231 for a full description of the irq and mappings for each mode of operation of the SX1231.

Configuration register value entries can be selected from the drop down menus besides each DIO listed.

Note that when necessary the GUI will automatically re-configure DIO mappings (i.e. Packet Handler operation).

Please refer to Table 1 and Table 2, below, for the available DIO mappings of the SX1231 in continuous and packet mode, respectively.

| Mode    | DIOx<br>Mapping | DIO5      | DIO4     | DIO3     | DIO2 | DIO1     | DIO0      |

|---------|-----------------|-----------|----------|----------|------|----------|-----------|

|         | 00              | -         | -        | -        | -    | -        | -         |

| Sleep   | 01              | -         | -        | -        | -    | -        | -         |

| Sleep   | 10              | LowBat    | LowBat   | AutoMode | -    | LowBat   | LowBat    |

|         | 11              | ModeReady | -        | -        | -    | -        | ModeReady |

|         | 00              | ClkOut    | -        | -        | -    | -        | -         |

| Standby | 01              | -         | -        | -        | -    | -        | -         |

| Standby | 10              | LowBat    | LowBat   | AutoMode | -    | -        | LowBat    |

|         | 11              | ModeReady | -        | -        | -    | LowBat   | ModeReady |

|         | 00              | ClkOut    | -        | -        | -    | -        | PIILock   |

| FS      | 01              | -         | -        | -        | -    | -        | -         |

| F3      | 10              | LowBat    | LowBat   | AutoMode | -    | LowBat   | LowBat    |

|         | 11              | ModeReady | PIILock  | -        | -    | PIILock  | ModeReady |

|         | 00              | ClkOut    | Timeout  | Rssi     | Data | Dclk     | SyncAddr  |

| RX      | 01              | Rssi      | RxReady  | RxReady  | Data | RxReady  | Timeout   |

|         | 10              | LowBat    | SyncAddr | AutoMode | Data | LowBat   | Rssi      |

|         | 11              | ModeReady | PIILock  | Timeout  | Data | SyncAddr | ModeReady |

|         | 00              | ClkOut    | TxReady  | TxReady  | Data | Dclk     | PIllock   |

| ТХ      | 01              | ClkOut    | TxReady  | TxReady  | Data | LowBat   | TxReady   |

|         | 10              | LowBat    | LowBat   | AutoMode | Data | LowBat   | LowBat    |

|         | 11              | ModeReady | PIILock  | TxReady  | Data | PIILock  | ModeReady |

#### Table 1: Continuous Mode DIO Mappings

| Mode    | DIOx<br>Mapping | DIO5      | DIO4      | DIO3     | DIO2         | DIO1         | DIO0         |

|---------|-----------------|-----------|-----------|----------|--------------|--------------|--------------|

|         | 00              | -         | -         | FifoFull | FifoNotEmpty | FifoLevel    | -            |

| Sleep   | 01              | -         | -         | -        | -            | FifoFull     | -            |

| Sleep   | 10              | LowBat    | LowBat    | LowBat   | LowBat       | FifoNotEmpty | LowBat       |

|         | 11              | ModeReady | -         | -        | AutoMode     | -            | -            |

|         | 00              | Clkout    | -         | FifoFull | FifoNotEmpty | FifoLevel    | -            |

| Standby | 01              | -         | -         | -        | -            | FifoFull     | -            |

| Standby | 10              | LowBat    | LowBat    | LowBat   | LowBat       | FifoNotEmpty | LowBat       |

|         | 11              | ModeReady | -         | -        | AutoMode     | -            | -            |

|         | 00              | Clkout    | -         | FifoFull | FifoNotEmpty | FifoLevel    | -            |

| FS      | 01              | -         | -         | -        | -            | FifoFull     | -            |

| 10      | 10              | LowBat    | LowBat    | LowBat   | LowBat       | FifoNotEmpty | LowBat       |

|         | 11              | ModeReady | PIILock   | PIILock  | AutoMode     | PIILock      | PIILock      |

|         | 00              | Clkout    | Timeout   | FifoFull | FifoNotEmpty | FifoLevel    | CrcOk        |

| RX      | 01              | Data      | Rssi      | Rssi     | Data         | FifoFull     | PayloadReady |

|         | 10              | LowBat    | RxReady   | SyncAddr | LowBat       | FifoNotEmpty | SyncAddr     |

|         | 11              | ModeReady | PIILock   | PIILock  | AutoMode     | Timeout      | Rssi         |

|         | 00              | Clkout    | ModeReady | FifoFull | FifoNotEmpty | FifoLevel    | PacketSent   |

| тх      | 01              | Data      | TxReady   | TxReady  | Data         | FifoFull     | TxReady      |

|         | 10              | LowBat    | LowBat    | LowBat   | LowBat       | FifoNotEmpty | LowBat       |

|         | 11              | ModeReady | PIILock   | PIILock  | AutoMode     | PLLlock      | PIILock      |

Table 2: Packet Mode DIO Mappings

| Device status         Bit Synchronizer:       ON         Data mode:       Packet         Operating mode:       Receiver         DIO mapping       DIO105:         DIO2:       ClkOut         DIO3:       FifoFull         DIO2:       FifoNotEmpty         DIO1:       FifoLevel         DIO0:       CrcOk         Clock out       Trequency:         DFF<       Hz | <br>RQ & Map  |                |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|--|

| Bit Synchronizer: ON   Data mode: Packet   Operating mode: Receiver     DIO mapping   DIO5: ClkOut ♥   DIO4: Timeout ♥♥   DIO3: FifoFull ♥   DIO2: FifoNetEmpty ♥   DIO1: FifoLevel ♥   DIO0: CrcOk ♥                                                                                                                                                               |               |                |  |

| Bit Synchronizer: ON   Data mode: Packet   Operating mode: Receiver     DIO mapping   DIO5: ClkOut ♥   DIO4: Timeout ♥♥   DIO3: FifoFull ♥   DIO2: FifoNetEmpty ♥   DIO1: FifoLevel ♥   DIO0: CrcOk ♥                                                                                                                                                               |               |                |  |

| Data mode: Packet   Operating mode: Receiver     DIO mapping   DIO5: ClkOut ♥   DIO4: Timeout ♥   DIO3: FifoFull ♥   DIO2: FifoNotEmpty ♥   DIO1: FifoLevel ♥   DIO0: CrcOk ♥                                                                                                                                                                                       | Device status |                |  |

| Operating mode:       Receiver         DIO mapping       DIO5:         DIO5:       ClkOut          DIO4:       Timeout          DIO3:       FifoFull          DIO2:       FifoNotEmpty          DIO1:       FifoLevel          DIO0:       CrcOk                                                                                                                    |               |                |  |

| DI0 mapping         DI05:       ClkOut         DI04:       Timeout         DI03:       FifoFull         DI02:       FifoNotEmpty         DI01:       FifoLevel         DI00:       CrcOk                                                                                                                                                                            |               |                |  |

| DID4: Timeout<br>DID3: FifoFull<br>DID2: FifoNotEmpty<br>DID1: FifoLevel<br>DID0: CrcDk<br>Clock out                                                                                                                                                                                                                                                                |               |                |  |

| DI03: FifoFull v<br>DI02: FifoNotEmpty v<br>DI01: FifoLevel v<br>DI00: CrcOk v                                                                                                                                                                                                                                                                                      | DI05:         | ClkOut 🖌       |  |

| DIO2: FifoNotEmpty v<br>DIO1: FifoLevel v<br>DIO0: CrcOk v                                                                                                                                                                                                                                                                                                          | DIO4:         | Timeout 🗸      |  |

| DI01: FifoLevel V<br>DI00: CrcOk V                                                                                                                                                                                                                                                                                                                                  | DI03:         | FifoFull 🗸     |  |

| DIOD: CrcOk V                                                                                                                                                                                                                                                                                                                                                       | DI02:         | FifoNotEmpty 🔽 |  |

| Clock out                                                                                                                                                                                                                                                                                                                                                           | DIO1:         | FifoLevel 🔽    |  |

|                                                                                                                                                                                                                                                                                                                                                                     | DIO0:         | CrcOk 🔽        |  |

| Frequency: OFF Mz                                                                                                                                                                                                                                                                                                                                                   | Clock out     |                |  |

|                                                                                                                                                                                                                                                                                                                                                                     | Frequency:    | OFF 🖌 Hz       |  |

|                                                                                                                                                                                                                                                                                                                                                                     |               |                |  |

|                                                                                                                                                                                                                                                                                                                                                                     |               |                |  |

|                                                                                                                                                                                                                                                                                                                                                                     |               |                |  |

Figure 23: Irq & Mapping Configuration Register Tab

# 5.5 Packet Handler Configuration Register Tab

The Packet Handler Configuration Register Tab is shown below. Please refer to the SX1231 for a full description of the packet engine message format and operation of the SX1231.

| 5.5.1 | _                        | Packet Handle                         | 91         |                           |          |                                         |       |

|-------|--------------------------|---------------------------------------|------------|---------------------------|----------|-----------------------------------------|-------|

| 0.0.1 | Preamble size:           | 3                                     | bytes      | Address based filtering:  | 📀 OFF    | Node ONode or Broadcast                 |       |

|       | Sync word:               | 💿 ON  🔿 OFF                           |            | Node address:             | 0        | © 0x00                                  |       |

|       | FIFO fill condition:     | 💿 Sync address 🔵 Alway                | s          | Broadcast address:        | 0        | \$ 0x00                                 |       |

|       | Sync word size:          | 4                                     | bytes      | DC-free:                  | 📀 OFF    | O Manchester O Whitening                |       |

|       | Sync word tolerance:     | 0                                     | bits       | CRC calculation:          | 💿 ON     | ○ OFF                                   |       |

|       | Sync word value:         | 01-01-01-01                           |            | CRC auto clear:           | 📀 ON     | O OFF                                   |       |

|       | Packet format:           | 🔿 Variable 💿 Fixed                    |            | AES:                      | 🔿 ON     | ⊙ OFF                                   |       |

|       | Payload length:          | 20 🛟 0x14                             | bytes      | AES key:                  | 00-00    | 0-00-00-00-00-00-00-00-00-00-00-00-00-0 |       |

|       | Intermediate mode enter: | None ( Auto Modes OFF )               | ~          | Tix start:                | 🔘 FifoLo | evel 💿 FifoNotEmpty                     |       |

|       | Intermediate mode exit:  | None ( Auto Modes OFF )               | ~          | FIFO Threshold:           | 15       | \$                                      |       |

|       | Intermediate mode:       | Sleep                                 | ~          | Inter packet Rx delay:    | 0.208    | ▼ ms                                    |       |

| 5.5.2 | Packet                   |                                       |            |                           |          | C Device status                         |       |

|       | Preamble                 | Sync Lengt                            | th NodeAdd | lress Message             | CRC      | Bit Synchronizer: ON                    |       |

|       | 55-55-55                 | 01-01-01-01                           |            |                           | AD-F8    | Data mode: Packet                       | 5.5.3 |

|       | Message                  |                                       |            |                           |          | Operating mode: Receiver                | 5.5.5 |

|       |                          | HEXADECIMAL<br>3 68 20 54 65 73 74 20 | 50 61 79   | ASCII<br>Semtech Test Pay |          | Start Log                               |       |

|       | 6C 6F 61 64              |                                       |            | load                      | -        | Rx packets: 0                           |       |

|       |                          |                                       |            |                           | ~        |                                         |       |

|       | 0                        |                                       |            |                           |          |                                         | l     |

Figure 24: Packet Handler Configuration Register Tab

#### 5.5.1 Sync Word

For correct packet mode operation, the sync word needs to be set to at least one byte. Note that 0x00 can not be set as for the first byte of the sync word. The GUI will prompt with an error message should the user attempt to set 0x00 in the first byte of the sync word.

#### 5.5.2 AutoMode Operation

Auto Modes defines the enter conditions to start the packet handler and exit conditions to terminate packet handler operation, as defined in the SX1231 datasheet.

#### 5.5.3 Packet Log

Clicking on the Log button within the Control Window enables the payload logging function, available in both TX and RX modes whenever the Packet Handler is enabled.

|            | <b>5</b> Packet Log                   |             |

|------------|---------------------------------------|-------------|

| Status Bar | Log control<br>Max samples:<br>Browse | 10<br>Start |

Figure 25: Packet Logger Window

In the Packet Logger window enter the number of packets to be logged and press the Start button. Then press the Start button in the Control Window of the main Packet Handler Tab to start packet transmission or reception. When the status bar indicates full, the log can be saved by clicking on the Browse button.

The log file can be viewed in Notepad or opened in Excel as a .CSV file

|        | Mic | rosoft E            | kcel - | sx123   | 1-pkt             |        |                             |                  |                |              |                                                             |       | X   |

|--------|-----|---------------------|--------|---------|-------------------|--------|-----------------------------|------------------|----------------|--------------|-------------------------------------------------------------|-------|-----|

|        | E   | ile <u>E</u> dit    | ⊻iew   | Inser   | t F <u>o</u> rmat | Tools  | <u>D</u> ata <u>W</u> indow | <u>H</u> elp Ado | <u>b</u> e PDF |              | Type a question for help                                    | 8     | ×   |

| D      |     | ¥ 🖬 🕯               | 3 Q.   | HBC I   | n + 🎑             | Σ.     | 21 M. 2                     | » Arial          |                | • 10 • H     | Ⅰ U 三三三國 \$ %,% \$ \$ \$ \$ # #                             | » - A | ÷ . |

|        |     | <b>-</b> 1 <b>S</b> |        |         |                   |        |                             |                  |                |              |                                                             | _     |     |

| e le j |     | G17                 | ÷      | ß       |                   |        |                             |                  |                |              |                                                             |       |     |

|        | A   | В                   | С      | D       | Е                 | F      | G                           | Н                | Ţ              | J            | К                                                           | L     | -   |

| 1      | #   | SX1231              | packe  | t log g | enerated f        | he 1/2 | 5/2011 at 05:46             | PM               |                |              |                                                             |       | -   |

| 2      | #   |                     |        | Rssi    | Pkt Max           | Pkt #  | Preamble Size               | Sync             |                | Node Address |                                                             | CRC   |     |

| 3      |     | 46:52.3             | Тх     |         | 10                | 0      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 |     |

| 4      |     | 46:52.4             | Тх     |         | 10                | 1      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 |     |

| 5      |     | 46:52.5             | Тх     | 1       | 10                | 2      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 |     |

| 6      |     | 46:52.6             | Тх     |         | 10                | 3      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 |     |

| 7      |     | 46:52.7             | Тx     |         | 10                | 4      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 | T   |

| 8      |     | 46:52.8             | Тх     |         | 10                | 5      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 | Π., |

| 9      |     | 46:53.0             | Тх     |         | 10                | 6      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 |     |

| 10     |     | 46:53.1             | Тх     |         | 10                | 7      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 | T   |

| 11     |     | 46:53.2             | Тх     |         | 10                | 8      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 | Τ   |

| 12     |     | 46:53.3             | Тх     |         | 10                | 9      | 3                           | 01-01-01-01      | 14             |              | 53-65-6D-74-65-63-68-20-54-65-73-74-20-50-61-79-6C-6F-61-64 | AD-F8 | Ť   |

| 13     |     |                     |        |         |                   |        |                             |                  |                |              |                                                             |       | Τ.  |

| H -    | • 1 | H SX                | L231-j | okt /   |                   |        |                             |                  |                |              |                                                             | •     | 1   |

| Rea    | dy  |                     |        |         |                   |        |                             |                  |                |              | NUM                                                         |       |     |

Figure 26: Packet Log CSV File Format

| Packet Log Parameter | Description                                                         |

|----------------------|---------------------------------------------------------------------|

| Time                 | Local (CPU) timestamp in MM:SS.S format for TX / RX packets         |

| Mode                 | SX1231 Packet Mode                                                  |

| RSSI                 | Indicated RSSI level (RX mode only)                                 |

| Pkt Max              | Number of repeated packets set in GUI Control Window (0 = infinite) |

| Pkt #                | Transmitted or received packet number                               |

| Preamble Size        | Size of transmitted or received preamble sequence                   |

| Sync                 | Sync Address                                                        |

| Length               | Payload length of TX / RX packet                                    |

| Node Address         | node Address (optional)                                             |

| Message              | Transmitted / received packet (can be viewed in GUI Message Window) |

| CRC                  | Transmitted / received CRC (optional)                               |

#### **Table 3: Packet Log Descriptors**

#### 5.5.4 Packet Handler GUI Limitations

When operating the packet handler via the SKB GUI, the user should be aware of the following limitations associated with the GUI:

- Minimum Preamble Size = 2 bytes

- Maximum Packet Length = 66 bytes (64 bytes of data + Length byte + Address byte)

# 5.6 Temperature Configuration Register Tab

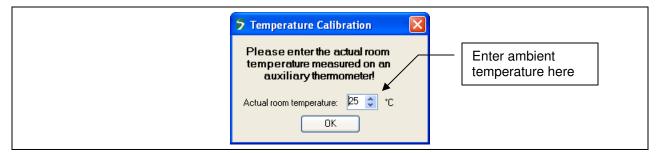

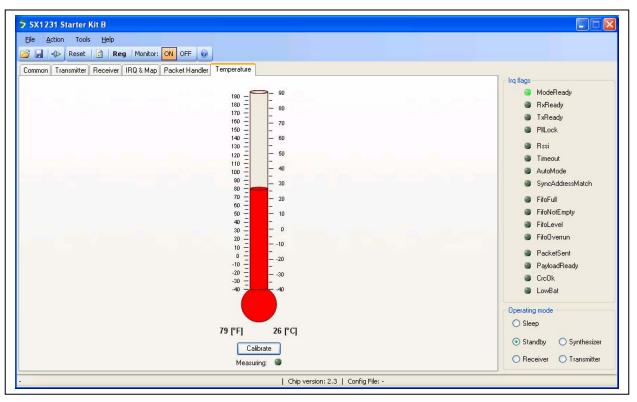

The Temperature Configuration Register Tab is illustrated below in Figure 28. Note that user is prompted to calibrate the SX1231 temperature sensor by clicking on the Calibrate button to access the temperature calibration dialog box.

Figure 27: Temperature Calibration Dialog Box

When the temperature sensor has been calibrate the temperature, as computed by the SX1231, will be displayed, as illustrated in Figure 28.

Figure 28: Calibrated Temperature Sensor Tab

# 6 Registers Display Window

As outlined in Section 4.2.3 the SX1231 GUI has a show registers utility that, when enabled from either the Menu or Windows toolbar, provides details of the status of all configuration registers that are documented in the SX1231 datasheet.

Whenever the contents of a register are changed in the main GUI window, the corresponding register displays the new contents of the register(s), highlighting changed contents in red for a period of approximately 5 seconds before reverting back to black.

The register window is displayed below in Figure 29. It can be noted that in this example, the contents of RegOpMode at Addr 0x01 have changed to 0x10, indicating that the SX1231 has been set to Receiver Mode operation.

| Register      | Addr | Value | Register       | Addr | Value | Register         | Addr | Value | Register         | Addr | Value | Register    | Addr | Value |

|---------------|------|-------|----------------|------|-------|------------------|------|-------|------------------|------|-------|-------------|------|-------|

| RegFifo       | 0x00 | 0x00  | Reserved14     | 0x14 | 0x40  | RegirqFlags2     | 0x28 | 0x00  | RegFifoThresh    | 0x3C | 0x8F  | RegTestLna  | 0x58 | 0x1B  |

| RegOpMode     | 0x01 | 0x10  | Reserved15     | 0x15 | 0xB0  | RegRssiThresh    | 0x29 | 0xE4  | RegPacketConfig2 | 0x3D | 0x02  | RegTestDagc | 0x6F | 0x30  |

| RegDataModul  | 0x02 | 0x00  | Reserved16     | 0x16 | 0x7B  | RegRxTimeout1    | 0x2A | 0x00  | RegAesKey1       | 0x3E | 0x00  | RegTestAlic | 0x71 | 0x00  |

| RegBitrateMsb | 0x03 | 0x1A  | Reserved17     | 0x17 | 0x9B  | RegRxTimeout2    | 0x2B | 0x00  | RegAesKey2       | 0x3F | 0x00  |             |      |       |

| RegBitrateLsb | 0x04 | 0x0B  | RegLna         | 0x18 | 0x88  | RegPreambleMsb   | 0x2C | 0x00  | RegAesKey3       | 0x40 | 0x00  |             |      |       |

| RegFdevMsb    | 0x05 | 0x00  | RegRxBw        | 0x19 | 0x55  | RegPreambleLsb   | 0x2D | 0x03  | RegAesKey4       | 0x41 | 0x00  |             |      |       |

| RegFdevLsb    | 0x06 | 0x52  | RegAfc8w       | 0x1A | 0x8B  | RegSyncConfig    | 0x2E | 0x98  | RegAesKey5       | 0x42 | 0x00  |             |      |       |

| RegFrfMsb     | 0x07 | 0xE4  | Reg0okPeak     | 0x1B | 0x40  | RegSyncValue1    | 0x2F | 0x01  | RegAesKey6       | 0x43 | 0x00  |             |      |       |

| RegFrfMid     | 0x08 | 0xC0  | RegOokAvg      | 0x1C | 0x80  | RegSyncValue2    | 0x30 | 0x01  | RegAesKey7       | 0x44 | 0x00  |             |      |       |

| RegFrfLsb     | 0x09 | 0x00  | RegOokFix      | 0x1D | 0x06  | RegSyncValue3    | 0x31 | 0x01  | RegAesKey8       | 0x45 | 0x00  |             |      |       |

| RegOsc1       | 0x0A | 0x41  | RegAfcFei      | 0x1E | 0x10  | RegSyncValue4    | 0x32 | 0x01  | RegAesKey9       | 0x46 | 0x00  |             |      |       |

| RegAfcCtd     | 0x0B | 0x40  | RegAfcMsb      | 0x1F | 0x00  | RegSyncValue5    | 0x33 | 0x01  | RegAesKey10      | 0x47 | 0x00  |             |      |       |

| RegLowBat     | 0x0C | 0x02  | RegAfcLsb      | 0x20 | 0x00  | RegSyncValue6    | 0x34 | 0x01  | RegAesKey11      | 0x48 | 0x00  |             |      |       |

| RegListen1    | 0x0D | 0x92  | RegFeiMsb      | 0x21 | 0x00  | RegSyncValue7    | 0x35 | 0x01  | RegAesKey12      | 0x49 | 0x00  |             |      |       |

| RegListen2    | 0x0E | 0xF5  | RegFeiLsb      | 0x22 | 0x00  | RegSyncValue8    | 0x36 | 0x01  | RegAesKey13      | 0x4A | 0x00  |             |      |       |

| RegListen3    | 0x0F | 0x20  | RegRssiConfig  | 0x23 | 0x00  | RegPacketConfig1 | 0x37 | 0x10  | RegAesKey14      | 0x4B | 0x00  |             |      |       |

| RegVersion    | 0x10 | 0x23  | RegRssiValue   | 0x24 | 0xC8  | RegPayloadLength | 0x38 | 0x42  | RegAesKey15      | 0x4C | 0x00  |             |      |       |

| RegPaLevel    | 0x11 | 0x9F  | RegDioMapping1 | 0x25 | 0x00  | RegNodeAdrs      | 0x39 | 0x00  | RegAesKey16      | 0x4D | 0x00  |             |      |       |

| RegPaRamp     | 0x12 | 0x09  | RegDioMapping2 | 0x26 | 0x07  | RegBroadcastAdrs | 0x3A | 0x00  | RegTemp1         | 0x4E | 0x01  |             |      |       |

| RegOcp        | 0x13 | 0x1A  | RegirgFlags1   | 0x27 | 0xD8  | RegAutoModes     | 0x3B | 0x00  | RegTemp2         | 0x4F | 0x8C  |             |      |       |

Figure 29: SX1231 Registers Display Window

# 7 Advanced Operating Modes

# 7.1 Packet Communications Test

To configure the SX1231 to enable a wireless packet communications transfer, follow the procedure outlined below:

#### 7.1.1 Transmitter Mode Configuration

- 1. Ensure that the SX1231 is in Standby operating Mode

- 2. Configure the SX1231 Common and Transmitter Configuration Registers

- 3. Configure the Packet Handler Registers for the payload you wish to transmit. The payload can be entered within the Message Window in either hexadecimal or ASCII format. Note that the packet can be configured with Address and / or Broadcast nodes enabled or disabled; DC-free mechanisms, CRC and / or AES may also be selected. The only limitation is that he maximum payload size for the purposes of GUI operation is 66 bytes

- 4. Click on the Transmitter radio button from within the Operating Mode Window and set the Repeat value from within the Control Window of the Packet Handler Tab. It is recommended for initial analysis that Repeat value is set to "0" (packet transmission repeat until manually stopped)

- 5. Click on the Start button within the Control Window of the Packet Handler Tab to start the Transmitter

- 6. The TX packet counter will commence to increment as the SX1231 repeatedly transmits the payload

#### 7.1.2 Receiver Mode Configuration

- 1. Ensure that the SX1231 is in Standby operating Mode

- 2. Configure the SX1231 Common and Receiver Configuration Registers. The Common configuration should be identical to that of the SX1231 configured as the transmitter. The Receiver filter BW configuration should be consistent with the signal parameters. It is recommended that the configuration of the transmitter module is used as a template

- 3. Configure the Packet Handler Registers for the payload you wish receive. Note that the packet can be configured with Address and / or Broadcast nodes enabled or disabled; DC-free mechanisms, CRC and / or AES may also be selected. The packet handler parameters must be identical for those selected for the transmitter for correct operation. The only limitation is that he maximum payload size for the purposes of GUI operation is 66 bytes

- 4. Click on the Receiver radio button from within the Operating Mode Window and set the Repeat value from within the Control Window of the Packet Handler Tab

- 5. Click on the Start button within the Control Window of the Packet Handler Tab to start the Receiver

- 6. The RX packet counter will commence to increment for each valid packet reception

# 7.2 Test Mode Window

The Test Mode window is accessed by depressing the <CTRL>+<ALT>+<T> keys of the PC keyboard simultaneously, and is illustrated below in Figure 30.

This window allows the user to write to and read from the contents of individual configuration register addresses. Note that address and data are entered in hexadecimal format.

The Antenna switch control dialog box enables control of the antenna diversity switch for the SX1231 antenna diversity reference design

| 5 Test               |                                                                                                                                                                         |