Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **ADVANCED COMMUNICATIONS & SENSING**

#### **GENERAL DESCRIPTION**

The SX8662 is an ultra low power, fully integrated 12-channel solution for capacitive touch-button matrix applications (up to 36 keys). Unlike many capacitive touch solutions, the SX8662 features dedicated capacitive sense inputs (that requires no external components) in addition to 8 general purpose I/O ports (GPIO) which can be used to drive up to 36 matrix LEDs (i.e. one per key). Each of the on-chip GPIO/LED driver is equipped with independent PWM source for enhanced visual effect such as dimming, and breathing.

The SX8662 includes a capacitive 10 bit ADC analog interface with automatic compensation up to 100pF. The high resolution capacitive sensing supports a wide variety of touch pad sizes and shapes and allows capacitive buttons to be created using thick overlay materials (up to 5mm) for an extremely robust and ESD immune system design.

The SX8662 incorporates a versatile firmware that was specially designed to simplify capacitive touch solution design and offers reduced time-to-market. Integrated multi-time programmable memory provides the ultimate flexibility to modify key firmware parameters (gain, threshold, scan period, auto offset compensation) in the field without the need for new firmware development.

The SX8662 supports the 400 kHz I<sup>2</sup>C serial bus data protocol and includes a field programmable slave address. The tiny 5mm x 5mm footprint makes it an ideal solution for portable, battery powered applications where power and density are at a premium.

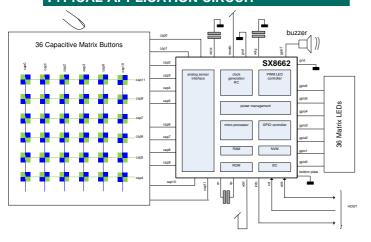

#### TYPICAL APPLICATION CIRCUIT

#### **KEY PRODUCT FEATURES**

- ♦ Complete Capacitive Touch-Button Solution

- o Up to 36 Matrix Buttons

- Up to 36 LEDs Control for individual Visual Feedback with Auto Lightening

- o Configurable Single or Continuous Fading Mode

- o 256 steps PWM Linear and Logarithmic control

- ♦ High Resolution Capacitive Sensing

- Up to 100pF of Offset Cap. Compensation at Full Sensitivity

- o Capable of Sensing up thru 5mm thick Overlay Materials

- Support of buzzer for audible feedback

- ♦ User-selectable Button Reporting Configuration

- ♦ Extremely Low Power

- o 8uA (typ) in Sleep Mode

- o 100uA (typ) in Doze Mode (195ms)

- o 460uA (typ) in Active Mode (30ms)

- ♦ Programmable Scanning Period from 15ms to several seconds

- ♦ Auto Offset Compensation

- Eliminates false triggers due to environmental factors (temperature, humidity)

- o Initiated on power-up and configurable intervals

- Multi-Time In-Field Programmable Firmware Parameters for Ultimate Flexibility

- On-chip user programmable memory for fast, self contained start-up

- ♦ No External Components per Sensor Input

- ♦ Internal Clock Requires No External Components

- ♦ Differential Sensor Sampling for Reduced EMI

- ♦ Optional 400 KHz I<sup>2</sup>C Interface with Programmable Address

- ♦ -40°C to +85°C Operation

#### **APPLICATIONS**

- Home Automation

- ♦ White Goods

- Printers

- ♦ Notebook/Netbook/Portable/Handheld computers

- ♦ Consumer Products, Instrumentation, Automotive

- ♦ Mechanical Button Replacement

#### ORDERING INFORMATION

| Part Number                  | Temperature<br>Range | Package            |  |  |  |

|------------------------------|----------------------|--------------------|--|--|--|

| SX8662I08AWLTRT <sup>1</sup> | -40℃ to +85℃         | Lead Free MLPQ-W32 |  |  |  |

<sup>1 3000</sup> Units/reel

<sup>\*</sup> This device is RoHS/WEEE compliant and Halogen Free

## **Table of Contents**

| GENERA                          | L DESCRIPTION                    |                     | 1               |

|---------------------------------|----------------------------------|---------------------|-----------------|

| TYPICAL                         | APPLICATION CIRCUIT              |                     | 1               |

| KEY PRO                         | DOUCT FEATURES                   |                     | 1               |

| APPLICA                         | TIONS                            |                     | 1               |

| ORDERIN                         | NG INFORMATION                   |                     | 1               |

| 1 GE                            | NERAL DESCRIPTION                |                     | 4               |

| 1.1                             | Pin Diagram                      |                     | 4               |

| 1.2                             | Marking information              |                     | 4               |

| 1.3                             | Pin Description                  |                     | 5               |

| 1.4                             | Simplified Block Diagram         |                     | 6               |

| 1.5                             | Acronyms                         |                     | 6               |

| 2 EL                            | ECTRICAL CHARACTERIST            | rics                | 7               |

| 2.1                             | Absolute Maximum Rating          | gs                  | 7               |

| 2.2                             | Recommended Operating            | Conditions          | 7               |

| 2.3                             | <b>Thermal Characteristics</b>   |                     | 7               |

| 2.4                             | <b>Electrical Specifications</b> |                     | 8               |

| 3 FU                            | NCTIONAL DESCRIPTION             |                     | 10              |

| 3.1                             | Introduction                     |                     | 10              |

| 3.1                             |                                  |                     | 10              |

| 3.1<br>3.1                      |                                  |                     | 10<br>10        |

| 3.2                             | Scan Period                      |                     | 10<br>10        |

| 3.3                             | Operation modes                  |                     | 11              |

| 3.4                             | Sensors on the PCB               |                     | 12              |

| 3.4                             |                                  | IK)                 | 12              |

| 3.4                             |                                  |                     | 12              |

| 3.4                             |                                  |                     | 12              |

| 3.5                             | Button Information (MK a         | nd PK)              | 14              |

| 3.6                             | Analog Sensing Interface         |                     | 14              |

| 3.7                             | Offset Compensation              |                     | 16              |

| 3.8                             | Processing                       |                     | 17              |

| 3.9                             | Configuration                    |                     | 17              |

| 3.10                            | Power Management                 |                     | 19              |

| 3.11                            | Clock Circuitry                  |                     | 19              |

| 3.12                            | I2C interface                    |                     | 19              |

| <b>3.13</b><br>3.13             | Interrupt<br>3.1 Power up        |                     | <b>20</b><br>20 |

| 3.1                             |                                  |                     | 20              |

| 3.1                             | <u> </u>                         |                     | 20              |

| 3.1                             | •                                |                     | 21              |

| <b>3.14</b><br>3.1 <sub>1</sub> | Reset<br>4.1 Power up            |                     | <b>21</b><br>21 |

| 3.1                             | 4.2 RESETĖ                       |                     | 22              |

|                                 | August 2011                      | © 2011 Semtech Corp | www.semtech.com |

| Α | DVAN         | NCED COMMUNICATIONS & SENSING     |                  |

|---|--------------|-----------------------------------|------------------|

|   | 3.14         | 4.3 Software Reset                | 22               |

|   | 3.15         | General Purpose Input and Outputs | 23               |

|   | 3.15         |                                   | 23               |

|   | 3.15         |                                   | 25               |

|   | 3.15<br>3.15 |                                   | 26<br>27         |

| 4 |              | DESCRIPTIONS                      |                  |

| • | 4.1          |                                   | _                |

|   | 4.1          | Introduction ASI pins             | 28<br>28         |

|   | 4.2          | Host interface pins               | 29               |

|   | 4.4          | Power management pins             | 32               |

|   | 4.5          | General purpose IO pins           | 33               |

|   |              |                                   |                  |

| 5 | DE           | TAILED CONFIGURATION DESCRIPTIONS | 34               |

|   | 5.1          | Introduction                      | 34               |

|   | 5.2          | General Parameters                | 37               |

|   | 5.3          | Capacitive Sensors Parameters     | 38               |

|   | 5.4          | Buttons (MK and PK) Parameters    | 40               |

|   | 5.5          | Buzzer Parameters                 | 43               |

|   | 5.6          | GPIO Parameters                   | 44               |

| 6 | I2C          | INTERFACE                         | 47               |

|   | 6.1          | I2C Write                         | 47               |

|   | 6.2          | I2C read                          | 48               |

|   | 6.3          | I2C Registers Overview            | 49               |

|   | 6.4          | Status Registers                  | 50               |

|   | 6.5          | Control Registers                 | 52               |

|   | 6.6          | SPM Gateway Registers             | 53               |

|   | 6.6.         | I I                               | 54<br>55         |

|   | 6.6.         | 2 SPM Read Sequence  NVM burn     | 55<br><b>5</b> 6 |

|   | 6.7          | NVM DUTI                          | 56               |

| 7 | API          | PLICATION INFORMATION             | 57               |

| 8 | REI          | FERENCES                          | 58               |

| 9 | PAG          | CKAGING INFORMATION               | 59               |

|   | 9.1          | Package Outline Drawing           | 59               |

|   | 9.2          | Land Pattern                      | 59               |

# 1 GENERAL DESCRIPTION

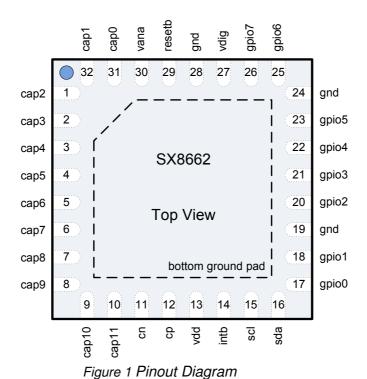

## 1.1 Pin Diagram

## 1.2 Marking information

yyww = Date Code xxxxxx = Semtech lot number R08 = Semtech Code

Figure 2 Marking Information

# 1.3 Pin Description

| Number       | Name   | Туре                 | Description                                                            |

|--------------|--------|----------------------|------------------------------------------------------------------------|

| 1            | CAP2   | Analog               | Capacitive Sensor 2                                                    |

| 2            | CAP3   | Analog               | Capacitive Sensor 3                                                    |

| 3            | CAP4   | Analog               | Capacitive Sensor 4                                                    |

| 4            | CAP5   | Analog               | Capacitive Sensor 5                                                    |

| 5            | CAP6   | Analog               | Capacitive Sensor 6                                                    |

| 6            | CAP7   | Analog               | Capacitive Sensor 7                                                    |

| 7            | CAP8   | Analog               | Capacitive Sensor 8                                                    |

| 8            | CAP9   | Analog               | Capacitive Sensor 9                                                    |

| 9            | CAP10  | Analog               | Capacitive Sensor 10                                                   |

| 10           | CAP11  | Analog               | Capacitive Sensor 11                                                   |

| 11           | CN     | Analog               | Integration Capacitor, negative terminal (1nF between CN and CP)       |

| 12           | СР     | Analog               | Integration Capacitor, positive terminal (1nF between CN and CP)       |

| 13           | VDD    | Power                | Main input power supply                                                |

| 14           | INTB   | Digital Output       | Interrupt, active LOW, requires pull up resistor (on host or external) |

| 15           | SCL    | Digital Input        | I2C Clock, requires pull up resistor (on host or external)             |

| 16           | SDA    | Digital Input/Output | I2C Data, requires pull up resistor (on host or external)              |

| 17           | GPIO0  | Digital Input/Output | General Purpose Input/Output 0                                         |

| 18           | GPIO1  | Digital Input/Output | General Purpose Input/Output 1                                         |

| 19           | GND    | Ground               | Ground                                                                 |

| 20           | GPIO2  | Digital Input/Output | General Purpose Input/Output 2                                         |

| 21           | GPIO3  | Digital Input/Output | General Purpose Input/Output 3                                         |

| 22           | GPIO4  | Digital Input/Output | General Purpose Input/Output 4                                         |

| 23           | GPIO5  | Digital Input/Output | General Purpose Input/Output 5                                         |

| 24           | GND    | Ground               | Ground                                                                 |

| 25           | GPIO6  | Digital Input/Output | General Purpose Input/Output 6                                         |

| 26           | GPIO7  | Digital Input/Output | General Purpose Input/Output 7                                         |

| 27           | VDIG   | Analog               | Digital Core Decoupling, connect to a 100nF decoupling capacitor       |

| 28           | GND    | Ground               | Ground                                                                 |

| 29           | RESETB | Digital Input        | Active Low Reset. Connect to VDD if not used.                          |

| 30           | VANA   | Analog               | Analog Core Decoupling, connect to a 100nF decoupling capacitor        |

| 31           | CAP0   | Analog               | Capacitive Sensor 0                                                    |

| 32           | CAP1   | Analog               | Capacitive Sensor 1                                                    |

| Bottom Plate | GND    | Ground               | Exposed pad connect to ground                                          |

Table 1 Pin description

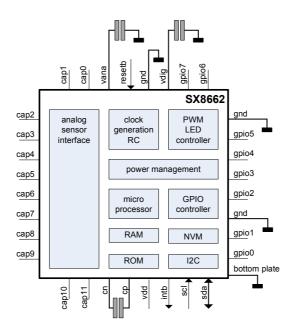

## 1.4 Simplified Block Diagram

The simplified block diagram of the SX8662 is illustrated in Figure 3.

Figure 3 Simplified block diagram of the SX8662

## 1.5 Acronyms

| ASI<br>DCV | Analog Sensor Interface<br>Digital Compensation Value |

|------------|-------------------------------------------------------|

| GPO        | General Purpose Output                                |

| GPP        | General Purpose PWM                                   |

| MTP        | Multiple Time Programmable                            |

| NVM        | Non Volatile Memory                                   |

| PWM        | Pulse Width Modulation                                |

| QSM        | Quick Start Memory                                    |

| SPM        | Shadow Parameter Memory                               |

| SPO        | Special Purpose Output                                |

| MK         | Matrix Key                                            |

| PK         | Priority Key                                          |

| PS         | Proximity Sensor                                      |

| TSM        | Tri-State Multiplexing                                |

## 2 ELECTRICAL CHARACTERISTICS

### 2.1 Absolute Maximum Ratings

Stresses above the values listed in "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these, or any other conditions beyond the "Recommended Operating Conditions", is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                 | Symbol             | Min.  | Max. | Unit |

|-------------------------------------------|--------------------|-------|------|------|

| Supply Voltage                            | VDD                | -0.5  | 3.9  | V    |

| Input voltage (non-supply pins)           | V <sub>IN</sub>    | -0.5  | 3.9  | V    |

| Input current (non-supply pins)           | I <sub>IN</sub>    |       | 10   | mA   |

| Operating Junction Temperature            | T <sub>JCT</sub>   |       | 125  | C    |

| Reflow temperature                        | T <sub>RE</sub>    |       | 260  | C    |

| Storage temperature                       | T <sub>STOR</sub>  | -50   | 150  | C    |

| ESD HBM (Human Body model) <sup>(i)</sup> | ESD <sub>HBM</sub> | 3     |      | kV   |

| Latchup <sup>(ii)</sup>                   | ILU                | ± 100 |      | mA   |

Table 2 Absolute Maximum Ratings

## 2.2 Recommended Operating Conditions

| Parameter                                   | Symbol              | Min. | Max. | Unit |

|---------------------------------------------|---------------------|------|------|------|

| Supply Voltage                              | VDD                 | 2.7  | 3.6  | V    |

| Supply Voltage Drop <sup>(iii, iv, v)</sup> | VDD <sub>drop</sub> |      | 100  | mV   |

| Supply Voltage for NVM programming          | VDD                 | 3.0  | 3.6  | V    |

| Ambient Temperature Range                   | T <sub>A</sub>      | -40  | 85   | S    |

Table 3 Recommended Operating Conditions

- a hardware reset issued by the host using the RESETB pin

- a software reset issued by the host using the I2C interface

- (v) In the event the host processor is reset or undergoes a power OFF/ON cycle, it is recommended that the host also resets the SX8662 and assures that parameters are re-written into the SPM (should these differ to the parameters held in NVM).

#### 2.3 Thermal Characteristics

| Parameter                                     | Symbol        | Min. | Max. | Unit |

|-----------------------------------------------|---------------|------|------|------|

| Thermal Resistance - Junction to Ambient (vi) | $\theta_{JA}$ |      | 25   | €/M  |

Table 4 Thermal Characteristics

(vi) Static airflow

<sup>(</sup>i) Tested to JEDEC standard JESD22-A114

<sup>(</sup>ii) Tested to JEDEC standard JESD78

<sup>(</sup>iii) Performance for 2.6V < VDD < 2.7V might be degraded.

<sup>(</sup>iv) Operation is not guaranteed below 2.6V. Should VDD briefly drop below this minimum value, then the SX8662 may require;

# 2.4 Electrical Specifications

All values are valid within the operating conditions unless otherwise specified.

| Parameter                     | Symbol                 |      | Conditions                                                       | Min.      | Тур. | Max.      | Unit |

|-------------------------------|------------------------|------|------------------------------------------------------------------|-----------|------|-----------|------|

| Current consumption           |                        |      |                                                                  |           |      | <u> </u>  |      |

| Active mode, average          | I <sub>OP,active</sub> |      | 30ms scan period,<br>12 sensors enabled,<br>minimum sensitivity  |           | 460  |           | uA   |

| Doze mode, average            | I <sub>OP,Doze</sub>   |      | 195ms scan period,<br>12 sensors enabled,<br>minimum sensitivity |           | 100  |           | uA   |

| Sleep                         | I <sub>OP,sleep</sub>  |      | I2C listening, sensors disabled                                  |           | 8    | 17        | uA   |

| ResetB, SCL, SDA              |                        |      |                                                                  |           |      |           | •    |

| Input logic high              | V <sub>IH</sub>        |      |                                                                  | 0.7*VDD   |      | VDD + 0.3 | ٧    |

| Input logic low               | V <sub>IL</sub>        |      | VSS applied to GND pins                                          | VSS - 0.3 |      | 0.8       | V    |

| Input leakage current         | Lı                     |      | CMOS input                                                       |           |      | ±1        | uA   |

| Pull up resistor              | R <sub>PU</sub>        |      | when enabled                                                     |           | 660  |           | kΩ   |

| Pull down resistor            | R <sub>PD</sub>        |      | when enabled                                                     |           | 660  |           | kΩ   |

| GPIO set as Output, INTB, SDA |                        |      |                                                                  |           |      |           |      |

| Output logic high             | V <sub>OH</sub>        |      | I <sub>OH</sub> <4mA                                             | VDD-0.4   |      |           | ٧    |

| Output logic low              | V <sub>OL</sub>        |      | I <sub>OL,GPIO</sub> <12mA<br>I <sub>OL,SDA,INTB</sub> <4mA      |           |      | 0.4       | V    |

| Start-up                      |                        |      |                                                                  |           | _    |           | 1    |

| Power up time                 | t <sub>por</sub>       |      | time between rising edge VDD and rising INTB                     |           |      | 400       | ms   |

| RESETB                        |                        |      |                                                                  |           |      |           |      |

| ResetB pulse width            | t <sub>res</sub>       |      |                                                                  | 50        |      |           | ns   |

| Recommended External compo    | onents                 |      |                                                                  |           | •    |           |      |

| capacitor between VDIG, GND   | C <sub>vdig</sub>      | type | 0402, tolerance +/-50%                                           |           | 100  |           | nF   |

| capacitor between VANA, GND   | C <sub>vana</sub>      | type | 0402, tolerance +/-50%                                           |           | 100  |           | nF   |

| capacitor between CP, CN      | Cint                   | type | 0402, COG, tolerance +/-5%                                       |           | 1    |           | nF   |

| capacitor between VDD, GND    | C <sub>vdd</sub>       | type | 0402, tolerance +/-50%                                           |           | 100  |           | nF   |

| capacitor between VDD, GND    | C <sub>vdd</sub>       | type | 0402, tolerance +/-50%                                           |           | 100  |           |      |

Table 5 Electrical Specifications

| Parameter                            | Symbol              | Conditions | Min. | Тур. | Max. | Unit |

|--------------------------------------|---------------------|------------|------|------|------|------|

| I2C Timing Specifications (i)        |                     |            |      |      |      |      |

| SCL clock frequency                  | f <sub>SCL</sub>    |            |      |      | 400  | KHz  |

| SCL low period                       | t <sub>LOW</sub>    |            | 1.3  |      |      | us   |

| SCL high period                      | t <sub>HIGH</sub>   |            | 0.6  |      |      | us   |

| Data setup time                      | t <sub>SU;DAT</sub> |            | 100  |      |      | ns   |

| Data hold time                       | t <sub>HD;DAT</sub> |            | 0    |      |      | ns   |

| Repeated start setup time            | t <sub>SU;STA</sub> |            | 0.6  |      |      | us   |

| Start condition hold time            | thd;sta             |            | 0.6  |      |      | us   |

| Stop condition setup time            | t <sub>SU;STO</sub> |            | 0.6  |      |      | us   |

| Bus free time between stop and start | t <sub>BUF</sub>    |            | 500  |      |      | us   |

| Input glitch suppression             | t <sub>SP</sub>     |            |      |      | 50   | ns   |

Table 6 I2C Timing Specification

#### Notes:

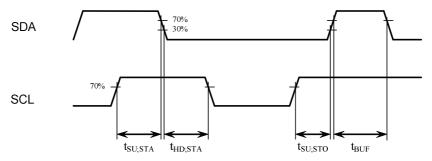

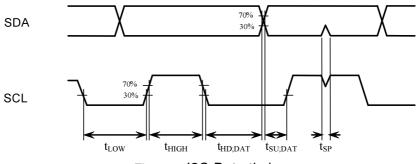

(i) All timing specifications, Figure 4 and Figure 5, refer to voltage levels ( $V_{IL}$ ,  $V_{IH}$ ,  $V_{OL}$ ) defined in Table 5.

The interface complies with slave F/S mode as described by NXP: "I2C-bus specification, Rev. 03 - 19 June 2007"

Figure 4 I2C Start and Stop timing

Figure 5 I2C Data timing

# **ADVANCED COMMUNICATIONS & SENSING**

#### 3 FUNCTIONAL DESCRIPTION

#### 3.1 Introduction

#### 3.1.1 General

The SX8662 is intended to be used in applications which require capacitive sensors covered by isolating overlay material. A finger approaching the capacitive sensors will change the charge that can be loaded on the sensors. The SX8662 measures the change of charge and converts that into digital values (ticks). The larger the charge on the sensors, the larger the number of ticks will be. The charge to ticks conversion is done by the SX8662 Analog Sensor Interface (ASI).

The ticks are further processed by the SX8662 and converted in a high level, easy to use information for the user's host.

The information between SX8662 and the host is passed through the I2C interface with an additional interrupt signal indicating that the SX8662 has new information. For buttons this information is simply touched or released. User feedback, done through the SX8662's GPIOs, can be visual via LEDs and/or audio via a buzzer.

#### 3.1.2 Parameters

The SX8662 has many low level built-in, fixed algorithms and procedures. To allow a lot of freedom for the user and adapt the SX8662 for different applications these algorithms and procedures can be configured with a large set of parameters which will be described in the following sections.

Sensitivity and detection thresholds of the sensors are part of these parameters. Assuming that overlay material and sensors areas are identical then the sensitivities and thresholds will be the same for each sensor. In case sensors are not of the same size then sensitivities or thresholds might be chosen individually per sensor.

So a smaller size sensor can have a larger sensitivity while a big size sensor may have the lower sensitivity.

#### 3.1.3 Configuration

During a development phase the parameters can be determined and fine tuned by the users and downloaded over the I2C in a dynamic way. The parameter set can be downloaded over the I2C by the host each time the SX8662 boots up. This allows a flexible way of setting the parameters at the expense of I2C occupation.

In case the parameters are frozen they can be programmed in Multiple Time Programmable (MTP) Non Volatile Memory (NVM) on the SX8662. The programming needs to be done once (over the I2C). The SX8662 will then boot up from the NVM and additional parameters from the host are not required anymore.

In case the host desires to overwrite the boot-up NVM parameters (partly or even complete) this can be done by additional I2C communications.

#### 3.2 Scan Period

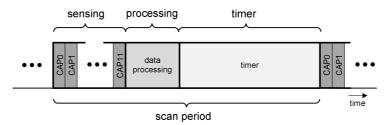

The basic operation Scan period of the SX8662 sensing interface can be split into three periods over time.

In the first period (Sensing) the SX8662 is sensing all enabled CAP inputs, from CAP0 towards CAP11.

In the second period (Processing) the SX8662 processes the sensor data, verifies and updates the GPIO and the I2C.

In the third period (Timer) the SX8662 is set in a low power mode and waits until a new cycle starts.

Figure 6 shows the different SX8662 periods over time.

## ADVANCED COMMUNICATIONS & SENSING

Figure 6 Scan Period

The scan period determines the minimum reaction time of the SX8662. The scan period can be configured by the host from 15ms to values larger than a second.

The reaction time is defined as the interval between a touch on the sensor and the moment that the SX8662 generates the interrupt on the INTB pin. The shorter the scan period the faster the reaction time will be.

Very low power consumptions can be obtained by setting very long scan periods with the expense of having longer reaction times.

All external events like GPIO, I2C and the interrupt are updated in the processing period, so once every scan period.

#### 3.3 Operation modes

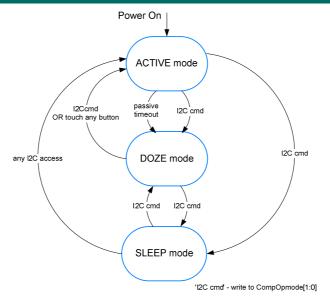

The SX8662 has 3 operation modes. The main difference is found in the reaction time (corresponding to the scan period) and power consumption.

Active mode offers fast scan periods. The typical reaction time is 30ms. All enabled sensors are scanned and information data is processed within this interval.

Doze mode increases the scan period time which increases the reaction time to 195ms typical and at the same time reduces the operating current.

Sleep mode turns the SX8662 OFF, except for the I2C peripheral, minimizing operating current while maintaining the power supplies. In Sleep mode the SX8662 does not do any sensor scanning. The Sleep mode will be exited by any I2C access.

The user can specify other scan periods for the Active and Doze mode and decide for other compromises between reaction time and power consumption.

In most applications the reaction time needs to be fast when fingers are present, but can be slow when no person uses the application. In case the SX8662 is not used for a specific time it will go from Active mode into Doze mode and power will be saved. This time-out is determined by the Passive Timer which can be configured by the user or turned OFF if not required.

To leave Doze mode and enter Active mode this can be done by a simple touch on any button.

The host can decide to force the operating mode by issuing commands over the I2C (using register CompOpMode) and take fully control of the SX8662. The diagram in Figure 7 shows the available operation modes and the possible transitions.

Figure 7 Operation modes

#### 3.4 Sensors on the PCB

#### 3.4.1 Matrix Keys/Buttons (MK)

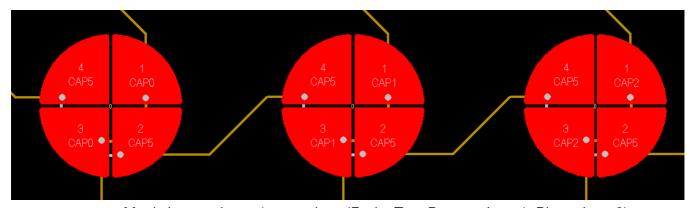

In opposition to most of the other Semtech capacitive sensing products where 1 button = 1 sensor (CAP0...CAP11)., the SX8662 requires sensors to be routed in matrix and each button is formed by the intersection/concatenation of two sensors areas. The buttons are covered by isolating overlay material (typically 1mm...3mm). The area of a button is typically one square centimetre which corresponds about to the area of a finger touching the overlay material.

Figure 8 Matrix buttons layout/connections (Red = Top; Brown = Inner1; Blue = Inner2)

**IMPORTANT:** Please note that while the matrix structure allows increasing dramatically the potential maximum number of buttons (up to 36 with only 12 sensors) it also limits the operation to max one matrix button reported at a time (ie single button touch operation). When several matrix buttons are touched only the first one is reported.

#### 3.4.2 Priority Key/Button (PK)

When the priority key is enabled in BtnCfg[6], CAP11 can be routed outside the matrix to a separate standard button sensor. Matrix size is then reduced to 6x5 keys (CAP0...CAP10). Priority key operation/reporting is independent from the matrix and can be used for any "high priority" key (Power, Reset, etc) or "multi-touch" function (Shift, Alt, etc).

## 3.4.3 Schematics Requirements

For each PK combination, a specific schematic must be followed on the board as illustrated in figure below.

Rev5 4<sup>th</sup> August 2011 © 2011 Semtech Corp. www.semtech.com

| MK   | MK   | MK   | MK      | MK   | MK       | - O A D 4 4 |      |      |      |          |       |          |        |

|------|------|------|---------|------|----------|-------------|------|------|------|----------|-------|----------|--------|

| 36   | 35   | 34   | 33      | 32   | 31       | CAP11       |      |      |      |          |       |          |        |

| мK   | MK   | MK   | MK      | MK   | MK       | 0.100       | MK   | MK   | MK   | MK       | MK    | MK       | CAP9   |

| 25   | 24   | 23   | 22      | 21   | 30       | CAP9        | 25   | 24   | 23   | 22       | 21    | 30       | OAI 3  |

| MK   | MK   | MK   | MK      | MK   | MK       |             | MK   | MK   | MK   | MK       | MK    | MK       | CAP7   |

| 16   | 15   | 14   | 13      | 20   | 29       | CAP7        | 16   | 15   | 14   | 13       | 20    | 29       | GAP /  |

| MK   | MK   | MK   | MK      | MK   | MK       |             | MK   | МK   | MK   | MK       | MK    | MK       | 0.4.00 |

| 9    | 8    | 7    | 12      | 19   | MK<br>28 | CAP6        | 9    | 8    | 7    | 12       | 19    | 28       | CAP6   |

| MK   | мк   | MK   | MK      | MK   | MK       | OADE        | MK   | MK   | MK   | мк       | MK    | MK<br>27 | CAP5   |

| 4    | 3    | 6    | 11      | 18   | MK<br>27 | CAP5        | 4    | 3    | 6    | 11       | 18    | 27       | CAF5   |

| MK   | MK   | MK   | МK      | MK   | MK       | 0454        | MK   | мк   | MK   | MK       | MK    | MK<br>26 | CAP4   |

| 1    | 2    | 5    | 10      | 17   | MK<br>26 | CAP4        | 1    | 2    | 5    | 10       | 17    |          | CAF4   |

| CAP0 | CAP1 | CAP2 | CAP3    | CAP8 | CAP10    |             | CAP0 | CAP1 | CAP2 | CAP3     | CAP8  | CAP10    |        |

|      |      |      | PK = OF | F    |          |             |      |      | PK   | = ON (CA | AP11) |          |        |

Figure 9 Sensors Schematics Requirements vs Configuration

#### 3.5 Button Information (MK and PK)

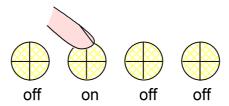

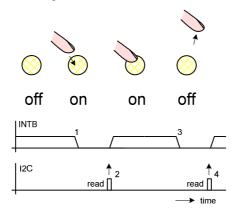

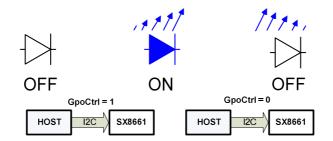

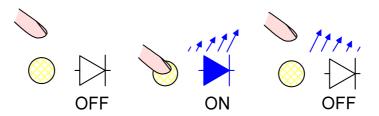

The touch buttons have two simple states (see Figure 10): ON (touched by finger) and OFF (released and no finger press).

Figure 10 Buttons

A finger touch is reported as soon as the ASI ticks of both sensors forming the button exceed their user-defined threshold plus a hysteresis.

A finger release is reported as soon as the ASI ticks of one at least of the sensors forming the button goes below its user-defined threshold minus a hysteresis.

The hysteresis around the threshold avoids rapid touch and release signalling during transients.

**IMPORTANT:** Please note that while the matrix structure allows increasing dramatically the potential maximum number of buttons (up to 36 with only 12 sensors) it also limits the operation to max one matrix button reported at a time (ie single button touch operation). When two matrix buttons are touched only the first one is reported.

## 3.6 Analog Sensing Interface

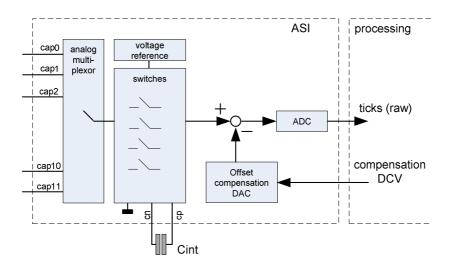

The Analog Sensing Interface (ASI) converts the charge on the sensors into ticks which will be further digitally processed. The basic principle of the ASI will be explained in this section.

The ASI consists of a multiplexer selecting the sensor, analog switches, a reference voltage, an ADC sigma delta converter, an offset compensation DAC and an external integration capacitor (see Figure 11).

Figure 11 Analog Sensor Interface

To get the ticks representing the charge on a specific sensor the ASI will execute several steps.

## **ADVANCED COMMUNICATIONS & SENSING**

The charge on a sensor cap (e.g CAP0) will be accumulated multiple times on the external integration capacitor, Cint.

This results in an increasing voltage on Cint proportional to the capacitance on CAP0.

At this stage the offset compensation DAC is enabled. The compensation DAC generates a voltage proportional to an estimation of the external capacitance. The estimation is obtained by the offset compensation procedure executed e.g. at power-up.

The difference between the DAC output and the charge on Cint is the desired signal. In the ideal case the difference of charge will be converted to zero ticks if no finger is present and the number of ticks becomes high in case a finger is present.

The difference of charge on Cint and the DAC output will be transferred to the ADC (Sigma Delta Integrator).

After the charge transfer to the ADC the steps above will be repeated.

The larger the number the cycles are repeated the larger the signal out of the ADC with improved SNR. The sensitivity is therefore directly related to the number of cycles.

The SX8662 allows setting the sensitivity for each sensor individually in applications which have a variety of sensors sizes or different overlays or for fine-tuning performances. The optimal sensitivity is depending heavily on the final application. If the sensitivity is too low the ticks will not pass the thresholds and user detection will not be possible. In case the sensitivity is set too large, some power will be wasted and false touch information may be output (i.e. for touch buttons => finger not touching yet).

Once the ASI has finished the first sensor, the ticks are stored and the ASI will start measuring the next sensor until all (enabled) sensors pins have been treated.

In case some sensors are disabled then these result in lower power consumption simply because the ASI is active for a shorter period and the following processing period will be shorter.

The ticks from the ASI will then be handled by the digital processing.

The ASI will shut down and wait until new sensing period will start.

## ADVANCED COMMUNICATIONS & SENSING

### 3.7 Offset Compensation

The capacitance at the CAP pins is determined by an intrinsic capacitance of the integrated circuit, the PCB traces, ground coupling and the sensor planes. This capacitance is relatively large and might become easily some tens of pF. This parasitic capacitance will vary only slowly over time due to environmental changes.

A finger touch is in the order of one pF. If the finger approaches the sensor this occurs typically fast.

The ASI has the difficult task to detect and distinguish a small, fast changing capacitance, from a large, slow varying capacitance. This would require a very precise, high resolution ADC and complicated, power consuming, digital processing.

The SX8662 features a 16 bit DAC which compensates for the large, slow varying capacitance already in front of the ADC. In other words the ADC converts only the desired small signal. In the ideal world the ADC will put out zero ticks even if the external capacitance is as high as 100pF.

At each power-up of the SX8662 the Digital Compensation Values (DCV) are estimated by the digital processing algorithms. The algorithm will adjust the compensation values such that zero ticks will be generated by the ADC. Once the correct compensation values are found these will be stored and used to compensate each CAP pin.

ones the compensation values are really those vim so stored and deed to compensate each or in pinn

If the SX8662 is shut down the compensation values will be lost. At a next power-up the procedure starts all over again. This assures that the SX8662 will operate under any condition. Powering up at e.g. different temperatures will not change the performance of the SX8662 and the host does not have to do anything special.

The DCVs do not need to be updated if the external conditions remain stable.

However if e.g. temperature changes this will influence the external capacitance. The ADC ticks will drift then slowly around zero values basically because of the mismatch of the compensation circuitry and the external capacitance.

In case the average value of the ticks become higher than the positive noise threshold (configurable by user) or lower than the negative threshold (configurable by user) then the SX8662 will initiate a compensation procedure and find a new set of DCVs.

Compensation procedures can as well be initiated by the SX8662 on periodic intervals. Even if the ticks remain within the positive and negative noise thresholds the compensation procedure will then estimate new sets of DCVs.

Finally the host can initiate a compensation procedure by using the I2C interface. This is e.g. required after the host changed the sensitivity of sensors.

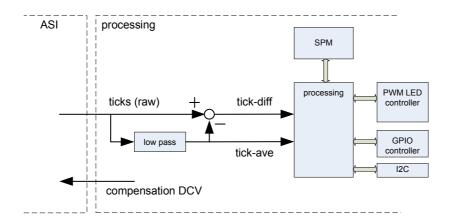

#### 3.8 Processing

The first processing step of the raw ticks, coming out of the ASI, is low pass filtering to obtain an estimation of the average capacitance: tick-ave (see Figure 12).

This slowly varying average is important in the detection of slowly changing environmental changes.

Figure 12 Processing

The difference of the tick average and the raw ticks, tick-diff, is a good estimation of rapid changing input capacitances.

The tick-diff, tick-ave and the configuration parameters in the SPM are then processed and determines the sensor information, I2C registers status and PWM control.

## 3.9 Configuration

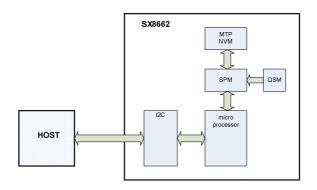

Figure 13 shows the building blocks used for configuring the SX8662.

Figure 13 Configuration

The default configuration parameters of the SX8662 are stored in the Quick Start Memory (QSM). This configuration data is setup to a very common application for the SX8662 with 8 buttons. Without any programming or host interaction the SX8662 will start up in the Quick Start Application.

The QSM settings are fixed and cannot be changed by the user.

## **ADVANCED COMMUNICATIONS & SENSING**

In case the application needs different settings than the QSM settings then the SX8662 can be setup and/or programmed over the I2C interface.

The configuration parameters of the SX8662 can be stored in the Multiple Time Programmable (MTP) Non Volatile Memory (NVM). The NVM contains all those parameters that are defined and stable for the application. Examples are the number of sensors enabled, sensitivity, active and Doze scan period. The details of these parameters are described in the next chapters.

At power up the SX8662 checks if the NVM contains valid data. In that case the configuration parameter source becomes the NVM. If the NVM is empty or non-valid then the configuration source becomes the QSM. In the next step the SX8662 copies the configuration parameter source into the Shadow Parameter Memory (SPM). The SX8662 is operational and uses the configuration parameters of the SPM.

During power down or reset event the SPM loses all content. It will automatically be reloaded following power up or at the end of the reset event.

The host will interface with the SX8662 through the I2C bus and the analog output interface.

The I2C of the SX8662 consists of 16 registers. Some of these I2C registers are used to read the status and information of the buttons. Other I2C registers allow the host to take control of the SX8662. The host can e.g. decide to change the operation mode from active mode to Doze mode or go into sleep (according Figure 7).

Two additional modes allow the host to have an access to the SPM or indirect access to the NVM.

These modes are required during development, can be used in real time or in-field programming.

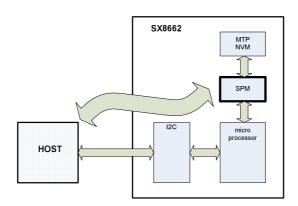

Figure 14 shows the Host SPM mode. In this mode the host can decide to overwrite the SPM. This is useful during the development phases of the application where the configuration parameters are not yet fully defined and as well during the operation of the application if some parameters need small deviations from the QSM or NVM content.

Figure 14 Host SPM mode

The content of the SPM remains valid as long as the SX8662 is powered. After a power down the host needs to re-write the SPM at the next power-up.

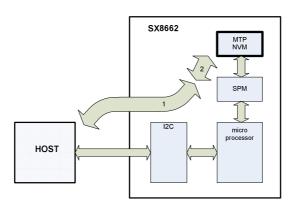

Figure 15 shows the Host NVM mode. In this mode the host will be able to write the NVM.

Figure 15 Host NVM mode

The writing of the host towards the NVM is not done directly but done in 2 steps (Figure 15).

In the first step the host writes to the SPM (as in Figure 14). In the second step the host signals the SX8662 to copy the SPM content into the NVM.

Initially the NVM memory is empty and it is required to determine a valid parameter set for the application. This can be done during the development phase using dedicated evaluation hardware representing the final application. This development phase uses probably initially the host SPM mode which allows faster iterations.

Once the parameter set is determined this can be written to the NVM over the I2C using the 2 steps approach by the host or a dedicated programmer for large volumes production (as described in the paragraphs 6.6 and 6.7).

#### 3.10 Power Management

The SX8662 uses on-chip voltage regulators which are controlled by the on-chip microprocessor. The regulators need to be stabilized with an external capacitor between VANA and ground and between VDIG and ground (see Table 5). Both regulators are designed to only drive the SX8662 internal circuitry and must not be loaded externally.

## 3.11 Clock Circuitry

The SX8662 has its own internal clock generation circuitry that does not require any external components. The clock circuitry is optimized for low power operation and is controlled by the on-chip microprocessor. The typical operating frequency of the oscillating core is 16.7MHz from which all other lower frequencies are derived.

#### 3.12 I2C interface

The I2C interface allows the communication between the host and the SX8662.

The I2C slave implemented on the SX8662 is compliant with the standard (100kb/s) and fast mode (400kb/s) The default SX8662 I2C address equals 0b010 1011.

A different I2C address can be programmed by the user in the NVM.

#### 3.13 Interrupt

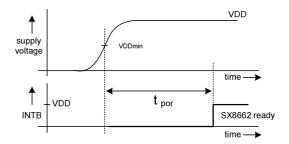

#### 3.13.1 Power up

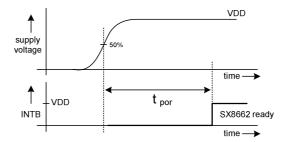

During power up the INTB is kept low. Once the power up sequence is terminated the INTB is cleared autonomously. The SX8662 is then ready for operation.

Figure 16 Power Up vs. INTB

During the power on period the SX8662 stabilizes the internal regulators, RC clocks and the firmware initializes all registers.

During the power up the SX8662 is not accessible and I2C communications are forbidden. The GPIOs set as inputs with a pull up resistor.

As soon as the INTB rises the SX8662 will be ready for I2C communication. The GPIOs are then configured according the parameters in the SPM.

The value of INTB before power up depends on the INTB pull up resistor supply voltage.

## 3.13.2 Assertion

INTB is updated in Active or Doze mode once every scan period.

The INTB will be asserted at the following events:

- if a Button event occurred (touch or release if enabled). I2C register CapStatKeys show the detailed status of the Buttons,

- when actually entering Active or Doze mode via a host request (may be delayed by 1 scan period). I2C register CompOpmode shows the current operation mode,

- once compensation procedure is completed either through automatic trigger or via host request (may be delayed by 1 scan period),

- once SPM write is effective (may be delayed by 1 scan period),

- once NVM burn procedure is completed (may be delayed by 1 scan period),

- during reset (power up, hardware RESETB, software reset).

## 3.13.3 Clearing

The clearing of the INTB is done as soon as the host performs a read to any of the SX8662 I2C registers.

3.13.4 Example

A typical example of the assertion and clearing of the INTB and the I2C communication is shown in Figure 17.

Figure 17 Interrupt and I2C

When a button is touched the SX8662 will assert the interrupt (1). The host will read the SX8662 status information over the I2C (2) and this clears the interrupt.

If the finger releases the button the interrupt will be asserted (3), the host reads the status (4) which clears the interrupt.

In case the host will not react to an interrupt then this will result in a missing touch.

#### 3.14 Reset

The reset can be performed by 3 sources:

- power up,

- RESETB pin,

- software reset.

#### 3.14.1 Power up

During power up the INTB is kept low. Once the power up sequence is terminated the INTB is released autonomously. The SX8662 is then ready for operation.

Figure 18 Power Up vs. INTB

During the power on period the SX8662 stabilizes the internal regulators, RC clocks and the firmware initializes all registers.

During the power up the SX8662 is not accessible and I2C communications are forbidden. As soon as the INTB rises the SX8662 will be ready for I2C communication.

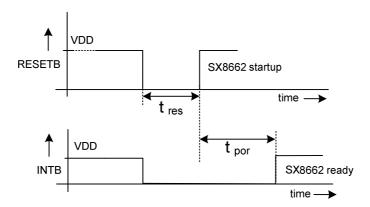

#### 3.14.2 RESETB

When RESETB is driven low the SX8662 will reset and start the power up sequence as soon as RESETB is driven high or pulled high.

In case the user does not require a hardware reset control pin then the RESETB pin can be connected to VDD.

Figure 19 Hardware Reset

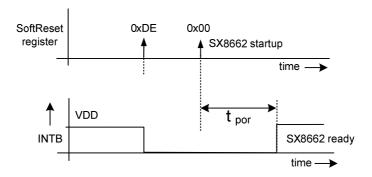

#### 3.14.3 Software Reset

To perform a software reset the host needs to write 0xDE followed by 0x00 at the SoftReset register at address 0xB1.

Figure 20 Software Reset

#### 3.15 General Purpose Input and Outputs

The SX8662 offers eight General Purpose Input and Outputs (GPIO) pins which can be configured in any of these modes:

- GPO (General Purpose Output) with Autoligth ON/OFF

- SPO (Special Purpose Output). GPIO7 only; in this mode the GPIO can be connected to an external buzzer.

The input state of the GPIO is only used during the initial phase of the power up period.

Each of these GPIO modes is described in more details in the following sections.

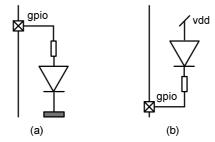

The polarity of the GPO pins is defined as in figure below, driving an LED as example. It has to be set accordingly in SPM parameter GpioPolarity.

Figure 21 polarity = 1/Normal (a), polarity = 0/Inverted (b)

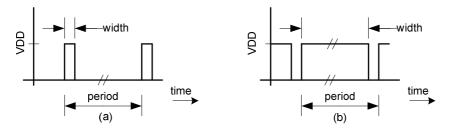

The PWM blocks used GPO modes are 8-bits based and clocked at 2MHz typ. hence offering 256 selectable pulse width values with a granularity of 0.5us typ.

Figure 22 PWM definition, (a) small pulse width, (b) large pulse width

#### 3.15.1 GPO

GPIOs configured as GPO will operate as digital outputs which can generate both standard low/high logic levels and PWM low/high duty cycles levels. Typical application is LED ON/OFF control.

Transitions between ON and OFF states can be triggered either automatically (Autolight ON) or manually by the host (Autolight OFF). This is illustrated in figures below.

Figure 23 LED Control in GPO mode, Autolight OFF

Figure 24 LED Control in GPO mode, Autolight ON

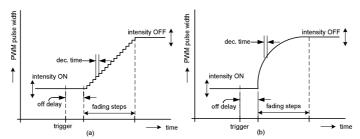

Additionally these transitions can be configured to be done with or without fading following a logarithmic or linear function. This is illustrated in figures below.

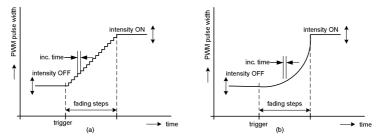

Figure 25 GPO ON transition (LED fade in), normal polarity, (a) linear, (b) logarithmic

Figure 26 GPO ON transition (LED fade in), inverted polarity, (a) linear, (b) logarithmic

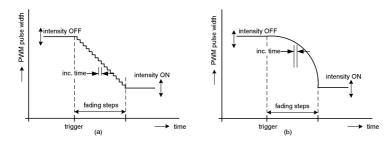

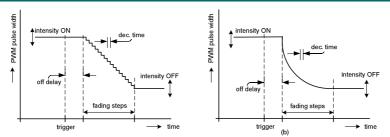

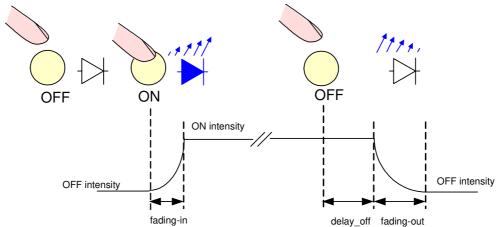

The fading out (e.g. after a button is released) is identical to the fading in but an additional off delay can be added before the fading starts (Figure 27 and Figure 28).

Figure 27 GPO OFF transition (LED fade out), normal polarity, (a) linear, (b) logarithmic

Figure 28 GPO OFF transition (LED fade out), inverted polarity, (a) linear, (b) logarithmic

Please note that standard high/low logic signals are just a specific case of GPO mode and can also be generated simply by setting inc/dec time to 0 (i.e. OFF) and programming intensity OFF/ON to 0x00 and 0xFF.

#### 3.15.2 Fading Modes

The SX8662 supports two different fading modes, namely Single and Continuous. These fading modes can be configured for each GPIO individually. Please see 5.6 "GPIO Parameters" for more information on how to configure this feature.

#### i) Single Fading Mode:

The GPO pin fades in when the associated button is touched and it fades out when it is released. This is shown in Figure 29

Figure 29 Single Fading Mode

ii) Continuous Fading Mode: