Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- Max. toggle frequency of 700MHz

- Clock to Q max. of 1200ps

- IEE min. of -98mA

- Industry standard 100K ECL levels

- Extended supply voltage option: VEE = -4.2V to -5.5V

- Voltage and temperature compensation for improved noise immunity

- Internal 75K $\Omega$  input pull-down resistors

- 50% faster than Fairchild 300K

- Better than 20% lower power than Fairchild

- Function and pinout compatible with Fairchild F100K

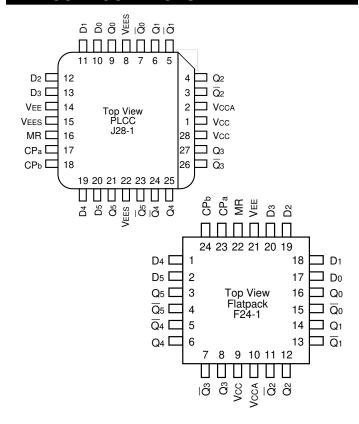

- Available in 24-pin CERPACK and 28-pin PLCC packages

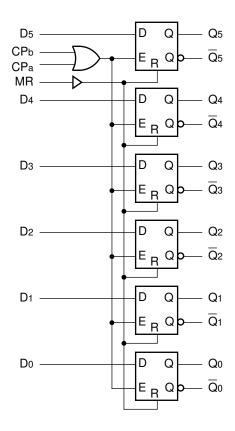

#### **BLOCK DIAGRAM**

### **DESCRIPTION**

The SY100S351 offers six D-type, edge-triggered, master/slave flip-flops with differential outputs, and is designed for use in high-performance ECL systems. The flip-flops are controlled by the signal from the logical OR operation on a pair of common clock signals (CPa, CPb). Data enters the master when both CPa and CPb are LOW and transfers to the slave when either CPa or CPb (or both) go to a logic HIGH. The Master Reset (MR) input overrides all other inputs and takes the Q outputs to a logic LOW. The inputs on this device have 75K $\Omega$  pull-down resistors.

#### PIN CONFIGURATIONS

# **PIN NAMES**

| Pin                               | Function                        |  |  |  |  |

|-----------------------------------|---------------------------------|--|--|--|--|

| D0 — D5                           | Data Inputs                     |  |  |  |  |

| CPa, CPb                          | Common Clock Inputs             |  |  |  |  |

| MR                                | Asynchronous Master Reset Input |  |  |  |  |

| Q0 — Q5                           | Data Outputs                    |  |  |  |  |

| $\overline{Q}_0 - \overline{Q}_5$ | Complementary Data Outputs      |  |  |  |  |

| VEES                              | VEE Substrate                   |  |  |  |  |

| VCCA                              | Vcco for ECL Outputs            |  |  |  |  |

#### **TRUTH TABLES**

| Asynchronous Operation <sup>(1)</sup> |        |     |    |          |  |  |  |

|---------------------------------------|--------|-----|----|----------|--|--|--|

|                                       | Inputs |     |    |          |  |  |  |

| Dn                                    | CPa    | СРь | MR | Qn (t+1) |  |  |  |

| Х                                     | Х      | Х   | Н  | L        |  |  |  |

#### NOTE:

1. H = High Voltage Level

L = Low Voltage Level

X = Don't Care

t = Time before CP Positive Transition

t+1 = Time after CP Positive Transition

u = LOW-to-HIGH Transition

| Synchronous Operation <sup>(1)</sup> |        |     |    |          |  |  |  |  |

|--------------------------------------|--------|-----|----|----------|--|--|--|--|

|                                      | Inputs |     |    |          |  |  |  |  |

| Dn                                   | CPa    | СРь | MR | Qn (t+1) |  |  |  |  |

| L                                    | u      | L   | L  | L        |  |  |  |  |

| Н                                    | u      | L   | L  | Н        |  |  |  |  |

| L                                    | L      | u   | L  | L        |  |  |  |  |

| Н                                    | L      | u   | L  | Н        |  |  |  |  |

| Х                                    | Η      | u   | L  | Qn(t)    |  |  |  |  |

| Х                                    | u      | Н   | L  | Qn(t)    |  |  |  |  |

| Х                                    | Ĺ      | L   | L  | Qn(t)    |  |  |  |  |

# DC ELECTRICAL CHARACTERISTICS

VEE = -4.2V to -5.5V unless otherwise specified; VCC = VCCA = GND

| Symbol | Parameter            | Min.     | Тур. | Max.        | Unit | Condition        |

|--------|----------------------|----------|------|-------------|------|------------------|

| Iн     | Input HIGH Current   |          |      |             | μΑ   | VIN = VIH (Max.) |

|        | MR                   | <b>—</b> | _    | 270         | ·    |                  |

|        | Do – D5              | <b> </b> | _    | 200         |      |                  |

|        | CPa, CPb             | <b>—</b> | _    | 300         |      |                  |

| IEE    | Power Supply Current | -98      | -71  | <b>–</b> 49 | mA   | Inputs Open      |

# AC ELECTRICAL CHARACTERISTICS

## **CERPACK**

VEE = -4.2V to -5.5V unless otherwise specified; VCC = VCCA = GND

|              |                                           | TA:         | = 0°C | TA = +25°C  |      | TA = +85°C  |      |      |           |

|--------------|-------------------------------------------|-------------|-------|-------------|------|-------------|------|------|-----------|

| Symbol       | Parameter                                 | Min.        | Max.  | Min.        | Max. | Min.        | Max. | Unit | Condition |

| fmax         | Toggle Frequency                          | 700         | _     | 700         |      | 700         | _    | MHz  |           |

| tPLH<br>tPHL | Propagation Delay<br>CPa, CPb to Output   | _           | 1200  | _           | 1200 | _           | 1200 | ps   |           |

| tPLH<br>tPHL | Propagation Delay<br>MR to Output         | _           | 1200  | _           | 1200 | _           | 1200 | ps   |           |

| tTLH<br>tTHL | Transition Time<br>20% to 80%, 80% to 20% | 300         | 900   | 300         | 900  | 300         | 900  | ps   |           |

| ts           | Set-up Time<br>D0-D5<br>MR (Release Time) | 500<br>1000 | _     | 500<br>1000 | _    | 500<br>1000 | _    | ps   |           |

| tH           | Hold Time, D0-D5                          | 550         | _     | 550         | _    | 550         | _    | ps   |           |

| tpw (H)      | Pulse Width HIGH<br>CPa, CPb, MR          | 1000        | _     | 1000        | _    | 1000        | _    | ps   |           |

#### **PLCC**

VEE = -4.2V to -5.5V unless otherwise specified; VCC = VCCA = GND

|              |                                           | TA = 0°C    |      | TA = +25°C  |      | TA = +85°C  |      |      |           |

|--------------|-------------------------------------------|-------------|------|-------------|------|-------------|------|------|-----------|

| Symbol       | Parameter                                 | Min.        | Max. | Min.        | Max. | Min.        | Max. | Unit | Condition |

| fMAX         | Toggle Frequency                          | 700         | _    | 700         | _    | 700         | _    | MHz  |           |

| tPLH<br>tPHL | Propagation Delay<br>CPa, CPb to Output   | _           | 1200 | _           | 1200 | _           | 1200 | ps   |           |

| tPLH<br>tPHL | Propagation Delay<br>MR to Output         | _           | 1200 | _           | 1200 |             | 1200 | ps   |           |

| tTLH<br>tTHL | Transition Time 20% to 80%, 80% to 20%    | 300         | 900  | 300         | 900  | 300         | 900  | ps   |           |

| ts           | Set-up Time<br>D0-D5<br>MR (Release Time) | 500<br>1000 | _    | 500<br>1000 |      | 500<br>1000 | _    | ps   |           |

| tH           | Hold Time, D0-D5                          | 550         | _    | 550         | _    | 550         | _    | ps   |           |

| tpw (H)      | Pulse Width HIGH<br>CPa, CPb, MR          | 1000        | _    | 1000        | _    | 1000        | _    | ps   |           |

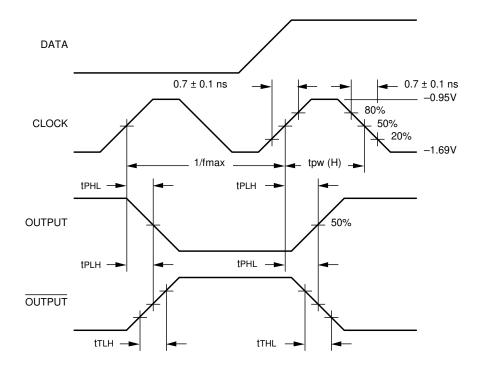

# **TIMING DIAGRAMS**

**Propagation Delay (Clock) and Transition Times**

#### NOTE:

VEE = -4.2V to -5.5V unless otherwise specified; VCC = VCCA = GND

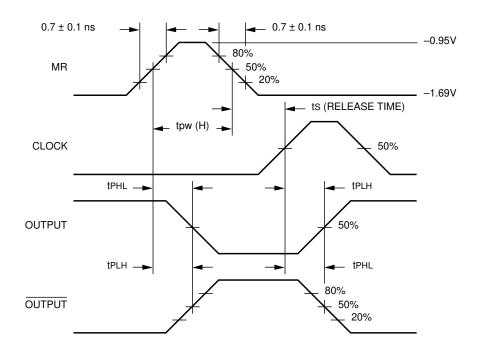

**Propagation Delay (Resets)**

# **TIMING DIAGRAMS**

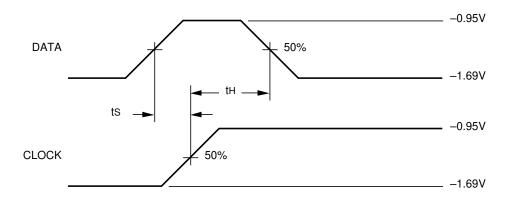

**Data Set-up and Hold Time**

#### NOTES:

- 1. VEE = -4.2V to -5.5V unless otherwise specified; VCC = VCCA = GND

- 2. ts is the minimum time before the transition of the clock that information must be present at the data input.

- 3. th is the minimum time after the transition of the clock that information must remain unchanged at the data input.

# **PRODUCT ORDERING CODE**

| Ordering<br>Code | Package<br>Type | Operating<br>Range |

|------------------|-----------------|--------------------|

| SY100S351FC      | F24-1           | Commercial         |

| SY100S351JC      | J28-1           | Commercial         |

| SY100S351JCTR    | J28-1           | Commercial         |

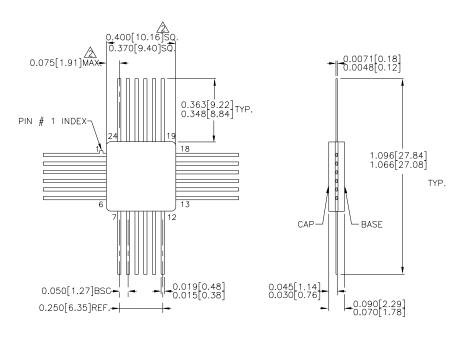

# 24 LEAD CERPACK (F24-1)

NOTES:

1. DIMENSIONS ARE IN INCHES[MM].

AND CAP TO BASE ALIGNMENT TOLERANCES.

3. DIMENSIONS SHOWN ARE MAX/MIN, WHERE NOTED.

Rev. 03

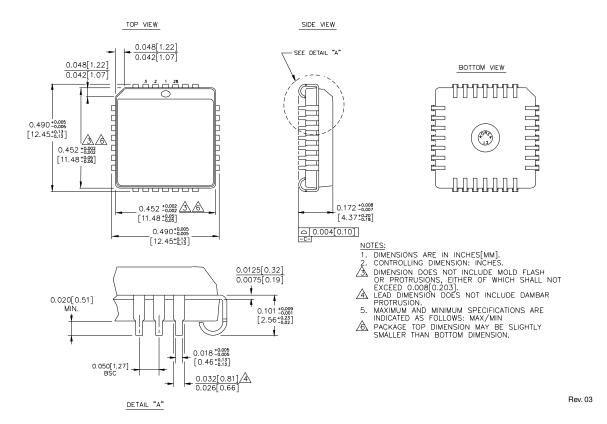

## 28 LEAD PLCC (J28-1)

MICREL-SYNERGY 3250 SCOTT BOULEVARD SANTA CLARA CA 95054 USA

TEL + 1 (408) 980-9191 FAX + 1 (408) 914-7878 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.