# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

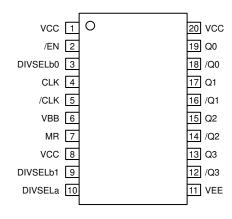

÷2/4, ÷4/5/6 CLOCK GENERATION CHIP

Precision Edge<sup>®</sup> SY100S839V

#### **FEATURES**

- 3.3V and 5V power supply option

- 50ps output-to-output skew

- 50% duty cycle outputs

- Synchronous enable/disable

- Master Reset for synchronization

- Internal 75KΩ input pull-down resistors

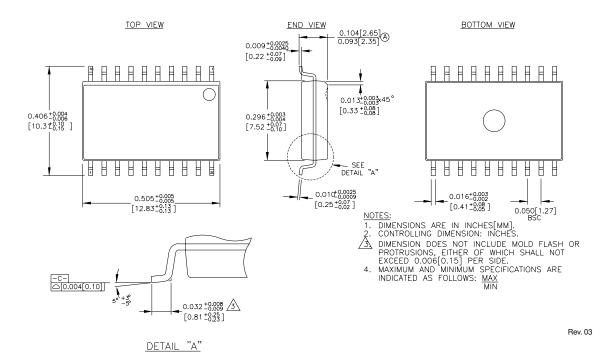

- Available in 20-pin SOIC package

#### DESCRIPTION

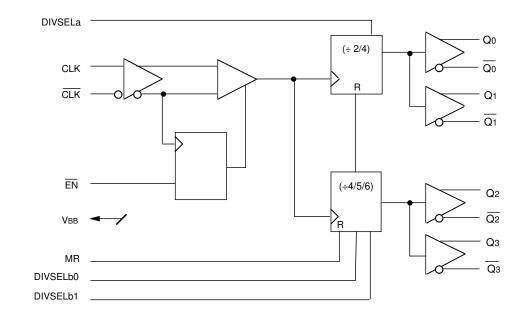

The SY100S839V is a low skew  $\div 2/4$ ,  $\div 4/5/6$  clock generation chip designed explicitly for low skew clock generation applications. The internal dividers are synchronous to each other, therefore, the common output edges are all precisely aligned. The device can be driven by either a differential or single-ended ECL/LVECL or, if positive power supplies are used, PECL/LVPECL input signal. In addition, by using the VBB output, a sinusoidal source can be AC-coupled into the device. If a single-ended input is to be used, the VBB output should be connected to the /CLK input and bypassed to ground via a 0.01µF capacitor. The VBB output is designed to act as the switching reference for the input of the S839V under single-ended input conditions. As a result, this pin can only source/sink up to 0.5mA of current.

The common enable (/EN) is synchronous so that the internal dividers will only be enabled/disabled when the internal clock is already in the LOW state. This avoids any chance of generating a runt clock pulse on the internal clock when the device is enabled/disabled as can happen with an asynchronous control. An internal runt pulse could lead to losing synchronization between the internal divider stages. The internal enable flip-flop is clocked on the falling edge of the input clock, therefore, all associated specification limits are referenced to the negative edge of the clock input.

Upon start-up, the internal flip-flops will attain a random state; the master reset (MR) input must be asserted to ensure synchronization. For systems which only use one S839V, the MR pin need not be exercised as the internal divider designs ensures synchronization between the  $\pm 2/4$ , and the  $\pm 4/5/6$  outputs of a single device.

Precision Edge is a registered trademark of Micrel, Inc.

## PACKAGE/ORDERING INFORMATION

## **Ordering Information**

| Part Number                      | Package<br>Type | Operating<br>Range | Package<br>Marking                              | Lead<br>Finish    |

|----------------------------------|-----------------|--------------------|-------------------------------------------------|-------------------|

| SY100S839VZC                     | Z20-1           | Commercial         | SY100S839VZC                                    | Sn-Pb             |

| SY100S839VZCTR <sup>(1)</sup>    | Z20-1           | Commercial         | SY100S839VZC                                    | Sn-Pb             |

| SY100S839VZG <sup>(2)</sup>      | Z20-1           | Industrial         | SY100S839VZG with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| SY100S839VZGTR <sup>(1, 2)</sup> | Z20-1           | Industrial         | SY100S839VZG with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

Notes:

1. Tape and Reel.

2. Pb-Free package is recommended for new designs.

20-Pin SOIC (Z20-1)

## **TRUTH TABLE**

| CLK | /EN | MR | Function   |

|-----|-----|----|------------|

| Z   | L   | L  | Divide     |

| ZZ  | Н   | L  | Hold Q0–3  |

| Х   | Х   | Н  | Reset Q0–3 |

Note:

Z = LOW-to-HIGH transition

ZZ = HIGH-to-LOW transition

| DIVSELa | Q0, Q1 OUTPUTS |

|---------|----------------|

| 0       | Divide by 2    |

| 1       | Divide by 4    |

| DIVSELb1 | DIVSELb0 | Q2, Q3 OUTPUTS |

|----------|----------|----------------|

| 0        | 0        | Divide by 4    |

| 0        | 1        | Divide by 6    |

| 1        | 0        | Divide by 5    |

| 1        | 1        | Divide by 5    |

## **PIN NAMES**

| Pin    | Function                    |

|--------|-----------------------------|

| CLK    | Differential Clock Inputs   |

| /EN    | Synchronous Enable          |

| MR     | Master Reset                |

| VBB    | Reference Output            |

| Q0, Q1 | Differential ÷2/4 Outputs   |

| Q2, Q3 | Differential ÷4/5/6 Outputs |

| DIVSEL | Frequency Select Input      |

## DC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

VEE = VEE (min) to VEE (max); VCC = GND

|        |                                    | T     | A = −40° | $-40^{\circ}C 	TA = 0^{\circ}C$ |       |       | Т     | 4 = +25° | С     | Т     |       |       |       |      |

|--------|------------------------------------|-------|----------|---------------------------------|-------|-------|-------|----------|-------|-------|-------|-------|-------|------|

| Symbol | Parameter                          | Min.  | Тур.     | Max.                            | Min.  | Тур.  | Max.  | Min.     | Тур.  | Max.  | Min.  | Тур.  | Max.  | Unit |

| IEE    | Power Supply Current               | -     | 50       | 95                              | —     | 50    | 95    | —        | 50    | 95    | —     | 54    | 95    | mA   |

| VBB    | Output Reference<br>Voltage        | -1.38 | _        | -1.26                           | -1.38 | —     | -1.26 | -1.38    | —     | -1.26 | -1.38 | —     | -1.26 | V    |

| Іін    | Input High Current                 | _     | _        | 150                             | _     | _     | 150   | _        | _     | 150   | _     | _     | 150   | μA   |

| Vон    | Output HIGH Voltage <sup>(2)</sup> | -1085 | -1005    | -880                            | -1025 | -955  | -880  | -1025    | -955  | -880  | -1025 | -955  | -880  | mV   |

| Vol    | Output LOW Voltage <sup>(2)</sup>  | -1830 | -1695    | -1555                           | -1810 | -1705 | -1620 | -1810    | -1705 | -1620 | -1810 | -1705 | -1620 | mV   |

| Vона   | Output HIGH Voltage <sup>(3)</sup> | -1095 | _        | _                               | -1035 | _     | _     | -1035    | _     | _     | -1035 | _     | —     | mV   |

| Vola   | Output LOW Voltage <sup>(3)</sup>  | _     | _        | -1555                           | _     | _     | -1610 | _        | _     | -1610 | _     | _     | -1610 | mV   |

| Viн    | Input HIGH Voltage                 | -1165 | _        | -880                            | -1165 | _     | -880  | -1165    | _     | -880  | -1165 | _     | -880  | mV   |

| VIL    | Input LOW Voltage                  | -1810 |          | -1475                           | -1810 |       | -1475 | -1810    |       | -1475 | -1810 |       | -1475 | mV   |

| lı∟    | Input LOW Current <sup>(4)</sup>   | 0.5   | _        |                                 | 0.5   | _     | _     | 0.5      | _     | _     | 0.5   |       | _     | μA   |

Note:

1. Parametric values specified at: -3.0V to -3.8V or -4.2V to -5.5V.

2. VIN = VIH(Max) or VIL(Min): Loading with  $50\Omega$  to -2.0V.

3. VIN = VIH(Min) or VIL(Max): Loading with  $50\Omega$  to -2.0V.

4. VIN = VIL(Min).

## AC ELECTRICAL CHARACTERISTICS<sup>(1)</sup>

VEE = VEE (min) to VEE (max); VCC = GND

|          |                                                                                           | TA = −40°C        |      | TA = 0°C          |                   |      | TA = +25°C        |                   |      | TA                |                   |      |                   |      |

|----------|-------------------------------------------------------------------------------------------|-------------------|------|-------------------|-------------------|------|-------------------|-------------------|------|-------------------|-------------------|------|-------------------|------|

| Symbol   | Parameter                                                                                 | Min.              | Тур. | Max.              | Unit |

| fmax     | Maximum Toggle Frequency                                                                  | 1000              | —    | _                 | 1000              |      | _                 | 1000              | _    | _                 | 1000              |      | _                 | MHz  |

| tPD      | Propagation Delay to Output<br>CLK → Output (Diff.)<br>CLK → Output (S.E.)<br>MR → Output | 725<br>675<br>600 |      | 925<br>975<br>900 | 725<br>675<br>600 |      | 925<br>975<br>900 | 725<br>675<br>610 |      | 925<br>975<br>910 | 725<br>675<br>630 |      | 925<br>975<br>930 | ps   |

| tskew    | Within-Device Skew $^{(2)}$ Q0 — Q3Part-to-PartQ0 — Q3 (Diff.)                            | _                 | _    | 50<br>200         |                   |      | 50<br>200         | _                 | _    | 50<br>200         | _                 |      | 50<br>200         | ps   |

| ts       | Set-up Time $/EN \rightarrow /CLK$<br>DIVSEL $\rightarrow CLK$                            | 250<br>400        | _    | _                 | 250<br>400        |      | _                 | 250<br>400        | _    | _                 | 250<br>400        |      | _                 | ps   |

| tн       | Hold Time $/CLK \rightarrow /EN$<br>$CLK \rightarrow DIVSEL$                              | 100<br>150        | _    | _                 | 100<br>150        | -    | _                 | 100<br>150        | _    | _                 | 100<br>150        |      |                   | ps   |

| VPP      | Minimum Input Swing <sup>(3)</sup> CLK                                                    | 250               | —    |                   | 250               | _    | —                 | 250               | —    | _                 | 250               | _    | _                 | mV   |

| VCMR     | Common Mode Range <sup>(4), (5)</sup>                                                     | -1.6              | —    | -0.4              | -1.7              | _    | -0.4              | -1.7              | —    | -0.4              | -1.7              | _    | -0.4              | V    |

| trr      | Reset Recovery Time                                                                       | _                 | _    | 100               | _                 | _    | 100               | _                 | _    | 100               | _                 | _    | 100               | ps   |

| tPW      | Minimum Pulse Width CLK MR                                                                | 500<br>700        | _    | _                 | 500<br>700        |      | _                 | 500<br>700        | _    | _                 | 500<br>700        |      | _                 | ps   |

| tr<br>tf | Output Rise/Fall Times Q<br>(20%—80%)                                                     | 280               | —    | 550               | 280               | _    | 550               | 280               | —    | 550               | 280               | _    | 550               | ps   |

#### Notes:

1. Parametric values specified at: -3.0V to -3.8V or -4.2V to -5.5V.

2. Skew is measured between outputs under identical transitions.

3. Minimum input swing for which AC parameters are guaranteed. The device will function reliably with differential inputs down to 100mV.

4. The CMR range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between VPP min. and 1V. The lower end of the CMR range varies 1:1 with VEE. The numbers in the spec table assume a nominal VEE = -3.3V. Note for PECL operation, the VCMR (min) will be fixed at 3.3V – IVCMR (min)I.

5. Duty Cycle: (Min. 48%; Max. 52%) } over temp.

### LOGIC DIAGRAM

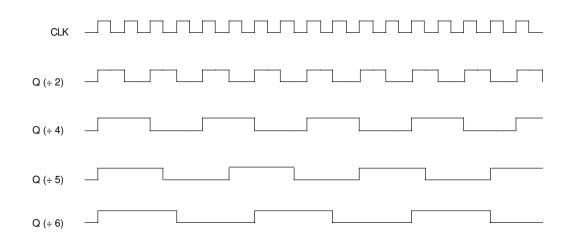

## TIMING DIAGRAMS

### 20-PIN SOIC .300" WIDE (Z20-1)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2006 Micrel, Incorporated.