Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: [info@chipsmall.com](mailto:info@chipsmall.com) Web: [www.chipsmall.com](http://www.chipsmall.com)

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## FEATURES

- Integrated synthesizer plus fanout buffers, clock dividers, and translator in a single 64-pin package

- Accepts any reference input between 14MHz to 160MHz (single-ended or differential)

- 33MHz to 500MHz output frequency range

- LVPECL outputs (SY89534L)

LVPECL and LVDS outputs (SY89535L)

- 3.3V  $\pm 10\%$  power supply

- Low jitter: <50ps cycle-to-cycle

- Low pin-to-pin skew: <50ps

- TTL/CMOS compatible control logic

- 3 independently programmable output frequency banks:

- 9 differential output pairs @BankB (LVPECL/LVDS)

- 2 differential output pairs @BankA (LVPECL)

- 2 differential output pairs @BankC (LVPECL)

- Available in 64-pin EPAD-TQFP

**Precision Edge®**

## DESCRIPTION

The SY89534L and SY89535L programmable clock synthesizers are a 3.3V, high-frequency, precision PLL-based family optimized for multi-frequency, large clock-tree applications that require the highest precision. These devices integrate the following blocks into a single monolithic IC:

- PLL (Phase-Lock-Loop)-based synthesizer

- Fanout buffer

- Clock generator (divider)

- Logic translation (LVPECL, LVDS)

The SY89534L and SY89535L includes a flexible input design that accepts any reference input; single-ended LVTTL/CMOS, SSTL and differential LVPECL, LVDS, HSTL and CML.

This level of integration minimizes the additive jitter and part-to-part skew associated with the discrete alternative, resulting in superior system-level timing as well as reduced board space and power. For applications that must interface to a crystal oscillator, see the SY89532/33.

Data sheets and support documentation can be found on Micrel's web site at [www.micrel.com](http://www.micrel.com).

## APPLICATIONS

- Servers

- Workstations

- Parallel processor-based systems

- Other high-performance computing

- Communications

## PRODUCT SELECTION GUIDE

| Device    | Input   |           | Output |        |        |

|-----------|---------|-----------|--------|--------|--------|

|           | Crystal | Reference | BankA  | BankB  | BankC  |

| SY89532L* | X       |           | LVPECL | LVPECL | LVPECL |

| SY89533L* | X       |           | LVPECL | LVDS   | LVPECL |

| SY89534L  |         | X         | LVPECL | LVPECL | LVPECL |

| SY89535L  |         | X         | LVPECL | LVDS   | LVPECL |

\*Refer to SY89532/33L data sheet for details.

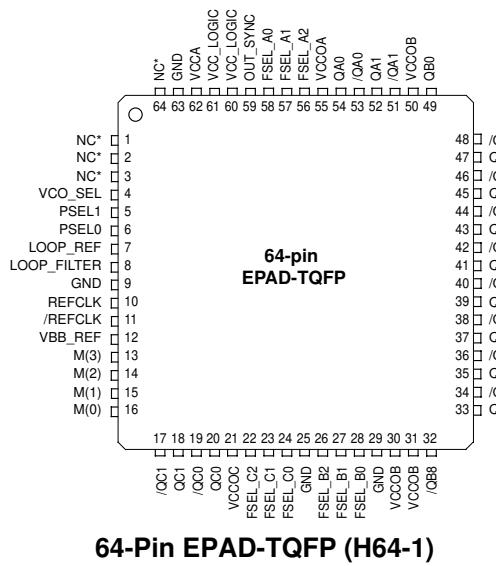

## PACKAGE/ORDERING INFORMATION

\*NC: Do not connect, leave floating.

Ordering Information<sup>(1)</sup>

| Part Number                    | Package Type | Operating Range | Package Marking                            | Lead Finish      |

|--------------------------------|--------------|-----------------|--------------------------------------------|------------------|

| SY89534LHC                     | H64-1        | Commercial      | SY89534LHC                                 | Sn-Pb            |

| SY89534LHCTR <sup>(2)</sup>    | H64-1        | Commercial      | SY89534LHC                                 | Sn-Pb            |

| SY89535LHC                     | H64-1        | Commercial      | SY89535LHC                                 | Sn-Pb            |

| SY89535LHCTR <sup>(2)</sup>    | H64-1        | Commercial      | SY89535LHC                                 | Sn-Pb            |

| SY89534LHZ <sup>(3)</sup>      | H64-1        | Commercial      | SY89534LHZ with Pb-Free bar line indicator | Pb-Free Matte-Sn |

| SY89534LHZTR <sup>(2, 3)</sup> | H64-1        | Commercial      | SY89534LHZ with Pb-Free bar line indicator | Pb-Free Matte-Sn |

| SY89535LHZ <sup>(3)</sup>      | H64-1        | Commercial      | SY89535LHZ with Pb-Free bar line indicator | Pb-Free Matte-Sn |

| SY89535LHZTR <sup>(2, 3)</sup> | H64-1        | Commercial      | SY89535LHZ with Pb-Free bar line indicator | Pb-Free Matte-Sn |

## Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25^\circ\text{C}$ , DC Electricals only.

2. Tape and Reel.

3. Pb-Free package is recommended for new designs.

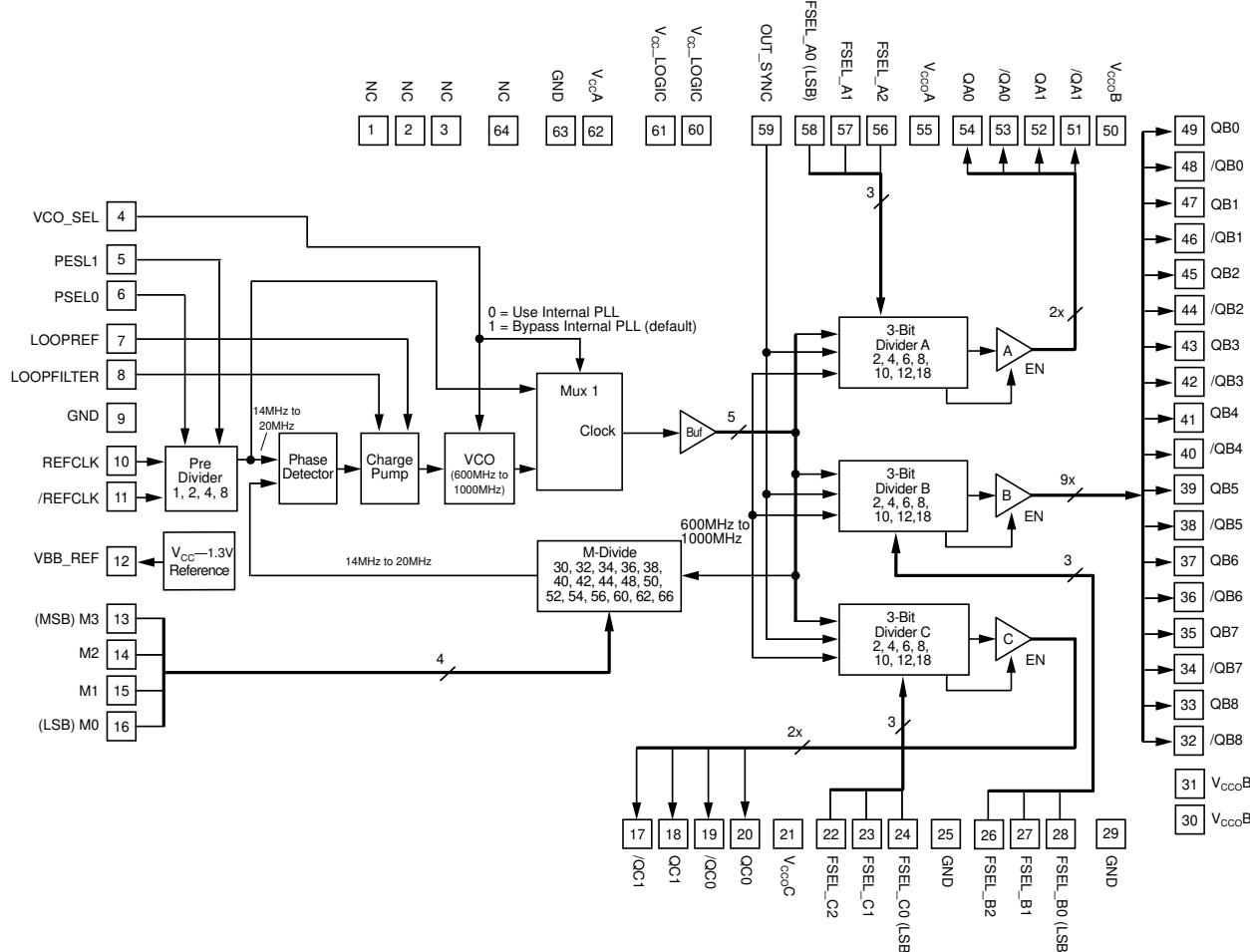

## FUNCTIONAL BLOCK DIAGRAM

**PIN DESCRIPTION****Power**

| Pin Number                        | Pin Name                                                       | Functional Description                                                                                                                             |

|-----------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 60, 61                            | V <sub>CC</sub> _Logic                                         | Power for Core Logic: Connect to 3.3V supply. 3.3V power pins are not internally connected on the die, and must be connected together on the PCB.  |

| 62                                | V <sub>CCA</sub>                                               | Power for PLL: Connect to "quiet" 3.3V supply. 3.3V power pins are not internally connected on the die, and must be connected together on the PCB. |

| 55<br>30, 31, 50<br>21            | V <sub>CCO</sub> A<br>V <sub>CCO</sub> B<br>V <sub>CCO</sub> C | Power for Output Drivers: Connect all V <sub>CCO</sub> pins to 3.3V supply. V <sub>CCO</sub> pins are not connected internally on the die.         |

| 4, 9, 25, 63, 29<br>(exposed pad) | GND                                                            | Ground. All GND pins must be tied together on the PCB. Exposed pad must be soldered to a ground plane.                                             |

**Configuration**

| Pin Number  | Pin Name     | Functional Description                                                                                                                                                                                          |

|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4           | VCO_SEL      | LVTTL/CMOS Compatible Input: Selects between internal or external VCO. When tied LOW (GND) internal VCO is selected. For external VCO, leave floating (default condition is logic HIGH). Internal 25kΩ pull-up. |

| 5, 6        | PSEL(1:0)    | LVTTL/CMOS Compatible Input: Controls input frequency pre divider. Internal 25kΩ pull-up. Default is logic HIGH. See "Pre-Divide Frequency Select" table.                                                       |

| 7           | LOOP REF     | Analog Input/Output: Provides the reference voltage for PLL loop filter.                                                                                                                                        |

| 8           | LOOP FILTER  | Analog Input/Output: Provides the loop filter for PLL. See "External Loop Filter Considerations" for loop filter values.                                                                                        |

| 13,14,15,16 | M (3:0)      | LVTTL/CMOS Compatible Input: Used to change the PLL (Phase-Lock Loop) feedback divider. Internal 25kΩ pull-up. (M0 = LSB). Default is logic HIGH. See "Feedback Divide Select" table.                           |

| 22, 23, 24  | FSEL_C (2:0) | LVTTL/CMOS Compatible Input: Bank C post divide select. Internal 25kΩ pull-up. Default is logic HIGH. See "Post-Divide Frequency Select" table.                                                                 |

| 26, 27, 28  | FSEL_B (2:0) | LVTTL/CMOS Compatible Input: Bank B post divide select. Internal 25kΩ pull-up. Default is logic HIGH. See "Post-Divide Frequency Select" table.                                                                 |

| 56, 57, 58  | FSEL_A (2:0) | LVTTL/CMOS Compatible Input: Bank A post divide select. Internal 25kΩ pull-up. Default is logic HIGH. See "Post-Divide Frequency Select." FSEL_A0 = LSB.                                                        |

| 59          | OUT_SYNC     | Banks A,B,C output synchronous control: (LVTTL/CMOS compatible). Internal 25kΩ pull-up. After any bank has been programmed, toggle with a HIGH-LOW-HIGH pulse to resynchronize all output banks.                |

**Input/Output**

| Pin Number     | Pin Name        | Functional Description                                                                                                                                                                                                   |

|----------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3        | NC              | No Connect: Leave floating.                                                                                                                                                                                              |

| 10, 11         | REFCLK, /REFCLK | Reference Input: This flexible input accepts any input TTL/CMOS, LVPECL, LVDS, HSTL, SSTL. See "Input Interface" section.                                                                                                |

| 12             | VBB_REF         | Reference Output Voltage. Used for single-ended input. Maximum sink/source current = 0.5mA.                                                                                                                              |

| 51, 52, 53, 54 | QA1 to QA0      | Bank A 100k LVPECL Output Drivers: Output frequency is controlled by FSEL_A (0:2). Terminate outputs with 50Ω to V <sub>CC</sub> –2V. See "Output Termination Recommendations" section for termination detail.           |

| 32–49          | QB8 to QB0      | Bank B Output Drivers: SY89534: 100k LVPECL output drivers. SY89535: Differential LVDS outputs. See "Output Termination Recommendations" section for termination detail. Output frequency is controlled by FSEL_B (0:2). |

| 17, 18, 19, 20 | QC1 to QC0      | Bank C 100k LVPECL Output Drivers: Output frequency is controlled by FSEL_C (0:2). Terminate outputs with 50Ω to V <sub>CC</sub> –2V. See "Output Termination Recommendations" section.                                  |

| 64             | NC              | No Connect: Leave floating.                                                                                                                                                                                              |

ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol        | Rating                                                                               | Value                            | Unit                   |

|---------------|--------------------------------------------------------------------------------------|----------------------------------|------------------------|

| All $V_{CC}$  | $V_{CC}$ Pin Potential to Ground Pin                                                 | -0.5 to +4.0                     | V                      |

| $V_{IN}$      | Input Voltage                                                                        | -0.5 to $V_{CCI}$                | V                      |

| $I_{OUT}$     | DC Output Current                                                                    | -LVPECL outputs<br>-LVDS outputs | -50<br>±10<br>mA<br>mA |

| $T_{LEAD}$    | Lead Temperature (soldering, 20sec.)                                                 | 260                              | °C                     |

| $T_{store}$   | Storage Temperature                                                                  | -65 to +150                      | °C                     |

| $\theta_{JA}$ | Package Thermal Resistance (Junction-to-Ambient)<br>With Die attach soldered to GND: | 23<br>18<br>15                   | °C/W<br>°C/W<br>°C/W   |

|               | -Still-Air (TQFP)<br>-200lfpm (TQFP)<br>-500lfpm (TQFP)                              | 44<br>36<br>30                   | °C/W<br>°C/W<br>°C/W   |

|               | With Die attach NOT soldered to GND: <sup>(2)</sup>                                  | 44<br>36<br>30                   | °C/W<br>°C/W<br>°C/W   |

|               | -Still-Air (TQFP)<br>-200lfpm (TQFP)<br>-500lfpm (TQFP)                              | 44<br>36<br>30                   | °C/W<br>°C/W<br>°C/W   |

| $\theta_{JC}$ | Package Thermal Resistance (Junction-to-Case)                                        | 4.4                              | °C/W                   |

## DC ELECTRICAL CHARACTERISTICS

## Power Supply

| Symbol                             | Parameter                                                             | $T_A = 0^\circ C$ |      |      | $T_A = +25^\circ C$ |      |      | $T_A = +85^\circ C$ |      |      | Unit |

|------------------------------------|-----------------------------------------------------------------------|-------------------|------|------|---------------------|------|------|---------------------|------|------|------|

|                                    |                                                                       | Min.              | Typ. | Max. | Min.                | Typ. | Max. | Min.                | Typ. | Max. |      |

| $V_{CCA}^{(3)}$<br>$V_{CC\_LOGIC}$ | PLL and Logic Supply Voltage                                          | 3.0               | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | V    |

| $V_{CCO A/C}$                      | Bank A and C $V_{CC}$ Output                                          | 3.0               | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | V    |

| $V_{CCO B}$                        | Bank B $V_{CC}$ Output<br>LVPECL/LVDS                                 | 3.0               | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | 3.0                 | 3.3  | 3.6  | V    |

| $I_{CC}$                           | Total Supply Current <sup>(4)</sup><br>SY89534L PECL<br>SY89535L LVDS | —                 | —    | 260  | —                   | —    | 260  | —                   | —    | 260  | mA   |

|                                    |                                                                       | —                 | 275  | 330  | —                   | 285  | 330  | —                   | 300  | 330  | mA   |

LVC MOS/LVTTL Input Control Logic (All  $V_{CC}$  pins = +3.3V ±10%)

| Symbol   | Parameter          | $T_A = 0^\circ C$ |      |      | $T_A = +25^\circ C$ |      |      | $T_A = +85^\circ C$ |      |      | Unit |

|----------|--------------------|-------------------|------|------|---------------------|------|------|---------------------|------|------|------|

|          |                    | Min.              | Typ. | Max. | Min.                | Typ. | Max. | Min.                | Typ. | Max. |      |

| $V_{IH}$ | Input HIGH Voltage | 2.0               | —    | —    | 2.0                 | —    | —    | 2.0                 | —    | —    | V    |

| $V_{IL}$ | Input LOW Voltage  | —                 | —    | 0.8  | —                   | —    | 0.8  | —                   | —    | 0.8  | V    |

| $I_{IH}$ | Input HIGH Current | —                 | —    | —    | —                   | —    | 150  | —                   | —    | —    | μA   |

| $I_{IL}$ | Input LOW Current  | —                 | —    | —    | -300                | —    | —    | —                   | —    | —    | μA   |

## NOTES:

1. permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

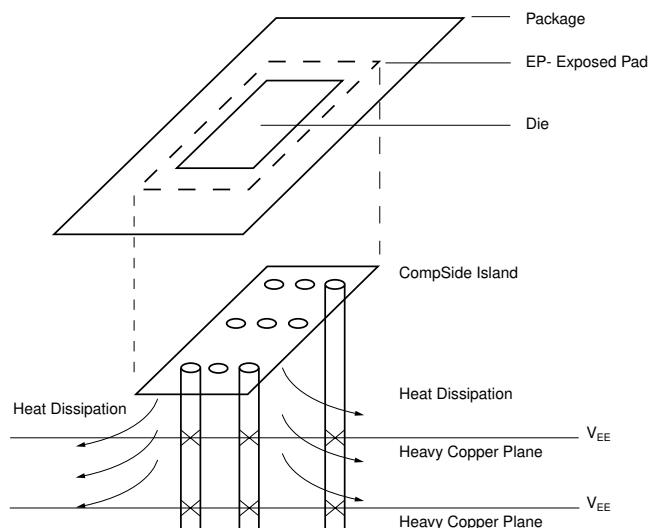

2. It is recommended that the user always solder the exposed die pad to a ground plane for enhanced heat dissipation.

3.  $V_{CCA}$ ,  $V_{CC\_LOGIC}$ ,  $V_{CCO A/C}$ ,  $V_{CCO B}$  are not internally connected together inside the device. They must be connected together on the PCB.

4. No load. Outputs floating, Banks A, B, and C enabled.

## DC ELECTRICAL CHARACTERISTICS

REFCLK (pins 10, 11) INPUT (All  $V_{CC}$  pins = +3.3V  $\pm 10\%$ )

| Symbol   | Parameter                  | $T_A = 0^\circ\text{C}$                  |      |                | $T_A = +25^\circ\text{C}$                |      |                | $T_A = +85^\circ\text{C}$                |      |                | Unit     |

|----------|----------------------------|------------------------------------------|------|----------------|------------------------------------------|------|----------------|------------------------------------------|------|----------------|----------|

|          |                            | Min.                                     | Typ. | Max.           | Min.                                     | Typ. | Max.           | Min.                                     | Typ. | Max.           |          |

| $V_{ID}$ | Differential Input Voltage | 100 <sup>(5)</sup><br>200 <sup>(6)</sup> | —    | —              | 100 <sup>(5)</sup><br>200 <sup>(6)</sup> | —    | —              | 100 <sup>(5)</sup><br>200 <sup>(6)</sup> | —    | —              | mV<br>mV |

| $V_{IH}$ | Input HIGH Voltage         | —                                        | —    | $V_{CC} + 0.3$ | —                                        | —    | $V_{CC} + 0.3$ | —                                        | —    | $V_{CC} + 0.3$ | V        |

| $V_{IL}$ | Input LOW Voltage          | -0.3                                     | —    | —              | -0.3                                     | —    | —              | -0.3                                     | —    | —              | V        |

100K LVPECL Outputs (All  $V_{CC}$  pins = +3.3V  $\pm 10\%$ )

| Symbol   | Parameter                                 | $T_A = 0^\circ\text{C}$                  |                 |                  | $T_A = +25^\circ\text{C}$                |                 |                  | $T_A = +85^\circ\text{C}$                |                 |                  | Unit          |

|----------|-------------------------------------------|------------------------------------------|-----------------|------------------|------------------------------------------|-----------------|------------------|------------------------------------------|-----------------|------------------|---------------|

|          |                                           | Min.                                     | Typ.            | Max.             | Min.                                     | Typ.            | Max.             | Min.                                     | Typ.            | Max.             |               |

| $V_{OH}$ | Output HIGH Voltage <sup>(7)</sup>        | $V_{CC} - 1.075$                         | —               | $V_{CC} - 0.830$ | $V_{CC} - 1.075$                         | —               | $V_{CC} - 0.830$ | $V_{CC} - 1.075$                         | —               | $V_{CC} - 0.830$ | V             |

| $V_{OL}$ | Output LOW Voltage <sup>(7)</sup>         | $V_{CC} - 1.860$                         | —               | $V_{CC} - 1.570$ | $V_{CC} - 1.860$                         | —               | $V_{CC} - 1.570$ | $V_{CC} - 1.860$                         | —               | $V_{CC} - 1.570$ | V             |

| $V_{ID}$ | Differential Input Voltage <sup>(8)</sup> | 100 <sup>(3)</sup><br>200 <sup>(4)</sup> | —               | —                | 100 <sup>(3)</sup><br>200 <sup>(4)</sup> | —               | —                | 100 <sup>(3)</sup><br>200 <sup>(4)</sup> | —               | —                | mV<br>mV      |

| $V_{IH}$ | Input HIGH Voltage <sup>(8)</sup>         | —                                        | —               | $V_{CC} + 0.3$   | —                                        | —               | $V_{CC} + 0.3$   | —                                        | —               | $V_{CC} + 0.3$   | V             |

| $V_{IL}$ | Input LOW Voltage <sup>(8)</sup>          | -0.3                                     | —               | —                | -0.3                                     | —               | —                | -0.3                                     | —               | —                | V             |

| $I_{IH}$ | Input HIGH Current                        | -600                                     | —               | -300             | -600                                     | —               | -300             | -600                                     | —               | -300             | $\mu\text{A}$ |

| $I_{IL}$ | Input LOW Current                         | -1200                                    | —               | -700             | -1200                                    | —               | -700             | -1200                                    | —               | -700             | $\mu\text{A}$ |

| $V_{BB}$ | Output Reference Voltage                  | $V_{CC} - 1.26$                          | $V_{CC} - 1.32$ | $V_{CC} - 1.38$  | $V_{CC} - 1.26$                          | $V_{CC} - 1.32$ | $V_{CC} - 1.38$  | $V_{CC} - 1.26$                          | $V_{CC} - 1.32$ | $V_{CC} - 1.38$  | V             |

LVDS Outputs (SY89535L) Bank B QB0:8<sup>(9)</sup> (All  $V_{CC}$  pins = +3.3V  $\pm 10\%$ )

| Symbol           | Parameter                                    | $T_A = 0^\circ\text{C}$ |      |       | $T_A = +25^\circ\text{C}$ |      |       | $T_A = +85^\circ\text{C}$ |      |       | Unit |

|------------------|----------------------------------------------|-------------------------|------|-------|---------------------------|------|-------|---------------------------|------|-------|------|

|                  |                                              | Min.                    | Typ. | Max.  | Min.                      | Typ. | Max.  | Min.                      | Typ. | Max.  |      |

| $V_{OD}$         | Output Voltage Swing <sup>(9, 10)</sup>      | 250                     | —    | 450   | 250                       | —    | 450   | 250                       | —    | 450   | mV   |

| $V_{OH}$         | Output HIGH Voltage                          | —                       | —    | 1.475 | —                         | —    | 1.475 | —                         | —    | 1.475 | V    |

| $V_{OL}$         | Output LOW Voltage                           | 0.925                   | —    | —     | 0.925                     | —    | —     | 0.925                     | —    | —     | V    |

| $V_{OCM}$        | Output Common Mode Voltage <sup>(9)</sup>    | 1.125                   | —    | 1.375 | 1.125                     | —    | 1.375 | 1.125                     | —    | 1.375 | V    |

| $\Delta V_{OCM}$ | Change in Common Mode Voltage <sup>(9)</sup> | -50                     | —    | 50    | -50                       | —    | 50    | -50                       | —    | 50    | mV   |

## NOTES:

5.  $V_{IN} < 2.4\text{V}$

6.  $V_{IN} < V_{CC} + 0.3\text{V}$

7. 50 $\Omega$  to  $V_{CC} - 2\text{V}$ . Banks A, B, and C enabled.

8.  $V_{CC} = 3.0\text{V}$  to  $3.6\text{V}$ .

9. 100 $\Omega$  termination across differential pair.

## AC ELECTRICAL CHARACTERISTICS

All V<sub>CC</sub> pins = +3.3V ±10%

| Symbol                                    | Parameter                                        | T <sub>A</sub> = 0°C |      |      | T <sub>A</sub> = +25°C |      |      | T <sub>A</sub> = +85°C |      |      | Unit               |

|-------------------------------------------|--------------------------------------------------|----------------------|------|------|------------------------|------|------|------------------------|------|------|--------------------|

|                                           |                                                  | Min.                 | Typ. | Max. | Min.                   | Typ. | Max. | Min.                   | Typ. | Max. |                    |

| f <sub>IN</sub>                           | Reference Input Frequency                        | —                    | —    | —    | 14                     | —    | 160  | —                      | —    | —    | MHz                |

| f <sub>OUT</sub>                          | Output Frequency Range                           | —                    | —    | —    | 33.33                  | —    | 500  | —                      | —    | —    | MHz                |

| t <sub>VCO</sub>                          | Internal VCO Frequency Range                     | 600                  | —    | 1000 | 600                    | —    | 1000 | 600                    | —    | 1000 | MHz                |

| t <sub>skew</sub>                         | Within Device <sup>(11)</sup>                    | —                    | 25   | 50   | —                      | 0    | 50   | —                      | 0    | 50   | ps                 |

|                                           | Within Bank                                      | —                    | 60   | 150  | —                      | 60   | 150  | —                      | 60   | 150  | ps                 |

|                                           | Bank-to-Bank                                     | —                    | —    | —    | —                      | —    | 200  | —                      | —    | 200  | ps                 |

| t <sub>LOCK</sub>                         | Maximum PLL Lock Time                            | —                    | —    | —    | —                      | —    | 10   | —                      | —    | 10   | ms                 |

| t <sub>JITTER</sub>                       | Cycle-to-Cycle Jitter <sup>(13)</sup> (Pk-to-Pk) | —                    | —    | —    | —                      | —    | 50   | —                      | —    | —    | ps                 |

|                                           | Period Jitter <sup>(14)</sup> (rms)              | —                    | —    | 50   | —                      | —    | 50   | —                      | —    | 50   | ps                 |

| t <sub>pw</sub> (min)                     | Minimum Pulse Width                              | —                    | —    | —    | 50                     | —    | —    | 50                     | —    | —    | ns                 |

|                                           | Target PLL Loop Bandwidth                        | —                    | 1.0  | —    | —                      | 1.0  | —    | —                      | 1.0  | —    | MHz                |

|                                           | Feedback Divider Ratio: 66 <sup>(15)</sup>       | —                    | 2.0  | —    | —                      | 2.0  | —    | —                      | 2.0  | —    | MHz                |

|                                           | Feedback Divider Ratio: 30 <sup>(15)</sup>       | —                    | —    | —    | —                      | —    | —    | —                      | —    | —    | —                  |

| t <sub>DC</sub>                           | f <sub>OUT</sub> Duty Cycle                      | —                    | —    | —    | 45                     | 50   | 55   | 45                     | 50   | 55   | %                  |

| t <sub>r</sub> , t <sub>f</sub>           | Output Rise/Fall Time<br>(20% to 80%)            | —                    | —    | 400  | —                      | 250  | 400  | —                      | —    | 400  | ps                 |

|                                           | LVPECL_Out                                       | —                    | —    | 450  | —                      | 300  | 450  | —                      | —    | 450  |                    |

|                                           | (SY89535L) LVDS_Out                              | —                    | —    | —    | —                      | —    | —    | —                      | —    | —    |                    |

| t <sub>OUTPUT_RESET</sub> <sup>(16)</sup> | —                                                | —                    | —    | —    | —                      | —    | 10   | —                      | —    | —    | ns                 |

| t <sub>HOLD_FSEL</sub> <sup>(16)</sup>    | —                                                | —                    | —    | 5    | —                      | —    | —    | —                      | —    | —    | ns                 |

| t <sub>SETUP_FSEL</sub> <sup>(16)</sup>   | —                                                | —                    | —    | 5    | —                      | —    | —    | —                      | —    | —    | ns                 |

| t <sub>OUTPUT_SYNC</sub> <sup>(16)</sup>  | —                                                | —                    | —    | 1    | —                      | —    | —    | —                      | —    | —    | VCO<br>clock cycle |

| FSEL-to-Valid Output Transition Time      | —                                                | —                    | —    | —    | 50                     | —    | —    | —                      | —    | —    | ns                 |

## NOTES:

11. The within-device skew is defined as the worst case difference between any two similar delay paths within a single device operating at the same voltage and temperature.

12. The part-to-part skew is defined as the absolute worst case difference between any two delay paths on any two devices operating at the same voltage and temperature.

13. Cycle-to-cycle jitter definition: The variation in period between adjacent cycles over a random sample of adjacent cycle pairs.  $T_{JITTER\_CC} = T_n - T_{n+1}$  where T is the time between rising edges of the output signal.

14. Period Jitter definition: For a specified amount of time (i.e., 1ms), there are N periods of a signal, and  $T_n$  is defined as the average period of that signal. Period jitter is defined as the variation in the period of the output signal for corresponding edges relative to  $T_n$ . Parameter guaranteed by design and characterization.

15. Using recommended loop filter components.

16. See "Timing Diagrams."

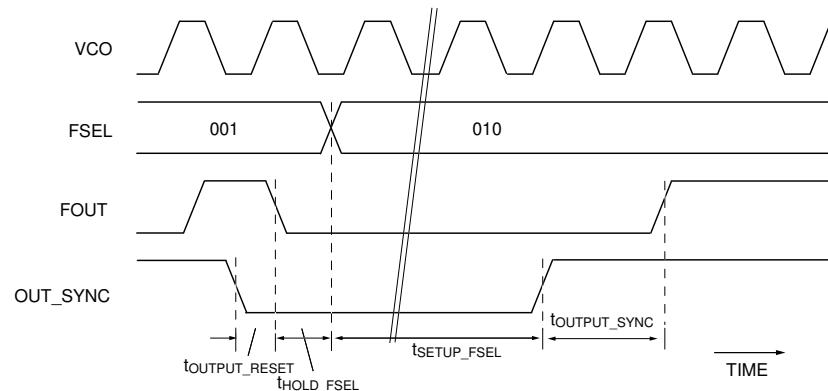

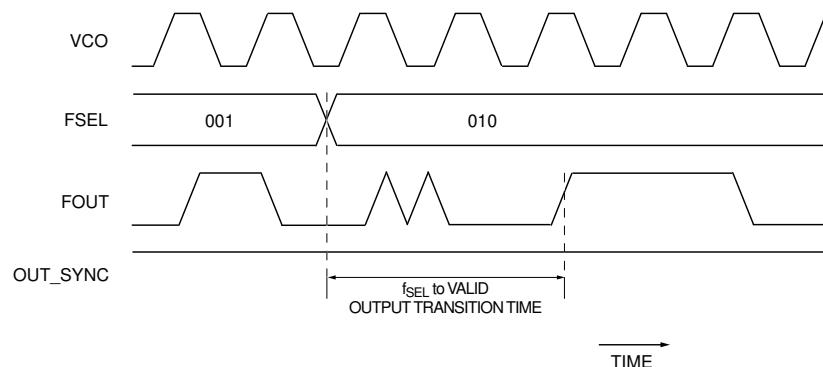

## TIMING DIAGRAMS

(Conditions: Internal VCO, unless otherwise stated.)

**Frequency Programming**

**Output Frequency Updates to Valid Output**

## FUNCTIONAL DESCRIPTION

At the core of the SY89534/35L clock synthesizer is a precision PLL driven by a differential or single-ended reference input. For users who wish to supply a crystal input, please use the SY89532L or SY89533L. The PLL output is sent to three banks of outputs. Each bank has its own programmable frequency divider, and the design is optimized to provide very low skew between banks, and very low jitter.

### PLL Programming and Operation

The internal VCO range is 600MHz to 1000MHz, and the feedback ratio is selectable via the MSEL divider control (M3:0 pins). The feedback ratio can be changed without powering the chip down. The PLL output is fed to three banks of outputs: Bank A, Bank B, and Bank C. Banks A and C each have two differential LVPECL output pairs. Bank B has nine differential output pairs. On the SY89534L, Bank B is LVPECL. On the SY89535L, Bank B is LVDS.

Each bank has a separate frequency divider circuit that can be reprogrammed on the fly. The FSEL\_x0:2 (where x is A, B, or C) pins control the divider value. The FSEL divider can be programmed in ratios from 2 to 18, and the outputs of Banks A, B, and C can be synchronized after programming by pulsing the OUT\_SYNC pin HIGH-LOW-HIGH.

To determine the correct settings for SY89534/35L follow these steps:

1. Refer to the *"Suggested Selections for Specific Customer Applications"* section for common applications, as well as the formula used to compute the output frequency.

2. Determine the desired output frequency, such as 66MHz.

3. Choose a reference input frequency between 14MHz and 20MHz. The user can also choose a higher input frequency, and use the PSEL pre-divider to divide it down to the 14MHz to 20MHz range. In this example, we choose 18MHz for the reference input frequency. This results in an input/output ratio of 66/18.

4. Refer to the *"Feedback Divide Select Table"* and the *"Post-Divide Frequency Select Table"* to find values for MSEL and FSEL such that MSEL/FSEL equals the same 66/18 ratio. In this example, values of MSEL=44 and FSEL=12 work.

5. Make sure that  $\text{REFCLK} \div \text{PSEL} \times \text{MSEL}$  is between 600MHz and 1000MHz.

The user may need to experiment with different REFCLK input frequencies to satisfy these requirements.

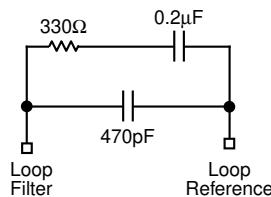

Figure 1. External Loop Filter Connection

### External Loop Filter Considerations

The SY89534/35L features an external PLL loop filter that allows the user to tailor the PLL's behavior to their application and operating environment. We recommend using ceramic capacitors with NPO or X7R dielectric, as they have very low effective series resistance. For applications that require ultra-low cycle-to-cycle jitter, use the components shown in Figure 1. The PLL loop bandwidth is a function of feedback divider ratio, and the external loop filter allows the user to compensate. For instance, the PLL's loop bandwidth can be decreased by using a smaller resistor in the loop filter. This results in less noise from the PLL input, but potentially more noise from the VCO. Refer to *"AC Electrical Characteristics"* for target PLL loop bandwidth. The designer should take care to keep the loop filter components on the same side of the board and as close as possible to the SY89534/35L's LOOP\_REF and LOOP\_FILTER pins. To insure minimal noise pick-up on the loop filter, it is desirable to cut away the ground plane directly underneath the loop filter component pads and traces. However, the benefit may not be significant in all applications and one must be careful to not alter the characteristic impedance of nearby traces.

### Power Supply Filtering Techniques

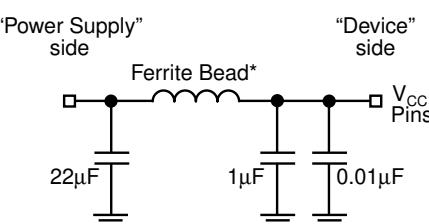

As with any high-speed integrated circuit, power supply filtering is very important. At a minimum,  $V_{CC_A}$ ,  $V_{CC\_Logic}$ , and all  $V_{CC_0}$  pins should be individually connected using a via to the power supply plane, and separate bypass capacitors should be used for each pin. To achieve optimal jitter performance, each power supply pin should use separate instances of the circuit shown in Figure 2.

\*For  $V_{CC\_Analog}$ ,  $V_{CC\_TTL}$ ,  $V_{CC1}$ , use ferrite bead = 200mA, 0.45Ω DC, Murata P/N BLM21A1025

\*For  $V_{CC\_OUT}$  use ferrite bead = 3A, 0.025Ω DC, Murata, P/N BLM31P005

\*Component size: 0805

Figure 2. Power Supply Filtering

## Output Logic Characteristics

See “*Output Termination Recommendations*” for illustrations. In cases where single-ended output is desired, the designer should terminate the unused complimentary output in the same manner as the normal output that is being used. Unused LVPECL output pairs can be left floating. Unused LVDS output pairs should be terminated w/100Ω across the pair.

LVPECL operation:

- Typical voltage swing is 700mV<sub>PP</sub> to 800mV<sub>PP</sub> into 50Ω.

- Common mode voltage is V<sub>CC</sub>–1.3V, typical.

- 100Ω termination across the output pair is NOT recommended for LVPECL. See “*Output Termination*” section, Figures 3 to 5.

LVDS operation (SY89535L, Bank B)

- Typical voltage swing is 250mV<sub>PP</sub> to 450mV<sub>PP</sub> into effective 50Ω.

- Common mode voltage is 1.25V, typical.

- 100Ω termination across differential output pair is fine.

## Thermal Considerations

This part has an exposed die pad for enhanced heat dissipation. We strongly recommend soldering the exposed die pad to a ground plane. Where this is not possible, we recommend maintaining at least 500lfpmp air flow around the part.

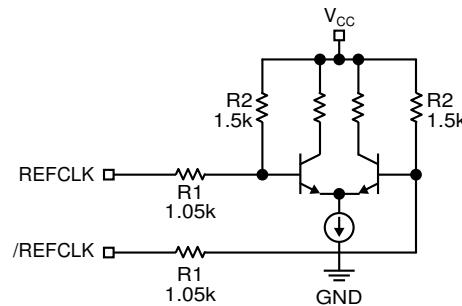

## REFCLK Input Interface

The flexible REFCLK inputs are designed to accept any differential to single-ended input signal within 300mV above V<sub>CC</sub> and 300mV below ground.

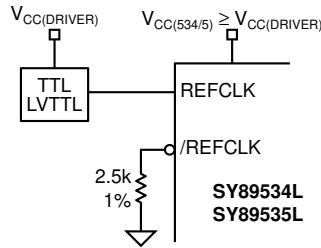

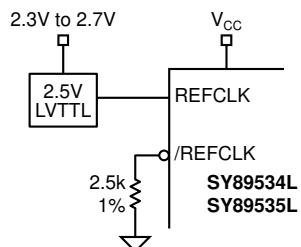

Do not leave unused REFCLK inputs floating. Tie either the true or complement inputs to ground, but not both. A logic zero is achieved by connecting the complement input to ground with the true input floating. For a TTL input, tie a 2.5kΩ resistor between the complement input and ground. See “Input Interface” section, Figures 4a through 4j.

## Input Levels

LVDS, CML and HSTL differential signals may be connected directly to the REFCLK inputs. Depending on the actual worst case voltage seen, the minimum input voltage swing varies as illustrated in the following table:

| Input Voltage Range       | Minimum Voltage Swing |

|---------------------------|-----------------------|

| 0 to 2.4V                 | 100mV                 |

| 0 to V <sub>CC</sub> +0.3 | 200mV                 |

Figure 3. Simplified Input Structure

**PRE-DIVIDE FREQUENCY SELECT TABLE (PSEL)**

| PSEL1 (MSB) | PSEL0 | Reference Input Frequency |

|-------------|-------|---------------------------|

| 0           | 0     | REFCLK ÷ 8                |

| 0           | 1     | REFCLK ÷ 4                |

| 1           | 0     | REFCLK ÷ 2                |

| 1           | 1     | REFCLK ÷ 1                |

**POST-DIVIDE FREQUENCY SELECT TABLE (FSEL)**

| FSEL_A2 <sup>(1)</sup> (MSB) | FSEL_A1 <sup>(1)</sup> | FSEL_A0 <sup>(1)</sup> (LSB) | Output Divider            |

|------------------------------|------------------------|------------------------------|---------------------------|

| 0                            | 0                      | 0                            | Output OFF (Q = /Q = LOW) |

| 0                            | 0                      | 1                            | VCO ÷ 2                   |

| 0                            | 1                      | 0                            | VCO ÷ 4                   |

| 0                            | 1                      | 1                            | VCO ÷ 6                   |

| 1                            | 0                      | 0                            | VCO ÷ 8                   |

| 1                            | 0                      | 1                            | VCO ÷ 10                  |

| 1                            | 1                      | 0                            | VCO ÷ 12                  |

| 1                            | 1                      | 1                            | VCO ÷ 18                  |

**NOTES:**

1. Same dividers apply to FSEL\_B (0:2) and FSEL\_C (0:2).

## FEEDBACK DIVIDE SELECT TABLE (MSEL)

| M3 | M2 | M1 | M0 | VCO Frequency <sup>(1)</sup> |

|----|----|----|----|------------------------------|

| 0  | 0  | 0  | 0  | REFCLK ÷ PSEL × 34           |

| 0  | 0  | 0  | 1  | REFCLK ÷ PSEL × 36           |

| 0  | 0  | 1  | 0  | REFCLK ÷ PSEL × 38           |

| 0  | 0  | 1  | 1  | REFCLK ÷ PSEL × 40           |

| 0  | 1  | 0  | 0  | REFCLK ÷ PSEL × 42           |

| 0  | 1  | 0  | 1  | REFCLK ÷ PSEL × 44           |

| 0  | 1  | 1  | 0  | REFCLK ÷ PSEL × 48           |

| 0  | 1  | 1  | 1  | REFCLK ÷ PSEL × 50           |

| 1  | 0  | 0  | 0  | REFCLK ÷ PSEL × 52           |

| 1  | 0  | 0  | 1  | REFCLK ÷ PSEL × 54           |

| 1  | 0  | 1  | 0  | REFCLK ÷ PSEL × 56           |

| 1  | 0  | 1  | 1  | REFCLK ÷ PSEL × 60           |

| 1  | 1  | 0  | 0  | REFCLK ÷ PSEL × 62           |

| 1  | 1  | 0  | 1  | REFCLK ÷ PSEL × 66           |

| 1  | 1  | 1  | 0  | REFCLK ÷ PSEL × 30           |

| 1  | 1  | 1  | 1  | REFCLK ÷ PSEL × 32           |

## SUGGESTED SELECTIONS FOR SPECIFIC CUSTOMER APPLICATIONS

| Protocol      | Rate (MHz) | FSEL (Post Divider) | MSEL (Feedback Div.) | REFCLK (MHz) | PSEL | FOUT |

|---------------|------------|---------------------|----------------------|--------------|------|------|

| PCI           | 33         | 18                  | 36                   | 16.67        | 1    | 33   |

| Fast Ethernet | 100        | 6                   | 40                   | 15           | 1    | 100  |

| 1/8 FC        | 133        | 6                   | 52                   | 15.36        | 1    | 133  |

| ESCON         | 200        | 4                   | 50                   | 16           | 1    | 200  |

$$FOUT = \frac{(REFCLK \div PSEL \times MSEL)}{FSEL}$$

## NOTES:

1.  $600\text{MHz} < (REFCLK \div PSEL \times MSEL) < 1000\text{MHz}$ .

2.  $14\text{MHz} \leq (REFCLK \div PSEL) \leq 20\text{MHz}$ .

3. Where two settings provide the user with the identical desired frequency, the setting with the higher PLL input reference frequency (and lower feedback divider) will usually have lower output jitter. However, the reference input frequency, as well as the VCO frequency, must be kept within their respective ranges.

## INPUT INTERFACE

Figure 4a. 5V, 3.3V "TTL"

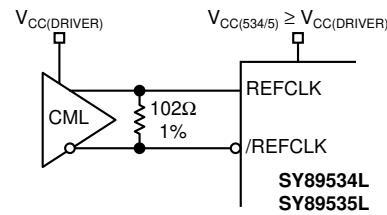

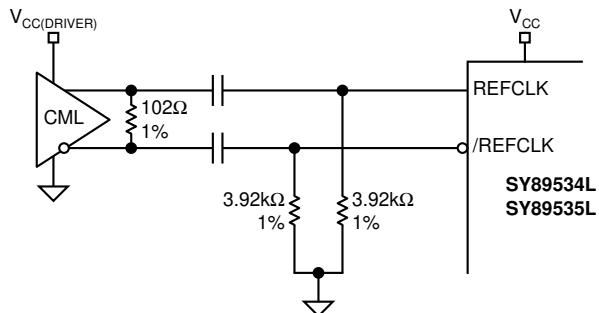

Figure 4b. CML-DC Coupled

Figure 4c. 2.5V "LVTTL"

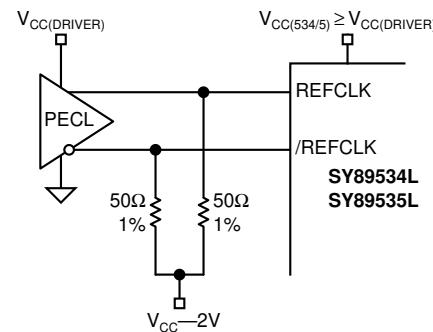

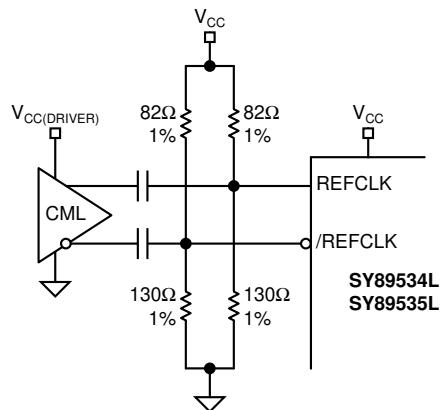

Figure 4d. 3.3V LVPECL-DC Coupled

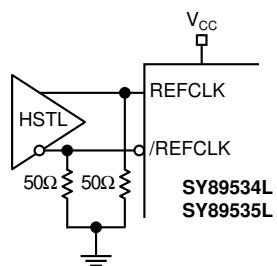

Figure 4e. HSTL

Figure 4f. CML-AC Coupled-Short Trace Lengths

Figure 4g. CML-AC Coupled-Long Trace Lengths

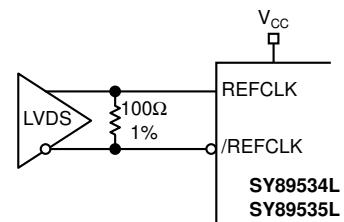

Figure 4h. LVDS

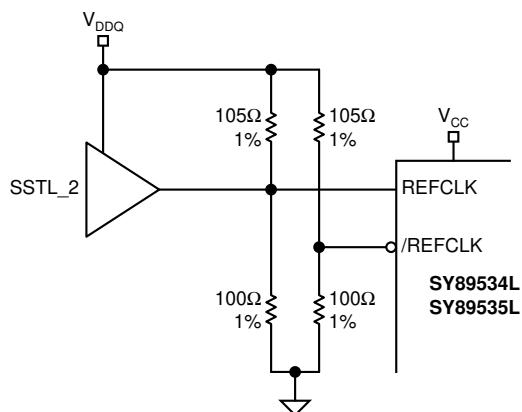

Figure 4i. SSTL\_2

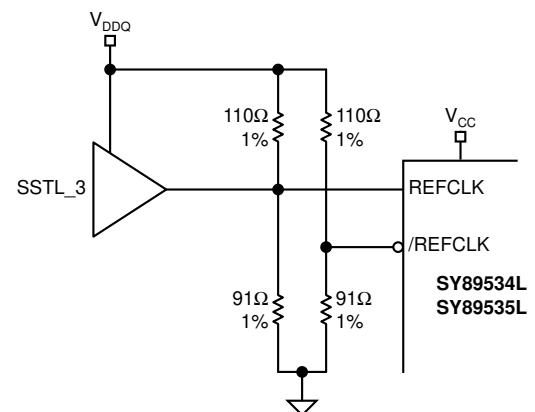

Figure 4j. SSTL\_3

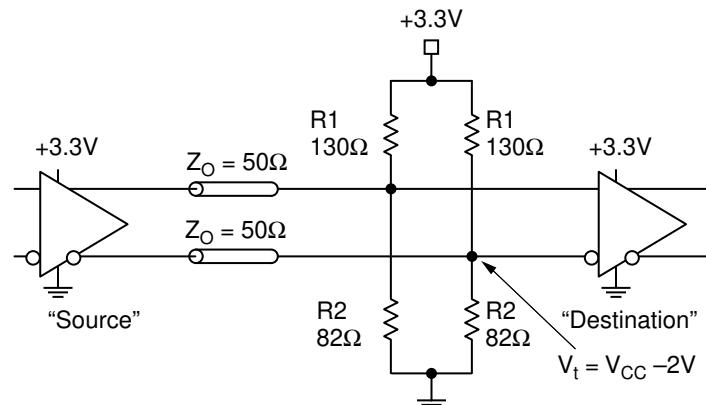

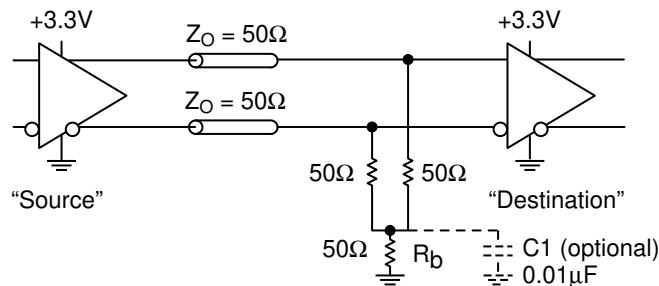

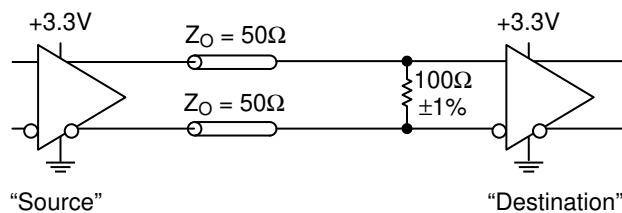

## OUTPUT TERMINATION RECOMMENDATIONS

Figure 5. PECL Parallel Termination—Thevenin Equivalent

Figure 6. PECL Three-Resistor "Y-Termination"

Figure 7. LVDS Differential Termination

## NOTES:

1. PECL Y-termination is a power-saving alternative to Thevenin termination.

2. Place termination resistors as close to destination inputs as possible.

3.  $R_b$  resistor sets the DC bias voltage, equal to  $V_t$ . For  $+3.3V$  systems  $R_b = 46\Omega$  to  $50\Omega$ .

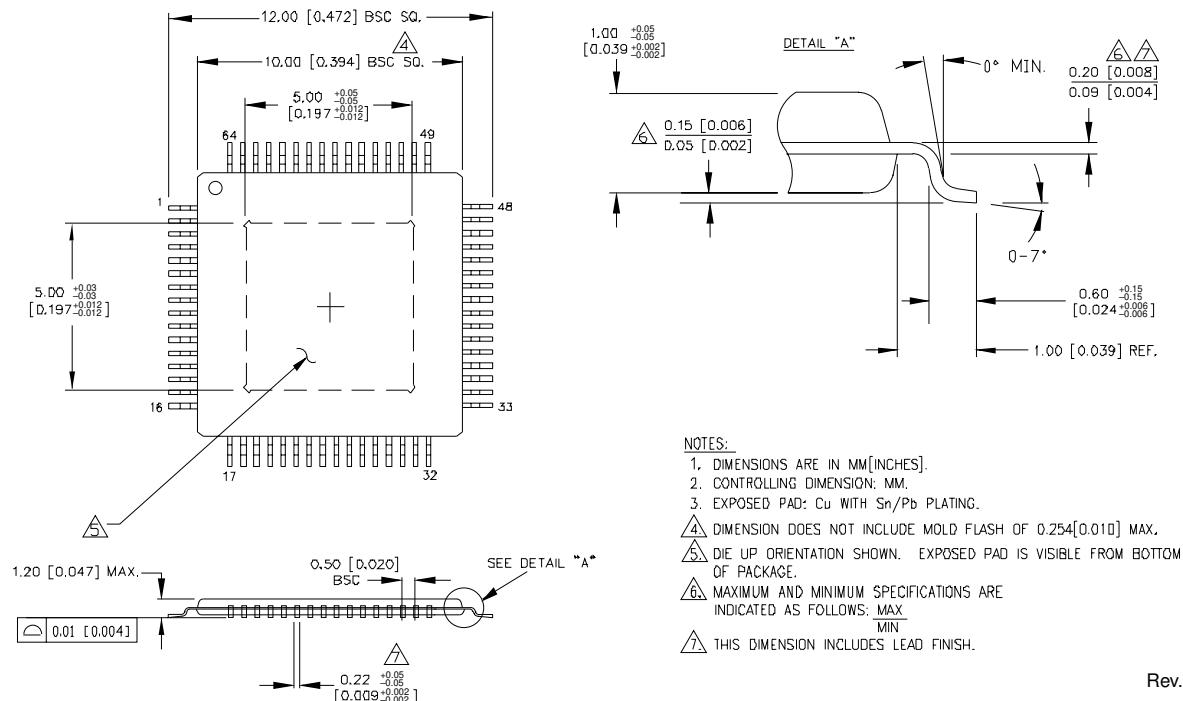

## 64-PIN EPAD-TQFP (DIE UP) (H64-1)

Rev 02

## PCB Thermal Consideration for 64-Pin EPAD-TQFP Package

---

MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB <http://www.micrel.com>

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use.

Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2005 Micrel, Incorporated.