Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Features**

- Supply Voltage up to 40 V

- R<sub>DSon</sub> Typically 0.5  $\Omega$  at 25°C, Maximum 1.1  $\Omega$  at 150°C

- Up to 1.5 A Output Current

- Three Half-bridge Outputs Formed by Three High-side and Three Low-side Drivers

- Capable to Switch all Kinds of Loads Such as DC Motors, Bulbs, Resistors, Capacitors and Inductors

- No Shoot-through Current

- Very Low Quiescent Current  $I_S < 5 \mu A$  in Standby Mode versus Total Temperature Range

- Outputs Short-circuit Protected

- Overtemperature Protection for Each Switch and Overtemperature Prewarning

- Undervoltage Protection

- Various Diagnostic Functions Such as Shorted Output, Open-load, Overtemperature and Power-supply Fail Detection

- Serial Data Interface, Daisy Chain Capable, up to 2 MHz Clock Frequency

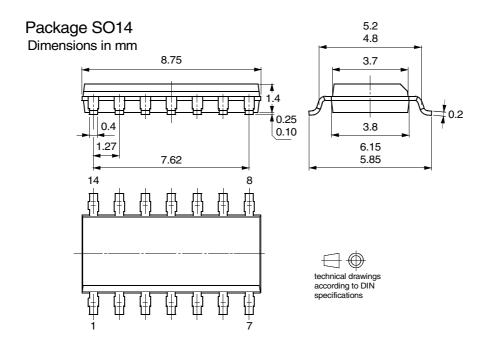

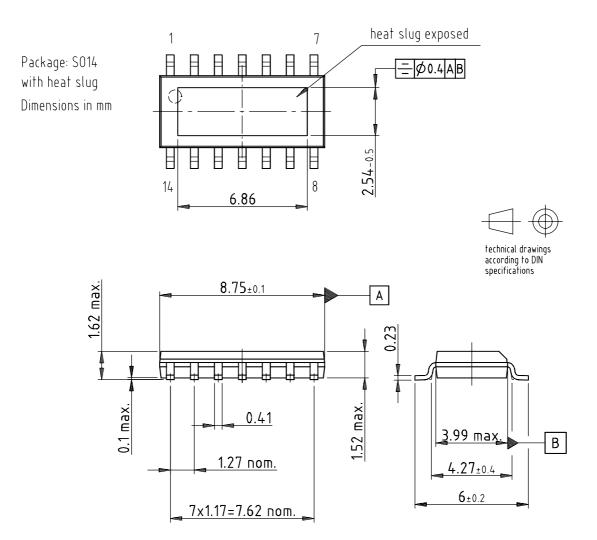

- SO14 Power Package

### **Description**

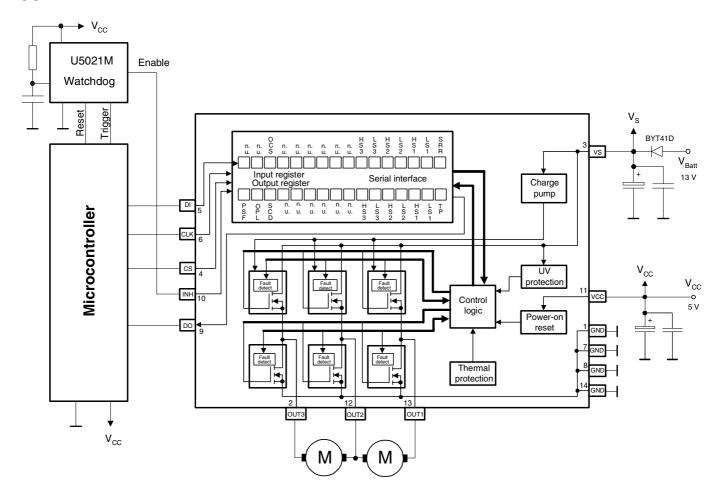

The T6818/T6828 are fully protected driver interfaces designed in 0.8-µm BCDMOS technology. They are used to control up to 3 different loads by a microcontroller in automotive and industrial applications.

Each of the 3 high-side and 3 low-side drivers is capable to drive currents up to 1.5 A. The drivers are internally connected to form 3 half-bridges and can be controlled separately from a standard serial data interface. Therefore, all kinds of loads such as bulbs, resistors, capacitors and inductors can be combined. The IC design especially supports the application of H-bridges to drive DC motors.

Protection is guaranteed regarding short-circuit conditions, overtemperature and undervoltage. Various diagnostic functions and a very low quiescent current in stand-by-mode opens a wide range of applications. Automotive qualification (protection against conducted interferences, EMC protection and 2-kV ESD protection) gives added value and enhanced quality for exacting requirements of automotive applications.

# Triple Halfbridge DMOS Output Driver with Serial Input Control

T6818/T6828

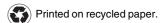

Figure 1. Block Diagram

## **Pin Configuration**

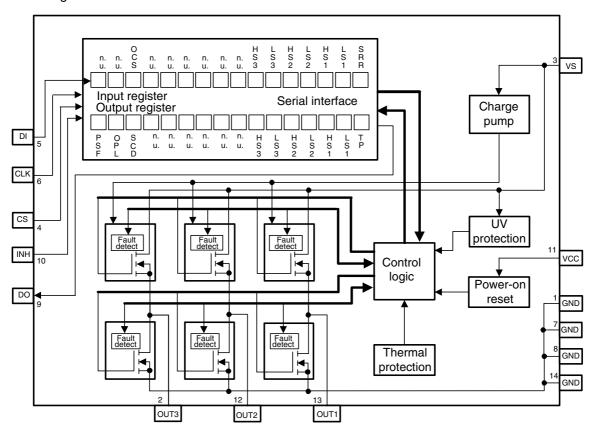

Figure 2. Pining SO14

## **Pin Description**

| Pin | Symbol | Function                                                                                                                                                                                                                                                                                                              |

|-----|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GND    | T6818: ground; reference potential; internal connection to pin 7, 8 and 14; cooling tab                                                                                                                                                                                                                               |

| '   | GND    | T6828: additional connection to heat slug                                                                                                                                                                                                                                                                             |

| 2   | OUT3   | Half-bridge output 3; formed by internally connected power MOS high-side switch 3 and low-side switch 3 with internal reverse diodes; short circuit protection; overtemperature protection; diagnosis for short and open load                                                                                         |

| 3   | VS     | Power supply for output stages OUT1, OUT2 and OUT3, internal supply                                                                                                                                                                                                                                                   |

| 4   | CS     | Chip select input; 5-V CMOS logic level input with internal pull up;                                                                                                                                                                                                                                                  |

| 4   | US     | low = serial communication is enabled, high = disabled                                                                                                                                                                                                                                                                |

| 5   | DI     | Serial data input; 5-V CMOS logic level input with internal pull down; receives serial data from the control device; DI expects a 16-bit control word with LSB being transferred first                                                                                                                                |

| 6   | CLK    | Serial clock input; 5-V CMOS logic level input with internal pull down;                                                                                                                                                                                                                                               |

| 0   | CLK    | controls serial data input interface and internal shift register (f <sub>max</sub> = 2 MHz)                                                                                                                                                                                                                           |

| 7   | GND    | Ground; see pin 1                                                                                                                                                                                                                                                                                                     |

| 8   | GND    | Ground; see pin 1                                                                                                                                                                                                                                                                                                     |

| 9   | DO     | Serial data output; 5-V CMOS logic level tri-state output for output (status) register data; sends 16-bit status information to the microcontroller (LSB is transferred first); output will remain tri-stated unless device is selected by CS = low, therefore, several ICs can operate on one data output line only. |

| 10  | INH    | Inhibit input; 5-V logic input with internal pull down; low = standby, high = normal operation                                                                                                                                                                                                                        |

| 11  | VCC    | Logic supply voltage (5 V)                                                                                                                                                                                                                                                                                            |

| 12  | OUT2   | Half-bridge output 2; see pin 2                                                                                                                                                                                                                                                                                       |

| 13  | OUT1   | Half-bridge output 1; see pin 2                                                                                                                                                                                                                                                                                       |

| 14  | GND    | Ground; see pin 1                                                                                                                                                                                                                                                                                                     |

### **Functional Description**

### **Serial Interface**

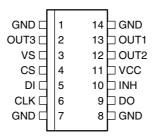

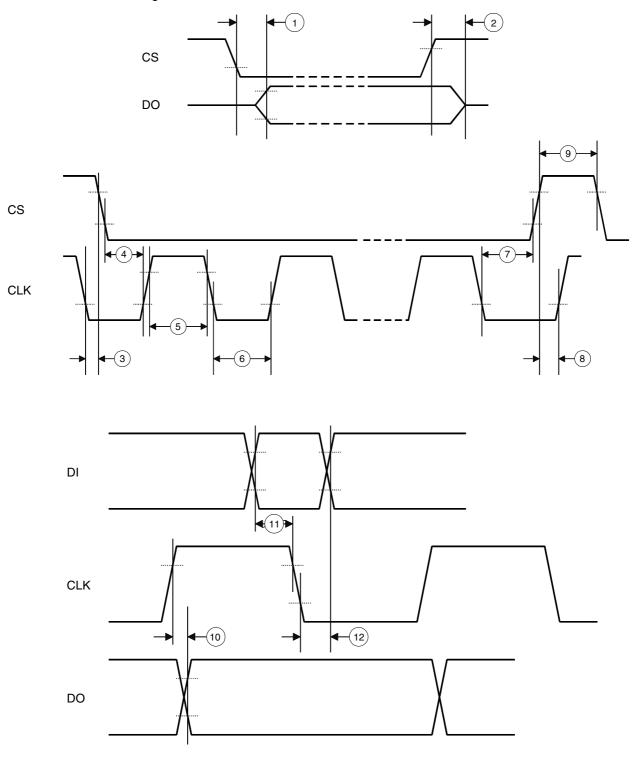

Data transfer starts with the falling edge of the CS signal. Data must appear at DI synchronized to CLK and are accepted on the falling edge of the CLK signal. LSB (bit 0, SRR) has to be transferred first. Execution of new input data is enabled on the rising edge of the CS signal. When CS is high, pin DO is in tri-state condition. This output is enabled on the falling edge of CS. Output data will change their state with the rising edge of CLK and stay stable until the next rising edge of CLK appears. LSB (bit 0, TP) is transferred first.

Figure 3. Data Transfer

Table 1. Input Data Protocol

| Bit | Input Register | Function                                                                                                   |

|-----|----------------|------------------------------------------------------------------------------------------------------------|

| 0   | SRR            | Status register reset (high = reset; the bits PSF, OPL and SCD in the output data register are set to low) |

| 1   | LS1            | Controls output LS1 (high = switch output LS1 on)                                                          |

| 2   | HS1            | Controls output HS1 (high = switch output HS1 on)                                                          |

| 3   | LS2            | See LS1                                                                                                    |

| 4   | HS2            | See HS1                                                                                                    |

| 5   | LS3            | See LS1                                                                                                    |

| 6   | HS3            | See HS1                                                                                                    |

| 7   | n. u.          | Not used                                                                                                   |

| 8   | n. u.          | Not used                                                                                                   |

| 9   | n. u.          | Not used                                                                                                   |

| 10  | n. u.          | Not used                                                                                                   |

| 11  | n. u.          | Not used                                                                                                   |

| 12  | n. u.          | Not used                                                                                                   |

| 13  | ocs            | Overcurrent shutdown (high = overcurrent shutdown is active)                                               |

| 14  | n. u.          | Not used                                                                                                   |

| 15  | n. u.          | Not used                                                                                                   |

Table 2. Output Data Protocol

| Bit | Output (Status)<br>Register | Function                                                                                                                                                                            |

|-----|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | TP                          | Temperature prewarning: high = warning                                                                                                                                              |

| 1   | Status LS1                  | High = output is on, low = output is off; not affected by SRR                                                                                                                       |

| 2   | Status HS1                  | High = output is on, low = output is off; not affected by SRR                                                                                                                       |

| 3   | Status LS2                  | Description see LS1                                                                                                                                                                 |

| 4   | Status HS2                  | Description see HS1                                                                                                                                                                 |

| 5   | Status LS3                  | Description see LS1                                                                                                                                                                 |

| 6   | Status HS3                  | Description see HS1                                                                                                                                                                 |

| 7   | n. u.                       | Not used                                                                                                                                                                            |

| 8   | n. u.                       | Not used                                                                                                                                                                            |

| 9   | n. u.                       | Not used                                                                                                                                                                            |

| 10  | n. u.                       | Not used                                                                                                                                                                            |

| 11  | n. u.                       | Not used                                                                                                                                                                            |

| 12  | n. u.                       | Not used                                                                                                                                                                            |

| 13  | SCD                         | Short circuit detected: set high when at least one high-side or low-side switch is switched off by a short-circuit condition. Bits 1 to 6 can be used to detect the shorted switch. |

| 14  | OPL                         | Open load detected: set high, when at least one active high-side or low-side switch sinks/sources a current below the open load threshold current.                                  |

| 15  | PSF                         | Power-supply fail: undervoltage at pin VS detected                                                                                                                                  |

After power-on reset, the input register has the following status:

| Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

|        |        | (OCS)  |        |        |        |       |       |       | (HS3) | (LS3) | (HS2) | (LS2) | (HS1) | (LS1) | (SRR) |

| х      | х      | Н      | х      | х      | х      | х     | х     | х     | L     | L     | L     | L     | L     | L     | L     |

The following patterns are used to enable internal test modes of the IC. It is not recommended to use these patterns during normal operation.

| Bit 15 | Bit 14 | Bit 13<br>(OCS) | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6<br>(HS3) | Bit 5<br>(LS3) | Bit 4<br>(HS2) | Bit 3<br>(LS2) | Bit 2<br>(HS1) | Bit 1<br>(LS1) | Bit 0<br>(SRR) |

|--------|--------|-----------------|--------|--------|--------|-------|-------|-------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Н      | Н      | Н               | Н      | Н      | L      | L     | L     | L     | L              | L              | L              | L              | L              | L              | L              |

| Н      | Н      | Н               | L      | L      | Н      | Н     | L     | L     | L              | L              | L              | L              | L              | L              | L              |

| Н      | Н      | Н               | L      | L      | L      | L     | Н     | Н     | L              | L              | L              | L              | L              | L              | L              |

### **Power-supply Fail**

In case of undervoltage at pin VS, the Power-Supply Fail bit (PSF) in the output register is set and all outputs are disabled. To detect an undervoltage, its duration has to last longer than the undervoltage detection delay time  $t_{\text{dUV}}$ . The outputs are enabled immediately when supply voltage recovers normal operation value. The PSF bit stays high until it is reset by the SRR bit in the input register.

### **Open-load Detection**

If the current through a high-side or low-side switch in ON-state stays below the open-load detection threshold, the open-load detection bit (OPL) in the output register is set.

The OPL bit stays high until it is reset by the SRR bit in the input register. To detect an open load, its duration has to last longer than the open-load detection delay time  $t_{dSd}$ .

# Overtemperature Protection

If the junction temperature of one or more output stages exceeds the thermal prewarning threshold,  $T_{jPW \, set}$ , the temperature prewarning bit (TP) in the output register is set. When the temperature falls below the thermal prewarning threshold,  $T_{jPW \, reset}$ , the bit TP is reset. The TP bit can be read without transferring a complete 16-bit data word. The status of TP is available at pin DO with the falling edge of CS. After the microcontroller has read this information, CS is set high and the data transfer is interrupted without affecting the status of input and output registers.

If the junction temperature of one or more output stages exceeds the thermal shutdown threshold,  $T_{j \text{ switch off}}$ , all outputs are disabled and the corresponding bits in the output register are set to low. The outputs can be enabled again when the temperature falls below the thermal shutdown threshold,  $T_{j \text{ switch on}}$  and the SRR bit in the input register is set to high. Hysteresis of thermal prewarning and shutdown threshold avoids oscillations.

### **Short-circuit Protection**

The output currents are limited by a current regulator. Overcurrent detection is activated by writing a high to the OCS bit in the input register. When the current in an output stage exceeds the overcurrent limitation and shutdown threshold, it is switched off after a delay time ( $t_{dSd}$ ). The short-circuit detection bit (SCD) is set and the corresponding status bit in the output register is set to low. For OCS = low the overcurrent shutdown is inactive. The SCD bit is also set if the current exceeds the overcurrent limitation and shutdown threshold, but the outputs are not affected. By writing a high to the SRR bit in the input register the SCD bit is reset and the disabled outputs are enabled.

### Inhibit

0 V applied to pin 10 (INH) inhibits the T6818/T6828.

All output switches are then turned off and switched to tri-state. The data in the output register are deleted. The current consumption is reduced to less than 5  $\mu$ A at pin VS and less than 25  $\mu$ A at pin VCC. The output switches can be activated again by switching pin 10 (INH) to 5 V which initiates an internal power-on reset.

### **Absolute Maximum Ratings**

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

All values refer to GND pins.

| Parameters                                           | Pin                           | Symbol                                                                 | Value                                        | Unit |

|------------------------------------------------------|-------------------------------|------------------------------------------------------------------------|----------------------------------------------|------|

| Supply voltage                                       | 3                             | V <sub>vs</sub>                                                        | -0.3 to +40                                  | V    |

| Supply voltage<br>t < 0.5 s; I <sub>S</sub> > -2 A   | 3                             | V <sub>VS</sub>                                                        | -1                                           | V    |

| Logic supply voltage                                 | 11                            | V <sub>vcc</sub>                                                       | -0.3 to +7                                   | V    |

| Logic input voltage                                  | 4 to 6, 10                    | $V_{CS}, V_{DI}, V_{CLK}, V_{INH}$                                     | -0.3 to V <sub>VCC</sub> +0.3                | V    |

| Logic output voltage                                 | 9                             | V <sub>DO</sub>                                                        | -0.3 to V <sub>VCC</sub> +0.3                | V    |

| Input current                                        | 4 to 6, 10                    | I <sub>CS</sub> ,I <sub>DI</sub> , I <sub>CLK</sub> , I <sub>INH</sub> | -10 to +10                                   | mA   |

| Output current                                       | 9                             | I <sub>DO</sub>                                                        | -10 to +10                                   | mA   |

| Output current                                       | 2, 12 and 13                  | I <sub>Out3</sub> , I <sub>Out2,</sub> I <sub>Out1</sub>               | Internally limited, see output specification |      |

| Output voltage                                       | 2, 12 and 13                  | I <sub>Out3</sub> , I <sub>Out2,</sub> I <sub>Out1</sub>               | -0.3 to +40                                  | V    |

| Reverse conducting current $(t_{pulse} = 150 \mu s)$ | 2, 12 and 13<br>towards pin 3 | I <sub>Out3</sub> , I <sub>Out2</sub> , I <sub>Out1</sub>              | 17                                           | А    |

| Junction temperature range                           |                               | T <sub>J</sub>                                                         | -40 to +150                                  | °C   |

| Storage temperature range                            |                               | T <sub>STG</sub>                                                       | -55 to +150                                  | °C   |

### **Thermal Resistance**

| Parameters       | Test Conditions                                  | Symbol            | Value | Unit |

|------------------|--------------------------------------------------|-------------------|-------|------|

| T6818            |                                                  |                   |       |      |

| Junction pin     | Measured to GND<br>Pins 1, 7, 8 and 14           | R <sub>thJP</sub> | 30    | K/W  |

| Junction ambient |                                                  | R <sub>thJA</sub> | 65    | K/W  |

| T6828            |                                                  |                   |       |      |

| Junction pin     | Measured to heat slug<br>GND pins 1, 7, 8 and 14 | R <sub>thJP</sub> | 5     | K/W  |

| Junction ambient |                                                  | $R_{thJA}$        | 30    | K/W  |

## **Operating Range**

| Parameters                       | Symbol                                                                 | Value                                | Unit |

|----------------------------------|------------------------------------------------------------------------|--------------------------------------|------|

| Supply voltage                   | V <sub>VS</sub>                                                        | V <sub>UV</sub> <sup>(1)</sup> to 40 | V    |

| Logic supply voltage             | V <sub>vcc</sub>                                                       | 4.75 to 5.25                         | V    |

| Logic input voltage              | V <sub>CS</sub> ,V <sub>DI</sub> , V <sub>CLK</sub> , V <sub>INH</sub> | -0.3 to V <sub>VCC</sub>             | V    |

| Serial interface clock frequency | f <sub>CLK</sub>                                                       | 2                                    | MHz  |

| Junction temperature range       | T <sub>j</sub>                                                         | -40 to +150                          | °C   |

Note: 1. Threshold for undervoltage detection

### **Noise and Surge Immunity**

| Parameters               | Test Conditions | Value                  |

|--------------------------|-----------------|------------------------|

| Conducted interferences  | ISO 7637-1      | Level 4 <sup>(1)</sup> |

| Interference suppression | VDE 0879 Part 2 | Level 5                |

| ESD (Human Body Model)   | ESD S 5.1       | 2 kV                   |

| ESD (Machine Model)      | JEDEC A115A     | 200 V                  |

Note: 1. Test pulse 5:  $V_{smax} = 40 \text{ V}$

### **Electrical Characteristics**

$7.5~V < V_{VS} < 40~V; \ 4.75~V < V_{VCC} < 5.25~V; \ INH = High; \ -40^{\circ}C < T_{j} < 150^{\circ}C; \ unless otherwise specified, \ all \ values \ refer \ to \ GND \ pins.$

| No. | Parameters                        | Test Conditions                                          | Pin | Symbol                    | Min. | Тур. | Max. | Unit | Type* |

|-----|-----------------------------------|----------------------------------------------------------|-----|---------------------------|------|------|------|------|-------|

| 1   | <b>Current Consumption</b>        |                                                          |     |                           |      |      |      |      |       |

| 1.1 | Quiescent current VS              | V <sub>VS</sub> < 20 V, INH = low                        | 3   | I <sub>VS</sub>           |      | 1    | 5    | μA   | Α     |

| 1.2 | Quiescent current VCC             | 4.75 V < V <sub>VCC</sub> < 5.25 V,<br>INH = low         | 11  | I <sub>vcc</sub>          |      | 15   | 25   | μΑ   | А     |

| 1.3 | Supply current VS                 | V <sub>VS</sub> < 20 V normal operating, all outputs off | 3   | I <sub>VS</sub>           |      | 4    | 6    | mA   | А     |

| 1.4 | Supply current VCC                | 4.75 V < V <sub>VCC</sub> < 5.25 V, normal operating     | 11  | I <sub>vcc</sub>          |      | 350  | 500  | μΑ   | Α     |

| 1.5 | Discharge current VS              | $V_{VS} = 32.5 \text{ V},$<br>INH = low                  | 3   | I <sub>VS</sub>           | 0.5  |      | 5.5  | mA   | Α     |

| 1.6 | Discharge current VS              | V <sub>VS</sub> = 40 V,<br>INH = low                     | 3   | I <sub>VS</sub>           | 2.5  |      | 10   | mA   | Α     |

| 2   | Undervoltage Detection            | n, Power-on Reset                                        |     |                           |      |      |      |      |       |

| 2.1 | Power-on reset threshold          |                                                          | 11  | V <sub>VCC</sub>          | 3.2  | 3.9  | 4.4  | V    | А     |

| 2.2 | Power-on reset delay time         | After switching on V <sub>CC</sub>                       |     | t <sub>dPor</sub>         | 30   | 95   | 190  | μs   | А     |

| 2.3 | Undervoltage-detection threshold  | V <sub>CC</sub> = 5 V                                    | 3   | V <sub>Uv</sub>           | 5.6  |      | 7.0  | V    | А     |

| 2.4 | Undervoltage-detection hysteresis | V <sub>CC</sub> = 5 V                                    | 3   | $\Delta V_{Uv}$           |      | 0.6  |      | V    | А     |

| 2.5 | Undervoltage-detection delay time |                                                          |     | t <sub>dUV</sub>          | 10   |      | 40   | μs   | Α     |

| 3   | Thermal Prewarning ar             | nd Shutdown                                              |     | 1                         |      |      |      |      |       |

| 3.1 | Thermal prewarning set            |                                                          |     | T <sub>jPW set</sub>      | 120  | 145  | 170  | °C   | В     |

| 3.2 | Thermal prewarning reset          |                                                          |     | T <sub>jPW reset</sub>    | 105  | 130  | 155  | °C   | В     |

| 3.3 | Thermal prewarning hysteresis     |                                                          |     | $\Delta T_{ m jPW}$       |      | 15   |      | °C   | В     |

| 3.4 | Thermal shutdown off              |                                                          |     | T <sub>j switch off</sub> | 150  | 175  | 200  | °C   | В     |

| 3.5 | Thermal shutdown on               |                                                          |     | T <sub>j switch on</sub>  | 135  | 160  | 185  | °C   | В     |

<sup>\*)</sup> Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on output stages to 90% of final level. Device not in standby for t > 1 ms

## **Electrical Characteristics (Continued)**

$7.5~V < V_{VS} < 40~V; \ 4.75~V < V_{VCC} < 5.25~V; \ INH = High; \ -40^{\circ}C < T_{j} < 150^{\circ}C; \ unless otherwise specified, \ all \ values \ refer \ to \ GND \ pins.$

| No.  | Parameters                                              | Test Conditions                                               | Pin          | Symbol                                              | Min. | Тур. | Max. | Unit | Type* |

|------|---------------------------------------------------------|---------------------------------------------------------------|--------------|-----------------------------------------------------|------|------|------|------|-------|

| 3.6  | Thermal shutdown hysteresis                             |                                                               |              | $\Delta T_{j \text{ switch off}}$                   |      | 15   |      | °C   | В     |

| 3.7  | Ratio thermal shutdown off/thermal prewarning set       |                                                               |              | T <sub>j switch off/</sub><br>T <sub>jPW set</sub>  | 1.05 | 1.2  |      |      | В     |

| 3.8  | Ratio thermal shutdown on/thermal prewarning reset      |                                                               |              | T <sub>j</sub> switch on/<br>T <sub>jPW reset</sub> | 1.05 | 1.2  |      |      | В     |

| 4    | Output Specification (                                  | OUT1-OUT3)                                                    |              |                                                     |      |      |      |      |       |

| 4.1  | On resistance                                           | I <sub>Out 1-3</sub> = -1.3 A                                 | 2, 12,<br>13 | R <sub>DSOn1-3</sub>                                |      |      | 1.1  | Ω    | Α     |

| 4.2  | Off resistance                                          | I <sub>Out 1-3</sub> = 1.3 A                                  | 2, 12,<br>13 | R <sub>DSOn1-3</sub>                                |      |      | 1.1  | Ω    | Α     |

| 4.3  | High-side output leakage current                        | V <sub>Out 1-3</sub> = 0 V <sub>,</sub><br>output stages off  | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 | -15  |      |      | μΑ   | А     |

| 4.4  | Low-side output leakage current                         | V <sub>Out 1-3</sub> = V <sub>VS</sub> ,<br>output stages off | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 |      |      | 200  | μΑ   | Α     |

| 4.5  | High-side switch reverse diode forward voltage          | I <sub>Out 1-3</sub> = 1.5 A                                  | 2, 12,<br>13 | V <sub>Out1-3</sub> - V <sub>VS</sub>               |      |      | 1.5  | V    | А     |

| 4.6  | Low-side switch reverse diode forward voltage           | I <sub>Out 1-3</sub> = -1.5 A                                 | 2, 12,<br>13 | V <sub>Out 1-3</sub>                                | -1.5 |      |      | V    | А     |

| 4.7  | High-side overcurrent limitation and shutdown threshold |                                                               | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 | -2.5 | -2   | -1.5 | А    | А     |

| 4.8  | Low-side overcurrent limitation and shutdown threshold  |                                                               | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 | 1.5  | 2    | 2.5  | Α    | А     |

| 4.9  | Overcurrent shutdown delay time                         |                                                               |              | t <sub>dSd</sub>                                    | 10   |      | 40   | μs   | А     |

| 4.10 | High-side open-load detection threshold                 |                                                               | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 | -45  | -30  | -15  | mA   | А     |

| 4.11 | Low-side open-load detection threshold                  |                                                               | 2, 12,<br>13 | I <sub>Out1-3</sub>                                 | 15   | 30   | 45   | mA   | Α     |

| 4.12 | Open-load detection delay time                          |                                                               |              | t <sub>dSd</sub>                                    | 200  |      | 600  | μs   | А     |

| 4.13 | High-side output switch on delay <sup>(1)</sup>         | $V_{VS} = 13 \text{ V}$ $R_{Load} = 30 \Omega$                |              | t <sub>don</sub>                                    |      |      | 20   | μs   | А     |

| 4.14 | Low-side output switch on delay <sup>(1)</sup>          | $V_{VS} = 13 V$<br>$R_{Load} = 30 \Omega$                     |              | t <sub>don</sub>                                    |      |      | 20   | μs   | А     |

| 4.15 | High-side output switch off delay <sup>(1)</sup>        | $V_{VS} = 13 \text{ V}$ $R_{Load} = 30 \Omega$                |              | t <sub>doff</sub>                                   |      |      | 20   | μs   | А     |

<sup>\*)</sup> Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on output stages to 90% of final level. Device not in standby for t > 1 ms

## **Electrical Characteristics (Continued)**

$7.5~V < V_{VS} < 40~V$ ;  $4.75~V < V_{VCC} < 5.25~V$ ; INH = High;  $-40^{\circ}C < T_{j} < 150^{\circ}C$ ; unless otherwise specified, all values refer to GND pins.

| No.  | Parameters                                                 | Test Conditions                                | Pin      | Symbol                               | Min.                      | Тур. | Max.                      | Unit | Type* |  |

|------|------------------------------------------------------------|------------------------------------------------|----------|--------------------------------------|---------------------------|------|---------------------------|------|-------|--|

| 4.16 | Low-side output switch off delay <sup>(1)</sup>            | $V_{VS} = 13 V$<br>$R_{Load} = 30 \Omega$      |          | t <sub>doff</sub>                    |                           |      | 3                         | μs   | А     |  |

| 4.17 | Dead time between corresponding high-and low-side switches | $V_{VS} = 13 \text{ V}$ $R_{Load} = 30 \Omega$ |          | t <sub>don</sub> - t <sub>doff</sub> | 1                         |      |                           | μs   | Α     |  |

| 5    | Logic Inputs DI, CLK, CS, INH                              |                                                |          |                                      |                           |      |                           |      |       |  |

| 5.1  | Input voltage low-level threshold                          |                                                | 4-6, 10  | V <sub>IL</sub>                      | 0.3 ×<br>V <sub>VCC</sub> |      |                           | V    | А     |  |

| 5.2  | Input voltage high-level threshold                         |                                                | 4-6, 10  | V <sub>IH</sub>                      |                           |      | 0.7 ×<br>V <sub>VCC</sub> | V    | А     |  |

| 5.3  | Hysteresis of input voltage                                |                                                | 4-6, 10  | $\Delta V_{I}$                       | 50                        |      | 700                       | mV   | В     |  |

| 5.4  | Pull-down current pin DI, CLK, INH                         | $V_{DI}$ , $V_{CLK}$ , $V_{INH} = V_{CC}$      | 5, 6, 10 | I <sub>PD</sub>                      | 10                        |      | 65                        | μΑ   | А     |  |

| 5.5  | Pull-up current<br>Pin CS                                  | V <sub>CS</sub> = 0 V                          | 4        | I <sub>PU</sub>                      | -65                       |      | -10                       | μΑ   | А     |  |

| 6    | Serial Interface – Logic                                   | Output DO                                      |          |                                      |                           |      |                           |      |       |  |

| 6.1  | Output-voltage low level                                   | I <sub>DOL</sub> = 2 mA                        | 9        | $V_{DOL}$                            |                           |      | 0.4                       | V    | Α     |  |

| 6.2  | Output-voltage high level                                  | I <sub>DOL</sub> = -2 mA                       | 9        | $V_{DOH}$                            | V <sub>VCC</sub> - 0.7 V  |      |                           | V    | А     |  |

| 6.3  | Leakage current (tri-state)                                | $V_{CS} = V_{CC}$<br>$0V < V_{DO} < V_{VCC}$   | 9        | I <sub>DO</sub>                      | -10                       |      | 10                        | μΑ   | А     |  |

| 7    | Inhibit Input - Timing                                     |                                                |          |                                      |                           |      |                           |      |       |  |

| 7.1  | Delay time from standby to normal operation                |                                                |          | t <sub>dINH</sub>                    |                           |      | 100                       | μs   | А     |  |

<sup>\*)</sup> Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Delay time between rising edge of input signal at pin CS after data transmission and switch on output stages to 90% of final level. Device not in standby for t > 1 ms

## **Serial Interface – Timing**

| No.  | Parameters                      | Test Conditions          | Pin | Timing Chart No.(1) | Symbol                | Min. | Тур. | Max. | Unit | Type* |

|------|---------------------------------|--------------------------|-----|---------------------|-----------------------|------|------|------|------|-------|

| 8.1  | DO enable after CS falling edge | C <sub>DO</sub> = 100 pF | 9   | 1                   | t <sub>ENDO</sub>     |      |      | 200  | ns   | D     |

| 8.2  | DO disable after CS rising edge | C <sub>DO</sub> = 100 pF | 9   | 2                   | t <sub>DISDO</sub>    |      |      | 200  | ns   | D     |

| 8.3  | DO fall time                    | C <sub>DO</sub> = 100 pF | 9   | -                   | t <sub>DOf</sub>      |      |      | 100  | ns   | D     |

| 8.4  | DO rise time                    | C <sub>DO</sub> = 100 pF | 9   | -                   | t <sub>DOr</sub>      |      |      | 100  | ns   | D     |

| 8.5  | DO valid time                   | C <sub>DO</sub> = 100 pF | 9   | 10                  | t <sub>DOVal</sub>    |      |      | 200  | ns   | D     |

| 8.6  | CS setup time                   |                          | 4   | 4                   | t <sub>CSSethl</sub>  | 225  |      |      | ns   | D     |

| 8.7  | CS setup time                   |                          | 4   | 8                   | t <sub>CSSetIh</sub>  | 225  |      |      | ns   | D     |

| 8.8  | CS high time                    |                          | 4   | 9                   | t <sub>CSh</sub>      | 500  |      |      | ns   | D     |

| 8.9  | CLK high time                   |                          | 6   | 5                   | t <sub>CLKh</sub>     | 225  |      |      | ns   | D     |

| 8.10 | CLK low time                    |                          | 6   | 6                   | t <sub>CLKI</sub>     | 225  |      |      | ns   | D     |

| 8.11 | CLK period time                 |                          | 6   | -                   | t <sub>CLKp</sub>     | 500  |      |      | ns   | D     |

| 8.12 | CLK setup time                  |                          | 6   | 7                   | t <sub>CLKSethl</sub> | 225  |      |      | ns   | D     |

| 8.13 | CLK setup time                  |                          | 6   | 3                   | t <sub>CLKSetlh</sub> | 225  |      |      | ns   | D     |

| 8.14 | DI setup time                   |                          | 5   | 11                  | t <sub>Diset</sub>    | 40   |      |      | ns   | D     |

| 8.15 | DI hold time                    |                          | 5   | 12                  | t <sub>DIHold</sub>   | 40   |      |      | ns   | D     |

<sup>\*)</sup> Type means: A =100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. See Figure 4 on page 12

Figure 4. Serial Interface Timing with Chart Numbers

Inputs DI, CLK, CS: High level = 0.7  $\times$  V<sub>CC</sub>, low level = 0.3  $\times$  V<sub>CC</sub> Output DO: High level = 0.8  $\times$  V<sub>CC</sub>, low level = 0.2  $\times$  V<sub>CC</sub>

## **Application Circuit**

### **Application Notes**

It is strongly recommended to connect the blocking capacitors at  $V_{CC}$  and  $V_{S}$  as close as possible to the power supply and GND pins.

Recommended value for capacitors at V<sub>S</sub>:

Electrolytic capacitor C > 22  $\mu$ F in parallel with a ceramic capacitor C = 100 nF. Value for electrolytic capacitor depends on external loads, conducted interferences and reverse conducting current I<sub>Out1,2,3</sub> (see "Absolute Maximum Ratings" on page 7).

Recommended value for capacitors at V<sub>CC</sub>:

Electrolytic capacitor C > 10  $\mu$ F in parallel with a ceramic capacitor C = 100 nF.

To reduce thermal resistance it is recommended to place cooling areas on the PCB as close as possible to the GND pins.

Negative spikes at the output pins (e.g. negative spikes caused by an inductive load switched off with a high side driver) may activate the overtemperature protection function of the T6818/T6828. In this condition, all outputs will be switched off simultaneously. If this behavior is not acceptable or compatible with your application functionally, it is necessary, that for switching on required outputs again, the SRR bit (Status Register Reset) is set, to ensure a reset of the overtemperature function.

## **Ordering Information**

| Extended Type Number | Package | Remarks                                        |  |

|----------------------|---------|------------------------------------------------|--|

| T6818-TUS            | SO14    | Power package, tubed                           |  |

| T6818-TUQ            | SO14    | Power package, taped and reeled                |  |

| T6828-T2S            | SO14    | Power package with heat slug, tubed            |  |

| T6828-T2Q            | SO14    | Power package with heat slug, taped and reeled |  |

## **Package Information**

Drawing-No.: 6.541-5051.01-4

Issue: 1; 25.02.02

## **Revision History**

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

Changes from Rev. 4530C - 11/03 to Rev. 4530D - 04/04

1. Features on page 1 changed.

Changes from Rev. 4530D - 04/04 to Rev. 4530E - 07/04

1. Table "Ordering Information" on page 14 changed.

### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### **Regional Headquarters**

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong Tel: (852) 2721-9778

Tel: (852) 2721-9778 Fax: (852) 2722-1369

### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18 Fax: (33) 2-40-18-19-60

### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00 Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

**Disclaimer:** Atmel Corporation makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel's Terms and Conditions located on the Company's web site. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel are granted by the Company in connection with the sale of Atmel products, expressly or by implication. Atmel's products are not authorized for use as critical components in life support devices or systems.

#### © Atmel Corporation 2004. All rights reserved.

Atmel® and combinations thereof are the registered trademarks of Atmel Corporation or its subsidiaries.

Other terms and product names may be the trademarks of others.