# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

TOSHIBA BiCD Integrated Circuit Silicon Monolithic

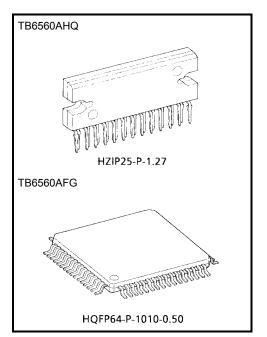

# TB6560AHQ, TB6560AFG

PWM Chopper-Type Bipolar Driver IC for Stepping Motor Control

The TB6560AHQ/AFG is a PWM chopper-type stepping motor driver IC designed for sinusoidal-input microstep control of bipolar stepping motors. The TB6560AHQ/AFG can be used in applications that require 2-phase, 1-2-phase, 2W1-2-phase and 4W1-2-phase excitation modes. The TB6560AHQ/AFG is capable of low-vibration, high-performance forward and reverse driving of a two-phase bipolar stepping motor using only a clock signal.

#### Features

- Single-chip motor driver for sinusoidal microstep control of stepping motors

- High output withstand voltage due to the use of BiCD process: Ron (upper and lower sum) =

TB6560AHQ: 0.6  $\Omega$  (typ.) TB6560AFG: 0.7  $\Omega$  (typ.)

- Forward and reverse rotation

- Selectable phase excitation modes (2, 1-2, 2W1-2 and 4W1-2)

- High output withstand voltage: VDSS = 40 V

- High output current: I<sub>OUT</sub> = TB6560AHQ: 3.5 A (peak) TB6560AFG: 2.5 A (peak)

- Packages: HZIP25-P-1.27 HQFP64-P-1010-0.50

- Internal pull-down resistors on inputs:  $100 \text{ k}\Omega$  (typ.)

- Output monitor pin: MO current (IMO (max) = 1 mA)

- Reset and enable pins

- Thermal shutdown (TSD)

Weight HZIP25-P-1.27: 9.86 g (typ.) HQFP64-P-1010-0.50: 0.26 g (typ.)

\*: These ICs are highly sensitive to electrostatic discharge. When handling them, ensure that the environment is protected against electrostatic discharge. Ensure also that the ambient temperature and relative humidity are maintained at reasonable level.

### **TOSHIBA**

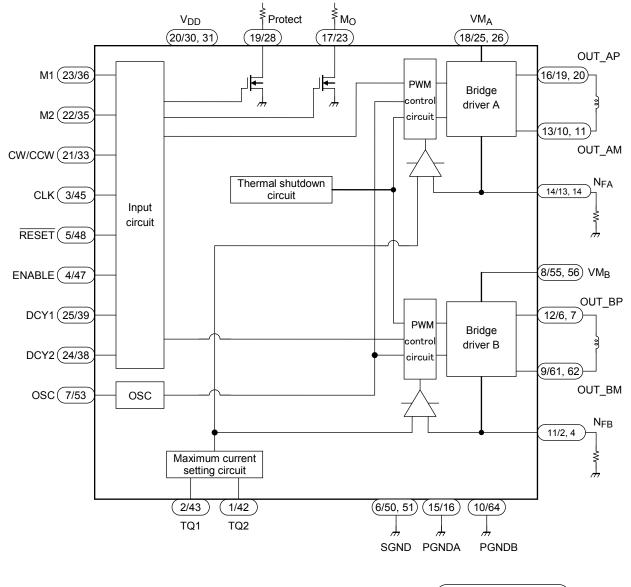

#### **Block Diagram**

(TB6560AHQ/TB6560AFG)

#### **Pin Functions**

| Pin           | No.           |        |                 |                                                                                                               |                             |

|---------------|---------------|--------|-----------------|---------------------------------------------------------------------------------------------------------------|-----------------------------|

| TB6560<br>AHQ | TB6560<br>AFG | I/O    | Symbol          | Functional Description                                                                                        | Remarks                     |

| 1             | 42            | Input  | TQ2             | Torque setting input (current setting)                                                                        | Internal pull-down resistor |

| 2             | 43            | Input  | TQ1             | Torque setting input (current setting)                                                                        | Internal pull-down resistor |

| 3             | 45            | Input  | CLK             | Clock input for microstepping                                                                                 | Internal pull-down resistor |

| 4             | 47            | Input  | ENABLE          | H: Enable; L: All outputs OFF                                                                                 | Internal pull-down resistor |

| 5             | 48            | Input  | RESET           | L: Reset (The outputs are reset to their initial states.)                                                     | Internal pull-down resistor |

| 6             | 50/51         | —      | SGND            | Signal ground (for control block)                                                                             | (Note 1)                    |

| 7             | 53            | _      | OSC             | A CR oscillation circuit is connected to this pin. Performs output chopping.                                  |                             |

| 8             | 55/56         | Input  | VMB             | Motor power supply pin (for phase-B driver)                                                                   | (Note 1)                    |

| 9             | 61/62         | Output | OUT_BM          | OUT_B output                                                                                                  | (Note 1)                    |

| 10            | 64 (*)        |        | PGNDB           | Power ground                                                                                                  |                             |

| 11            | 2/4 (*)       | _      | N <sub>FB</sub> | Connection pin for a B-channel current sensing resistor Two pins of the TB6560AFG should be short-circuited.  | (Note 1)                    |

| 12            | 6/7           | Output | OUT_BP          | OUT_B output                                                                                                  | (Note 1)                    |

| 13            | 10/11         | Output | OUT_AM          | OUT_A output                                                                                                  | (Note 1)                    |

| 14            | 13/14 (*)     | _      | N <sub>FA</sub> | Connection pin for an A-channel current sensing resistor Two pins of the TB6560AFG should be short-circuited. | (Note 1)                    |

| 15            | 16            | _      | PGNDA           | Power ground                                                                                                  |                             |

| 16            | 19/20         | Output | OUT_AP          | OUT_A output                                                                                                  | (Note 1)                    |

| 17            | 23            | Output | Mo              | Initial state sensing output. This pin is enabled in the initial state.                                       | Open drain                  |

| 18            | 25/26         | Input  | VMA             | Motor power supply pin (for phase-A driver)                                                                   | (Note 1)                    |

| 19            | 28            | Output | Protect         | When TSD is activated: High; when in normal state: High-Z.                                                    | Open drain                  |

| 20            | 30/31         | Input  | V <sub>DD</sub> | Power supply pin for control block                                                                            | (Note 1)                    |

| 21            | 33            | Input  | CW/CCW          | Rotation direction select input.<br>L: Clockwise; H: Counterclockwise                                         | Internal pull-down resistor |

| 22            | 35            | Input  | M2              | Excitation mode setting input                                                                                 | Internal pull-down resistor |

| 23            | 36            | Input  | M1              | Excitation mode setting input                                                                                 | Internal pull-down resistor |

| 24            | 38            | Input  | DCY2            | Current decay mode setting input                                                                              | Internal pull-down resistor |

| 25            | 39            | Input  | DCY1            | Current decay mode setting input                                                                              | Internal pull-down resistor |

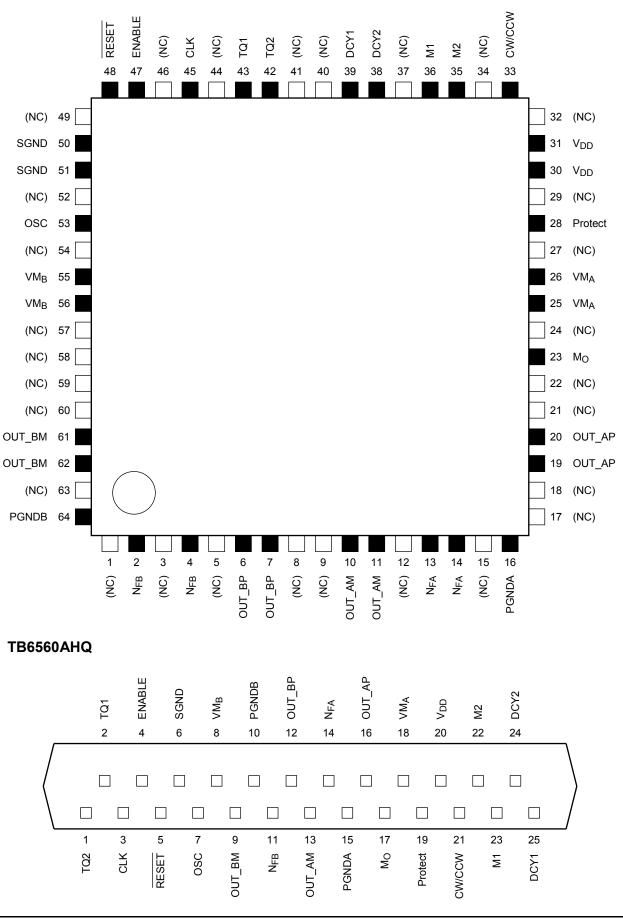

(\*): The pin assignment of the TB6560AFG is different from that of the TB6560FG.

TB6560AHQ: There is no no-connect (NC) pin.

TB6560AFG: Except the above pins, all pins are NC. The pin numbers of NC pins are: 1, 3, 5, 8, 9, 12, 15, 17, 18, 21, 22, 24, 27, 29, 32, 34, 37, 40, 41, 44, 46, 49, 52, 54, 57, 58, 59, 60, and 63.

Applying a voltage to NC pins does not cause any problem since they are not connected inside the IC.

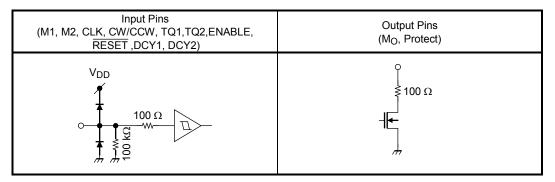

All control input pins have an internal pull-down resistor of 100 k $\Omega$  (typ.)

Note 1: As for the TB6560AFG, two pins that have the same functionality should be short-circuited at a location as close to the TB6560AFG as possible.

(The electrical characteristics provided in this document are measured when those pins are handled in this manner.)

#### **Equivalent Circuits**

### **TOSHIBA**

#### Pin Assignment (top view)

TB6560AFG

Absolute Maximum Ratings ( $T_a = 25^{\circ}C$ )

| Characteristics              |      |           | Symbol            | Rating          | Unit |

|------------------------------|------|-----------|-------------------|-----------------|------|

| Power supply yelts           |      |           |                   | 6               | V    |

| Power supply volta           | ge   |           | VM <sub>A/B</sub> | 40              | v    |

| Output current               | Peak | TB6560AHQ |                   | 3.5             | А    |

| (per phase)                  | геак | TB6560AFG | lo (PEAK)         | 2.5             | A    |

| M <sub>O</sub> drain current |      |           | I (M∘)            | 1               | mA   |

| Protect drain current        |      |           | I (Protect)       | 1               | mA   |

| Input voltage                |      |           | V <sub>IN</sub>   | V <sub>DD</sub> | V    |

|                              |      | TB6560AHQ |                   | 5 (Note 1)      |      |

| Dower dissinction            |      | TBODOUARQ | D-                | 43 (Note 2)     | W    |

| Power dissipation            |      | TB6560AFG | PD                | 1.7 (Note 3)    | vv   |

|                              |      | TB0500AFG |                   | 4.2 (Note 4)    |      |

| Operating temperature        |      |           | T <sub>opr</sub>  | -30 to 85       | °C   |

| Storage temperatu            | re   |           | T <sub>stg</sub>  | -55 to 150      | °C   |

Note 1:  $T_a = 25^{\circ}C$ , without heatsink.

Note 2:  $T_a = 25^{\circ}C$ , with infinite heatsink (HZIP25).

Note 3:  $T_a = 25^{\circ}C$ , with soldered leads.

Note 4:  $T_a = 25^{\circ}C$ , when mounted on a board (4-layer board).

#### Operating Range ( $T_a = -30$ to $85^{\circ}$ C)

| Characteristi        | Characteristics |                   | Test Condition        | Min | Тур. | Max | Unit |

|----------------------|-----------------|-------------------|-----------------------|-----|------|-----|------|

| Dower oupply yeltere |                 | V <sub>DD</sub>   | —                     | 4.5 | 5.0  | 5.5 | V    |

| Power supply voltage |                 | VM <sub>A/B</sub> | $VM_{A/B} \ge V_{DD}$ | 4.5 | _    | 34  | V    |

| Output ourrent       | TB6560AHQ       |                   | _                     | _   | _    | 3   | Α    |

| Output current       | TB6560AFG       | IOUT              | _                     | _   | _    | 1.5 |      |

| Input voltage        |                 | V <sub>IN</sub>   |                       | 0   | _    | 5.5 | V    |

| Clock frequency      |                 | fCLK              |                       |     |      | 15  | kHz  |

| OSC frequency        |                 | f <sub>OSC</sub>  |                       |     | _    | 600 | kHz  |

### Electrical Characteristics (T\_a = 25°C, V\_{DD} = 5 V, VM = 24 V)

| Characteristics                            |            | Symbol                         | Test Condition                                                                                                                                        | Min  | Тур. | Max             | Unit |  |

|--------------------------------------------|------------|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|------|--|

| Input voltage High Low                     |            | V <sub>IN (H)</sub>            | M1, M2, CW/CCW, CLK,                                                                                                                                  | 2.0  |      | V <sub>DD</sub> | V    |  |

|                                            |            | V <sub>IN (L)</sub>            | RESET , ENABLE, DCY1, DCY2,                                                                                                                           | -0.2 | _    | 0.8             | v    |  |

| Input hysteresis voltage                   | e (Note)   | V <sub>INhys</sub>             | TQ1, TQ2                                                                                                                                              |      | 400  | _               | mV   |  |

| Input current                              |            | lin (H)                        | M1, M2, CW/CCW, CLK,<br>$\overline{\text{RESET}}$ , ENABLE, DCY1, DCY2,<br>TQ1, TQ2<br>$V_{\text{IN}} = 5.0 \text{ V}$<br>Internal pull-down resistor | 30   | 55   | 80              | μΑ   |  |

|                                            |            | I <sub>IN (L)</sub>            | V <sub>IN</sub> = 0 V                                                                                                                                 | _    | _    | 1               |      |  |

|                                            |            | I <sub>DD1</sub>               | Outputs: Open,<br>RESET : H, ENABLE: H<br>(2, 1-2 phase excitation)                                                                                   | _    | 3    | 5               |      |  |

| V <sub>DD</sub> supply current             |            | I <sub>DD2</sub>               | Outputs: Open,<br>RESET : H, ENABLE: H<br>(4W1-2, 2W1-2 phase excitation)                                                                             | _    | 3    | 5               | mA   |  |

|                                            |            |                                | RESET : L, ENABLE: L                                                                                                                                  | _    | 2    | 5               |      |  |

|                                            |            | I <sub>DD4</sub>               | RESET : H, ENABLE: L                                                                                                                                  | —    | 2    | 5               |      |  |

|                                            |            | I <sub>M1</sub>                | RESET : H/L, ENABLE: L                                                                                                                                |      | 0.5  | 1 mA            |      |  |

| VM supply current                          |            | I <sub>M2</sub>                | RESET : H/L, ENABLE: H                                                                                                                                |      | 0.7  |                 |      |  |

| Channel-to-channel voltage<br>differential |            | ΔV <sub>O</sub>                | B/A, C <sub>OSC</sub> = 330 μF                                                                                                                        | -5   | _    | 5               | %    |  |

|                                            |            | V <sub>NFHH</sub>              | TQ1 = H, TQ2 = H                                                                                                                                      | 10   | 20   | 30              |      |  |

| V <sub>NF</sub> voltage change ac          | cording to | V <sub>NFHL</sub>              | TQ1 = L, TQ2 = H                                                                                                                                      | 45   | 50   | 55              | %    |  |

| the torque settings                        |            | V <sub>NFLH</sub>              | TQ1 = H, TQ2 = L 70                                                                                                                                   |      | 75   | 80              | 70   |  |

|                                            |            | V <sub>NFLL</sub>              | TQ1 = L, TQ2 = L                                                                                                                                      | —    | —    | 100             |      |  |

| Minimum clock pulse width                  |            | t <sub>W</sub> (CLK)           | C <sub>OSC</sub> = 330 pF                                                                                                                             | 30   | —    | —               | μS   |  |

| M <sub>O</sub> output residual voltage     |            | V <sub>OL</sub> M <sub>O</sub> | I <sub>OL</sub> = 1 mA                                                                                                                                | —    | —    | 0.5             | V    |  |

| Protect output rest voltage (Note)         |            | V <sub>OL</sub> Protect        | I <sub>OL</sub> = 1 mA                                                                                                                                | —    | _    | 0.5             | V    |  |

| TSD threshold                              | (Note)     | TSD                            | —                                                                                                                                                     |      | 170  |                 | °C   |  |

| TSD hysteresis                             | (Note)     | TSDhys                         | —                                                                                                                                                     | —    | 20   | —               | °C   |  |

| Oscillating frequency                      |            | fosc                           | C <sub>OSC</sub> = 330 pF                                                                                                                             | 60   | 130  | 200             | kHz  |  |

Note: Not tested in production

## **TOSHIBA**

### Electrical Characteristics (T<sub>a</sub> = 25°C, V<sub>DD</sub> = 5 V, VM = 24 V)

|                                      |                                                     | Characte                      | ristics                  | Symbol                                | Te                       | est Condition            | Min | Тур. | Max | Unit |

|--------------------------------------|-----------------------------------------------------|-------------------------------|--------------------------|---------------------------------------|--------------------------|--------------------------|-----|------|-----|------|

|                                      |                                                     |                               | TROFCOALLO               | Ron U1H                               |                          | •                        |     | 0.3  | 0.4 |      |

| <u></u>                              | tout ON roo                                         | iatanaa                       | TB6560AHQ                | Ron L1H                               | 10UT = 1.5               | I <sub>OUT</sub> = 1.5 A |     | 0.3  | 0.4 |      |

| Ou                                   | tput ON-res                                         | Istance                       | TREEGONEC                | Ron U1F                               | 1                        | •                        |     | 0.35 | 0.5 | Ω    |

| TB6560AFG                            |                                                     | Ron L1F                       | – I <sub>OUT</sub> = 1.5 | A                                     |                          | 0.35                     | 0.5 |      |     |      |

|                                      |                                                     | 2W1-2-<br>phase<br>excitation | 1-2-<br>phase excitation |                                       | $\theta = 0$             |                          | _   | 100  | _   |      |

|                                      |                                                     | —                             | —                        |                                       | $\theta = 1/16$          |                          |     | 100  | —   |      |

|                                      |                                                     | 2W1-2-<br>phase<br>excitation | _                        |                                       | θ = 2/16                 |                          | 93  | 98   | 100 |      |

|                                      |                                                     |                               | —                        |                                       | $\theta=3/16$            |                          | 91  | 96   | 100 |      |

|                                      |                                                     | 2W1-2-<br>phase<br>excitation | _                        |                                       | $\theta = 4/16$          |                          | 87  | 92   | 97  |      |

| ÷                                    |                                                     |                               | —                        |                                       | $\theta = 5/16$          |                          | 83  | 88   | 93  |      |

| ent (Note                            | 2W1-2-<br>phase<br>excitation                       | _                             |                          | θ = 6/16                              |                          | 78                       | 83  | 88   |     |      |

| curr                                 | 4W1-2-                                              |                               |                          |                                       | $\theta = 7/16$          |                          | 72  | 77   | 82  |      |

| A-/B-phase chopping current (Note 1) | b phase<br>excitation 2W1-2-<br>phase<br>excitation | 1-2-<br>phase excitation      | Vector                   | θ = 8/16                              | TQ1 = L, TQ2 = L         | 66                       | 71  | 76   | %   |      |

| ase                                  |                                                     | _                             |                          |                                       | $\theta = 9/16$          |                          | 58  | 63   | 68  |      |

| A-/B-ph                              |                                                     | 2W1-2-<br>phase<br>excitation | _                        |                                       | θ = 10/16                |                          | 51  | 56   | 61  |      |

|                                      |                                                     |                               | —                        |                                       | $\theta = 11/16$         |                          | 42  | 47   | 52  |      |

|                                      |                                                     | 2W1-2-<br>phase<br>excitation | _                        |                                       | θ = 12/16                |                          | 33  | 38   | 43  |      |

|                                      |                                                     | —                             | —                        |                                       | $\theta = 13/16$         |                          | 24  | 29   | 34  |      |

|                                      |                                                     | 2W1-2-<br>phase<br>excitation | _                        |                                       | θ = 14/16                |                          | 15  | 20   | 25  |      |

|                                      |                                                     | —                             | —                        |                                       | $\theta = 15/16$         |                          | 5   | 10   | 15  |      |

|                                      | 2-phase ex                                          | citation                      |                          | ]                                     |                          |                          |     | 100  |     |      |

| Re                                   | ference volt                                        | age                           |                          | V <sub>NF</sub>                       | TQ1, TQ2<br>OSC = 100    | = L (100 %)<br>) kHz     | 450 | 500  | 550 | mV   |

| Ou                                   | tput transist                                       | or switchin                   | g characteristics        | tr                                    | $R_{1} = 10.0$           | $V_{NE} = 0.5 V$         |     | 1    | —   |      |

| (Note 2)                             |                                                     | t <sub>f</sub>                |                          | $R_L = 10 \ \Omega, V_{NF} = 0.5 \ V$ |                          | 1                        | —   |      |     |      |

|                                      |                                                     |                               |                          | t <sub>pLH</sub>                      | RESET to                 | o output                 |     | 1    | —   | μS   |

| De                                   | lay time                                            |                               | (Note 2)                 | t <sub>pLH</sub>                      | ENABLE to                | output                   |     | 3    |     |      |

|                                      |                                                     |                               |                          | t <sub>pHL</sub>                      |                          |                          | —   | 2    | —   |      |

| <u></u>                              | tput leakage                                        |                               | Upper side               | I <sub>LH</sub>                       | $\sqrt{M} = 40 \sqrt{2}$ |                          |     | —    | 1   |      |

| Οu                                   | ции неакаде                                         | current                       | Lower side               | ILL                                   | V IVI = 40 V             | VM = 40 V                |     | _    | 1   | μA   |

Note 1: Relative to the peak current at  $\theta = 0$ .

Note 2: Not tested in production.

#### **Functional Descriptions**

#### 1. Excitation Mode Settings

The excitation mode can be selected from the following four modes using the M1 and M2 inputs. (The 2-phase excitation mode is selected by default since both M1 and M2 have internal pull-down resistors.)

| Inp | outs | Mode         |

|-----|------|--------------|

| M2  | M1   | (Excitation) |

| L   | L    | 2-phase      |

| L   | Н    | 1-2-phase    |

| н   | L    | 4W1-2-phase  |

| Н   | Н    | 2W1-2-phase  |

#### 2. Function Table (Relationship Between Inputs and Output Modes)

When the ENABLE pin is Low, outputs are off. When the  $\overline{\text{RESET}}$  pin is Low, the outputs are put in the Initial mode as shown in the table below. In this mode, the states of the CLK and CW/CCW pins are don't-cares.

|          | Inp    | Output Mode |        |              |

|----------|--------|-------------|--------|--------------|

| CLK      | CW/CCW | RESET       | ENABLE | Output Mode  |

| _▲       | L      | Н           | Н      | CW           |

| <u> </u> | Н      | Н           | Н      | CCW          |

| х        | Х      | L           | Н      | Initial mode |

| Х        | Х      | Х           | L      | Z            |

X: Don't care

#### 3. Initial Mode

When  $\overline{\text{RESET}}$  is asserted, phase currents in each excitation mode are as follows. At this time, the M<sub>O</sub> pin goes Low (open-drain connection).

| Excitation Mode | A-Phase Current | B-Phase Current |

|-----------------|-----------------|-----------------|

| 2-phase         | 100 %           | -100 %          |

| 1-2-phase       | 100 %           | 0 %             |

| 2W1-2-phase     | 100 %           | 0 %             |

| 4W1-2-phase     | 100 %           | 0 %             |

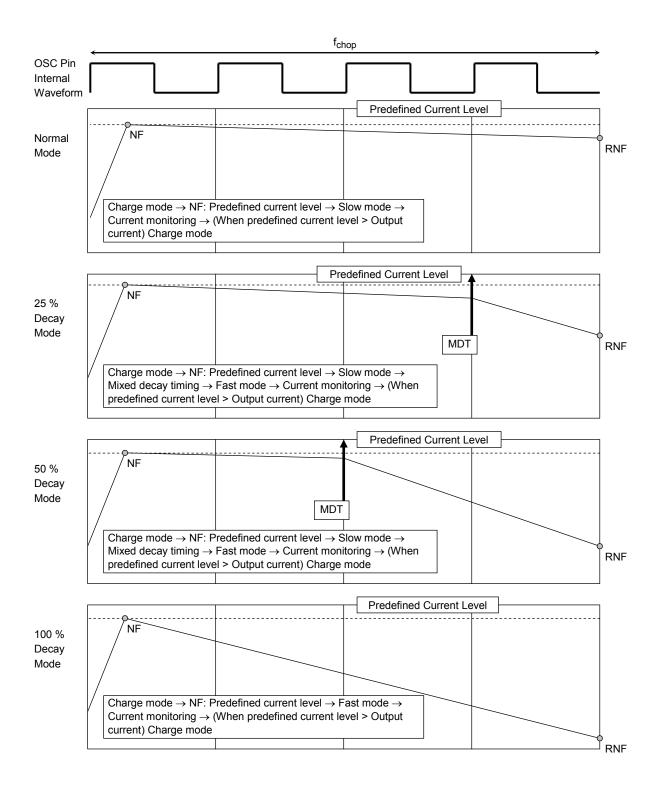

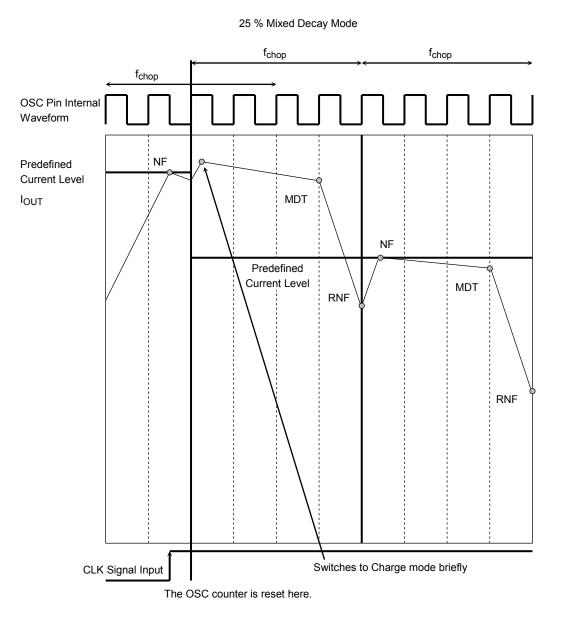

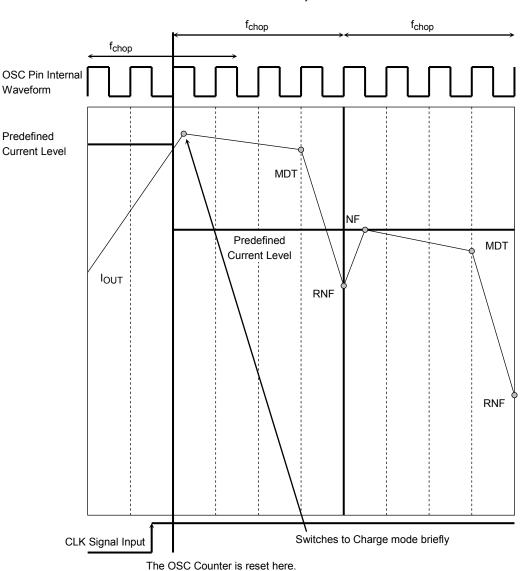

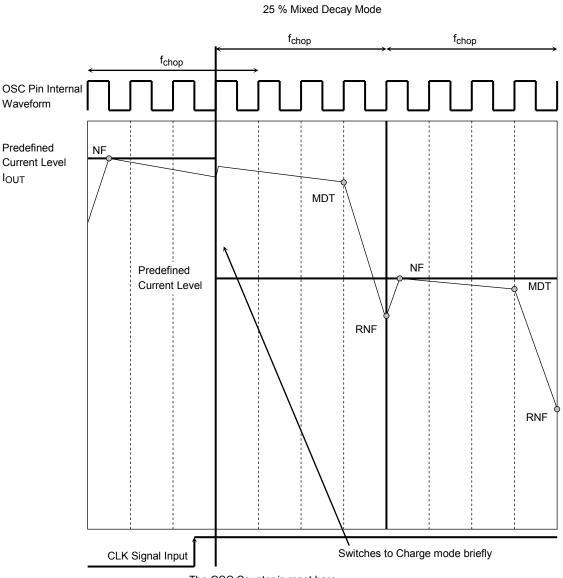

#### 4. Decay Mode Settings

It takes approximately four OSC cycles for discharging a current in PWM mode. The 25 % decay mode is created by inducing decay during the last cycle in Fast Decay mode; the 50 % Decay mode is created by inducing decay during the last two cycles in Fast Decay mode; and the 100 % Decay mode is created by inducing decay during all four cycles in Fast Decay mode.

Since the DCY1 and DCY2 pins have internal pull-down resistors, the Normal mode is selected when DCY1 and DCY2 are undriven.

| DCY2 | DCY1 | Current Decay Setting |

|------|------|-----------------------|

| L    | L    | Normal 0 %            |

| L    | Н    | 25 % Decay            |

| н    | L    | 50 % Decay            |

| Н    | Н    | 100 % Decay           |

#### 5. Torque Settings (Current Value)

The ratio of the current necessary for actual operations to the predefined current adjusted by an external resistor can be selected as follows. The Weak Excitation mode should be selected to set a torque extremely low like when the motor is at a fixed position.

Since the TQ2 and TQ1 pins have pull-down resistors, the 100 % torque setting is selected when TQ2 and TQ1 are undriven.

| TQ2 | TQ1 | Current Ratio             |

|-----|-----|---------------------------|

| L   | L   | 100 %                     |

| L   | Н   | 75 %                      |

| Н   | L   | 50 %                      |

| Н   | Н   | 20 %<br>(Weak excitation) |

#### 6. Calculation of the Predefined Output Current

To perform a constant current drive, the reference current should be adjusted by an external resistor. Charging stops when the  $N_{FA}$  ( $N_{FB}$ ) voltage reaches 0.5 V (when the torque setting is 100 %) so that a current does not exceed the predefined level.

$I_{OUT}(A) = 0.5 (V) / R_{NF}(\Omega)$

Example: To set the peak current to 1 A, the value of an external resistor should be 0.5  $\Omega.$

#### 7. Protect and M<sub>O</sub> Output Pins

These are open-drain outputs. An external pull-up resistor should be added to these pins when in use. If the TSD circuit is activated, Protect is driven Low. When the IC enters the Initial state,  $M_{\rm O}$  is driven Low.

| Pin State | Protect          | M <sub>O</sub>               | Open-drain connection   | ( |

|-----------|------------------|------------------------------|-------------------------|---|

| Low       | Thermal shutdown | Initial state                | - Open-drain connection |   |

| High-Z    | Normal operation | Other than the initial state |                         |   |

Rest voltage of output terminal Mo and output terminal Protect reach 0.5 V (max) when IO is 1 mA.

# 8. Adjusting the External Capacitor Value (C<sub>OSC</sub>) and Minimum Clock Pulse Width (tw(CLK))

A triangular-wave is generated internally by CR oscillation. The capacitor is externally connected to the OSC pin. The recommended capacitor value is between 100 pF and 1000 pF.

Approximate equation:  $fosc = 1/\{ Cosc \times 1.5 \times (10/Cosc + 1)/66\} \times 1000 \text{ kHz}$  (Since this is an approximation formula, the calculation result may not be exactly equal to the actual value.)

The approximate values are shown below. The minimum clock pulse width  $(t_{W(CLK)})$  corresponds to the external capacitor (Cosc ) as follows:

| Capacitor | Oscillating Frequency | Minimum Clock Pulse Width $t_{W({\mbox{CLK}})}$ (Note 1) |

|-----------|-----------------------|----------------------------------------------------------|

| 1000 pF   | 44 kHz                | 90 μs (Note 2)                                           |

| 330 pF    | 130 kHz               | 30 μs                                                    |

| 100 pF    | 400 kHz               | 10 μs (Note 2)                                           |

Note 1: When the frequency of an input clock signal is high, the C<sub>OSC</sub> value should be small so that the duty cycle of an input clock pulse does not become extremely high (should be around 50 % or lower).

Note 2: Not tested in production.

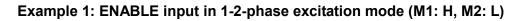

#### Relationship between the Enable and RESET and Output Signals

Setting the ENABLE signal Low disables only the output signals, while internal circuitry other than the output block continues to operate in accordance with the CLK input. Therefore, when the ENABLE signal goes High again, the output current generation is restarted as if phases proceeded with the CLK signal.

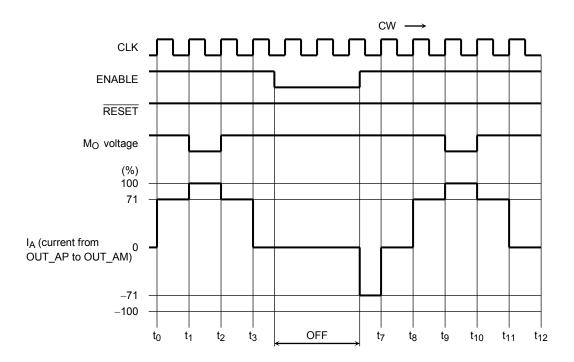

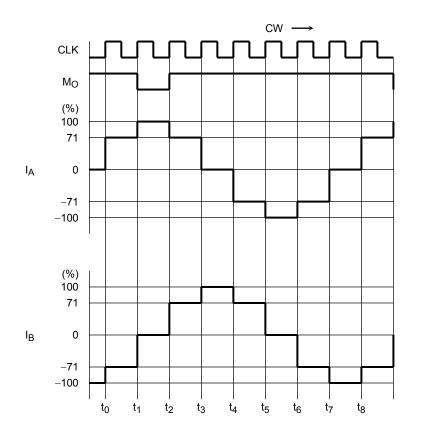

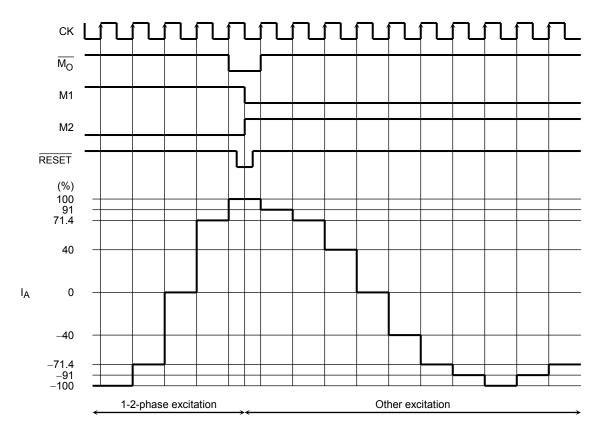

Example 2: RESET input in 1-2-phase excitation mode (M1: H, M2: L)

Setting the  $\overline{\text{RESET}}$  signal Low causes the outputs to be put in the Initial state and the MO output to be driven Low (Initial state: A-channel output current is at its peak (100 %)).

When the  $\overline{\text{RESET}}$  signal goes High again, the output current generation is restarted at the next rising edge of CLK with the state following the Initial state.

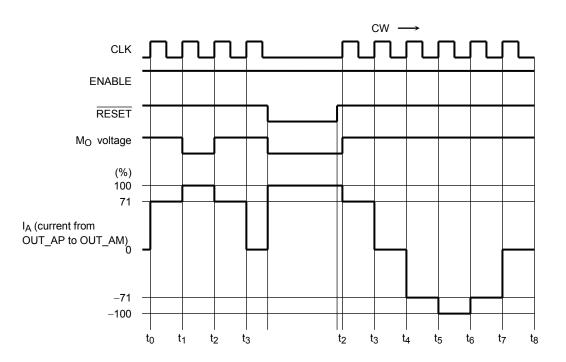

2-Phase Excitation (M1: L, M2: L, CW Mode)

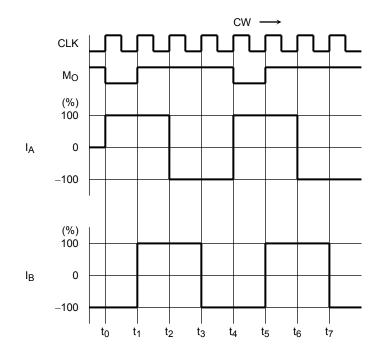

1-2-Phase Excitation (M1: H, M2: L, CW Mode)

TOSHIBA

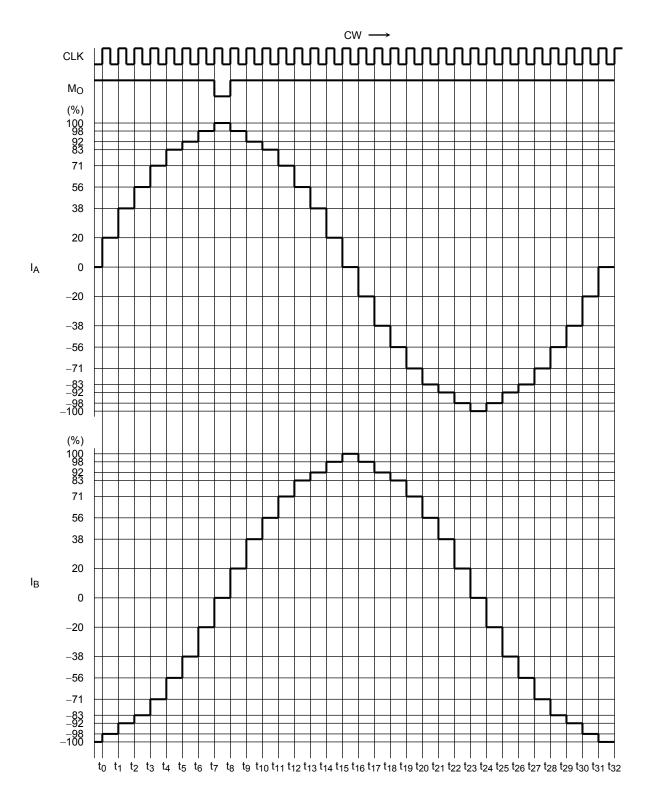

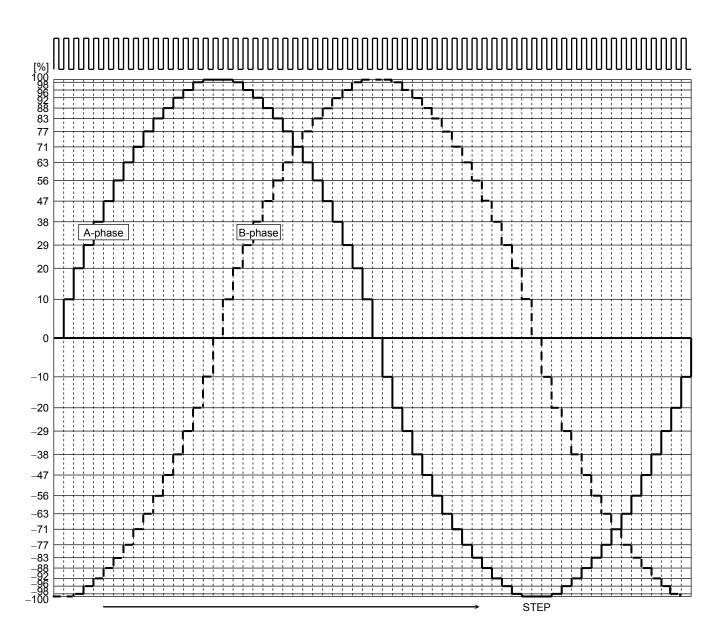

#### 2W1-2-Phase Excitation (M1: H, M2: H, CW Mode)

#### 4W1-2-Phase Excitation (M1: L, M2: H, CW Mode)

#### <Input Signal Example>

It is recommended that the state of the M1 and M2 pins be changed after setting the  $\overline{\text{RESET}}$  signal Low during the Initial state (MO = Low). Even when the MO signal is Low, changing the M1 and M2 signals without setting the  $\overline{\text{RESET}}$  signal Low may cause a discontinuity in the current waveform.

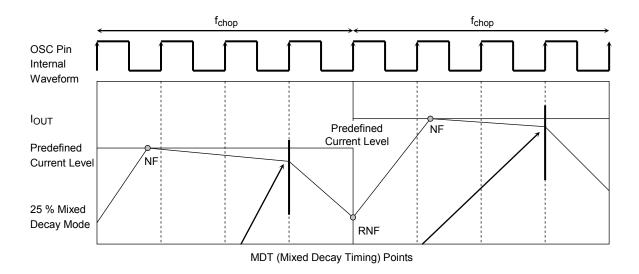

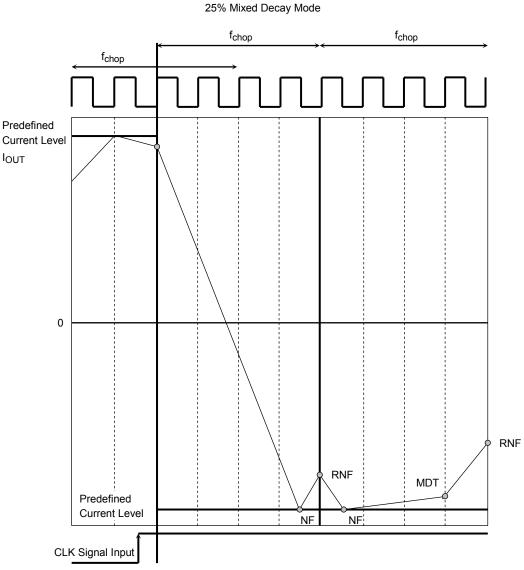

#### 9. Current Waveforms and Mixed Decay Mode Settings

The current decay rate of the Decay mode operation can be determined by the DCY1 and DCY2 inputs for constant-current control.

The "NF" refers to the point at which the output current reaches its predefined current level, and the "RNF" refers to the monitoring timing of the predefined current.

The smaller the MDT value, the smaller the current ripple amplitude. However, the current decay rate decreases.

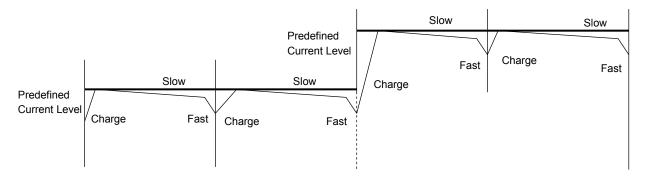

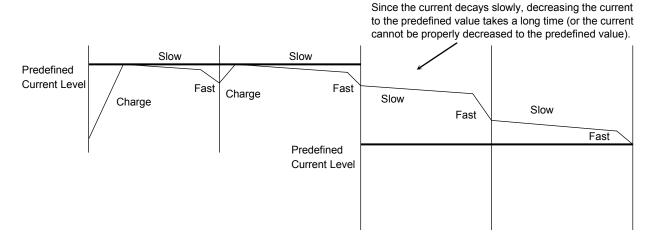

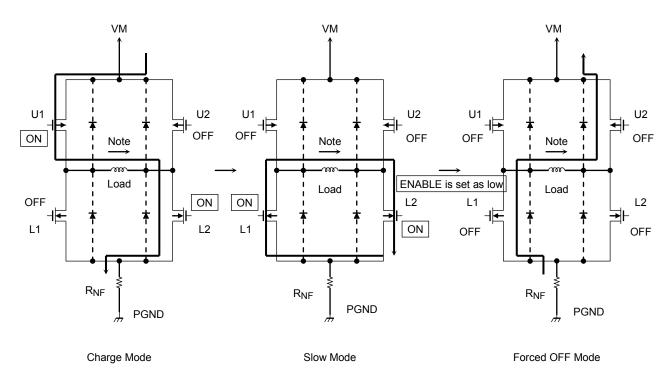

#### 10. Current Control Modes (Effects of Decay Modes)

• Increasing the current (sine wave)

• Decreasing the current with a high decay rate (The current decay rate in Mixed Decay mode is the ratio between the time in Fast-Decay mode (discharge time after MDT) and the remainder of the period.)

• Decreasing the current with a low decay rate (The current decay rate in Mixed Decay mode is the ratio between the time in Fast-Decay mode (discharge time after MDT) and the remainder of the period.)

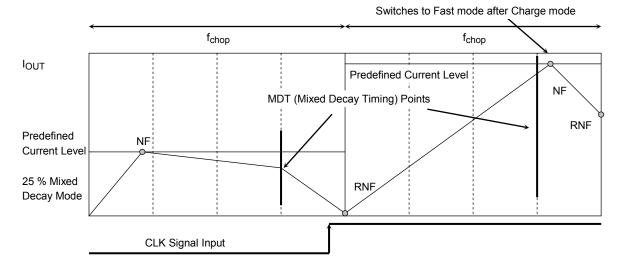

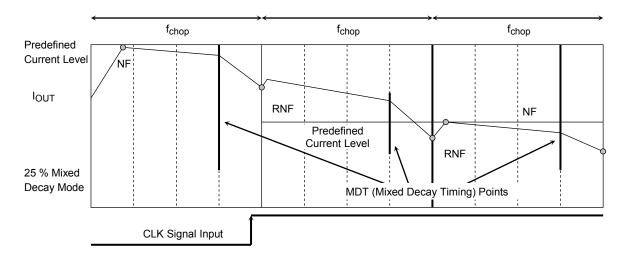

During Mixed Decay and Fast Decay modes, if the predefined current level is less than the output current at the RNF (current monitoring point), the Charge mode in the next chopping cycle will disappear (though the current control mode is briefly switched to Charge mode in actual operations for current sensing) and the current is controlled in Slow and Fast Decay modes (mode switching from Slow Decay mode to Fast Decay mode at the MDT point).

Note: The above figures are rough illustration of the output current. In actual current waveforms, transient response curves can be observed.

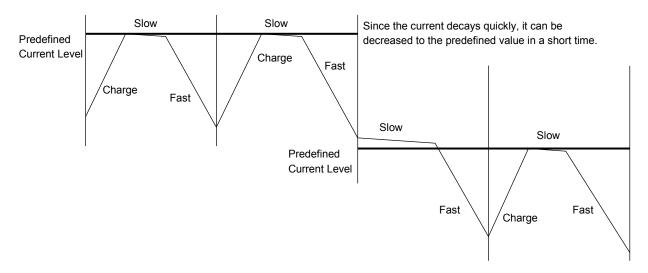

#### 11. Current Waveforms in Mixed Decay Mode

• When the NF points come after Mixed Decay Timing points

• When the output current value > predefined current level in Mixed Decay mode

\*: Even if the output current rises above the predefined current at the RNF point, the current control mode is briefly switched to Charge mode for current sensing.

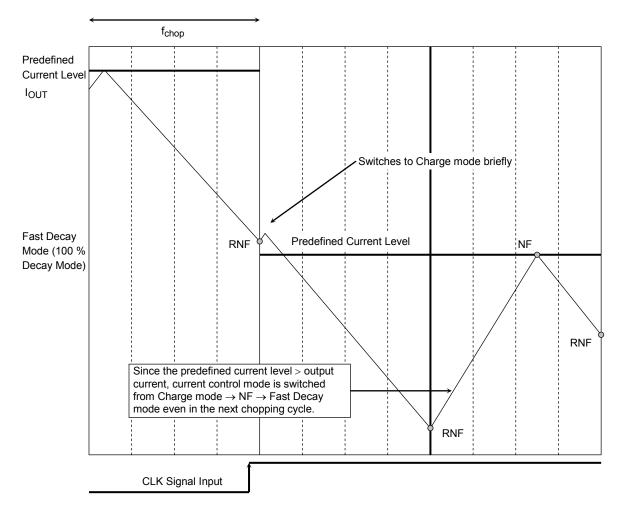

#### 12. Current Waveform in Fast Decay Mode

After the output current to the load reaches the current value specified by RNF, torque or other means, the output current to the load will be fed back to the power supply fully in Fast Decay mode.

#### 13. CLK and Internal OSC Signals and Output Current Waveform (when the CLK signal is asserted during Slow Decay mode)

When the CLK signal is asserted, the Chopping Counter (OSC Counter) is forced to reset at the next rising edge of the OSC signal.

As a result, the response to input data is faster compared to methods in which the counter is not reset. The delay time that is theoretically determined by the logic circuit is one OSC cycle =  $10 \mu s$  at a 100 kHz chopping rate.

After the OSC Counter is reset by the CLK signal input, the current control mode is invariably switched to Charge mode briefly for current sensing.

Note: Even in Fast Decay mode, the current control mode is invariably switched to Charge mode briefly for current sensing.

# 14. CLK and Internal OSC Signals and Output Current Waveform (when the CLK signal is asserted during Charge mode)

25 % Mixed Decay Mode

# 15. CLK and Internal OSC Signals and Output Current Waveform (when the CLK signal is asserted during Fast Decay mode)

The OSC Counter is reset here.

#### 16. Internal OSC Signal and Output Current Waveform when Predefined Current is Changed from Positive to Negative (when the CLK signal is input using 2-phase excitation)

## <u>TOSHIBA</u>

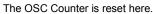

#### Current Discharge Path when ENABLE is Set as Low During Operation

When all the output transistors are forced off during Slow Decay mode, the coil energy is discharged in the following modes:

Note: Parasitic diodes are located on dotted lines. However, they are not normally used in normal Mixed Decay mode.

As shown in the figure above, output transistors have parasitic diodes.

Normally, when the energy of the coil is discharged, each transistor is turned on allowing the current to flow in the reverse direction to that in normal operation; as a result, the parasitic diodes are not used. However, when all the output transistors are forced off, the coil energy is discharged via the parasitic diodes.

#### **Output Transistor Operating Modes**

#### **Output Transistor Operating Modes**

| CLK        | U1  | U2  | L1  | L2  |

|------------|-----|-----|-----|-----|

| Charge     | ON  | OFF | OFF | ON  |

| Slow Decay | OFF | OFF | ON  | ON  |

| Fast Decay | OFF | ON  | ON  | OFF |

Note: This table shows an example of when the current flows as indicated by the arrows in the above figures. If the current flows in the opposite direction, refer to the following table:

| CLK        | U1  | U2  | L1  | L2  |

|------------|-----|-----|-----|-----|

| Charge     | OFF | ON  | ON  | OFF |

| Slow Decay | OFF | OFF | ON  | ON  |

| Fast Decay | ON  | OFF | OFF | ON  |

Upon transitions of above-mentioned modes, a dead time of about 300 ns is inserted between each mode respectively.