# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Voltage Supervisor with Manual Reset Input**

#### Features:

- Precision Voltage Monitor

- 2.63V, 2.93V, 3.08V, 4.38V and 4.63V Trip Points (Typical)

- Manual Reset Input

- Reset Time-Out Delay:

- Standard: 280 ms (Typical)

- Optional: 2.19 ms, and 35 ms (Typical)

- Power Consumption  $\leq$  15  $\mu A$  max

- No glitches on outputs during power-up

- Active Low Output Options:

- Push-Pull Output and Open-Drain Output

- Active High Output Option:

- Push-Pull Output

- Replacement for (Specification compatible with):

- TC1270, TC1271

- TCM811, TCM812

- Fully Static Design

- Low-Voltage Operation (1.0V)

- ESD Protection:

- ≥ 4 kV Human Body Model (HBM)

- ≥ 400V Machine Model (MM)

- Extended (E) Temperature Range: -40°C to +125°C

- Package Options:

- 4-Lead SOT-143

- 5-Lead SOT-23

- Pb-free Device

#### **Device Features**

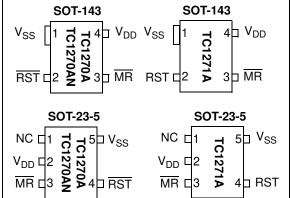

#### Package Types

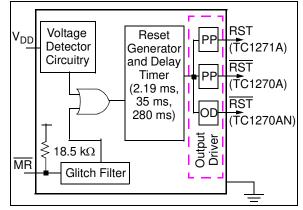

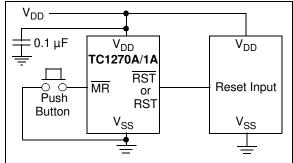

#### **Functional Block Diagram**

|                                                                                                                                                                                                                                                                                                                                                                                                     | Outpu      | t               | <b>V</b><br>(3)                          |                                                   |                      | Ire                  |                                      |                                      |                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------|------------------------------------------|---------------------------------------------------|----------------------|----------------------|--------------------------------------|--------------------------------------|----------------------------|

| Device                                                                                                                                                                                                                                                                                                                                                                                              | Туре       | Active<br>Level | Reset Delay<br>(ms) (Typ) <sup>(3)</sup> | Reset Trip<br>Point (V) <sup>(3)</sup>            | Voltage<br>Range (V) | Temperature<br>Range | Packages                             | Comment                              |                            |

| TC1270A                                                                                                                                                                                                                                                                                                                                                                                             | Push-Pull  | Low             |                                          | 4.00, 4.00                                        |                      | -40°C to<br>+125°C   |                                      | SOT-143 <sup>(2)</sup> ,<br>SOT-23-5 | Replaces TC1270 and TCM811 |

| TC1270AN                                                                                                                                                                                                                                                                                                                                                                                            | Open-Drain | Low             | 2.19, 35,<br>280 <sup>(1)</sup>          | 4.63, 4.38,<br>3.08, 2.93,<br>2.63 <sup>(4)</sup> | 1.0V to<br>5.5V      |                      | SOT-143 <sup>(2)</sup> ,<br>SOT-23-5 | New Option                           |                            |

| TC1271A                                                                                                                                                                                                                                                                                                                                                                                             | Push-Pull  | High            |                                          |                                                   |                      |                      | SOT-143 <sup>(2)</sup> ,<br>SOT-23-5 | Replaces TC1271 and TCM812           |                            |

| Note 1: The 280 ms Reset delay time-out is compatible with the TC1270, TC1271, TCM811 and TCM812 device         2: The SOT-143 package is compatible with the TC1270, TC1271, TCM811 and TCM812 devices.         3: Custom Reset trip points and Reset delays available, contact your local Microchip sales office.         4: The TC1270/1 and TCM811/12 1.75V trip point option is not supported. |            |                 |                                          |                                                   |                      |                      |                                      |                                      |                            |

NOTES:

#### 1.0 ELECTRICAL CHARACTERISTICS Absolute Maximum Ratings †

| Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> )+7.0V<br>Input Current, V <sub>DD</sub> 10 mA |

|---------------------------------------------------------------------------------------------------|

| Output Current, RESET, Reset 10 mA                                                                |

| Voltage on all inputs and outputs<br>w.r.t. V <sub>SS</sub>                                       |

| Storage Temperature Range                                                                         |

| Operating Temperature Range40°C to +125°C                                                         |

| Maximum Junction Temperature, T <sub>S</sub> 150°C                                                |

| ESD protection on all pins                                                                        |

| Human Body Model $\geq 4 \; kV$ Machine Model $\geq 400V$                                         |

**† Notice:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to a device. The absolute maximum values are merely stress ratings – functional operation of a device at those, or any other conditions above those indicated in the operational listing of these specifications, is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

| Elec | ctrical Characteristics: Unless otherwise noted, V <sub>DD</sub> = 5V for L/M versions, V <sub>DD</sub> = 3.3V for T/S versions, |

|------|----------------------------------------------------------------------------------------------------------------------------------|

| VDD  | $_{\rm D}$ = 3V for R version, T <sub>A</sub> = -40°C to +125°C. Typical values are at T <sub>A</sub> = +25°C.                   |

| Parameter                | Sym               | Min  | Typ <sup>(1)</sup> | Max  | Units | Test Conditions                                         |

|--------------------------|-------------------|------|--------------------|------|-------|---------------------------------------------------------|

| Operating Voltage Range  | V <sub>DD</sub>   | 1.0  | —                  | 5.5  | V     |                                                         |

| Supply Current           | I <sub>DD</sub>   | _    | 7                  | 15   | μA    | $V_{DD} > V_{TRIP}$ , for L/M/R/S/T,<br>$V_{DD} = 5.5V$ |

|                          |                   | _    | 4.75               | 10   | μΑ    | $V_{DD} > V_{TRIP}$ , for R/S/T, $V_{DD} = 3.6V$        |

|                          |                   |      | 10                 | 15   | μΑ    | $V_{DD} < V_{TRIP}$ , for L/M/R/S/T                     |

| Reset Trip Point         | V <sub>TRIP</sub> | 4.54 | 4.63               | 4.72 | V     | TC127xAL: $T_A = +25^{\circ}C$                          |

| Threshold <sup>(3)</sup> |                   | 4.50 | —                  | 4.75 | V     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$        |

|                          |                   | 4.30 | 4.38               | 4.46 | V     | TC127xAM: $T_A = +25^{\circ}C$                          |

|                          |                   | 4.25 | —                  | 4.50 | V     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$        |

|                          |                   | 3.03 | 3.08               | 3.14 | V     | TC127xAT: $T_A = +25^{\circ}C$                          |

|                          |                   | 3.00 | —                  | 3.15 | V     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$        |

|                          |                   | 2.88 | 2.93               | 2.98 | V     | TC127xAS: $T_A = +25^{\circ}C$                          |

|                          |                   | 2.85 | —                  | 3.00 | V     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$        |

|                          |                   | 2.72 | 2.77               | 2.82 | V     | TC127xA: <sup>(5)</sup> T <sub>A</sub> = +25°C          |

|                          |                   | 2.70 | —                  | 2.85 | V     | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$          |

|                          |                   | 2.58 | 2.63               | 2.68 | V     | TC127xAR: $T_{A} = +25^{\circ}C$                        |

|                          |                   | 2.55 | —                  | 2.70 | V     | $T_{A} = -40^{\circ}C \text{ to } +125^{\circ}C$        |

Note 1: Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated.

2: RST output for TC1270A and TC1270AN, RST output for TC1271A.

3: TC127XA refers to the TC1270A, TC1270AN or TC1271A device.

4: Hysteresis is within the V<sub>TRIP(MIN)</sub> to V<sub>TRIP(MAX)</sub> window.

5: Custom-ordered voltage trip point. Minimum order volume requirement.

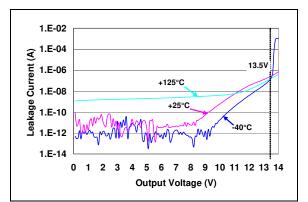

6: This specification allows this device to be used in PIC<sup>®</sup> microcontroller applications that require the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) feature (see device-specific programming specifications for voltage requirements). The total time that the RST pin can be above the maximum device operational voltage (5.5V) is 100s. Current into the RST pin should be limited to 2 mA. It is recommended that the device operational temperature be maintained between 0°C to +70°C (+25°C preferred). For additional information, refer to Figure 2-41.

#### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:** Unless otherwise noted,  $V_{DD} = 5V$  for L/M versions,  $V_{DD} = 3.3V$  for T/S versions,  $V_{DD} = 3V$  for R version,  $T_A = -40^{\circ}$ C to  $+125^{\circ}$ C. Typical values are at  $T_A = +25^{\circ}$ C.

| Par                                                   | ameter               | Sym               | Min                   | Typ <sup>(1)</sup> | Max           | Units  | Test Conditions                                                                                                                                                                |

|-------------------------------------------------------|----------------------|-------------------|-----------------------|--------------------|---------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset Thre                                            | shold Tempco         |                   | _                     | ±30                | _             | ppm/°C |                                                                                                                                                                                |

| Reset Trip<br>Hysteresis                              | Point                | V <sub>HYS</sub>  | _                     | 0.3                |               | %      | Percentage of V <sub>TRIP</sub> Voltage                                                                                                                                        |

| MR Input H                                            | ligh Threshold       | V <sub>IH</sub>   | 2.3                   | _                  | —             | V      | $V_{DD} > V_{TRIP(MAX)}$ , L/M only                                                                                                                                            |

|                                                       |                      |                   | 0.7 V <sub>DD</sub>   |                    | _             | V      | $V_{DD} > V_{TRIP(MAX)}$ , R/S/T only                                                                                                                                          |

| MR Input L                                            | ow Threshold         | V <sub>IL</sub>   | —                     |                    | 0.8           | V      | $V_{DD} > V_{TRIP(MAX)}$ , L/M only                                                                                                                                            |

|                                                       |                      |                   | —                     | _                  | $0.25 V_{DD}$ | V      | $V_{DD} > V_{TRIP(MAX)}$ , R/S/T only                                                                                                                                          |

| MR Pull-up                                            | Resistance           |                   | 10                    | 18.5               | 40            | kΩ     |                                                                                                                                                                                |

| Open-Drair<br>on Output                               | n High Voltage       | V <sub>ODH</sub>  | _                     |                    | 13.5          | V      | Open-Drain Output pin only.<br>$V_{DD} = 3.0V$ , Time voltage > 5.5<br>applied $\leq 100s$ . Current into pin<br>limited to 2 mA +25°C operation<br>recommended <sup>(6)</sup> |

| Reset<br>Output                                       | TC1270A/<br>TC1270AN | V <sub>OL</sub>   | _                     |                    | 0.3           | V      | R/S/T only,<br>I <sub>SINK</sub> = 1.2 mA, V <sub>DD</sub> = V <sub>TRIP(MIN)</sub>                                                                                            |

| Voltage<br>Low <sup>(2)</sup>                         | TC1271A              |                   | —                     |                    | 0.3           | V      | R/S/T only,<br>I <sub>SINK</sub> = 1.2 mA, V <sub>DD</sub> = V <sub>TRIP(MAX)</sub>                                                                                            |

|                                                       | TC1270A/<br>TC1270AN |                   | _                     | _                  | 0.4           | V      | L/M only,<br>$I_{SINK} = 3.2 \text{ mA}, V_{DD} = V_{TRIP(MIN)}$                                                                                                               |

|                                                       | TC1271A              |                   | —                     | _                  | 0.3           | V      | L/M only,<br>$I_{SINK} = 3.2 \text{ mA}, V_{DD} = V_{TRIP(MAX)}$                                                                                                               |

|                                                       | TC1270A/<br>TC1270AN |                   | —                     |                    | 0.3           | V      | L/M only,<br>$I_{SINK} = 50 \ \mu A, V_{DD} > 1.0V$                                                                                                                            |

| Reset<br>Output                                       | TC1270A              | V <sub>OH</sub>   | 0.8 V <sub>DD</sub>   | _                  | —             | V      | R/S/T only,<br>I <sub>SOURCE</sub> = 500 $\mu$ A, V <sub>DD</sub> = V <sub>TRIP(MAX)</sub>                                                                                     |

| Voltage<br>High <sup>(2)</sup>                        | TC1270A              |                   | V <sub>DD</sub> - 1.5 |                    |               | V      | L/M only,<br>I <sub>SOURCE</sub> = 800 $\mu$ A, V <sub>DD</sub> = V <sub>TRIP(MAX)</sub>                                                                                       |

| TC1271A                                               |                      |                   | 0.8 V <sub>DD</sub>   | _                  | _             | V      | $I_{SOURCE} = 500 \ \mu A, \ V_{DD} \le V_{TRIP(MIN)}$                                                                                                                         |

| Input Leaka                                           | age Current          | ١ <sub>IL</sub>   | —                     | _                  | ±1            | μA     | $V_{PIN} = V_{DD}$                                                                                                                                                             |

| Open-Drair<br>Leakage                                 | RST Output           | I <sub>OLOD</sub> | —                     | _                  | 1             | μA     | Open-Drain configuration only.                                                                                                                                                 |

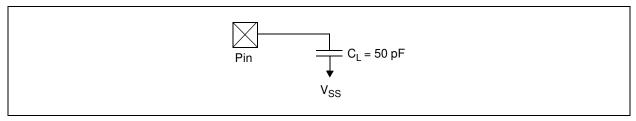

| Capacitive Loading<br>Specification on Output<br>Pins |                      | C <sub>IO</sub>   | _                     | _                  | 50            | pF     |                                                                                                                                                                                |

**Note 1:** Data in the Typical ("Typ") column is at 5V, +25°C, unless otherwise stated.

2: RST output for TC1270A and TC1270AN, RST output for TC1271A.

3: TC127XA refers to the TC1270A, TC1270AN or TC1271A device.

4: Hysteresis is within the V<sub>TRIP(MIN)</sub> to V<sub>TRIP(MAX)</sub> window.

5: Custom-ordered voltage trip point. Minimum order volume requirement.

6: This specification allows this device to be used in PIC<sup>®</sup> microcontroller applications that require the In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) feature (see device-specific programming specifications for voltage requirements). The total time that the RST pin can be above the maximum device operational voltage (5.5V) is 100s. Current into the RST pin should be limited to 2 mA. It is recommended that the device operational temperature be maintained between 0°C to +70°C (+25°C preferred). For additional information, refer to Figure 2-41.

#### 1.1 AC CHARACTERISTICS

#### 1.1.1 TIMING PARAMETER SYMBOLOGY

The timing parameter symbols have been created following one of the following formats:

| 1. TppS2p | ρS                                   | 2. TppS |                |

|-----------|--------------------------------------|---------|----------------|

| Т         |                                      |         |                |

| F         | Frequency                            | Т       | Time           |

| E         | Error                                |         |                |

| Lowerca   | ase letters (pp) and their meanings: |         |                |

| рр        |                                      |         |                |

| io        | Input or Output pin                  | osc     | Oscillator     |

| rx        | Receive                              | tx      | Transmit       |

| bitclk    | RX/TX BITCLK                         | RST     | Reset          |

| drt       | Device Reset Timer                   |         |                |

| Upperca   | ase letters and their meanings:      |         |                |

| S         |                                      |         |                |

| F         | Fall                                 | Р       | Period         |

| н         | High                                 | R       | Rise           |

| 1         | Invalid (High-impedance)             | V       | Valid          |

| L         | Low                                  | Z       | High-impedance |

FIGURE 1-1: Test Load Conditions.

#### TIMING DIAGRAMS AND SPECIFICATIONS

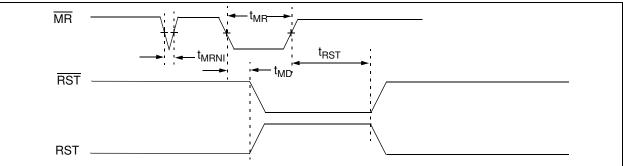

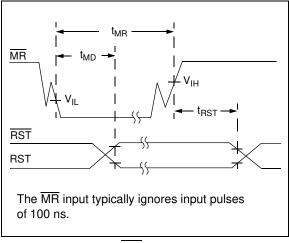

#### MR Pin and Reset Pin Waveform

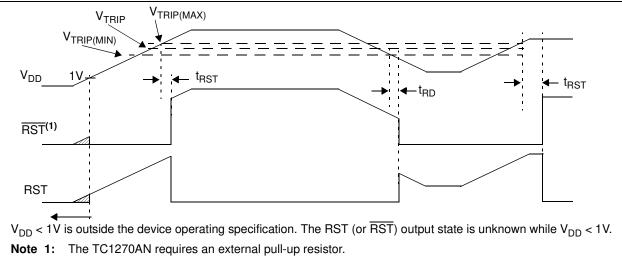

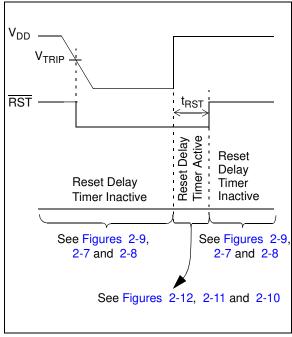

#### Device Voltage and Reset Pin (Active Low) Waveform

#### **Reset and Device Reset Timer Requirements**

| <b>Electrical Characteristics:</b> Unless otherwise noted, $V_{DD} = 5V$ for L/M versions, $V_{DD} = 3.3V$ for T/S versions, $V_{DD} = 3V$ for R version, $T_A = -40^{\circ}$ C to $+125^{\circ}$ C. Typical values are at $T_A = +25^{\circ}$ C. |                                      |                  |      |      |      |                                                        |                          |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|------------------|------|------|------|--------------------------------------------------------|--------------------------|--|--|--|--|--|

| Parameter Sym Min Typ <sup>(1)</sup> Max Units Test Conditions                                                                                                                                                                                    |                                      |                  |      |      |      |                                                        |                          |  |  |  |  |  |

| V <sub>DD</sub> to Reset D                                                                                                                                                                                                                        | t <sub>RD</sub>                      | _                | 50   | _    | μs   | $V_{DD} = V_{TRIP(MAX)}$ to<br>$V_{TRIP(MIN)}$ –125 mV |                          |  |  |  |  |  |

| Reset Active                                                                                                                                                                                                                                      | TC127XAx <b>B</b> Vyy <sup>(3)</sup> | t <sub>RST</sub> | 1.09 | 2.19 | 4.38 | ms                                                     | $V_{DD} = V_{TRIP(MAX)}$ |  |  |  |  |  |

| Time Out<br>Period                                                                                                                                                                                                                                | TC127XAx <b>A</b> Vyy <sup>(3)</sup> |                  | 17.5 | 35   | 70   | ms                                                     | $V_{DD} = V_{TRIP(MAX)}$ |  |  |  |  |  |

| i enou                                                                                                                                                                                                                                            | TC127XAxVyy <sup>(3)</sup>           |                  | 140  | 280  | 560  | ms                                                     | $V_{DD} = V_{TRIP(MAX)}$ |  |  |  |  |  |

| MR Minimum I                                                                                                                                                                                                                                      | Pulse Width                          | t <sub>MR</sub>  | 10   | —    | _    | μs                                                     |                          |  |  |  |  |  |

| MR Noise Imm                                                                                                                                                                                                                                      | t <sub>MRNI</sub>                    | _                | 0.1  | _    | μs   |                                                        |                          |  |  |  |  |  |

| MR to Reset P                                                                                                                                                                                                                                     | t <sub>MD</sub>                      |                  | 0.2  |      | μs   |                                                        |                          |  |  |  |  |  |

Note 1: Unless otherwise stated, data in the Typical ("Typ") column is at 5V, +25°C.

2: RST output for TC1270A, RST output for TC1271A.

**3:** TC127XA refers to the TC1270A, TC1270AN or TC1271A device. "x" indicates the selected voltage trip point, while "yy" indicates the package code.

#### **TEMPERATURE CHARACTERISTICS**

| Electrical Specifications: Unless otherwise indicated, $V_{DD} = +1.0V$ to +5.5V, $V_{SS} = GND$ . |                |     |     |      |       |            |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------|----------------|-----|-----|------|-------|------------|--|--|--|--|--|

| Parameters                                                                                         | Sym            | Min | Тур | Max  | Units | Conditions |  |  |  |  |  |

| Temperature Ranges                                                                                 |                |     |     |      |       |            |  |  |  |  |  |

| Specified Temperature Range                                                                        | T <sub>A</sub> | -40 | —   | +125 | °C    |            |  |  |  |  |  |

| Operating Temperature Range                                                                        | T <sub>A</sub> | -40 | —   | +125 | °C    |            |  |  |  |  |  |

| Storage Temperature Range                                                                          | T <sub>A</sub> | -65 | —   | +150 | °C    |            |  |  |  |  |  |

| Thermal Package Resistances                                                                        |                |     |     |      |       |            |  |  |  |  |  |

| Thermal Resistance, 5L-SOT-23 θ <sub>JA</sub> — 256 — °C/W                                         |                |     |     |      |       |            |  |  |  |  |  |

| Thermal Resistance, 4L-SOT-143 θ <sub>JA</sub> — 426 — °C/W                                        |                |     |     |      |       |            |  |  |  |  |  |

NOTES:

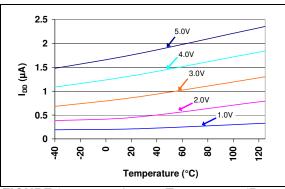

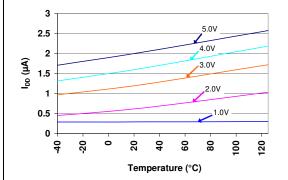

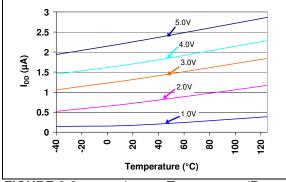

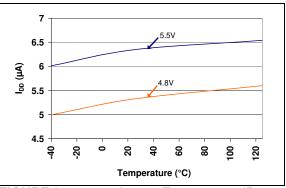

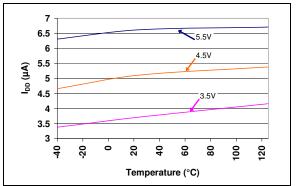

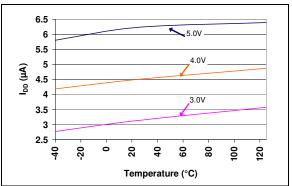

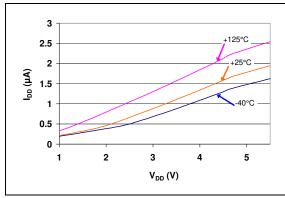

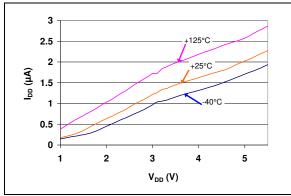

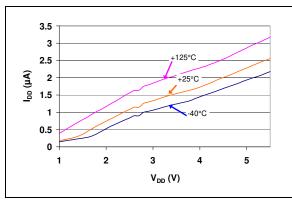

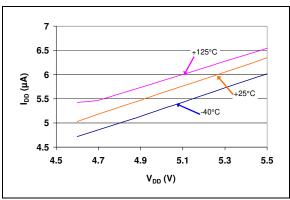

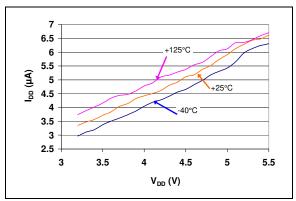

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables that follow this note are the result of a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

**FIGURE 2-1:** I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Inactive) (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

FIGURE 2-2: I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Inactive) (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-3:** I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Inactive) (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

**FIGURE 2-4:** I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Active) (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

**FIGURE 2-5:** I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Active) (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

FIGURE 2-6: I<sub>DD</sub> vs. Temperature (Reset Power-up Timer Active) (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

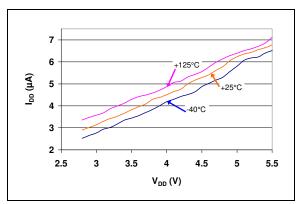

**FIGURE 2-7:** I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Inactive) (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

**FIGURE 2-8:** I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Inactive) (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-9:** I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Inactive) (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

**FIGURE 2-10:** I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Active) (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

FIGURE 2-11: I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Active) (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-12:** I<sub>DD</sub> vs. V<sub>DD</sub> (Reset Power-up Timer Active) (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

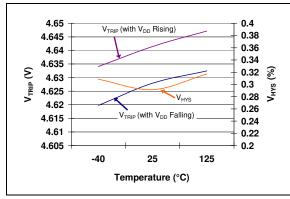

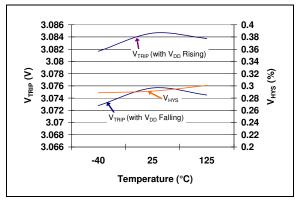

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

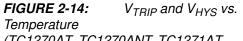

(TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

FIGURE 2-15:

V<sub>TRIP</sub> and V<sub>HYST</sub> vs.

Temperature

(TC1270AR, TC1270ANR, TC1271AR

- 2.55V min./2.63V typ./2.70V max.).

(TC1270AR, TC1270ANR, TC1271AR)

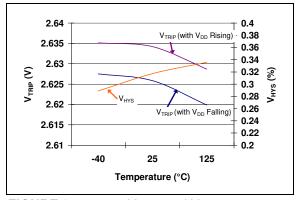

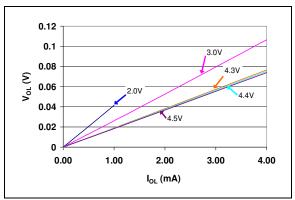

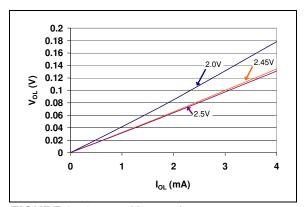

FIGURE 2-16: V<sub>OL</sub> vs. I<sub>OL</sub> (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

FIGURE 2-17: V<sub>OL</sub> vs. I<sub>OL</sub> (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

FIGURE 2-18: V<sub>OL</sub> vs. I<sub>OL</sub> (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

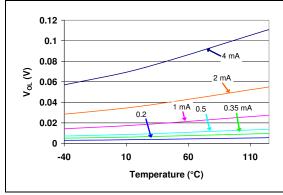

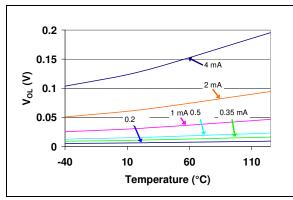

**FIGURE 2-19:** V<sub>OL</sub> vs. Temperature (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.). @ V<sub>DD</sub> = 4.5V).

**FIGURE 2-20:** V<sub>OL</sub> vs. Temperature (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.). @ V<sub>DD</sub> = 2.7V).

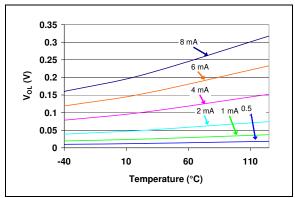

FIGURE 2-21: V<sub>OL</sub> vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.). @ V<sub>DD</sub> = 1.8V).

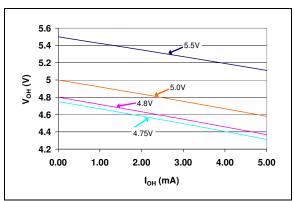

*FIGURE 2-22:* V<sub>OH</sub> vs. I<sub>OL</sub> (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.) @ +25°C).

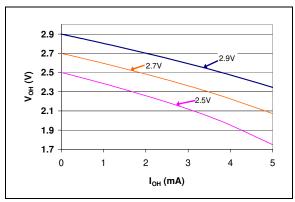

*FIGURE 2-23:* V<sub>OH</sub> vs. I<sub>OH</sub> (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.) @ +25℃).

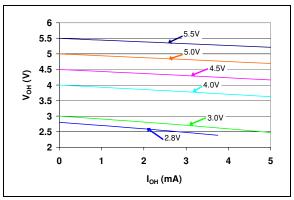

FIGURE 2-24: V<sub>OH</sub> vs. I<sub>OH</sub> (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.) @ +25°C).

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

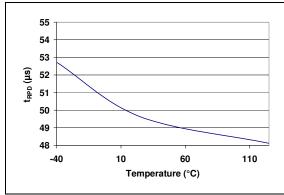

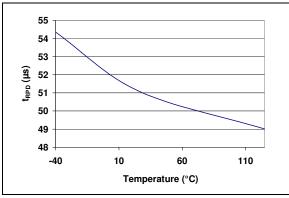

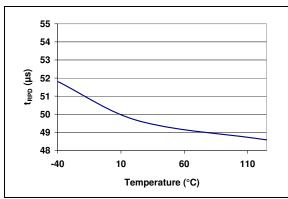

**FIGURE 2-25:** V<sub>DD</sub> Falling to Reset Propagation Delay (t<sub>RPD</sub>) vs. Temperature (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

**FIGURE 2-26:** V<sub>DD</sub> Falling to Reset Propagation Delay (t<sub>RPD</sub>) vs. Temperature (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-27:** V<sub>DD</sub> Falling to Reset Propagation Delay (t<sub>RPD</sub>) vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

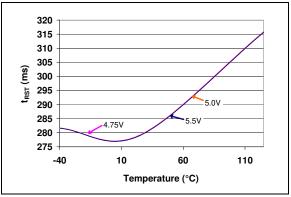

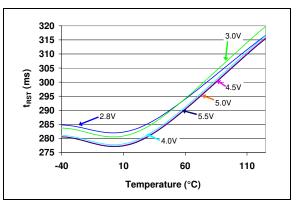

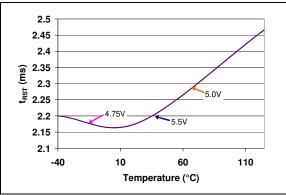

**FIGURE 2-28:** Reset Time-Out Period (t<sub>RST</sub>) vs. Temperature (TC1270AL, TC1270ANL, TC1271AL

- 4.50V min./4.63V typ./4.75V max.).

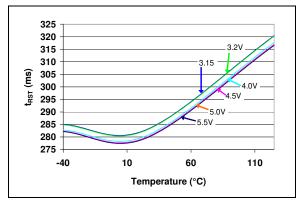

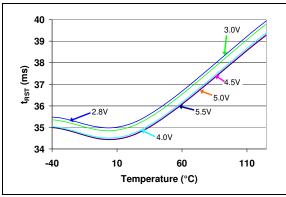

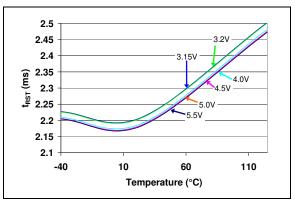

**FIGURE 2-29:** Reset Time-Out Period (t<sub>RST</sub>) vs. Temperature

(TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

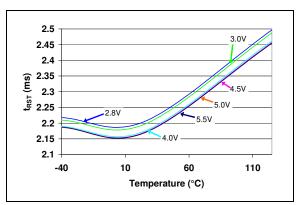

**FIGURE 2-30:** Reset Time-Out Period (t<sub>RST</sub>) vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

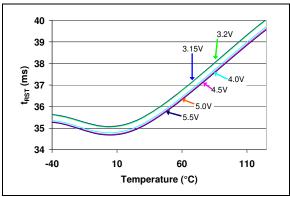

**FIGURE 2-31:** Reset Time-Out Period (t<sub>RST</sub>) (C time out option) vs. Temperature (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

**FIGURE 2-32:** Reset Time-Out Period (t<sub>RST</sub>) (C time out option) vs. Temperature (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-33:** Reset Time-Out Period (t<sub>RST</sub>) (C time out option) vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

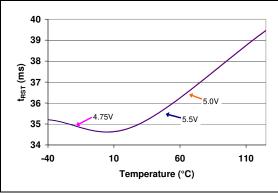

**FIGURE 2-34:** Reset Time-Out Period (t<sub>RST</sub>) (B time out option) vs. Temperature (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

**FIGURE 2-35:** Reset Time-Out Period (t<sub>RST</sub>) (B time out option) vs. Temperature (TC1270AT, TC1270ANT, TC1271AT - 3.00V min./3.08V typ./3.15V max.).

**FIGURE 2-36:** Reset Time-Out Period (t<sub>RST</sub>) (B time out option) vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

Note: Unless otherwise indicated, all limits are specified for  $V_{DD} = 1V$  to 5.5V,  $T_A = -40^{\circ}C$  to  $+125^{\circ}C$ .

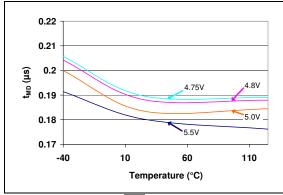

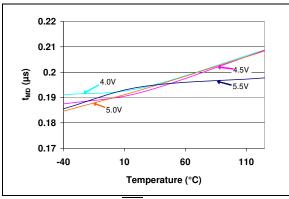

**FIGURE 2-37:** MR Low to Reset Propagation Delay (t<sub>MD</sub>) vs. Temperature (TC1270AL, TC1270ANL, TC1271AL - 4.50V min./4.63V typ./4.75V max.).

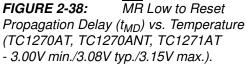

**FIGURE 2-39:** MR Low to Reset Propagation Delay (t<sub>MD</sub>) vs. Temperature (TC1270AR, TC1270ANR, TC1271AR - 2.55V min./2.63V typ./2.70V max.).

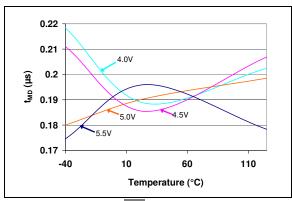

**FIGURE 2-40:**  $V_{DD}$  Transient Duration vs. Reset Threshold Overdrive  $(V_{TBIP} (minimum) - V_{DD}).$

NOTES:

#### 3.0 PIN DESCRIPTIONS

Descriptions of the pins are listed in Table 3-1.

#### TABLE 3-1: PINOUT DESCRIPTION

|          |                           | Pin Nu                                  | mber      |                                        |           |           |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|---------------------------|-----------------------------------------|-----------|----------------------------------------|-----------|-----------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Push    | 270A<br>n-Pull,<br>e-low) | TC1270AN<br>(Open-Drain,<br>active-low) |           | TC1271A<br>(Push-Pull,<br>active-high) |           | Sym       |      | Pin                | Standard Function                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SOT-23-5 | SOT-143-4                 | SOT-23-5                                | SOT-143-4 | SOT-23-5                               | SOT-143-4 | <b>-,</b> | Туре | Buffer /<br>Driver |                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 5        | 1                         |                                         | 1         | 5                                      | 1         | $V_{SS}$  | —    | Power              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 4        | 2                         | _                                       | _         |                                        |           | RST       | 0    | Push-<br>Pull      | Reset output (Push-Pull), active-low<br>$H = V_{DD} > V_{TRIP}$ , Reset pin is inactive<br>(after Reset Delay Timer completes)<br>$L = V_{DD} < V_{TRIP}$ , Reset pin is active<br>Goes active (Low) if one of these conditions                                                                                                                                                                                                                                           |

|          |                           |                                         |           |                                        |           |           |      |                    | <ol> <li>If V<sub>DD</sub> falls below the selected Reset voltage threshold.</li> <li>If the MR pin is forced low.</li> <li>During power-up.</li> </ol>                                                                                                                                                                                                                                                                                                                   |

| _        |                           | 4                                       | 2         | _                                      | _         | RST       | 0    | Open-<br>Drain     | <ul> <li>Reset output (Open-Drain), active-low</li> <li>Float = V<sub>DD</sub> &gt; V<sub>TRIP</sub>, Reset pin is inactive<br/>(after Reset Delay Timer completes)</li> <li>L = V<sub>DD</sub> &lt; V<sub>TRIP</sub>, Reset pin is active</li> <li>Goes active (Low) if one of these conditions occurs:</li> <li>1. If V<sub>DD</sub> falls below the selected Reset voltage threshold.</li> <li>2. If the MR pin is forced low.</li> <li>3. During power-up.</li> </ul> |

| —        |                           | _                                       | _         | 4                                      | 2         | RST       | 0    | Push-<br>Pull      | <ul> <li>Reset output (Push-Pull), active-high<br/>H = V<sub>DD</sub> &lt; V<sub>TRIP</sub>. Reset pin is active<br/>L = V<sub>DD</sub> &gt; V<sub>TRIP</sub>. Reset pin is inactive<br/>(after Reset Delay Timer completes)</li> <li>Goes active (High) if one of these conditions<br/>occurs:</li> <li>1. If V<sub>DD</sub> falls below the selected Reset<br/>voltage threshold.</li> <li>2. If the MR pin is forced low.</li> <li>3. During power-up.</li> </ul>      |

**Note 1:** The  $\overline{\text{MR}}$  pin has an internal weak pull-up (18.5 k $\Omega$  typical).

|          |                           |                              |           |          |                            | (CONTINUED) |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|----------|---------------------------|------------------------------|-----------|----------|----------------------------|-------------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|          |                           | Pin Nu                       | mber      |          |                            |             |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| (Push    | 270A<br>I-Pull,<br>e-low) | TC127(<br>(Open-D<br>active- | rain,     | (Pusł    | 271A<br>℩-Pull,<br>բ-high) | Pin<br>Sym  |      | Pin                | Standard Eurotion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| SOT-23-5 | SOT-143-4                 | SOT-23-5                     | SOT-143-4 | SOT-23-5 | SOT-143-4                  |             | Туре | Buffer /<br>Driver | Standard Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 3        | 3                         | 3                            | 3         | 3        | 3                          | MR          | I    | ST <sup>(1)</sup>  | Manual Reset Input Pin<br>This input allows a push button switch to be<br>directly connected to a TC1270A/70AN/71A<br>device's MR pin, which can be used to force a<br>system Reset. The input filter ignores noise<br>pulses that occur on the MR pin.<br>H = Switch is open (internal pull-up resistor<br>pulls signal high). State of the RST/RST<br>pin is determined by other system condi-<br>tions.<br>L = Switch is depressed (shorted to ground).<br>This forces the RST/RST pin Active. |  |

| 2        | 4                         | 2                            | 4         | 2        | 4                          | $V_{DD}$    | —    | Power              | Supply Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 1        |                           | 1                            |           | 1        |                            | NC          | _    | _                  | No Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|          |                           |                              |           |          |                            |             |      |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

#### TABLE 3-1: PINOUT DESCRIPTION (CONTINUED)

**Note 1:** The  $\overline{\text{MR}}$  pin has an internal weak pull-up (18.5 k $\Omega$  typical).

#### 3.1 Ground Terminal (V<sub>SS</sub>)

$V_{SS}$  provides the negative reference for the analog input voltage. Typically, the circuit ground is used.

#### 3.2 Supply Voltage (V<sub>DD</sub>)

V<sub>DD</sub> can be used for power supply monitoring or a voltage level that requires monitoring.

#### 3.3 Reset Output (RST and RST)

There are three types of Reset output pins. These are:

- 1. Push-Pull active-low Reset

- 2. Push-Pull active-high Reset

- 3. Open-Drain active-low Reset, external pull-up resistor required.

#### 3.3.1 ACTIVE-LOW (RST) – PUSH-PULL

The  $\overline{\text{RST}}$  push-pull output remains low while V<sub>DD</sub> is below the Reset voltage threshold (V<sub>TRIP</sub>). The time that the  $\overline{\text{RST}}$  pin is held low after the device voltage (V<sub>DD</sub>) returns to a high level (> V<sub>TRIP</sub>) is typically 280 ms. After the Reset Delay Timer expires, the RST pin will be driven to the high state.

#### 3.3.2 ACTIVE-HIGH (RST) – PUSH-PULL

The RST push-pull output remains high while V<sub>DD</sub> is below the Reset voltage threshold (V<sub>TRIP</sub>). The time that the RST pin is held high after the device voltage (V<sub>DD</sub>) returns to a high level (> V<sub>TRIP</sub>) is typically 280 ms. After the Reset Delay Timer expires, the RST pin will be driven to the low state.

#### 3.3.3 ACTIVE-LOW (RST) – OPEN-DRAIN

The  $\overline{\text{RST}}$  open-drain output remains low while V<sub>DD</sub> is below the Reset voltage threshold (V<sub>TRIP</sub>). The time that the  $\overline{\text{RST}}$  pin is held low after the device voltage (V<sub>DD</sub>) returns to a high level (> V<sub>TRIP</sub>) depends on the Reset time-out selected. After the Reset Delay Timer expires, the  $\overline{\text{RST}}$  pin will float.

#### 3.4 Manual Reset Input (MR)

The Manual Reset ( $\overline{\text{MR}}$ ) input pin allows a push button switch to easily be connected to the system. When the push button is depressed, it forces a system Reset. This pin has circuitry that filters noise that may be present on the  $\overline{\text{MR}}$  signal.

The  $\overline{\text{MR}}$  pin is active-low and has an internal pull-up resistor.

#### 4.0 DEVICE OPERATION

#### 4.1 General Description

For many of today's microcontroller applications, care must be taken to prevent low-power conditions that can cause many different system problems. The most common causes are brown-out conditions, where the system supply drops below the operating level momentarily. The second most common cause is when a slowly decaying power supply causes the microcontroller to begin executing instructions without sufficient voltage to sustain volatile memory (RAM), thus producing indeterminate results.

The TC127XA family (TC1270A, TC1270AN and TC1271A) are cost-effective voltage supervisor devices designed to keep a microcontroller in Reset until the system voltage has reached and stabilized at the proper level for reliable system operation. These devices also operate as protection from brown-out conditions when the system supply voltage drops below a safe operating level.

A Manual Reset input ( $\overline{\text{MR}}$  pin) is provided. This allows a push button switch to be directly connected to the TC127XA device, and is suitable for use as a push button Reset. This allows the system to easily be reset from the external control of the push button switch. No external components are required.

The Reset pin (RST or  $\overline{RST}$ ) will be forced active, if any of the following occur:

- During device power-up

- · V<sub>DD</sub> goes below the device threshold voltage

- The Manual Reset input (MR) goes low

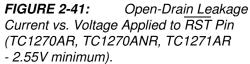

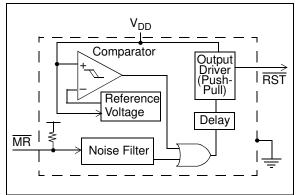

Figure 4-1 shows a high level block diagram of the devices. The device can be described with three functional blocks. These are:

- · Voltage detect circuit

- Manual Reset with glitch filter circuit

- · Reset generator circuit

The Reset generator circuit controls the Reset delay time of the Reset output signal.

There are three Reset Delay Timer options. Depending on the option, the Reset signal ( $\overline{RST}/RST$  pin) will be held active for a minimum of 1.09 ms, 17.5 ms, or 140 ms.

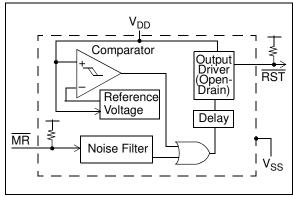

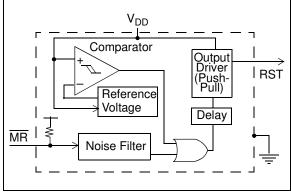

The TC1271A has an active-high RST output while the TC1270A and TC1270AN have an active-low  $\overline{\text{RST}}$  output.

The TC1270A and TC1271A have a push-pull output driver, while the TC1270AN has an open-drain output.

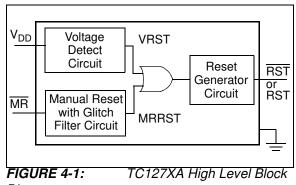

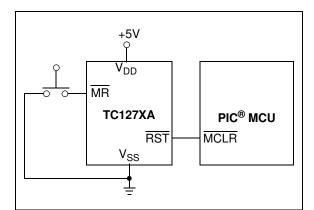

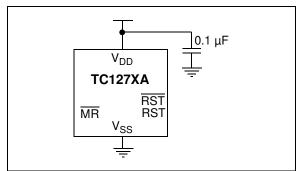

Figure 4-2 shows a typical circuit for a push-pull device and Figure 4-3 shows a typical circuit for an open-drain device.

Diagram.

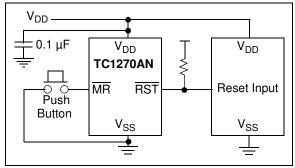

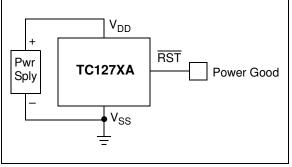

**FIGURE 4-2:** Typical Push-Pull Application Circuit.

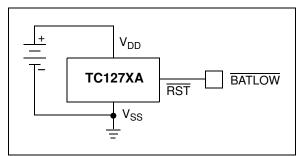

**FIGURE 4-3:** Typical Open-Drain Application Circuit.

The TC1270A and TC1271A devices are available in a 4-Pin SOT-143 package (to maintain footprint compatibility with the TC1270, TC1271, TCM811 and TCM812 devices) and a SOT-23-5 package. The TC1270AN is only available in the SOT-23-5 package.

Low supply current makes these devices suitable for battery-powered applications.

Device specific block diagrams are presented in Figure 4-4 through Figure 4-6.

FIGURE 4-4:

TC1270A Block Diagram.

#### FIGURE 4-5:

TC1270AN Block Diagram.

TC1271A Block Diagram.

#### 4.2 Voltage Detect Circuit

The voltage detect circuit monitors V<sub>DD</sub>. The device's Reset voltage trip point (V<sub>TRIP</sub>) is selected when the device is ordered. The voltage on the device's V<sub>DD</sub> pin determines the output state of the  $\overrightarrow{RST}/RST$  pin.

$V_{DD}$  voltages above the  $V_{TRIP(MAX)}$  force the  $\overline{RST}/RST$  pin inactive.  $V_{DD}$  voltages below the  $V_{T\underline{RIP}(\underline{M}|N)}$  force the  $\overline{RST}/RST$  pin active. The state of the RST/RST pin is unknown for  $V_{DD}$  voltages between  $V_{TRIP(MAX)}$  and  $V_{TRIP(MIN)}$ . This is shown in Table 4-1

### TABLE 4-1:VDD LEVELS TO RST/RST<br/>OUTPUT STATES

| V Veltere Level                                                             | Output State        |                  |  |  |

|-----------------------------------------------------------------------------|---------------------|------------------|--|--|

| V <sub>DD</sub> Voltage Level                                               | RST                 | RST              |  |  |

| $V_{DD} \geq V_{TRIP(MAX)}$                                                 | H <sup>(1, 2)</sup> | L <sup>(1)</sup> |  |  |

| $V_{\text{TRIP}(\text{MIN})} < V_{\text{DD}} < V_{\text{TRIP}(\text{MAX})}$ | U                   | U                |  |  |

| $V_{DD} \leq V_{TRIP(MIN)}$                                                 | L                   | Н                |  |  |

| Legendu II Driven Iligh                                                     |                     |                  |  |  |

Legend: H = Driven High L = Driven Low U = Unknown, driven either High or Low

- Note 1: The  $\overline{\text{RST}}/\text{RST}$  pin will be driven inactive after the Reset Delay Timer ( $t_{\text{RST}}$ ) times out.

- 2: The TC1270AN RST pin will be floated after the Reset Delay Timer (t<sub>RST</sub>) times out.

The term  $V_{TRIP}$  will be used as the general term for the trip point voltage where the device actually trips.

In the case where  $V_{DD}$  is falling (for voltages starting above  $V_{TRIP(MAX)})$ :

- Voltages above V<sub>TRIP(MAX)</sub> will never cause the RST/RST output pin to be driven active.

- Voltages below V<sub>TRIP(MIN)</sub> will always cause the RST/RST output pin to be driven active.

In the case where  $V_{DD}$  is rising (for voltages starting below  $V_{TRIP(MIN)})$ :

• Voltages above  $V_{TRIP(MAX)}$  will always cause the RST/RST output pin to be driven inactive, (or floated, in the TC1270AN) after the Reset Delay Timer (t<sub>RST</sub>), times out.

Table 4-2 shows the various device trip point options and their  $V_{TRIP(MAX)}$  and  $V_{TRIP(MIN)}$  voltages. The negative percentage change from common regulated voltages is also shown.

If the V<sub>DD</sub> is falling from the regulated voltage as it crosses the V<sub>TRIP</sub> voltage, the RST/RST pin is driven active. Then, the desired circuitry is forced into Reset, or the circuitry has the indication that the V<sub>DD</sub> is below the selected V<sub>TRIP</sub>

If the V<sub>DD</sub> is rising as it crosses the V<sub>TRIP</sub> voltage, the RST/RST pin is driven inactive after the Reset Delay Timer elapses. Then, the desired circuitry is released from Reset and will start to operate in its Normal mode, or the circuitry has the indication that the V<sub>DD</sub> is above the selected V<sub>TRIP</sub>

| Trip<br>Voltage | V <sub>TRIP(MAX)</sub> <sup>(1)</sup> /<br>V <sub>TRIP(MIN)</sub> <sup>(2)</sup> | - % From<br>Regulated Voltage |       |       |  |  |  |

|-----------------|----------------------------------------------------------------------------------|-------------------------------|-------|-------|--|--|--|

| Selection       | VTRIP(MIN)                                                                       | 5.0V                          | 3.3V  | 3.0V  |  |  |  |

| L               | 4.75V                                                                            | 5.0%                          | —     | —     |  |  |  |

|                 | 4.50V                                                                            | 10.0%                         | —     | —     |  |  |  |

| М               | M 4.50V                                                                          |                               | —     | —     |  |  |  |

|                 | 4.25V                                                                            | 15.0%                         | —     | —     |  |  |  |

| Т               | 3.15V                                                                            | —                             | 4.5%  | —     |  |  |  |

|                 | 3.00V                                                                            |                               | 9.2%  | —     |  |  |  |

| S               | 3.00V                                                                            | _                             | 9.2%  | —     |  |  |  |

|                 | 2.85V                                                                            | -                             | 13.7% | —     |  |  |  |

| R               | 2.70V                                                                            | _                             | —     | 10.0% |  |  |  |

|                 | 2.55V                                                                            |                               | —     | 15.0% |  |  |  |

TABLE 4-2: SELECTING THE TRIP POINT

Circuitry being reset must have a wider tolerance (%) than V<sub>TRIP(MIN)</sub>% from regulated voltage.

The TC1270A/TC1270AN/TC1271A devices are optimized to reject fast transient glitches on the  $V_{DD}$  line. If the low input signal (which is below  $V_{TRIP}$ ) is not rejected, the Reset output is driven active within 50 µs of  $V_{DD}$  falling through the Reset voltage threshold.

After the device exits the Reset condition, the delay circuitry will hold the  $\overline{\text{RST}}/\text{RST}$  pin active until the appropriate Reset delay time (t<sub>RST</sub>) has elapsed.

During device power-up, the input voltage is below the trip point voltage. The device must enter the valid operating range for the device to start operation.

#### 4.2.1 HYSTERESIS

There is also a minimal hysteresis ( $V_{HYS}$ ) on the trip point. This is so that small noise signals on the device voltage ( $V_{DD}$ ) do not cause the Reset pin (RST/RST) to "jitter" (oscillate between active and inactive levels).

The characterization graphs shown in Figures 2-13 through 2-15 show the device hysteresis as a percentage of the voltage trip point ( $V_{TRIP}$ ).

The Reset Delay Timer  $(t_{\text{RST}})$  gives a time-based hysteresis for the system.

#### 4.2.2 POWER-UP/RISING V<sub>DD</sub>

As the device  $V_{DD}$  rises, the device's Reset circuit will remain active until the voltage rises above the "actual" trip point ( $V_{TRIP}$ ).

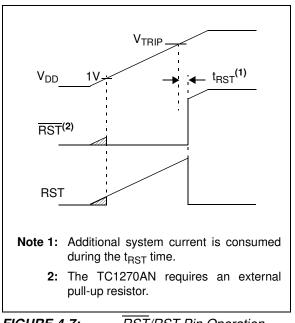

Figure 4-7 shows <u>a</u> power-up sequence and the waveform of the RST and RST pins. As the device powers up, the voltage will start below the valid operating voltage of the device. At this voltage, the RST/RST output is not valid. Once the voltage is above the minimum operating voltage (1V) and below the selected  $V_{TRIP}$  the Reset output will be active.

Once the device voltage rises above the V<sub>TRIP</sub> voltage, the Reset Delay Timer ( $t_{RST}$ ) starts. When the Reset Delay Timer times out, the Reset output (RST/RST) is driven inactive.

FIGURE 4-7: RST/RST Pin Operation Power-up.

Note 1: Voltage regulator circuit must have tighter tolerance (%) than V<sub>TRIP(MAX)</sub>% from regulated voltage.

#### 4.2.3 POWER-DOWN/BROWN-OUT

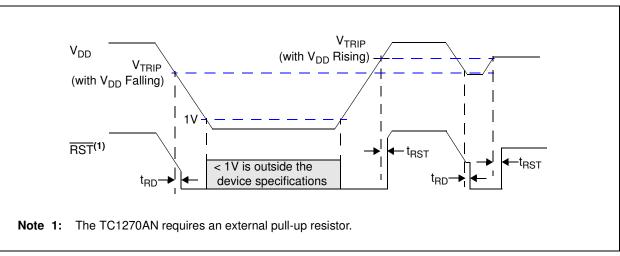

As the device powers-down/browns-out, the V<sub>DD</sub> falls from a voltage above the devices trip point (V<sub>TRIP</sub>). The device will trip at a voltage between the maximum trip point (V<sub>TRIP(MAX)</sub>) and the minimum trip point (V<sub>TRIP(MIN)</sub>). Once the device voltage (V<sub>DD</sub>) goes below this voltage, the RST/RST pin will be forced to the active state. Table 4-3 shows the state of the RST or RST pins.

determined by the V<sub>DD</sub> voltage. As the V<sub>DD</sub> voltage falls from the normal operating point, the device "enters" Reset by crossing the V<sub>TRIP</sub> voltage (between V<sub>TRIP(MAX)</sub> and V<sub>TRIP(MIN)</sub>). Then, when V<sub>DD</sub> voltage rises, the device "exits" Reset by crossing the V<sub>TRIP</sub> voltage (below, or at, V<sub>TRIP(MAX)</sub>). After the "exit" state has been detected, the Reset Delay Timer (t<sub>RST</sub>) starts. When the t<sub>RST</sub> time completes, the Reset pin is driven inactive.

Figure 4-8 shows the waveform of the  $\overline{\text{RST}}$  pin as

#### TABLE 4-3:RESET PIN STATES

| Device  | State of RST Pin when:              |                           | State of RST Pin when:              |                           |               |

|---------|-------------------------------------|---------------------------|-------------------------------------|---------------------------|---------------|

|         | V <sub>DD</sub> < V <sub>TRIP</sub> | $V_{DD} > V_{TRIP}^{(1)}$ | V <sub>DD</sub> < V <sub>TRIP</sub> | $V_{DD} > V_{TRIP}^{(1)}$ | Output Driver |

| TC1270A | L                                   | Н                         | _                                   | _                         | Push-Pull     |

| TC1271A | —                                   | —                         | Н                                   | L                         | Push-Pull     |

Note 1: The  $\overline{RST}/RST$  pin will be driven inactive after the Reset Delay Timer (t<sub>RST</sub>) times out.

FIGURE 4-8: RST Operation as determined by the V<sub>TRIP</sub>

#### 4.3 Negative-Going V<sub>DD</sub> Transients

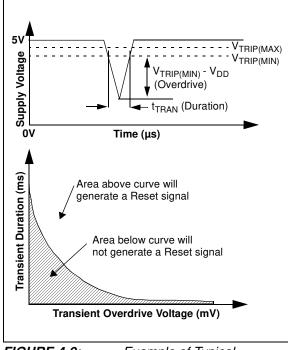

The minimum pulse width (time) required to cause a Reset may be an important criteria in the implementation of a Power-on Reset (POR) circuit. This time is referred to as transient duration. The TC127XA devices are designed to reject a level of negative-going transients (glitches) on the power supply line.

Transient duration is the amount of time needed for these supervisory devices to respond to a drop in V<sub>DD</sub>. The transient duration time (t<sub>TRAN</sub>) is dependent on the magnitude of V<sub>TRIP</sub> – V<sub>DD</sub> (overdrive). Any combination of duration and overdrive that lies under the duration/ overdrive curve will not generate a Reset signal. Generally speaking, the transient duration time decreases with an increase in the V<sub>TRIP</sub> – V<sub>DD</sub> voltage.

Figure 4-9 shows an example transient duration vs. Reset comparator overdrive. It shows that the farther below the trip point the transient pulse goes, the shorter the duration of the pulse required to cause a Reset gets. So, any combination of duration and overdrive that lays **under** the curve will **not** generate a Reset signal. Combinations **above** the curve are detected as a brown-out or power-down.

Transient immunity can be improved by adding a bypass capacitor (typically 0.1  $\mu F)$  as close as possible to the V<sub>DD</sub> pin of the TC127XA device.

FIGURE 4-9: Example of Typical Transient Duration Waveform.

#### 4.4 Manual Reset with Glitch Filter Circuit

The Manual Reset input pin ( $\overline{\text{MR}}$ ) allows the Reset pins (RST/RST) to be manually forced to their active states. The  $\overline{\text{MR}}$  pin has circuitry to filter noise pulses that may be present on the pin. Figure 4-10 shows a block diagram for using the TC127XA with a push button switch. To minimize the required external components, the  $\overline{\text{MR}}$  input has an internal pull-up resistor.

A mechanical push button or active logic signal can drive the  $\overline{\text{MR}}$  input.

Once  $\overline{\text{MR}}$  has been low for a time,  $t_{\text{MD}}$  (the manual Reset delay time), the Reset output pins are forced active. The Reset output pins will remain in their active states for the Reset Delay Timer time-out period ( $t_{\text{RST}}$ ).

Figure 4-11 shows a waveform for the manual Reset switch input and the Reset pins output.

FIGURE 4-10: Push Button Reset.

FIGURE 4-11: MR Input – Push Button.

#### 4.4.1 NOISE FILTER

The noise filter filters out noise spikes (glitches) on the Manual Reset pin ( $\overline{MR}$ ). Noise spikes less than 100 ns (typical) are filtered.

#### 4.5 Reset Generator Circuit

The output signals from the voltage detect circuit and the manual Reset with glitch filter circuit are OR'd together and used to activate the Reset generator module.

After the Reset conditions have been removed (the  $\overline{\text{MR}}$  pin is no longer forced low and the input voltage is greater than the trip point voltage), the Reset generator circuit determines the Reset delay time-out required.

There are three options for the delay circuit. These are:

- 2.19 ms (typical) delay

- · 35 ms (typical) delay

- 280 ms (typical) delay

#### 4.5.1 RESET DELAY TIMER

The Reset Delay Timer ensures that the TC127XA device will "hold" the embedded system in Reset until the system voltage has stabilized. The Reset Delay Timer time-out is shown in Table 4-4.

The Reset Delay Timer starts when the voltage detect circuit output AND the manual Reset with glitch filter circuit output become inactive. While the Reset Delay Timer is active, the  $\overline{\text{RST}}$  or RST pin is driven to the active state. When the Reset Delay Timer times out, the  $\overline{\text{RST}}$  or RST pin is driven inactive.

The Reset Delay Timer ( $t_{RST}$ ) starts after the device voltage rises above the "actual" trip point ( $V_{TRIP}$ ). When the Reset Delay Timer times out, the Reset output pin (RST/RST) is driven inactive.

The Reset Delay Timer is cleared if either, or both, the voltage detector circuit output and the manual Reset with glitch filter circuit output become active. The RST or RST pin continues to be driven to the active state.

Figure 4-12 illustrates when the Reset Delay Timer  $(t_{RST})$  is active or inactive.

#### 4.5.2 EFFECT OF TEMPERATURE ON RESET POWER-UP TIMER (t<sub>RPU</sub>)

The Reset Delay Timer time-out period  $(t_{RST})$  determines how long the device remains in the Reset condition. This time out is affected by the device  $V_{DD}$  and the temperature. Typical responses for varying  $V_{DD}$  values and temperatures are presented in Figures 2-28, 2-29 and 2-30.

| TABLE 4-4: | <b>RESET DELAY TIMER</b> |

|------------|--------------------------|

|            | TIME OUTS                |

| t <sub>RST</sub>                                                                                                                                                |      |                                                                                                                                                                 |       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|

| Min                                                                                                                                                             | Тур  | Max                                                                                                                                                             | Units |  |

| 1.09                                                                                                                                                            | 2.19 | 4.38                                                                                                                                                            | ms    |  |

| 17.5                                                                                                                                                            | 35   | 70                                                                                                                                                              | ms    |  |

| 140                                                                                                                                                             | 280  | 560                                                                                                                                                             | ms    |  |

| ↑<br>This is the<br>minimum time that<br>the Reset Delay<br>Timer will "hold"<br>the Reset pin<br>active after V <sub>DD</sub><br>rises above V <sub>TRIP</sub> |      | ↑<br>This is the<br>maximum time that<br>the Reset Delay<br>Timer will "hold"<br>the Reset pin<br>active after V <sub>DD</sub><br>rises above V <sub>TRIP</sub> |       |  |

Note 1: Shaded rows are custom-ordered time outs.

Reset Power-up Timer

#### 5.0 APPLICATION INFORMATION

This section presents application-related information that may be useful for your particular design requirements.

#### 5.1 Supply Monitor Noise Sensitivity

The TC127XA devices are optimized for fast responses to negative-going changes in V<sub>DD</sub>. A system with an inordinate amount of electrical noise on V<sub>DD</sub> (such as a system using relays) may require a 0.01  $\mu$ F or 0.1  $\mu$ F bypass capacitor to reduce detection sensitivity. This capacitor should be installed as close to the TC127XA as possible to keep the capacitor lead length short.

**FIGURE 5-1:** Typical Application Circuit with Bypass Capacitor.

#### 5.2 Conventional Voltage Monitoring

Figure 5-2 and Figure 5-3 show the TC127XA in conventional voltage monitoring applications.

FIGURE 5-2:

Battery Voltage Monitor.

FIGURE 5-3:

Power Good Monitor.

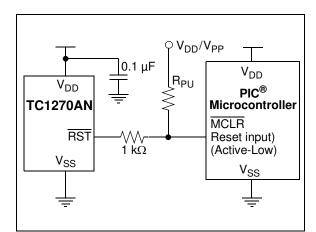

#### 5.3 Using in PIC<sup>®</sup> Microcontroller, ICSP™ Applications

# **Note:** This operation can only be done using the device that has an Open-Drain RST pin (TC1270AN).

Figure 5-4 shows the typical application circuit for using the TC1270AN for voltage supervisory function when the PIC microcontroller will be programmed via the In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) feature. Additional information is available in the Microchip Technical Brief TB087, *"Using Voltage Supervisors with PICmicro<sup>®</sup> Microcontroller Systems which Implement In-Circuit Serial Programming<sup>TM</sup>"* (DS91087).

Note: It is recommended that the current into the RST pin is current that is limited by a 1  $k\Omega$  resistor.

**FIGURE 5-4:** Typical Application Circuit for PIC Microcontroller with the ICSP Feature.