Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

32-Bit

Microcontroller

TC1791

32-Bit Single-Chip Microcontroller

Data Sheet V 1.1 2014-05

Microcontrollers

Edition 2014-05

Published by

Infineon Technologies AG

81726 Munich, Germany

© 2014 Infineon Technologies AG

All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (<a href="https://www.infineon.com">www.infineon.com</a>).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

32-Bit

Microcontroller

TC1791

32-Bit Single-Chip Microcontroller

Data Sheet V 1.1 2014-05

Microcontrollers

# **Table of Contents**

| 1                                   | Summary of Features                                                                                                           | 1-1                          |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| <b>2</b><br>2.1                     | System Overview of the TC1791                                                                                                 |                              |

| <b>3</b><br>3.1                     | Pinning TC1791 Pin Configuration                                                                                              |                              |

| 4                                   | Identification Registers                                                                                                      | . 4-67                       |

| 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3 | Electrical Parameters General Parameters Parameter Interpretation Pad Driver and Pad Classes Summary Absolute Maximum Ratings | 5-70<br>5-70<br>5-71<br>5-72 |

| 5.1.4<br>5.1.5                      | Pin Reliability in Overload                                                                                                   |                              |

| 5.1.5<br>5.1.5.1<br>5.2             | Operating Conditions                                                                                                          | . 5-81                       |

| 5.2.1                               | Input/Output Pins                                                                                                             | . 5-83                       |

| 5.2.2                               | Analog to Digital Converters (ADCx)                                                                                           |                              |

| 5.2.3                               | Fast Analog to Digital Converter (FADC)                                                                                       |                              |

| 5.2.4<br>5.2.5                      | Oscillator Pins                                                                                                               | 5-108<br>5-109               |

| 5.2.5<br>5.2.6                      | Power Supply Current                                                                                                          | 5-110                        |

| 5.2.6.1                             | Calculating the 1.3 V Current Consumption                                                                                     | 5-113                        |

| 5.3                                 | AC Parameters                                                                                                                 | 5-115                        |

| 5.3.1                               | Testing Waveforms                                                                                                             | 5-115                        |

| 5.3.2                               | Power Sequencing                                                                                                              | 5-116                        |

| 5.3.3                               | Power, Pad and Reset Timing                                                                                                   | 5-118                        |

| 5.3.4                               | Phase Locked Loop (PLL)                                                                                                       | 5-120                        |

| 5.3.5                               | ERAY Phase Locked Loop (ERAY_PLL)                                                                                             | 5-123                        |

| 5.3.6                               | JTAG Interface Timing                                                                                                         | 5-124                        |

| 5.3.7                               | DAP Interface Timing                                                                                                          | 5-126                        |

| 5.3.8                               | Micro Link Interface (MLI) Timing                                                                                             | 5-127                        |

| 5.3.9                               | Micro Second Channel (MSC) Interface Timing                                                                                   | 5-130                        |

| 5.3.10                              | SSC Master/Slave Mode Timing                                                                                                  | 5-132                        |

| 5.3.11                              | ERAY Interface Timing                                                                                                         | 5-135                        |

| 5.4                                 | Flash Memory Parameters                                                                                                       | 5-136                        |

| 5.5                                 | Package and Reliability                                                                                                       | 5-139                        |

| 5.5.1                               | Package Parameters                                                                                                            | 5-139                        |

| 552                                 | Package Outline                                                                                                               | 5-140                        |

| 5.5.3 | Quality Declarations | 5-140 |

|-------|----------------------|-------|

| 6     | History              | 6-1   |

## 1 Summary of Features

The SAK-TC1791F-512F240EL / SAK-TC1791F-512F240EP has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 240 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 4 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with 2 x 255 hardware priority arbitration levels serviced by CPU or PCP2

- High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- One FlexRay<sup>™</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 48 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of f<sub>FADC</sub> clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL and PLL ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

# The SAK-TC1791F-512F200EL / SAK-TC1791F-512F200EP has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 200 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 4 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with 2 x 255 hardware priority arbitration levels serviced by CPU or PCP2

- High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- One FlexRay<sup>™</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 44 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{\text{FADC}}$  clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL and PLL\_ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

# The SAK-TC1791F-384F200EL / SAK-TC1791F-384F200EP has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 200 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 3 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with  $2 \times 255$  hardware priority arbitration levels serviced by CPU or PCP2

- · High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- One FlexRay<sup>TM</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 44 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{EADC}$  clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- · Clock Generation Unit with PLL and PLL ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

#### The **SAK-TC1791S-512F240EP** has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 240 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 4 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with 2 x 255 hardware priority arbitration levels serviced by CPU or PCP2

- High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- One FlexRay<sup>TM</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 48 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{\text{FADC}}$  clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- · Clock Generation Unit with PLL and PLL ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

- Secure Hardware Extension (SHE)

- For further information please contact your Infineon representative

#### The **SAK-TC1791S-384F200EP** has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 200 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 3 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with 2 x 255 hardware priority arbitration levels serviced by CPU or PCP2

- · High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- One FlexRay<sup>™</sup> module with 2 channels (E-Ray).

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 44 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{EADC}$  clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL and PLL ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

- Secure Hardware Extension (SHE)

- For further information please contact your Infineon representative

## The SAK-TC1791N-384F200EP has the following features:

- High-performance 32-bit super-scalar TriCore V1.6 CPU with 6-stage pipeline

- Superior real-time performance

- Strong bit handling

- Fully integrated DSP capabilities

- Multiply-accumulate unit able to sustain 2 MAC operations per cycle

- Fully pipelined Floating point unit (FPU)

- 200 MHz operation at full temperature range

- 32-bit Peripheral Control Processor with single cycle instruction (PCP2)

- 16 Kbyte Parameter Memory (PRAM)

- 32 Kbyte Code Memory (CMEM)

- 200 MHz operation at full temperature range

- Multiple on-chip memories

- 3 Mbyte Program Flash Memory (PFLASH) with ECC

- 192 Kbyte Data Flash Memory (DFLASH) usable for EEPROM emulation

- 2 x 8 Kbyte Key Flash

- 128 Kbyte Data Scratch-Pad RAM (DSPR)

- 16 Kbyte Instruction Cache (ICACHE)

- 32 Kbyte Instruction Scratch-Pad RAM (PSPR)

- 16 Kbyte Data Cache (DACHE)

- 128 Kbyte Memory (SRAM)

- 16 Kbyte BootROM (BROM)

- 16-Channel DMA Controller

- · 8-Channel Safe DMA (SDMA) Controller

- Sophisticated interrupt system with  $2 \times 255$  hardware priority arbitration levels serviced by CPU or PCP2

- · High performing on-chip bus structure

- 64-bit Cross Bar Interconnect between CPU, Flash and Data Memory

- 32-bit System Peripheral Bus (SPB) for on-chip peripheral and functional units

- One bus bridge (SFI Bridge)

- Versatile On-chip Peripheral Units

- Two Asynchronous/Synchronous Serial Channels (ASC) with baud rate generator, parity, framing and overrun error detection

- Four High-Speed Synchronous Serial Channels (SSC) with programmable data length and shift direction

- Four SSC Guardian (SSCG) modules, one for each SSC

- Two serial Micro Second Bus interfaces (MSC) for serial port expansion to external power devices

- Two High-Speed Micro Link interfaces (MLI) for serial inter-processor communication

- One MultiCAN Module with 4 CAN nodes and 128 free assignable message objects for high efficiency data handling via FIFO buffering and gateway data transfer (one CAN node supports TTCAN functionality)

- Two General Purpose Timer Array Modules (GPTA) with additional Local Timer Cell Array (LTCA2) providing a powerful set of digital signal filtering and timer functionality to realize autonomous and complex Input/Output management

- Two Capture / Compare 6 modules

- Two General Purpose 12 Timer Units (GPT120 and GPT121)

- 44 analog input lines for ADC

- 4 independent kernels (ADC0, ADC1, and ADC2)

- Analog supply voltage range from 3.3 V to 5 V (single supply)

- 4 different FADC input channels

- channels with impedance control and overlaid with ADC1 inputs

- Extreme fast conversion, 21 cycles of  $f_{EADC}$  clock

- 10-bit A/D conversion (higher resolution can be achieved by averaging of consecutive conversions in digital data reduction filter)

- 8 digital input lines for SENT

- communication according to the SENT specification J2716 FEB2008

- 128 digital general purpose I/O lines (GPIO)

- Digital I/O ports with 3.3 V capability

- On-chip debug support for OCDS Level 1 (CPU, PCP, DMA, On Chip Buses)

- Dedicated Emulation Device chip available (TC1791ED)

- multi-core debugging, real time tracing, and calibration

- four/five wire JTAG (IEEE 1149.1) or two wire DAP (Device Access Port) interface

- Power Management System

- Clock Generation Unit with PLL and PLL ERAY

- Flexible CRC Engine (FCE)

- IEEE 802.3 CRC32 ethernet polynomial: 0x82608EDB (CRC kernel 0)

- CRC32C Castagnoli: 0xD419CC15 (CRC kernel 1)

### **Ordering Information**

The ordering code for Infineon microcontrollers provides an exact reference to the required product. This ordering code identifies:

- The derivative itself, i.e. its function set, the temperature range, and the supply voltage

- · The package and the type of delivery.

For the available ordering codes for the TC1791 please refer to the "**Product Catalog Microcontrollers**". which summarizes all available microcontroller variants.

This document describes the derivatives of the device. The **Table 1** enumerates these derivatives and summarizes the differences.

Table 1 TC1791 Derivative Synopsis

| Derivative            | <b>Ambient Temperature Range</b>                     |

|-----------------------|------------------------------------------------------|

| SAK-TC1791F-512F240EL | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791F-512F240EP | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$ |

| SAK-TC1791F-512F200EL | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791F-512F200EP | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791F-384F200EL | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791F-384F200EP | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791S-512F240EP | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791S-384F200EP | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

| SAK-TC1791N-384F200EP | $T_A = -40^{\circ}C \text{ to } +125^{\circ}C$       |

|                       | <del></del>                                          |

#### System Overview of the TC1791

## 2 System Overview of the TC1791

The TC1791 combines three powerful technologies within one silicon die, achieving new levels of power, speed, and economy for embedded applications:

- · Reduced Instruction Set Computing (RISC) processor architecture

- Digital Signal Processing (DSP) operations and addressing modes

- · On-chip memories and peripherals

DSP operations and addressing modes provide the computational power necessary to efficiently analyze complex real-world signals. The RISC load/store architecture provides high computational bandwidth with low system cost. On-chip memory and peripherals are designed to support even the most demanding high-bandwidth real-time embedded control-systems tasks.

Additional high-level features of the TC1791 include:

- Efficient memory organization: instruction and data scratch memories, caches

- Serial communication interfaces flexible synchronous and asynchronous modes

- Peripheral Control Processor standalone data operations and interrupt servicing

- DMA Controller DMA operations and interrupt servicing

- General-purpose timers

- High-performance on-chip buses

- On-chip debugging and emulation facilities

- · Flexible interconnections to external components

- · Flexible power-management

The TC1791 is a high-performance microcontroller with TriCore CPU, program and data memories, buses, bus arbitration, an interrupt controller, a peripheral control processor and a DMA controller and several on-chip peripherals. The TC1791 is designed to meet the needs of the most demanding embedded control systems applications where the competing issues of price/performance, real-time responsiveness, computational power, data bandwidth, and power consumption are key design elements.

The TC1791 offers several versatile on-chip peripheral units such as serial controllers, timer units, and Analog-to-Digital converters. Within the TC1791, all these peripheral units are connected to the TriCore CPU/system via the Flexible Peripheral Interconnect (FPI) Bus and the Cross Bar Interconnect (SRI). Several I/O lines on the TC1791 ports are reserved for these peripheral units to communicate with the external world.

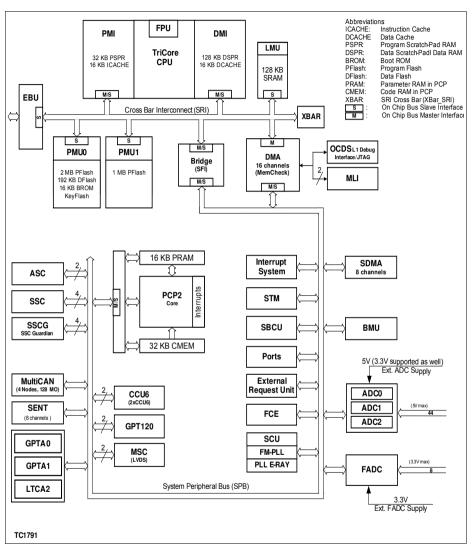

## 2.1 Block Diagram

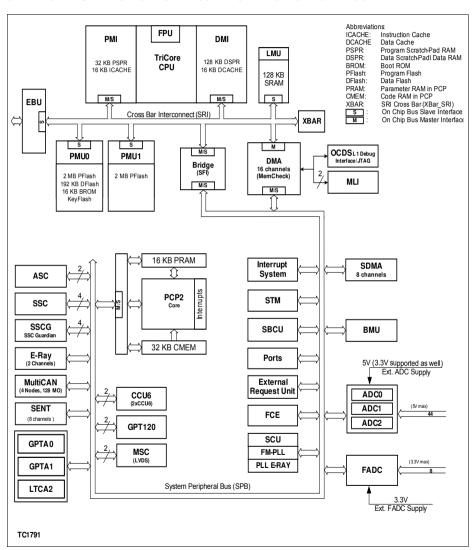

Figure 1 shows the block diagram of the SAK-TC1791F-512F240EL / SAK-TC1791F-512F240EP / SAK-TC1791F-512F200EL / SAK-TC1791F-512F200EP.

Figure 1 Block Diagram

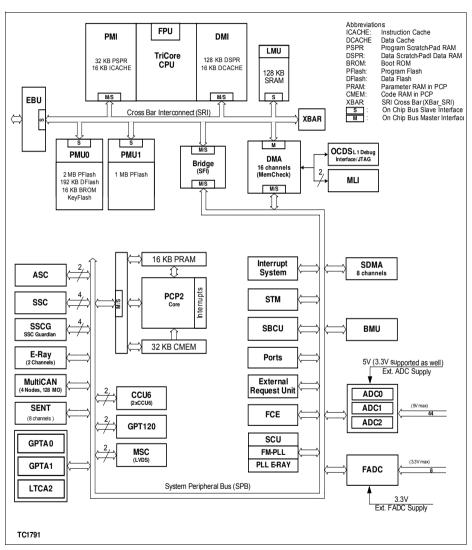

Figure 2 shows the block diagram of the SAK-TC1791F-384F200EL / SAK-TC1791F-384F200FP

Figure 2 Block Diagram

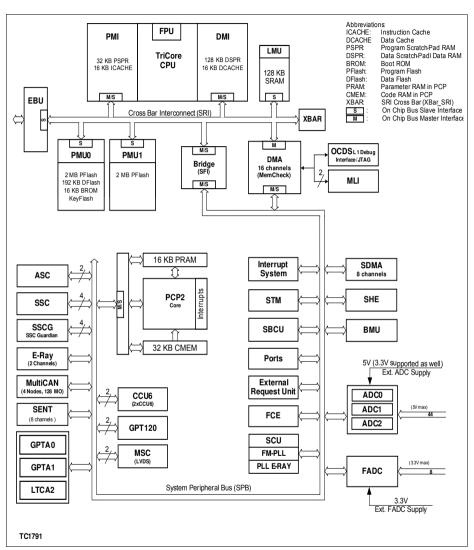

Figure 3 shows the block diagram of the SAK-TC1791S-512F240EP.

Figure 3 Block Diagram

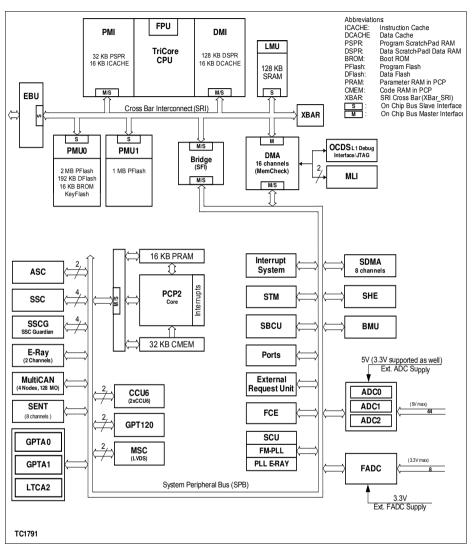

Figure 4 shows the block diagram of the SAK-TC1791S-384F200EP.

Figure 4 Block Diagram

Figure 5 shows the block diagram of the SAK-TC1791N-384F200EP.

Figure 5 Block Diagram