Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Serial Interface Adapter for TC500 A/D Converter Family

#### **Features**

- Converts TC500/TC500A/TC510/TC514 to Serial Operation

- Programmable Conversion Rate and Resolution for Maximum Flexibility

- Supports up to 17-Bits of Accuracy Plus Polarity Bit

- Low Power Operation: Typically 7.5mΩ

- 14-Pin PDIP or 16-Pin SOIC Packages

- · Polled or Interrupt Mode Operation

### **Applications**

- · Computer Peripheral Interface

- · Portable Instruments

- · Data Acquisition System Interface

#### **Device Selection Table**

| Part Number | Package            | Temperature Range |  |  |

|-------------|--------------------|-------------------|--|--|

| TC520ACOE   | 16-Pin SOIC (Wide) | 0°C to +70°C      |  |  |

| TC520ACPD   | 14-Pin PDIP        | 0°C to +70°C      |  |  |

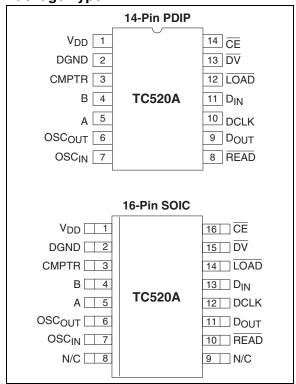

#### Package Type

#### **General Description**

The TC520A serial interface adapter provides logic control for Microchip's TC500/TC500A/TC510/TC514 family of dual slope, integrating A/D converters. It directly manages TC500 converter phase control signals A, B and CMPTR, thereby reducing host processor task loading and software complexity. Communication with the TC520A is accomplished over a 3 wire serial port. Key converter operating parameters are programmable for complete user flexibility. Data conversion is initiated when the  $\overline{CE}$  input is brought low. The converted data (plus overrange and polarity bits) are held in an 18-bit shift register until read by the processor or until the next conversion is completed. Data may be clocked out of the TC520A at any time, and at any rate, the user prefers, A Data Valid (DV) output is driven active at the start of each conversion cycle, indicating the 18-bit shift register update has just been completed. This signal may be polled by the processor or can be used as data ready interrupt. The TC520A timebase can be derived from an external frequency source of up to 6MHz or can operate from its own external crystal. It requires a single 5V logic supply and dissipates less than 7.5m $\Omega$ .

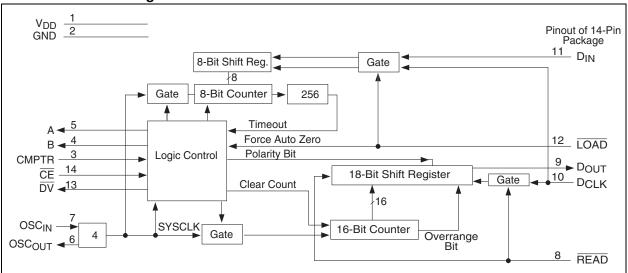

## **Functional Block Diagram**

# 1.0 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings\***

DC Supply Voltage ( $V_{DD}$ )......+6.0V Input Voltage (All Inputs  $V_{IN}$ ):.... - 0.3V to ( $V_{DD}$  + 0.3V) Operating Temperature Range ( $T_A$ ).......0°C to 70°C Storage Temperature Range.....-65°C to +150°C

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions above those indicated in the operation sections of the specifications is not implied. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

#### **TC520A ELECTRICAL SPECIFICATIONS**

| Electrical Characteristics: V <sub>DD</sub> = 5V, F <sub>OSC</sub> = 1MHz, T <sub>A</sub> = +25°C, unless otherwise specified. |                                                                |          |     |     |      |                 |  |

|--------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|----------|-----|-----|------|-----------------|--|

| Symbol                                                                                                                         | Parameters                                                     | Min      | Тур | Max | Unit | Test Conditions |  |

| Supply                                                                                                                         |                                                                | <b>-</b> | 1   | •   |      |                 |  |

| V <sub>DD</sub>                                                                                                                | Operating Voltage Range                                        | 4.5      | 5   | 5.5 | V    |                 |  |

| I <sub>DD</sub>                                                                                                                | Supply Current                                                 | _        | 0.8 | 1.5 | mA   |                 |  |

| Input Chara                                                                                                                    | cteristics                                                     |          |     |     |      |                 |  |

| V <sub>IL</sub>                                                                                                                | Low Input Voltage                                              | _        | _   | 0.8 | V    |                 |  |

| V <sub>IH</sub>                                                                                                                | High Input Voltage                                             | 2.0      | _   | _   | V    |                 |  |

| I <sub>IL</sub>                                                                                                                | Input Leakage Current                                          | <u> </u> |     | μА  |      |                 |  |

| I <sub>PD</sub>                                                                                                                | Pull-down Current (CE)                                         | _        | 5   | _   | μА   |                 |  |

| I <sub>PU</sub>                                                                                                                | Pull-up Current (READ, LOAD)                                   | _        | 5   | _   | μА   |                 |  |

| Output Cha                                                                                                                     | racteristics (I <sub>OUT</sub> = 250 μA, V <sub>DD</sub> = 5V) | •        | •   |     |      |                 |  |

| V <sub>OL</sub>                                                                                                                | Low Output Voltage                                             | _        | 0.2 | 0.3 | V    |                 |  |

| V <sub>OH</sub>                                                                                                                | High Output Voltage                                            | 3.5      | 4.3 | _   | V    |                 |  |

| T <sub>R</sub> , T <sub>F</sub>                                                                                                | C <sub>L</sub> = 10pF, Rise/Fall Times                         | _        | _   | 250 | nsec |                 |  |

| Oscillator (0                                                                                                                  | OSC <sub>IN</sub> , OSC <sub>OUT</sub> )                       | •        | •   |     |      |                 |  |

| F <sub>XTL</sub>                                                                                                               | Crystal Frequency                                              | _        | 1.0 | 4.0 | MHz  |                 |  |

| Fosc                                                                                                                           | External Frequency (OSC <sub>IN</sub> )                        | _        | _   | 6.0 | MHz  |                 |  |

| Timing Cha                                                                                                                     | racteristics                                                   |          |     |     |      |                 |  |

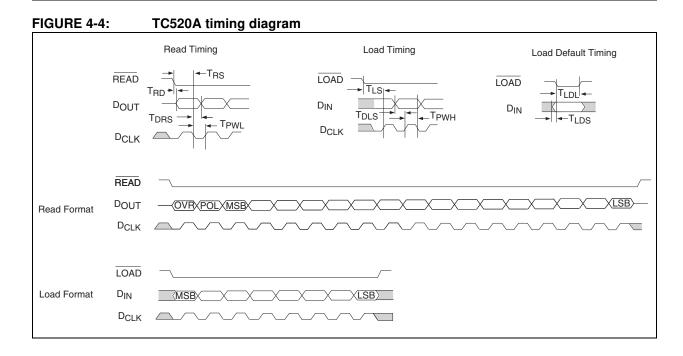

| $T_RD$                                                                                                                         | READ Delay Time                                                | 250      | _   | _   | nsec |                 |  |

| T <sub>RS</sub>                                                                                                                | Data Read Setup Time                                           | 1        | _   | _   | μsec |                 |  |

| T <sub>DRS</sub>                                                                                                               | D <sub>CLK</sub> to D <sub>OUT</sub> Delay                     | 450      | _   | _   | nsec |                 |  |

| T <sub>LS</sub>                                                                                                                | LOAD Setup Time                                                | 1        | _   | _   | μsec |                 |  |

| T <sub>DLS</sub>                                                                                                               | Data Load Setup Time                                           | 50       | _   | _   | nsec |                 |  |

| T <sub>PWL</sub>                                                                                                               | D <sub>CLK</sub> Pulse Width Low Time                          | 150      | _   | _   | nsec |                 |  |

| T <sub>PWH</sub>                                                                                                               | D <sub>CLK</sub> Pulse Width High Time                         | 150      | _   | _   | nsec |                 |  |

| T <sub>LDL</sub>                                                                                                               | Load Default Low Time                                          | 250      | _   | _   | nsec |                 |  |

| T <sub>LDS</sub>                                                                                                               | Load Default Setup Time                                        | 250      | _   | _   | nsec |                 |  |

| Parameter                                                                                                                      |                                                                |          |     |     |      |                 |  |

| T <sub>IZ</sub>                                                                                                                | Integrator ZERO Time                                           | _        | 0.5 | _   | msec |                 |  |

| T <sub>AZI</sub>                                                                                                               | Auto zero (RESET) Time at Power-Up                             | _        | 100 | _   | msec |                 |  |

## 2.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 2-1

TABLE 2-1: PIN FUNCTION TABLE

| Pin Number<br>14-Pin PDIP | Pin Number<br>16-Pin SOIC | Symbol             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------|---------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                         | 1                         | $V_{DD}$           | Input. +5V ±10% power supply input with respect to DGND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2                         | 2                         | DGND               | Input. Digital Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3                         | 3                         | CMPTR              | Input, active high or low (depending on polarity of the voltage input to A/D converter). This pin connects directly to the zero crossing comparator output (CMPTR) of the TC5XX A/D converter. A high-to-low state change on this pin causes the TC520A to terminate the de-integrate phase of conversion.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4                         | 4                         | В                  | Output, active high. The A and B outputs of the TC520A connect directly to the A and B inputs of the TC5XX A/D converter connected to the TC520A. The binary code on A, B determines the conversion phase of the TC5XX A/D converter: (A, B) = 01 places the TC5XX A/D converter into the Auto Zero phase; (A, B) =10 for Integrate phase (INT); (A, B) =11 for De-integrate phase (DINI) and (A, B) = 00 for Integrator Zero phase (IZ). Please see the TC500/TC500A/TC510/TC514 family data sheets for a complete description of these phases of operation.                                                                                                                                                                                                                                   |

| 5                         | 5                         | Α                  | Output, active high. See pin 4 description above.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6                         | 6                         | OSC <sub>OUT</sub> | Input. This pin connects to one side of an AT-cut crystal having a effective series resistance of $100\Omega$ (typ.) and a parallel capacitance of $20pF$ (typ.). If an external frequency source is used to clock the TC520A, this pin must be left floating.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 7                         | 7                         | OSC <sub>IN</sub>  | Input. This pin connects to the other side of the crystal described in pin 6 above. The TC520A may also be clocked from an external frequency source connected to this pin. The external frequency source must be a pulse train having a duty cycle of 30% (minimum); rise and fall times of 15nsec and a min/max amplitude of 0 to V <sub>IH</sub> . If an external frequency source is used, pin 6 must be left floating. A maximum operating frequency of 4MHz (crystal) or 6MHz (external clock source) is permitted.                                                                                                                                                                                                                                                                       |

|                           | 8                         | N/C                | No connection on 16 pin package version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                           | 9                         | N/C                | No connection on 16 pin package version.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8                         | 10                        | READ               | Input, active low, level and negative edge triggered. A high-to-low transition on READ loads serial port output shift register with the most recent converted data. Data is loaded such that the first bit transmitted from the TC520A to the processor is the OVERRANGE bit (OVR), followed by the POLARITY bit (POL) (high = input positive; low = input negative). This is followed by a 16-bit data word (MSB first). OVR is available at the D <sub>OUT</sub> as soon as READ is brought low. This bit may be used as the 17th data bit, if so desired. The D <sub>OUT</sub> pin of the serial port is enabled only when READ is held low. Otherwise, D <sub>OUT</sub> remains in a high impedance state. A serial port read access cycle is terminated at any time by bringing READ high. |

| 9                         | 11                        | D <sub>OUT</sub>   | Output, logic level. Serial port output pin. This pin is enabled only when READ is low (see READ pin description).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 10                        | 12                        | D <sub>CLK</sub>   | Input, positive and negative edge triggered. Serial port clock. With $\overline{\text{READ}}$ low, serial data is clocked into the TC520A at each low-to-high transition of $D_{CLK}$ , and clocked out of the TC520A on each high-to-low transition of $D_{CLK}$ . A maximum serial port $D_{CLK}$ frequency of 3MHz is permitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 11                        | 13                        | D <sub>IN</sub>    | Input, logic level. Serial port input pin. The TC5XX A/D converter integration time ( $T_{INT}$ ) and Auto Zero time (TAZ) values are determined by the LOAD VALUE byte clocked into this pin. This initialization must take place at power up and can be rewritten (or modified and rewritten) at any time. The LOAD VALUE is clocked into $D_{IN}$ MSB first.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

# TABLE 2-1: PIN FUNCTION TABLE (CONTINUED)

| Pin Number<br>14-Pin PDIP | Pin Number<br>16-Pin SOIC | Symbol | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------|---------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12                        | 14                        | LOAD   | Input, active low; level and edge triggered. The LOAD VALUE is clocked into the 8-bit shift register on board the TC520A while $\overline{\text{LOAD}}$ is held low. The LOAD VALUE is then transferred into the TC520A internal timebase counter (and becomes effective) when $\overline{\text{LOAD}}$ is returned high. If so desired, $\overline{\text{LOAD}}$ can be momentarily pulsed low, eliminating the need to clock a LOAD VALUE into D $_{\text{IN}}$ . In this case, the current state of D $_{\text{IN}}$ is clocked into the TC520A timebase counter selecting either a count of 65536 (D $_{\text{IN}}$ = High), or count of 32768, (D $_{\text{IN}}$ = Low).                                                                                                                                                                                                                              |

| 13                        | 15                        | DV     | Output, active low. $\overline{\text{DV}}$ is brought low any time the TC520A is in the AZ phase of conversion. This occurs when, either the TC520A initiates a normal AZ phase by setting A, B, equal to 01, or when $\overline{\text{CE}}$ is pulled high, which overrides the normal A, B sequencing and forces an AZ state. $\overline{\text{DV}}$ is returned high when the TC520A exits AZ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 14                        | 16                        | CE     | Input, active low, level triggered. Conversion will be continuously performed as long as $\overline{\text{CE}}$ remains low. Pulling $\overline{\text{CE}}$ high causes the conversion process to be halted and forces the TC520A into the AZ mode for as long as $\overline{\text{CE}}$ remains high. $\overline{\text{CE}}$ should be taken high whenever it is necessary to momentarily suspend conversion (for example: to change the address lines of an input multiplexer). $\overline{\text{CE}}$ should be pulled high only when the TC520A enters an AZ phase (i.e. when $\overline{\text{DV}}$ is low). This is necessary to avoid excessively long integrator discharge times, which could result in erroneous conversion. This pin should be grounded if unused. It should be left floating if a $0.01\mu\text{F}$ RESET capacitor is connected to it (see Section 4.0, Typical Applications). |

#### 3.0 DETAILED DESCRIPTION

#### 3.1 TC520A Timing

The TC520A consists of a serial port and state machine. The state machine provides control timing to the TC5xx A/D converter connected to the TC520A as well as providing sequential timing for TC520A internal operation. All timing is derived from the frequency source at  $\rm OSC_{IN}$  and  $\rm OSC_{OUT}$ . This frequency source can be either an externally provided clock signal or external crystal. If an external clock is used, it must be connected to the  $\rm OSC_{IN}$  pin and  $\rm OSC_{OUT}$  must remain floating. If a crystal is used, it must be connected between the  $\rm OSC_{IN}$  and  $\rm OSC_{OUT}$  and be physically located as close to the  $\rm OSC_{IN}$  and  $\rm OSC_{OUT}$  pins as possible. The incoming frequency is internally divided by 4 and the resulting clock (SYSCLK) controls all timing functions.

# 3.2 TC5XX A/D Converter Control Signals

The TC520A control outputs (A, B) and control input (CMPTR) connect directly to the corresponding pins of the TC5XX A/D converter. A conversion is consummated when A, B have been sequenced through the required 4 phases of conversion: Auto Zero (AZ), Integrate (INT), De-integrate (D<sub>INT</sub>) and Integrator Zero (IZ) (see Figure 4-1). The Auto Zero phase compensates for offset errors in the TC5XX A/D converter. The Integrate phase connects the voltage to be converted to the TC5XX A/D converter input, resulting in an integrator output dv/dt directly proportional to the magnitude of the applied input voltage. Actual A/D conversion (counting) is initiated at the start of the DINT phase and terminates when the integrator output crosses 0V. The integrator output is then forced to 0V during the IZ phase and the converter is ready for another cycle. Please see the TC500/TC500A/TC510/TC514 data sheet for a complete description of these phases.

The number of SYSCLK periods (counts) for the AZ and INT phases is determined by the LOAD VALUE. The LOAD VALUE is a single byte that must be loaded into the most significant byte of 16-bit counter on board the TC520A during initialization. The lower byte of this counter is pre-loaded to a value of 0FFH (256<sub>10</sub>) and cannot be changed.

The LOAD VALUE (upper 8 bits of the counter) can be programmed over a range of 0FFH to 00H (corresponding to a range of AZ = INT = 256 counts to 65536 counts). (See Figure 3-2). The LOAD VALUE sets the number of counts for both the AZ and INT phases and directly affects resolution and speed of conversion. The greater the number of counts allowed for AZ and INT, the greater the A/D resolution (but the slower the conversion speed).

The time period required for the DINT phase is a function of the amount of voltage stored on the integrator during the INT phase and the value of  $V_{REF}$ . The DINT phase is initiated by the TC520A immediately after the INT phase and terminated when the TC5XX A/D converter changes the state of the CMPTR input of the TC520A, indicating a zero crossing. In general, the maximum number of counts chosen for DINT is twice that of INT (with  $V_{REF}$  chosen at  $V_{ININ(MAX)}/2$ ). Choosing these values guarantees a full count (maximum resolution) during  $D_{INT}$  when  $V_{IN} = V_{IN(MAX)}$ .

The IZ phase is initiated immediately following the  $D_{INT}$  phase and is maintained until the CMPTR input transitions high. This indicates the integrator is initialized and ready for another conversion cycle. This phase typically takes 2msec.

#### 3.3 Serial Port Control Signals

Communication to and from the TC520A is accomplished over a 3 wire serial port. Data is clocked into  $D_{IN}$  on the rising edge of  $D_{CLK}$  and clocked out of  $D_{OUT}$  on the falling edge of  $D_{CLK}$ . READ must be low to read from the serial port and can be taken high at any time, which terminates the read cycle and releases  $D_{OUT}$  to a high impedance state. Conversion data is shifted to the processor from  $D_{OUT}$  in the following order: OVERRANGE (which can also be used as the 17th data bit), POLARITY, conversion data (MSB first).

#### 4.0 TYPICAL APPLICATIONS

## 4.1 TC500 Series A/D Converter Component Selection

The TC500/TC500A/TC510/TC514 data sheet details the equations necessary to calculate values for integration resistor (R<sub>INT</sub>) and capacitor (C<sub>INT</sub>), auto zero (C<sub>AZ</sub>) and reference capacitors (C<sub>REF</sub>) and voltage reference (V<sub>REF</sub>). All equations apply when using the TC520A, except Integration time (T<sub>INT</sub>) and Auto zero time (T<sub>AZ</sub>), which are functions of the SYSCLK period (timebase frequency and LOAD VALUE). Microchip offers a ready-to-use TC5XX A/D converter design tool. The TC500 Design Spreadsheet is an Excel-based spreadsheet that calculates values for all components as well as the TC520A LOAD VALUE. It also calculates overall converter performance such as noise rejection, converter speed, etc.

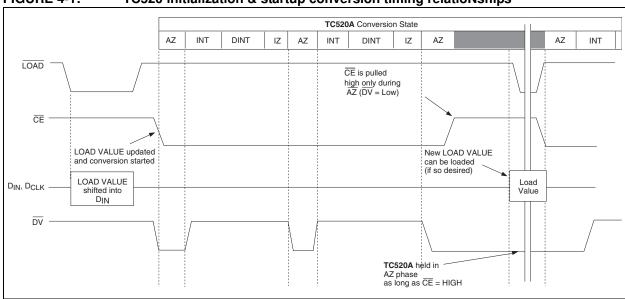

#### 4.2 TC520A Initialization

Initialization of the TC520A consists of:

- Power-On RESET of the TC500/TC520A (forcing the TC520A into an AZ phase).

- 2. Initializing the TC520A LOAD VALUE.

#### 4.3 Power-On RESET

The TC520A powers up with A,B = 00 (IZ Phase), awaiting a high logic state on CMPTR, which must be initiated by forcing the TC520A into the AZ phase. This can be accomplished in one of two ways:

- External hardware (processor or logic) can momentarily pull LOAD or CE low for a minimum of 100msec (T<sub>AZI</sub>) or;

- 2. A  $.01\mu F$  RESET capacitor can be connected from  $\overline{CE}$  to  $V_{CC}$  to generate a power-on pulse on  $\overline{CE}$ .

#### 4.4 LOAD VALUE Initialization

The LOAD VALUE is the preset value (high byte of the SYSCLK timing counter) which determines the number of counts allocated to the AZ and INT phases of conversion. This value can be calculated using either the TC520A spreadsheet within the TC500 Design Spreadsheet software or can be setup as shown in the following sections.

#### 4.4.1 SELECT VREF, TDEINT

Choose the TC5XX A/D converter reference voltage ( $V_{REF}$ ) to be half of the maximum A/D converter input voltage. For example, if  $V_{IN(MAX)} = 2.5V$ , choose  $V_{REF} = 1.25V$ . This forces the maximum de-integration time ( $T_{DEINT}$ ) to be equal to twice the maximum integration time ( $T_{INT}$ ), ensuring a full count (maximum resolution) during DINT.

#### 4.4.2 CALCULATE TINT

The TC520A counter length is 16-bits (65536), allowing the full 65536 counts for  $T_{DEINT}$  results in a maximum  $T_{INT}$  = 65536/2 or 32768.

#### 4.4.3 SELECT SYSCLK FREQUENCY

SYSCLK frequency directly affects conversion time. The faster the SYSCLK, the faster the conversion time. The upper limit SYSCLK frequency is determined by the worst case delay of the TC500 comparator (which for the TC500 and TC500A is  $3.2\mu sec)$ . While a faster value for SYSCLK can be used, operation is optimized (error minimized) by choosing a SYSCLK period (1/SYSCLK frequency) that is greater than  $3.2\mu sec$ . Choosing  $T_{SYSCLK}=4\mu sec$  makes the SYSCLK frequency equal to 250kHz. This makes the external crystal (or frequency source) equal to 1.0MHz, since SYSCLK = crystal frequency/4). Calculating integration time (in msec) using  $T_{SYSCLK}=4\mu sec$ ,  $T_{INT}=4\mu sec$  x 32768=131 msec.

#### 4.4.4 CALCULATE LOAD VALUE

Plug the  $T_{INT}$  and  $T_{SYSCLK}$  values into the equation and convert the resulting value to hexadecimal:

#### **EQUATION 4-1:**

$$LOAD VALUE = \frac{[(65536 - (T_{INT}/T_{SYSCLK})]}{256}$$

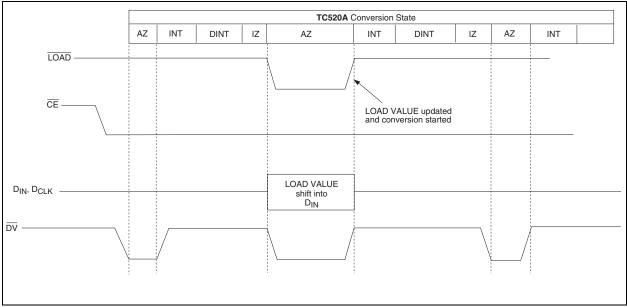

In this example, LOAD VALUE =  $128_{(10)} = 10$ H. Therefore, a LOAD VALUE of 10H is loaded into the TC520A. If the desired T<sub>INT</sub> was 100msec instead of 131msec, the LOAD VALUE would be 9EH, and so on. The TC520A LOAD VALUE must be initialized on power-up, and can be re-initialized as often as desired thereafter. This is accomplished by bringing the  $\overline{\text{LOAD}}$  input low while transmitting the appropriate LOAD VALUE to the TC520A as shown in Figure 4-1 and Figure 4-2.

# 4.4.5 POLLED VS. INTERRUPT OPERATION

The TC520A can be accessed at any time by the host processor. This makes operation in a polled environment especially easy since the most recently converted data is available to the processor as needed. The TC520A can also be used in an interrupt environment by connecting  $\overline{\text{DV}}$  to the  $\overline{\text{IRQ}}$  line of the processor. Since AZ is the first phase of a new conversion cycle, the most recently converted data will be available as soon as  $\overline{\text{DV}}$  goes low. If so desired, the interrupt service routine can also modify the LOAD VALUE during the  $\overline{\text{DV}}$  = low interval.

FIGURE 4-1: TC520 initialization & startup conversion timing relatioNships

#### 4.4.6 OPTO-ISOLATED APPLICATIONS

The 3 wire serial port of the TC520A can be optoisolated for applications requiring isolated data acquisition. The additional control lines ( $\overline{\text{LOAD}}$ ,  $\overline{\text{DV}}$ ,  $\overline{\text{READ}}$ ) are normally not needed in such applications, but can also be brought across the isolation barrier with the addition of a second isolator.

FIGURE 4-3: **Typical System Application** +5V V+ 16 6 OSC<sub>OUT</sub>  $C_{\mathsf{INT}}$ 1 INT V+ 10k Crystal 🗀 12 LOAD (LD 3 CAZ 7 OSCIN 8 READ (RD 4 BUF 3 CMPTR 100k CMPTR 10  $R_{INT}$ 11  $\mathsf{D}_{\mathsf{CLK}}$ <SK V<sub>IN</sub>+ 13 IN+ В В TC500 11 TC520A DIN  $\langle so \rangle$ 12 5 13 DV 5 .01 Α 9 10 SI  $D_{\mathsf{OUT}}$ 6 V<sub>IN</sub>-IN-CR-9 14 CE REF+  $\mathsf{C}_\mathsf{REF}$ 7 MCP1525 .01 CR+ 8 15 REF-GND GND 1 F <u>v</u> 2 5 COM -5V Analog Ground ± DGND (CE DV

#### 5.0 PACKAGING INFORMATION

## 5.1 Package Marking Information

Package marking information not available at this time.

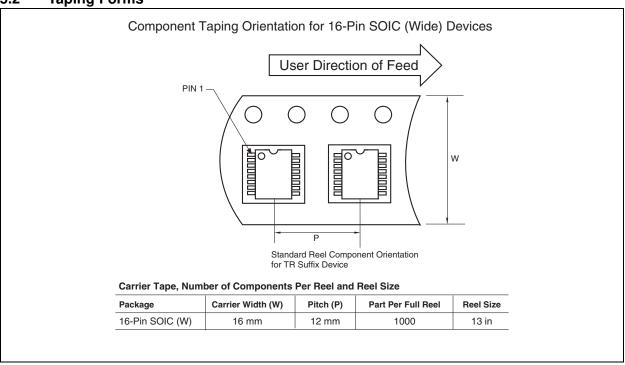

## 5.2 Taping Forms

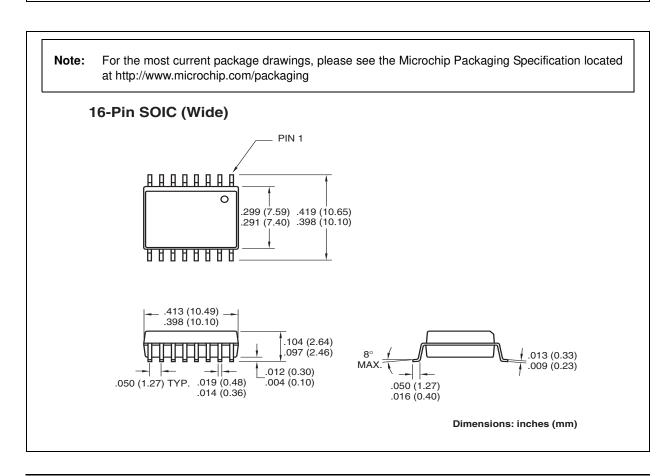

#### 5.3 Package Dimensions

For the most current package drawings, please see the Microchip Packaging Specification located Note: at http://www.microchip.com/packaging 14-Pin PDIP (Narrow) PIN 1 .260 (6.60) .240 (6.10) .310 (7.87) .770 (19.56) .290 (7.37) .745 (18.92) .200 (5.08) .140 (3.56) -.040 (1.02) -.020 (0.51) .015 (0.38) 3°MIN. .150 (3.81) .008 (0.20) .115 (2.92) .400 (10.16) .310 (7.87) .110 (2.79) .070 (1.78) .022 (0.56) .015 (0.38) .090 (2.29) .045 (1.14) Dimensions: inches (mm)

## 6.0 REVISION HISTORY

**Revision C (December 2012)**

Added a note to each package outline drawing.

## **SALES AND SUPPORT**

## Data Sheets

Products supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recommended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:

- Your local Microchip sales office

- 1. 2. The Microchip Worldwide Site (www.microchip.com)

Please specify which device, revision of silicon and Data Sheet (include Literature #) you are using.

#### **New Customer Notification System**

Register on our web site (www.microchip.com/cn) to receive the most current information on our products.

**NOTES:**

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our

knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data

Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, dsPIC, FlashFlex, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, PIC<sup>32</sup> logo, rfPIC, SST, SST Logo, SuperFlash and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Hampshire, HI-TECH C, Linear Active Thermistor, MTP, SEEVAL and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

Analog-for-the-Digital Age, Application Maestro, BodyCom, chipKIT, chipKIT logo, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, HI-TIDE, In-Circuit Serial Programming, ICSP, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, mTouch, Omniscient Code Generation, PICC, PICC-18, PICDEM, PICDEM.net, PICkit, PICtail, REAL ICE, rfLAB, Select Mode, SQI, Serial Quad I/O, Total Endurance, TSHARC, UniWinDriver, WiperLock, ZENA and Z-Scale are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

GestIC and ULPP are registered trademarks of Microchip Technology Germany II GmbH & Co. & KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2001-2012, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Printed on recycled paper.

ISBN: 9781620768211

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/

support

Web Address: www.microchip.com

**Atlanta**

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto

Mississauga, Ontario,

Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733

Fax: 61-2-9868-6755 China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Chongqing** Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300

Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Osaka** Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859 **Malaysia - Penang**

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7828

Tel: 886-7-213-7828 Fax: 886-7-330-9305

**Taiwan - Taipei** Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 **Denmark - Copenhagen**

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399

Fax: 31-416-690340 **Spain - Madrid** Tel: 34-91-708-08-90

Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

11/29/12