# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# High-Performance DrBLADE 6.6 mm x 4.5 mm x 0.6 mm

TDA21320

# Data Sheet

Revision 2.4, 2015-07-16

# Power Management and Multi Market

Edition 2015-07-1626 Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

| Revision History         |                                                  |  |  |  |  |  |  |

|--------------------------|--------------------------------------------------|--|--|--|--|--|--|

| Page or Item             | Subjects (major changes since previous revision) |  |  |  |  |  |  |

| Revision 2.4, 2015-07-16 |                                                  |  |  |  |  |  |  |

|                          | Package drawings figures 18 – 20 updated         |  |  |  |  |  |  |

|                          | Inserted chapter 10 (packaging information)      |  |  |  |  |  |  |

|                          |                                                  |  |  |  |  |  |  |

#### Trademarks of Infineon Technologies AG

AURIX<sup>™</sup>, BlueMoon<sup>™</sup>, C166<sup>™</sup>, CanPAK<sup>™</sup>, CIPOS<sup>™</sup>, CIPURSE<sup>™</sup>, COMNEON<sup>™</sup>, EconoPACK<sup>™</sup>, CoolMOS<sup>™</sup>, CoolSET<sup>™</sup>, CORECONTROL<sup>™</sup>, CROSSAVE<sup>™</sup>, DAVE<sup>™</sup>, EasyPIM<sup>™</sup>, EconoBRIDGE<sup>™</sup>, EconoDUAL<sup>™</sup>, EconoPIM<sup>™</sup>, EiceDRIVER<sup>™</sup>, eupec<sup>™</sup>, FCOS<sup>™</sup>, HITFET<sup>™</sup>, HybridPACK<sup>™</sup>, I<sup>2</sup>RF<sup>™</sup>, ISOFACE<sup>™</sup>, IsoPACK<sup>™</sup>, MIPAQ<sup>™</sup>, ModSTACK<sup>™</sup>, my-d<sup>™</sup>, NovalithIC<sup>™</sup>, OmniTune<sup>™</sup>, OptiMOS<sup>™</sup>, ORIGA<sup>™</sup>, PRIMARION<sup>™</sup>, PrimePACK<sup>™</sup>, PrimeSTACK<sup>™</sup>, PRO-SIL<sup>™</sup>, PROFET<sup>™</sup>, RASIC<sup>™</sup>, ReverSave<sup>™</sup>, SatRIC<sup>™</sup>, SIEGET<sup>™</sup>, SINDRION<sup>™</sup>, SIPMOS<sup>™</sup>, SMARTi<sup>™</sup>, SmartLEWIS<sup>™</sup>, SOLID FLASH<sup>™</sup>, TEMPFET<sup>™</sup>, thinQ!<sup>™</sup>, TRENCHSTOP<sup>™</sup>, TriCore<sup>™</sup>, X-GOLD<sup>™</sup>, X-PMU<sup>™</sup>, XMM<sup>™</sup>, XPOSYS<sup>™</sup>.

#### **Other Trademarks**

Advance Design System™ (ADS) of Agilent Technologies, AMBA™, ARM™, MULTI-ICE™, KEIL™, PRIMECELL™, REALVIEW™, THUMB™, µVision™ of ARM Limited, UK. AUTOSAR™ is licensed by AUTOSAR development partnership. Bluetooth™ of Bluetooth SIG Inc. CAT-iq™ of DECT Forum. COLOSSUS™, FirstGPS™ of Trimble Navigation Ltd. EMV™ of EMVCo, LLC (Visa Holdings Inc.). EPCOS™ of Epcos AG. FLEXGO<sup>™</sup> of Microsoft Corporation. FlexRay<sup>™</sup> is licensed by FlexRay Consortium. HYPERTERMINAL<sup>™</sup> of Hilgraeve Incorporated. IEC<sup>™</sup> of Commission Electrotechnique Internationale. IrDA<sup>™</sup> of Infrared Data Association Corporation. ISO™ of INTERNATIONAL ORGANIZATION FOR STANDARDIZATION. MATLAB™ of MathWorks, Inc. MAXIM™ of Maxim Integrated Products, Inc. MICROTEC<sup>™</sup>, NUCLEUS<sup>™</sup> of Mentor Graphics Corporation. Mifare<sup>™</sup> of NXP. MIPI<sup>™</sup> of MIPI Alliance, Inc. MIPS™ of MIPS Technologies, Inc., USA. muRata™ of MURATA MANUFACTURING CO., MICROWAVE OFFICE™ (MWO) of Applied Wave Research Inc., OmniVision™ of OmniVision Technologies, Inc. Openwave™ Openwave Systems Inc. RED HAT™ Red Hat, Inc. RFMD™ RF Micro Devices, Inc. SIRIUS™ of Sirius Satellite Radio Inc. SOLARIS™ of Sun Microsystems, Inc. SPANSION™ of Spansion LLC Ltd. Symbian™ of Symbian Software Limited. TAIYO YUDEN™ of Taiyo Yuden Co. TEAKLITE™ of CEVA, Inc. TEKTRONIX™ of Tektronix Inc. TOKO™ of TOKO KABUSHIKI KAISHA TA. UNIX™ of X/Open Company Limited. VERILOG™, PALLADIUM™ of Cadence Design Systems, Inc. VLYNQ™ of Texas Instruments Incorporated. VXWORKS<sup>™</sup>, WIND RIVER<sup>™</sup> of WIND RIVER SYSTEMS, INC. ZETEX<sup>™</sup> of Diodes Zetex Limited.

Last Trademarks Update 2010-10-26

TDA21320

## 1 Applications

- Desktop and Server Vcore and non-Vcore buck-converter

- Single Phase and Multiphase POL

- CPU/GPU Regulation in Notebook, Desktop Graphics Cards, DDR Memory, Graphic Memory

- High Power Density Voltage Regulator Modules (VRM).

## 2 Features

- Input voltage range +4.5 V to +16 V

- Maximum average current up to 60 A

- For synchronous Buck step down voltage applications

- Power MOSFETs rated 25 V for safe operation under all conditions

- Fast switching technology for improved performance at high switching frequencies (> 750 kHz)

- Up to 95.5% peak efficiency<sup>1</sup>

- Includes bootstrap diode

- Shoot through protection

- Max +8 V V<sub>GS</sub>, high-side and low-side MOSFET gate driving voltage

- Compatible to standard +3.3 V PWM controller integrated circuits

- Tri-state PWM input functionality

- Small package: LG-WIQFN-38-1 (6.6x4.5x0.6 mm<sup>3</sup>)

- RoHS compliant

- Integrated temperature sense

- Integrated current sense

#### Table 1 Product Identification

| Part Number | Temp Range     | Package                                      | Marking  |

|-------------|----------------|----------------------------------------------|----------|

| TDA21320    | -25°C to 125°C | LG-WIQFN-38-1 (6.6x4.5x0.6 mm <sup>3</sup> ) | TDA21320 |

| <b>(i)</b> | Data Matrix Code                      |

|------------|---------------------------------------|

| TDA21320   | Production Site,<br>Lot and Date Code |

Figure 1 Picture of the Product

$<sup>^{1}</sup>$  f<sub>sw</sub> = 429 kHz, V<sub>DRV</sub> = 5V, Vin = 12V, Vout = 1.8V, 5 phases, no heatsink, no airflow

**TDA21320**

Description

#### 3 Description

#### 3.1 Pinout

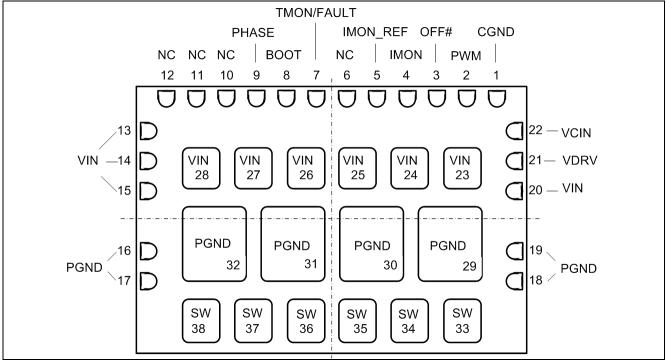

| Figure 2  | Pinout, Numbering and Name of Pins (transparent top | view) |

|-----------|-----------------------------------------------------|-------|

| i igaio z | i nout, numbering and nume of time (numeration top  | ••••• |

| Table 2 | I/O Signals |          |              |                                                                                                                              |

|---------|-------------|----------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Name        | Pin Type | Buffer Type  | Function                                                                                                                     |

| 2       | PWM         | I/O      | +3.3 V logic | PWM drive logic input, Status output for VCIN                                                                                |

|         |             |          |              | The tri-state PWM input is compatible with 3.3 V.                                                                            |

| 3       | OFF#        | 1        | +3.3 V logic | Deactivates LS-MOSFET                                                                                                        |

|         |             |          |              | Pull low to prevent LS-FET turn-on. Leave open if not used. (If traced out in noisy layout it may require external pull up.) |

| 4       | IMON        | 0        | Analog       | Load current Sensing                                                                                                         |

|         |             |          |              | Provides a voltage proportional to the high/low-side MOSFET currents; Leave open if not used.                                |

| 5       | IMONREF     | 0        | Analog       | Load current Sensing                                                                                                         |

|         |             |          |              | Reference to pin 4; Leave open if not used.                                                                                  |

| 7       | TMON/FAULT  | 0        | Analog/      | Thermal Sensing / Fault Pin                                                                                                  |

|         |             |          | Digital      | Temperature reporting, fault signaling by logic "H"; Status output of VDRV, Leave open if not used.                          |

| 8       | BOOT        | 1        | Analog       | Bootstrap voltage pin                                                                                                        |

|         |             |          |              | Connect to BOOT capacitor                                                                                                    |

| 9       | PHASE       | 1        | Analog       | Switch node input                                                                                                            |

|         |             |          |              | Internally connected to SW pins, Connect to BOOT<br>capacitor as reference pin for boot voltage                              |

| 33-38   | SW          | 0        | Analog       | Switch node output                                                                                                           |

| (pads)  |             |          |              | High current output switching node                                                                                           |

Description

| Table 3      | Power S | upply    |                                                                                 |

|--------------|---------|----------|---------------------------------------------------------------------------------|

| Pin No.      | Name    | Pin Type | Function                                                                        |

| 13 – 15, 20, | VIN     | POWER    | Input voltage                                                                   |

| 23-28 (pads) |         |          | Converter input voltage (connected to drain of the high-side MOSFET and driver) |

| 21           | VDRV    | POWER    | MOSFET gate drive supply voltage                                                |

|              |         |          | High and low-side gate drive                                                    |

| 22           | VCIN    | POWER    | Driver logic supply voltage                                                     |

|              |         |          | bias voltage for the internal logic                                             |

#### Table 4 Ground Pins

| Pin No.      | Name | Pin Type | Function                                                                                      |

|--------------|------|----------|-----------------------------------------------------------------------------------------------|

| 1            | CGND | GND      | Control signal ground                                                                         |

|              |      |          | Should be connected to local PGND externally, preferably by vias to GND plane                 |

| 16 – 19,     | PGND | GND      | Power ground                                                                                  |

| 29-32 (pads) |      |          | All these pins must be connected to the power GND plane through multiple low inductance vias. |

#### Table 5Not Connected

| Pin No.       | Name | Pin Type | Function                               |  |  |  |  |  |

|---------------|------|----------|----------------------------------------|--|--|--|--|--|

| 6, 10, 11, 12 | NC   | -        | No internal connection                 |  |  |  |  |  |

|               |      |          | Leave pin floating, tie to VIN or GND. |  |  |  |  |  |

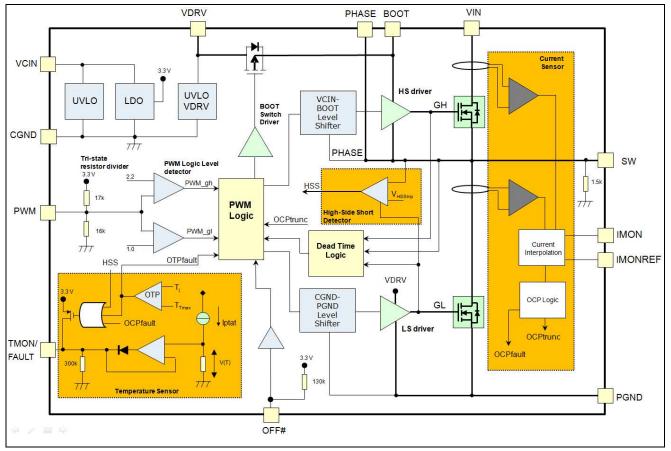

#### 3.2 General Description

The Infineon TDA21320 is a multichip module that incorporates Infineon's premier MOSFET technology into a single high-side and a single low-side MOSFET. This is coupled with a robust, high performance, high switching frequency gate driver on a single 38 pin LG-WIQFN-38-1 (6.6x4.5x0.6 mm<sup>3</sup>) package. The optimized gate timing enables significant light load efficiency improvements over discrete solutions. State of the art MOSFET technology provides exceptional performance at full and light load.

When combined with Infineon's Primarion<sup>™</sup> Controller Family of Digital Multi-phase Controllers, the TDA21320 forms a complete core-voltage regulator solution for advanced micro and graphics processors as well as point-of-load applications. The device package height is 0.6 mm. It is an excellent choice for applications with critical height limitations and has reduced thermal impedance from junction to top case compared to DrMOS, allowing for top side cooling.

The power density for transmitted power of this approach is approximately 50 W within a 28 mm<sup>2</sup> area.

Attention: GH and GL are not accessible on this package, but are mentioned for clarity in this block diagram.

# 4 Electrical Specification

## 4.1 Absolute Maximum Ratings

#### Note: $T_A = 25 \circ C$

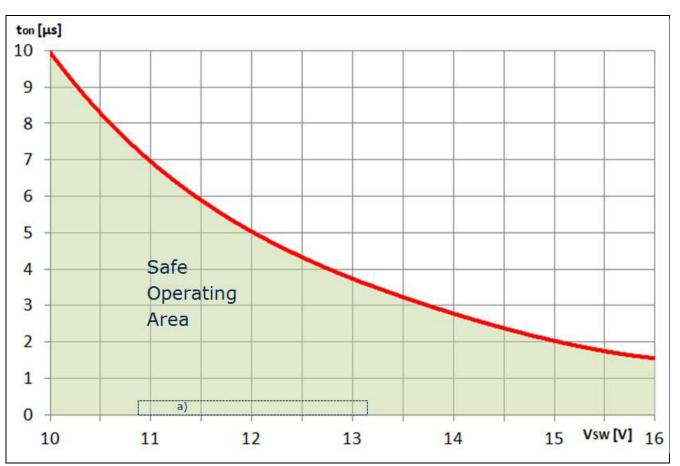

Stresses above those listed in Table 6 "Absolute Maximum Ratings" and Figure 4 "Repetitive Voltage Stress at Phase Node - Safe Operating Area" may cause permanent damage to the device. These are absolute stress ratings only and operation of the device is not implied or recommended at these or any other conditions in excess of those given in the operational sections of this specification. Exposure over values of the recommended ratings (Table 8) for extended periods may adversely affect the operation and reliability of the device.

#### Table 6 Absolute Maximum Ratings

| Parameter                        | Symbol                       |                     | Value | S               | Unit | Note / Test Condition                                                                                  |  |

|----------------------------------|------------------------------|---------------------|-------|-----------------|------|--------------------------------------------------------------------------------------------------------|--|

|                                  |                              | Min.                | Тур.  | Max.            |      |                                                                                                        |  |

| Frequency of the PWM input       | f <sub>sw</sub>              | 0.01<br>(in<br>CCM) | _     | 1.2             | MHz  | rated current sense accuracy<br>between 100 kHz and 800 kHz                                            |  |

| Maximum average load current     | I <sub>OUT</sub>             | -                   | _     | 60              | А    | -                                                                                                      |  |

| Input Voltage                    | V <sub>IN</sub> (DC)         | -0.30               | _     | 18              | V    | I                                                                                                      |  |

| Logic supply voltage             | V <sub>CIN</sub> (DC)        | -0.30               | -     | 9               | V    | -                                                                                                      |  |

| High and low-side driver voltage | V <sub>DRV</sub> (DC)        | -0.30               | -     | 9               | ۷    | -                                                                                                      |  |

| Switch node voltage              | V <sub>SW</sub> (DC)         | -1                  | _     | 18              | ٧    | _                                                                                                      |  |

|                                  | V <sub>SW</sub> (AC)         | -10 <sup>2</sup>    | _     | 25 <sup>2</sup> | V    | _                                                                                                      |  |

| PHASE voltage pin (9)            | V <sub>PHASE</sub> (DC)      | -1                  | _     | 18              | ٧    | _                                                                                                      |  |

|                                  | V <sub>PHASE</sub> (AC)      | -10 <sup>2</sup>    | _     | 25 <sup>2</sup> | V    | _                                                                                                      |  |

| BOOT voltage                     | V <sub>BOOT</sub> (DC)       | -0.3                | _     | 25              | V    | _                                                                                                      |  |

|                                  | V <sub>BOOT</sub> (AC)       | -                   | _     | 30 <sup>2</sup> | V    | _                                                                                                      |  |

|                                  | V <sub>BOOT-PHASE</sub> (DC) | -0.3                | _     | 9               | V    | -                                                                                                      |  |

| OFF# voltage                     | V <sub>OFF#</sub>            | -0.3                | -     | 4               | V    | Maximum value valid for<br>operation up to 24h<br>accumulated over lifetime in<br>temperature range of |  |

| PWM voltage                      | V <sub>PWM</sub>             | -0.3                | -     | 4               | V    | -25°C $\leq$ T <sub>j</sub> $\leq$ 125°C.<br>Else the maximum value is 3.6V.                           |  |

| TMON/FAULT                       | VTMON/FAULT                  | -0.3                | _     | 3.6             | V    | _                                                                                                      |  |

| IMON                             | VIMON                        | -0.3                | _     | 3.6             | V    | _                                                                                                      |  |

| IMONREF                          | VIMONREF                     | -0.3                | _     | 3.6             | V    | -                                                                                                      |  |

| Junction temperature             | T <sub>Jmax</sub>            | -40                 | _     | 150             | °C   | 1                                                                                                      |  |

| Storage temperature              | T <sub>STG</sub>             | -55                 | _     | 150             | °C   | -                                                                                                      |  |

Note: All rated voltages are relative to voltages on the CGND and PGND pins unless otherwise specified.

<sup>2</sup> AC is limited to 10 ns

Data Sheet

**Electrical Specification**

#### Figure 4 Repetitive Voltage Stress at Phase Node - Safe Operating Area

Note:  $t_{on}$  refers to the on-time of the HS-MOSFET. For input voltages below 10 V no limits on the duration of  $t_{on}$  need to be applied.

Information: a) - Area of typical computing applications with 12 V input supply voltage

**Electrical Specification**

## 4.2 Thermal Characteristics

#### Table 7 Thermal Characteristics

| Parameter                                                                                                      | Symbol                  |      | Values | ;    | Unit | Note / Test     |

|----------------------------------------------------------------------------------------------------------------|-------------------------|------|--------|------|------|-----------------|

|                                                                                                                |                         | Min. | Тур.   | Max. |      | Condition       |

| Thermal resistance to case (soldering point)                                                                   | $\theta_{JC}$           | -    | 3.5    | _    | K/W  | -               |

| Thermal resistance to top of package                                                                           | $\theta_{\text{JCtop}}$ | -    | 3.7    | _    |      | -               |

| Thermal resistance to ambient                                                                                  | θ <sub>JA</sub>         | -    | 14     | -    |      | Still air       |

| $(P_{loss} = 4.5 \text{ W}, T_A = 70 \text{ °C}, 8 \text{ layer server}$<br>board with 2 oz copper per layer ) | -                       | _    | 10     | _    |      | 200 lfm airflow |

| board with 2 oz copper per layer )                                                                             |                         | _    | 8      | -    |      | 300 lfm airflow |

## 4.3 Recommended Operating Conditions and Electrical Characteristics<sup>3</sup>

Note:  $V_{IN} = 12V$ ,  $V_{DRV} = V_{CIN} = 5 V$ ,  $T_A = 25 \ ^{\circ}C$  unless otherwise specified

| Parameter             | Symbol           | Values |      |      | Unit | Note / Test Condition                            |

|-----------------------|------------------|--------|------|------|------|--------------------------------------------------|

|                       |                  | Min.   | Тур. | Max. |      |                                                  |

| Input voltage         | V <sub>IN</sub>  | 4.5    | -    | 16   | V    | -                                                |

| MOSFET driver voltage | V <sub>DRV</sub> | 4.5    | _    | 8    | V    | -                                                |

| Logic supply voltage  | V <sub>CIN</sub> | 4.5    | _    | 8    |      | -                                                |

| Frequency of the PWM  | f <sub>sw</sub>  | 100    | -    | 800  | kHz  | CCM operation with stated current sense accuracy |

| Junction temperature  | T <sub>iOP</sub> | -25    | -    | +125 | °C   | -                                                |

#### Table 8 Recommended Operating Conditions

<sup>&</sup>lt;sup>3</sup> Exposure over values of the recommended ratings for extended periods may adversely affect operation and reliability of the device. Min/Max values are based on empirical Cpk.

| Parameter               | Symbol                             |      | Value | s    | Unit | Note / Test Condition                                                                                                                                                                                                                                   |  |  |  |  |

|-------------------------|------------------------------------|------|-------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                         | _                                  | Min. | Тур.  | Max. |      |                                                                                                                                                                                                                                                         |  |  |  |  |

| UVLO VCIN<br>rising     | V <sub>UVLO1_R</sub>               | 3.0  | -     | 4.0  | V    | Driver enable threshold; above threshold driver is active,<br>driver responds to PWM input when UVLO VDRV and<br>UVLO BOOT are enabled, TMON/FAULT reports driver<br>temperature when UVLO VDRV is enabled                                              |  |  |  |  |

| UVLO VCIN<br>falling    | $V_{\rm UVLO1_F}$                  | 2.6  | -     | 3.6  |      | Driver disable threshold; below threshold driver is inactive, PWM and TMON/FAULT held low by pull-down resistors                                                                                                                                        |  |  |  |  |

| UVLO VDRV<br>rising     | V <sub>UVLO2_R</sub>               | 4.16 | 4.25  | 4.34 | V    | GL, GH and TMON/FAULT enable threshold; when UVLO<br>VCIN is enabled then: above threshold GL is enabled, GH<br>depends on UVLO BOOT, TMON/FAULT is released to<br>report driver temperature                                                            |  |  |  |  |

| UVLO VDRV<br>falling    | V <sub>UVLO2_F</sub>               | 3.7  | 3.8   | 3.9  |      | GL, GH and TMON/FAULT disable threshold; when UVLO VCIN is enabled: below threshold after 3 consecutive cycles or 15 $\mu$ s (typ.) the driver outputs GL/GH are disabled, TMON/FAULT stops temperature reporting and is held low by pull-down resistor |  |  |  |  |

| UVLO BOOT<br>rising     | V <sub>UVLOboot_R</sub>            | 3.88 | 4.05  | 4.22 | V    | $V_{\text{BOOT}}\text{-}V_{\text{SW}}$ rising, GH enable threshold; when UVLO VCIN and UVLO VDRV are active: above threshold GH responds to PWM                                                                                                         |  |  |  |  |

| UVLO BOOT<br>falling    | V <sub>UVLOboot_F</sub>            | 3.5  | 3.63  | 3.76 |      | V <sub>BOOT</sub> -V <sub>SW</sub> falling, GL/GH disable threshold; when UVLO<br>VCIN and UVLO VDRV are enabled: below threshold<br>counter starts, after 3 consecutive PWM cycles driver<br>outputs are disabled                                      |  |  |  |  |

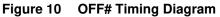

| Driver current          | I <sub>VDRV_600kHz</sub>           | 1    | 27    | ١    | mA   | OFF# = 3.3 V, <i>f</i> <sub>SW</sub> = 600 kHz                                                                                                                                                                                                          |  |  |  |  |

|                         | I <sub>VDRV_1MHz</sub>             | 1    | 44    | Ι    |      | OFF# = 3.3 V, <i>f</i> <sub>SW</sub> = 1 MHz                                                                                                                                                                                                            |  |  |  |  |

| IC current<br>(control) | I <sub>VCIN_O</sub>                | Ι    | 1.0   | Ι    | mA   | OFF# = 3.3 V, PWM = Open for > 19 $\mu$ s (typ.)                                                                                                                                                                                                        |  |  |  |  |

| IC quiescent            | I <sub>CIN</sub> +I <sub>DRV</sub> | _    | 1.2   | -    |      |                                                                                                                                                                                                                                                         |  |  |  |  |

| Pre-Bias at<br>SW       | V <sub>SW_0</sub>                  | _    | 120   | 160  | mV   | PWM in Tri-state (V <sub>PWM_S</sub> ), VCIN = VDRV = 5V, internal pull-down resistor 1.5 k $\Omega$                                                                                                                                                    |  |  |  |  |

#### Table 9Voltage Supply And Biasing Current

#### Table 10Current Sense

| Parameter             |                                                                                       | Symbol              | Values |      | Unit | Note / Test Condition |                                                                                                                                      |                                                  |  |  |

|-----------------------|---------------------------------------------------------------------------------------|---------------------|--------|------|------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|--|

|                       |                                                                                       |                     | Min.   | Тур. | Max. |                       |                                                                                                                                      |                                                  |  |  |

| IMON                  | Voltage Range                                                                         | V <sub>IMON</sub>   | 0.8    | _    | 2.2  | V                     | IMONREF is a current mirror output serving<br>as unfiltered reference node. At IMON a<br>filtered voltage signal proportional to the |                                                  |  |  |

| IMONREF               | IMON gain resistor range                                                              |                     | 0.2    | -    | 1.0  | kΩ                    |                                                                                                                                      |                                                  |  |  |

|                       | Current sense a <sub>CS</sub> - 6.67<br>gain <sup>4</sup>                             |                     |        |      | -    | μA/A                  | current is provided. It tracks the average value of IMONREF.                                                                         |                                                  |  |  |

|                       | Leakage current                                                                       | I <sub>Leak</sub>   | -2     | 0    | 2    | μA                    | $I_D = 0$ , $V_{CM} = 1.5$ , PWM in tri-state                                                                                        |                                                  |  |  |

| Current<br>Monitoring | Zero current offset                                                                   | I <sub>Offset</sub> | -3     | 0    | 3    | μA                    | Corresponds to 2.25 mV at 5 mV/A $(R_{IMONREF} = 750\Omega)$ , device in regulation                                                  |                                                  |  |  |

|                       | Accuracy at 25 °C<br>125 °C<br>$V_{DRV} = 5 V \pm 10 \%$<br>$V_{CIN} = 5 V \pm 10 \%$ | a11                 | -3     | _    | 3    | %                     | for 45 A < lout < $I_{OCPtrip}$                                                                                                      | tested at 25 A,<br>other guaranteed<br>by design |  |  |

|                       |                                                                                       | a12                 | -2.5   | _    | 2.5  | %                     | for 25 A $\leq$ lout $\leq$ 45 A                                                                                                     |                                                  |  |  |

|                       |                                                                                       | a13                 | -0.5   | _    | 0.5  | А                     | for -25 < lout < 25 A                                                                                                                |                                                  |  |  |

|                       |                                                                                       | a14                 | -20    | _    | 20   | %                     | for -50 A $\leq$ lout $\leq$ -25 A                                                                                                   |                                                  |  |  |

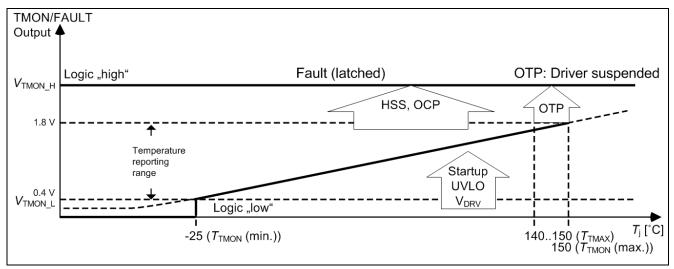

## Table 11 Temperature Sense

| Parameter                         |                                                                                     | Symbol                       | Values |      | Unit | Note / Test Condition |                                                                                      |  |  |

|-----------------------------------|-------------------------------------------------------------------------------------|------------------------------|--------|------|------|-----------------------|--------------------------------------------------------------------------------------|--|--|

|                                   |                                                                                     |                              | Min.   | Тур. | Max. |                       |                                                                                      |  |  |

| Temp.<br>Sense<br>and<br>Accuracy | Temp. FAULT                                                                         | T <sub>TMAX</sub>            | 140    | 145  | 150  | °C                    | Temperature monitors driver junction.                                                |  |  |

|                                   | Output high                                                                         | $V_{\text{TMON}_{\text{H}}}$ | 2.6    | _    | _    | V                     | Circuit reports temperatures to -25 °C                                               |  |  |

|                                   | Output monitor                                                                      | V <sub>TMON</sub>            | 0.4    | _    | 1.8  |                       | accurately (0.4V). The maximum temperature reported is $T_{TMAX}$ . Above $T_{TMAX}$ |  |  |

|                                   | Fault delay <sup>5</sup>                                                            | t <sub>TMONdeg</sub>         | -      | 3    | _    | μs                    | a logic 'H' is asserted to indicate a fault                                          |  |  |

|                                   | Temp. range <sup>5</sup>                                                            | T <sub>TMON</sub>            | -25    | _    | 150  | °C                    | (latched). At OTP fault PWM input is                                                 |  |  |

|                                   | Temp. coefficient <sup>5</sup>                                                      | TC                           | -      | 8    | _    | mV/K                  | suspended and driver is being set to tri-state mode until VCIN and/or VDRV           |  |  |

|                                   | Nominal                                                                             | V <sub>25C</sub>             | -      | 800  | _    | mV                    | have been re-cycled.                                                                 |  |  |

|                                   | Accuracy at -25 °C<br>125 °C (tested<br>at 25 °C, other<br>guaranteed by<br>design) | a <sub>TMON</sub>            | -4     | -    | 4    | К                     | unspecified below -25 °C                                                             |  |  |

<sup>&</sup>lt;sup>4</sup> Guaranteed by design

<sup>&</sup>lt;sup>5</sup> Guaranteed by design

| Parameter |                                        | Symbol                 | Values |      |      | Unit | Note / Test Condition                                                                                                           |  |

|-----------|----------------------------------------|------------------------|--------|------|------|------|---------------------------------------------------------------------------------------------------------------------------------|--|

|           |                                        |                        | Min.   | Тур. | Max. |      |                                                                                                                                 |  |

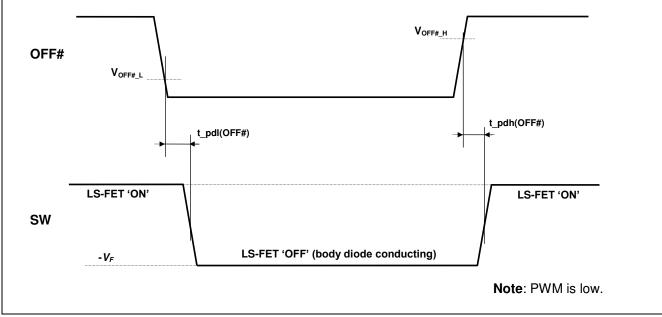

| OFF#      | Input low                              | V <sub>OFF#_L</sub>    | -      | _    | 0.8  | V    | V <sub>OFF#</sub> falling                                                                                                       |  |

|           | Input high                             | V <sub>OFF#_H</sub>    | 2.0    | -    | -    |      | V <sub>OFF#</sub> rising                                                                                                        |  |

| PWM       | Input low                              | V <sub>PWM_L</sub>     | -      | _    | 0.8  | V    | $V_{\rm PWM}$ falling                                                                                                           |  |

|           | Input high                             | V <sub>PWM_H</sub>     | 2.4    | _    | -    |      | $V_{PWM}$ rising                                                                                                                |  |

|           | Input resistance                       | R <sub>IN-PWM</sub>    | 6      | _    | 10   | kΩ   | $V_{PWM} = 1 \text{ V}$                                                                                                         |  |

|           | Open voltage                           | V <sub>PWM_O</sub>     | -      | 1.6  | -    | V    | V <sub>PWM_O</sub>                                                                                                              |  |

|           | Tri-state shutdown window <sup>6</sup> |                        | 1.2    | -    | 2.0  |      | _                                                                                                                               |  |

|           | Min pulse width <sup>5</sup>           | t <sub>PWMdetect</sub> | 5      | _    | 10   | ns   | Minimum pulse width to detect PWM pulse                                                                                         |  |

|           | Min pulse time <sup>5</sup>            | t <sub>PWMmin</sub>    | -      | 30   | -    | ns   | PWM pulses shorter than t <sub>PWMmin</sub> will be extended to t <sub>PWMmin</sub>                                             |  |

| OCP       | Overcurrent<br>Protection              | I <sub>OCPtrip</sub>   | 68     | 75   | 82   | A    | Duty cycle limitation at I <sub>OCPtrip</sub> , fault asserted and latched after 10 truncated consecutive switching cycles      |  |

| HSS       | High-Side-Short<br>Protection          | V <sub>HSStrip</sub>   | -      | 0.83 | -    | V    | Voltage tested at phase node during LS-MOSFET on-time. If voltage exceeds $V_{\text{HSStrip}}$ , fault is asserted and latched. |  |

#### Table 12 Other Logic Functions, Inputs/Outputs And Thresholds

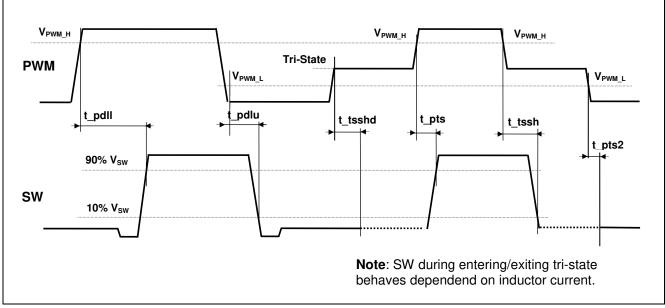

#### Table 13 Timing Characteristics <sup>7</sup>

| Parameter                                     | Symbol     |      | Values |      | Unit | Note / Test Condition                                                  |

|-----------------------------------------------|------------|------|--------|------|------|------------------------------------------------------------------------|

|                                               |            | Min. | Тур.   | Max. |      |                                                                        |

| PWM tri-state to SW falling delay             | t_pts2     | -    | 16     | -    | ns   | V <sub>OUT</sub> prebiased at 1 V,<br>other conditions as for<br>t_pts |

| PWM tri-state to SW rising delay              | t_pts      | _    | 19     | -    | ns   | $I_{LOAD} = 0,$                                                        |

| PHASE Shutdown Hold-Off time from<br>PWM low  | t_tsshd    | -    | 41     | -    |      | VDRV = VCIN = 5 V,<br>VIN = 12 V,                                      |

| PHASE Shutdown Hold-Off time from<br>PWM high | t_tssh     | -    | 45     | -    |      | fsw = 600 kHz                                                          |

| PWM to SW Turn-off propagation delay          | t_pdlu     | _    | 31     | -    |      |                                                                        |

| PWM to SW Turn-on propagation delay           | t_pdll     | _    | 21     | -    |      |                                                                        |

| OFF# Turn-off propagation delay falling       | t_pdl_OFF# | _    | 17     | -    | ns   |                                                                        |

| OFF# Turn-on propagation delay rising         | t_pdh_OFF# | _    | 25     | _    |      |                                                                        |

Corresponding diagrams can be found under section "Gate Driver Timing Diagram".

<sup>&</sup>lt;sup>6</sup> Maximum voltage range for tri-state

<sup>&</sup>lt;sup>7</sup>All timing data are guaranteed by design

The TDA21320 features a power stage with MOSFET driver. Temperature and current are being monitored. Data and various fault conditions can be reported to the controller.

The power MOSFETs are optimized for 5 V gate drive enabling excellent high load and light load efficiency. The gate driver is a robust high-performance driver rated at the switching node for DC voltages ranging from -1 V to +18 V.

## 5.1 Driver Characteristics

The gate driver has 2 voltage inputs, VCIN and VDRV. VCIN is the 5 V logic supply for the driver. VDRV sets the driving voltage for the high-side and low-side MOSFETs. The reference for the gate driver control circuit (VCIN) is CGND. To decouple the sensitive control circuitry (logic supply) from a noisy environment a ceramic capacitor must be placed between VCIN and CGND close to the pins. VDRV needs also to be decoupled using a ceramic capacitor (MLCC) between VDRV and PGND in close proximity to the pins. PGND serves as reference for the power circuitry including the driver output stage.

## 5.2 Power-Up Sequence

Without the logic supply VCIN the device remains off. PWM is held low by an internal pull down resistor. PWM information cannot be fed to the driver. VCIN supplies power to the driver logic. With the presence of VCIN on power-up of the gate drive voltage VDRV, the driver and the PWM input will be enabled, the unforced PWM level will be within its tri-state window. This signals that the driver supply voltages have cleared their respective UVLO thresholds. TMON/FAULT reports temperature. The PWM controller is expected to wait for this to happen before initiating PWM signals to start up the system.

Note that with VCIN and VDRV present, the switching node can rise up to  $V_{SW_0}$  with PWM in tri-state condition.

## 5.3 Inputs to the Internal Control Circuits

**PWM** is the control input to the IC from an external PWM controller and is compatible with 3.3 V logic. The PWM input has tri-state functionality. When the voltage remains in the specified PWM-shutdown-window for at least the PWM-shutdown-holdoff time t\_tsshd, the operation will be suspended by keeping both MOSFET gate outputs low. Once left open, the pin is held internally at a tri-state level of  $V_{PWM_O}$ . The PWM signal must prevail for at least  $t_{PWMmin}$  to initiate a response from the driver.

The PWM threshold voltages VPMW\_O, VPWM\_H, VPWM\_L do not vary over the wide range of VCIN supply voltages (4.5 V to 8 V).

The **OFF#** pin provides a means to keep the low-side MOSFET disabled regardless of the PWM signal. It is an active low signal. An internal pull up resistor ensures regular operation when the pin is not used.

When pulled low, the low-side MOSFET is kept in off-state. In multiphase systems the OFF# pins of all phases may be connected together. One controller output is then able to toggle the LS-FET operation mode.

Data Sheet

| Table 14 FWW and OTT # FITT unctionality, Driver Outputs |                  |                  |                  |  |  |  |  |  |

|----------------------------------------------------------|------------------|------------------|------------------|--|--|--|--|--|

| PWM logic level                                          | OFF# logic level | Gate HS-FET (GH) | Gate LS-FET (GL) |  |  |  |  |  |

| High                                                     |                  | High             |                  |  |  |  |  |  |

| Open (Tri-state: left floating, or high impedance)       | Any              |                  | Low              |  |  |  |  |  |

| Low                                                      | Low              | Low              |                  |  |  |  |  |  |

| Low                                                      | High or open     |                  | High             |  |  |  |  |  |

#### Table 14 PWM and OFF# Pin Functionality, Driver Outputs

### 5.4 Monitoring and Protection Circuits

The TDA21320 is designed with the various protection functions. Most of these protection features require a PWM controller that reacts properly on the assertion of a fault signal at TMON/FAULT to shutdown the circuit. Fault assertion is latched and is being removed when VCIN and/or VDRV will be re-cycled. A reported fault is always indicating a critical condition with high stress levels on the device and/or load that requires immediate action in form of shutdown to prevent imminent catastrophic failure.

In multiphase regulators the TMON/FAULT outputs of the power stages will have to be connected together. The TMON/FAULT output voltage follows the highest voltage output of any phase connected. The pull-down capability of any TMON/FAULT output is weak so that a fault assertion of any phase will always override other phase outputs.

## 5.4.1 High-Side Short Protection (HSS)

The voltage at the switching node is being monitored during the LS-MOSFET being driven in on-state. When during that time the switching node voltage exceeds a critical threshold of V<sub>HSStrip</sub> the HSS fault is being asserted by pulling TMON/FAULT to 'high'. The PWM controller has to shut down the power stage to prevent catastrophic failure. TMON/FAULT is latched and will be released when VCIN and/or VDRV will be re-cycled.

HSS can lead to a very sudden current rise that can impact voltage potentials in and in vicinity of the power device so that early reset events could potentially occur. Therefore, it is important to always have the system controller terminate the power supply as soon as a critical event has been reported by the power stage.

### 5.4.2 Thermal Protection and Temperature Monitoring

The driver monitors and reports its temperature. In multiphase systems with connected TMON/FAULT pins only the highest temperature of any of the connected phases will be reported. The PWM controller is supposed to react on the reported temperature with power throttling commands to the load. If the system fails to respond and the temperature continues to rise to a value of  $T_{TMAX}$  for at least  $t_{TMONdeg}$ , TMON/FAULT is being pulled high to report an Over-Temperature Fault (OTP). TMON/FAULT is latched and will be released when VCIN and/or VDRV will be recycled. At OTP fault the driver outputs will be deactivated until VCIN and/or VDRV have been re-cycled.

The PWM controller is expected to shut down the power stage to prevent catastrophic failure.

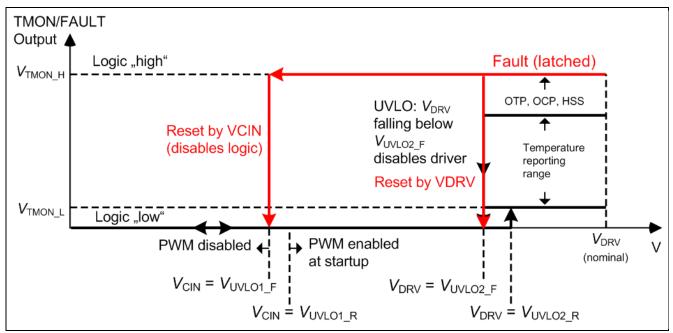

Figure 5 Thermal monitoring and protection

Note: Temperature reporting below  $T_{TMON\_min}$  occurs with limited accuracy.  $T_{TMON\_min}$  is being defined by the corresponding controller detection threshold for logic 'L'.

The reported voltage as function of temperature follows this equation:

$$V_{TMON} = 0.6V + 8\frac{mV}{K} \cdot T(^{\circ}C)$$

<sup>(1)</sup>

#### 5.4.3 Undervoltage Lockout (UVLO)

The power stage should not be operated when its supply voltages are out of the nominal range. UVLO conditions occurring during power up and power down must be accommodated by proper sequencing. An UVLO condition under normal operation can indicate a problem with the driver voltage and must be handled with a shutdown to prevent damage to the power stage.

#### TDA21320

#### **Theory of Operation**

A primary UVLO circuit monitors VCIN. Only after having VCIN in regulation range the UVLO monitoring on VDRV takes place. During startup UVLO on VDRV is being signaled by keeping TMON/FAULT low.

With VCIN being below  $V_{UVLO1_R}$  at startup the driver is inactive, PWM and TMON/FAULT are held low.

When VCIN exceeds  $V_{UVLO1_R}$  the driver becomes active, pin PWM is being enabled as input and held internally at its tri-state level of  $V_{PWM_O}$ . Then VDRV determines TMON/FAULT:

Below  $V_{UVLO2_R}$  TMON/FAULT remains 'low'.

- When VDRV exceeds  $V_{UVLO2_R}$  TMON/FAULT is released and reports temperature.

- When VDRV falls below V<sub>UVLO2\_F</sub> for 3 consecutive cycles or 15 µs (typ.) TMON/FAULT is being pulled 'low'.

If at startup VCIN and/or VDRV are below their respective undervoltage lockout rising thresholds ( $V_{UVLO1_R}$ ,  $V_{UVLO2_R}$ ) GL and GH remain disabled. Once these thresholds have been cleared, the driver provides GL output signal following PWM. When the voltage  $V_{BOOT}$ - $V_{SW}$  has been exceeding  $V_{UVLOboot_R}$ , GH is being released to respond to PWM.

When VCIN and/or VDRV are falling below their respective undervoltage lockout falling thresholds ( $V_{UVLO1_F}$ ,  $V_{UVLO2_F}$ ) the driver disables its outputs GH and GL to drive the MOSFETs.

When the voltage  $V_{BOOT}$ - $V_{SW}$  has been falling below  $V_{UVLOboot_F}$  for three consecutive PWM cycles the driver will be disabled.

Figure 6 Output Signal at TMON/Fault

#### 5.4.4 BOOT - Undervoltage Protection (UVLO<sub>BOOT</sub>)

The voltage between BOOT and SW pins (boot-voltage) is being monitored when VCIN and VDRV have been clearing their respective UVLO conditions. At startup, the LS-MOSFET gate (GL) is enabled to respond to the PWM signal when VDRV is being active. If the voltage at the boot capacitor is insufficient to clear the V<sub>UVLOboot\_R</sub> threshold, GH remains disabled until the active LS-MOSFET has forced sufficient charge onto the boot capacitor during the PWM "L" state. When the boot capacitor voltage exceeds V<sub>UVLOboot\_R</sub>, the GH output for the gate drive of the HS-MOSFET is enabled.

At startup and anytime when the boot voltage is below  $V_{UVLOboot_F}$  an internal boot-error flag is set. The boot-error flag is being reset when the boot voltage exceeded  $V_{UVLOboot_R}$ .

If during the falling edge of the PWM (from 'H' to tri-state or from 'H' to 'L') the UVLO<sub>BOOT</sub> error flag is set, an internal counter increases by one. When the counter reaches three, the driver outputs GH/GL are being disabled (i.e. latched in tri-state), regardless of the PWM input.

To reset the driver and resume operation, the PWM input has to be held in tri-state for 19  $\mu$ s (typ). After that, the UVLO<sub>BOOT</sub> counter is being reset to zero and the driver performs a startup sequence as described before in order to bring sufficient charge onto the boot capacitor.

The UVLO<sub>BOOT</sub> counter is also being reset to zero whenever during the falling edge of the PWM the UVLO<sub>BOOT</sub> error flag was not set, i.e. the error condition had been temporary for less than three consecutive instances of the falling edge of the PWM signal.

To prevent depletion of the boot capacitor during extended time in tri-state during regular operation, a boot refresh circuit will engage after 19  $\mu$ s (typ) in consecutive tristate condition when the voltage at the boot capacitor has fallen below V<sub>UVLOboot\_F</sub>. This circuit remains active until V<sub>UVLOboot\_R</sub> has been reached or the PWM input signal leaves the region of tri-state. The boot refresh circuit is powered by V<sub>IN</sub>. To ensure full effectiveness the voltage difference (V<sub>IN-</sub>V<sub>sw</sub>) should be more than 4.8 V.

If the driver was disabled due to an UVLO<sub>BOOT</sub> error, it will be reset to resume operation when VCIN and/or VDRV will be re-cycled or PWM will be held at tri-state level for more than 19 µs (typ).

In case of an UVLO<sub>BOOT</sub> error it is expected that the system controller discovers a missing phase, phase current mismatch, excessive temperature or OCP events on other phases and initiates shutdown.

#### 5.4.5 Current Monitoring and Overcurrent Protection (OCP)

The TDA21320 senses and reports current back to the controller via the voltage at IMON. This voltage is a filtered representation of the voltage at IMONREF. IMONREF is a current source output:

$$I_{IMONREF} = I_{OUT} \cdot a_{CS} \tag{2}$$

The voltage at IMONREF depends on the impedance its current is being passed through. A recommended target voltage at zero output current is 1.5V (common mode voltage). The series resistor  $R_{IMONREF}$  between IMONREF and the common mode voltage reference sets the voltage gain of the current sense according to:

$$V_{IMONREF} = V_{IMONREF\_CM} + R_{IMONREF} \cdot I_{MONREF}$$

(3)

The output current is now represented by the voltage difference between IMON and  $V_{IMONREF_CM}$ .  $V_{IMONREF_CM}$  is the voltage at IMONREF when the load current is zero.

$$V_{IMON} - V_{IMONREF\_CM} = I_{OUT} \cdot R_{IMONREF} \cdot a_{CS}$$

$$\tag{4}$$

$a_{cs}$  is given in 0 for VDRV = 5V. If VDRV has been chosen to be different,  $a_{cs}$  has to be calculated as:

$$a_{CS} = 6.67 \frac{\mu A}{A} \cdot \left(1 + \left(VDRV[V] - 5\right) \cdot 0.012\right)$$

(5)

A filter capacitor  $C_{IMON}$  of 10 pF has to be placed between IMON and  $V_{IMONREF_CM}$  (reference voltage pin of  $R_{IMONREF}$ ).  $C_{IMON}$  and  $R_{IMONREF}$  have to be arranged in a tight loop close to the pins of the TDA21320. An additional resistor  $R_{IMON}$  has to be connected in parallel to  $C_{IMON}$ . Its location is flexible and can also be at the controller. The value for  $R_{IMON}$  should be chosen identical to  $R_{IMONREF}$  within the range of 200  $\Omega$  to 1 k $\Omega$ .

At the voltage receiver side the measurement loop has to be closed. It is important to not inject noise into this loop. Therefore differential routing of IMON and IMONREF is required.

For example, having a permissible 500 mV voltage range at the receiver side to report positive current of 100 A, the resistor that has to be used in the IMONREF path can be calculated as:

$$V_{IMON} - V_{IMONREF\_CM} = 500mV$$

$$R_{IMONREF} = \frac{V_{IMON} - V_{IMONREF\_CM}}{I_{OUT} \cdot a_{CS}} = \frac{500mV}{100A \cdot 6.67 \cdot 10^{-6}} = 750\Omega$$

(6)

Having a resistor value of 348  $\Omega$  will result in the following voltage difference:

$$V_{IMON} - V_{IMONREF\_CM} = R_{IMONREF} \cdot I_{OUT} \cdot a_{CS} = 348\Omega \cdot 100A \cdot 6.67 \cdot 10^{-6} = 232mV$$

(7)

The sensing of current occurs in the HS-MOSFET and the LS-MOSFET during their respective on-times. During tristate condition both MOSFETs are in off-state without sensing. The current reported is then zero. If the tri-state condition was present for more than 19  $\mu$ s (typ.), current reporting resumes with a delay of 1  $\mu$ s (typ.).

<u>OCP</u>: By design of the application the current should never exceed the OCP tripping threshold  $I_{OCPtrip}$ . The duty cycle is being truncated by the TDA21320 when the current exceeds  $I_{OCPtrip}$ . This prevents the part from being destroyed by excessive current. A counter is being increased counting consecutive PWM duty cycle truncations. The counter is being reset at the first non-truncated PWM duty cycle. When the counter reaches the value of 10, a fault will be reported at TMON/FAULT by pulling it to 'high' level signaling the PWM controller the need for immediate action to prevent catastrophic failure. This fault is latched and will be released when VCIN and/or VDRV are being re-cycled.

#### 5.4.6 Shoot Through Protection

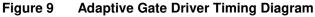

The TDA21320 driver includes gate drive functionality to protect against shoot through. In order to protect the power stage from overlap, both high-side and low-side MOSFETs being on at the same time, the adaptive control circuitry monitors specific voltages. When the PWM signal transitions to low, the high-side MOSFET will begin to turn-off after the propagation delay time t\_pdlu. When V<sub>GS</sub> of the high-side MOSFET is discharged below 1 V (a threshold below which the high-side MOSFET is off), a secondary delay t\_pdhl is initiated. After that delay the low-side MOSFET turns on regardless of the state of the "PHASE" pin. It ensures that the converter can sink current efficiently and the bootstrap capacitor will be refreshed appropriately during each switching cycle. See Figure 9 for more detail.

Application

## 6 Application

### 6.1 Implementation

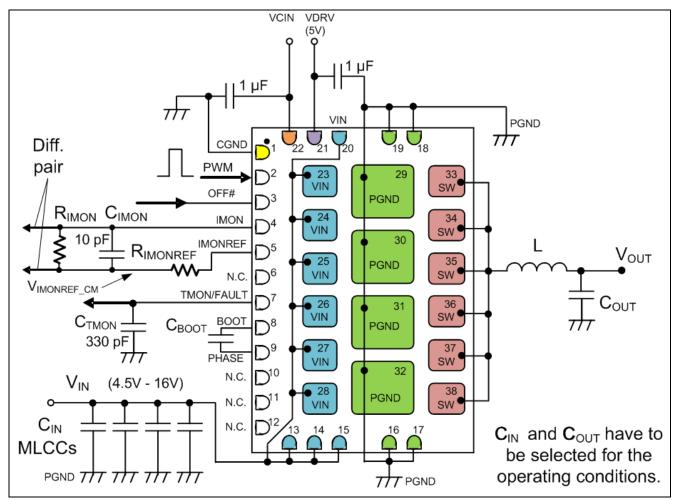

Figure 7 Pin Interconnection Outline (transparent top view)

Note:

- 1. Pin 9 (PHASE) is internally connected to the SW pads 33-38.

- The capacitor C<sub>TMON</sub> is used to filter noise from the TMON/FAULT connection. The capacitor has to be placed at the input of the controller. Its value should be set between 0.1 nF and 0.5 nF.

- 3. R<sub>IMON</sub> should be chosen identical to R<sub>IMONREF</sub>.

- 4.  $C_{IMON}$  and  $R_{IMONREF}$  have to be arranged in a tight loop close to the pins of the TDA21320.

- 5. To lower the pre-bias voltage at Vout to below  $V_{SW_0}$ , place a resistor from Vout to GND.

- C<sub>IN</sub> should consist of a 0.1 μF and a 1 μF very close to the pins 15/16 and a 1 μF capacitor at pins 19/20. In addition place sufficient MLCCs in relative proximity of each power stage to deliver energy for the on-time of the HS-MOSFET.

- 7. The value of capacitor  $C_{BOOT}$  should be chosen according to the corresponding application note.

## TDA21320

Application

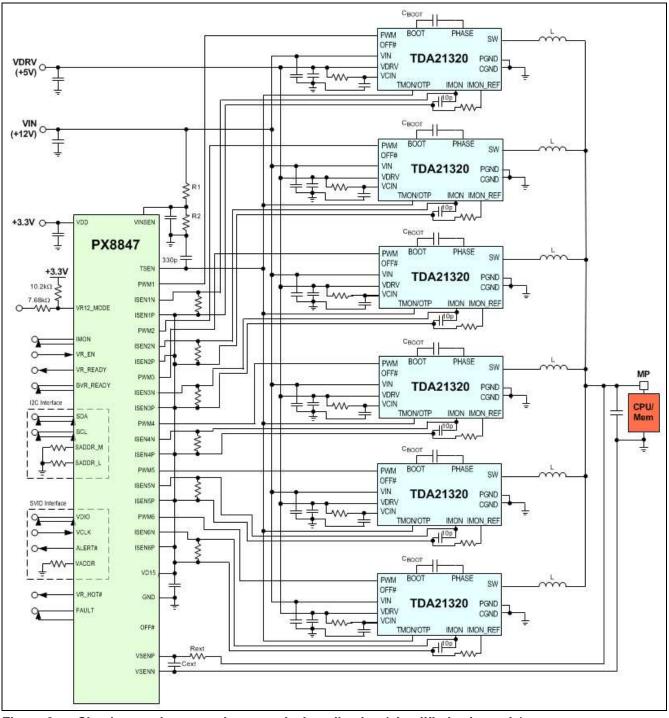

### 6.2 Typical Application

Figure 8 Six-phase voltage regulator - typical application (simplified schematic)

**Gate Driver Timing Diagram**

# 7 Gate Driver Timing Diagram

# 8 Performance Curves – Typical Data

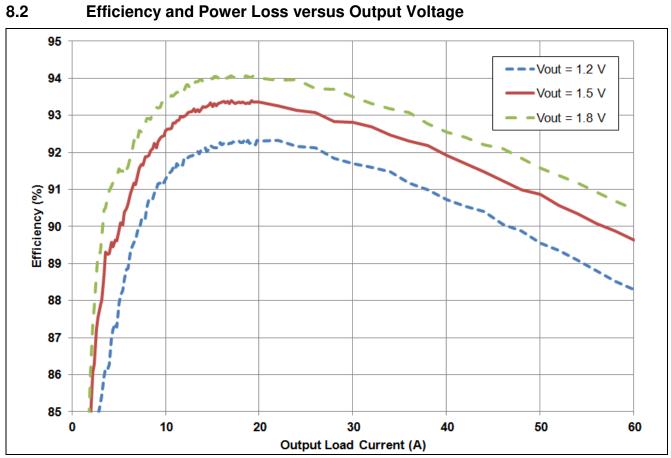

Operating conditions (unless otherwise specified): VIN = +12 V, VCIN = VDRV = +5 V, VOUT = +1.8 V, fsw = 750 kHz, 180nH (Delta, HCB118080D-181, DCR = 0.19 m $\Omega$ ) inductor, T<sub>A</sub> = 25 °C, airflow = 200 LFM, no heatsink. Efficiency and power loss reported herein include only TDA21320 losses.

## 8.1 Driver Current versus Switching Frequency

Figure 11 Driver Current over Switching Frequency in CCM Operation

Performance Curves – Typical Data

Figure 12 Efficiency at VIN = 12 V, VCIN = VDRV = 5 V, f<sub>sw</sub> = 750 kHz, Parameter: VOUT