Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Power-Factor Controller (PFC) IC for High Power Factor and Active Harmonic Filter

**TDA 4862**

#### **Advanced Information**

**Bipolar IC**

#### **Features**

- IC for sinusoidal line-current consumption

- Power factor approaching 1

- Controls boost converter as an active harmonics filter

- Internal start-up with low current consumption

- Zero current detector for discontinuous operation mode

- · High current totem pole gate driver

- Trimmed ± 1.4% internal reference

- Undervoltage lock-out with hysteresis

- Very low start-up current consumption

- Pin compatible to world standard

- Fast overvoltage regulator

- Current sense input with internal low pass filter

|                  | Туре       | Ordering Code | Package    |  |  |

|------------------|------------|---------------|------------|--|--|

| lacktriangledown | TDA 4862   | Q67000-A8368  | PG-DIP-8-1 |  |  |

| lacktriangledown | TDA 4862 G | Q67006-A8369  | PG-DSO-8-1 |  |  |

1

▼ = New type

2005-02-17

#### **Description**

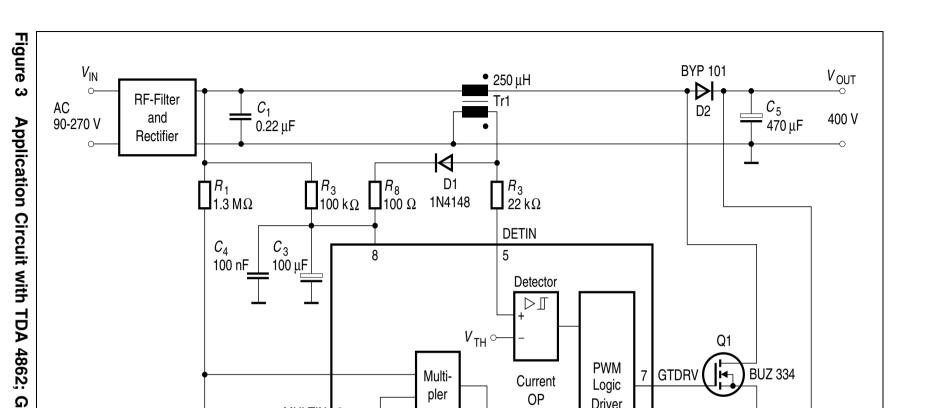

The TDA 4862 is excellent convenient for designing a preconverter in ballasts and switched mode power supplies with sinusoidal line current consumption and a power factor approaching unity.

The TDA 4862 controls a boost converter as an active harmonics filter in a discontinuous mode (free oscillating triangular shaped current mode).

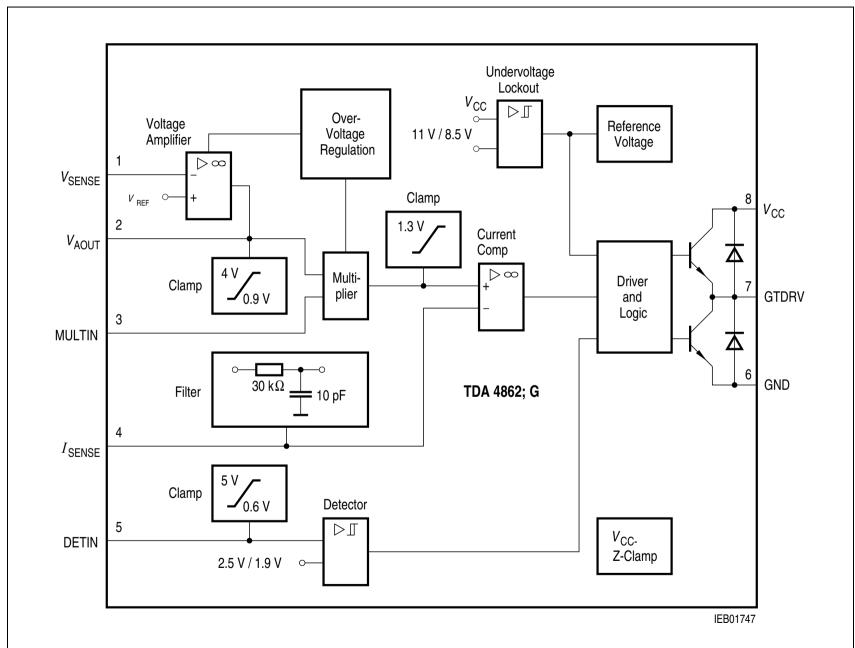

The TDA 4862 comprises an internal start-up timer, a high gain voltage amplifier, an one quadrant multiplier for approaching unity power factor, a zero current detector, PWM and logic circuitry, and totem pole MOSFET gate driver.

Protective features are: input undervoltage lockout with hysteresis,  $V_{\rm CC}$  zener clamp, cycle-by-cycle current limiting, output voltage limiting for fast and slow load changes up to open circuit, and a sinking gate driver current activated whenever undervoltage mode occurs.

The output voltage of this preconverter is regulated with high accuracy. Therefore the device can be used for world-wide line voltages without switches.

The TDA 4862 is the improved version of the TDA 4817 with a pinout equivalent to world standard.

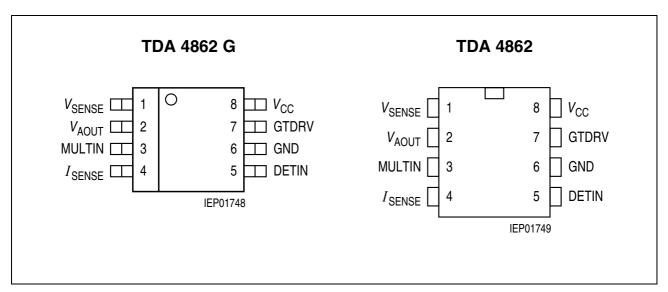

Figure 1 Pin Configuration (top view)

### **Pin Definitions and Functions**

| Pin | Symbol          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | $V_{\sf SENSE}$ | $\begin{tabular}{lll} \textbf{Voltage Amplifier Inverting Input;} \\ V_{\text{SENSE}} \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                                                                                                                                                                                                                                          |

| 2   | $V_{AOUT}$      | $\label{eq:Voltage Amplifier Output:} V_{\text{AOUT}} \text{ is connected internally to the first multiplier input. To prevent overshoot the input voltage will be clamped at 5 V. During no load conditions output pulses are suppressed completely when $V_{\text{AOUT}}$ falls below 2.2 V. If the current flowing into this pin is exceeding an internal defined margin the multiplier output voltage is reduced to prevent the MOSFET from overvoltage damage.$ |

| 3   | MULTIN          | Multiplier Input; MULTIN is the second multiplier input and connected via a resistive divider to the rectifier output voltage.                                                                                                                                                                                                                                                                                                                                       |

| 4   | $I_{SENSE}$     | <b>Current Sense Minus;</b> $I_{\rm SENSE}$ is connected to a sense resistor controlling the MOSFET source current. The input is internally clamped at $-0.3$ V to prevent negative input voltage interaction. An internal low pass filter suppresses voltage spikes when turning the MOSFET on.                                                                                                                                                                     |

| 5   | DETIN           | Zero Current Detector Input; DETIN is connected to an auxiliary winding monitoring the zero crossing of the inductor current.                                                                                                                                                                                                                                                                                                                                        |

| 6   | GND             | Ground; All voltages are measured with respect to GND. $V_{\rm CC}$ should be bypassed directly to GND with a 0.1 $\mu \rm F$ or larger ceramic capacitor.                                                                                                                                                                                                                                                                                                           |

| 7   | GTDRV           | Gate Drive Output; GTDRV is the output of a totem-pole circuitry for direct driving a MOSFET. A clamping network bypasses low state source current and high state sink current.                                                                                                                                                                                                                                                                                      |

| 8   | $V_{\sf CC}$    | Positive Supply Voltage; $V_{\rm CC}$ should be connected to a stable source slightly above the $V_{\rm CC}$ turn-ON threshold for normal operation. A 100 nF or lager ceramic capacitor connected to $V_{\rm CC}$ absorbs supply current spikes required to charge external MOSFET gate capacitances.                                                                                                                                                               |

#### **Functional Description**

#### Introduction

Conventional electronic ballasts and switching power supplies are designed with a bridge rectifier and bulk capacitor. Their disadvantage is that the circuit draws power from the line when the instantaneous AC voltage exceeds the capacitor's voltage. This occurs near the line voltage peak and causes a high charge current spike with following characteristics: the apparent power is higher than the real power that means low power factor condition, the current spikes are non-sinusoidal with a high content of harmonics causing line noise, the rectified voltage depends on load condition and requires a large bulk capacitor, special efforts in noise suppression are necessary.

With the TDA 4862 preconverter a sinusoidal current is achieved which varies in direct instantaneous proportion to the input voltage half sine wave and means a power factor near 1. This is due to the appearance of almost any complex load like a resistive one at the AC line. The harmonic distortions are reduced and comply with the IEC555 standard.

#### **Operating Description**

The TDA 4862 contains a wide bandwidth voltage amplifier used in a feedback loop, an overvoltage regulator, an one quadrant multiplier with a wide linear operating range, a current sense comparator, zero current detector, a PWM and logic circuitry, a totem-pole MOSFET driver, an internal trimmed voltage reference, a restart timer and an undervoltage lockout circuitry. These functional blocks are described below.

#### **Voltage Amplifier**

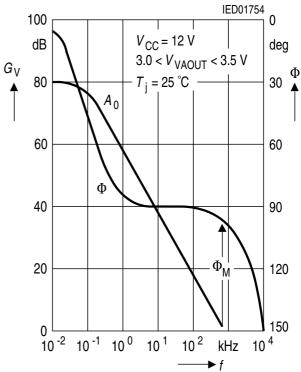

The voltage amplifier is internally compensated and yields a gain bandwidth of 0.8 MHz and a phase margin of 80 degrees. The non-inverting input is biased at 2.5 V and is not pinned out. The inverting input is sensing the output voltage via a resitive devider. The voltage amplifier output  $V_{\mathsf{AOUT}}$  and the inverting input  $V_{\mathsf{SENSE}}$  are connected in a simplest way via an external capacitor. It forms an integrator which monitors the average output voltage over several line cycles. Typically the bandwidth is set below 20 Hz. In order to keep the output voltage constant the voltage amplifier output is connected to the multiplier input for regulation.

#### Overvoltage Regulator

Fast changes of the output voltage can't be regulated by the integrator formed with the voltage amplifier This occurs during initial start-up, sudden load removal, or output arcing and leads to a current peak at the voltage amplifier input while the voltage amplifier's differential input voltages remains zero. The peak current is flowing through the external capacitor into  $V_{\text{AOUT}}$ . Exceeding an internal defined margin causes a regulation circuitry to reduce the multiplier output voltage.

#### Functional Description (cont'd)

#### Multiplier

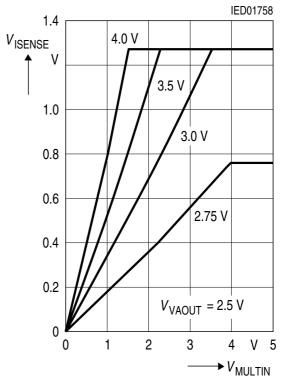

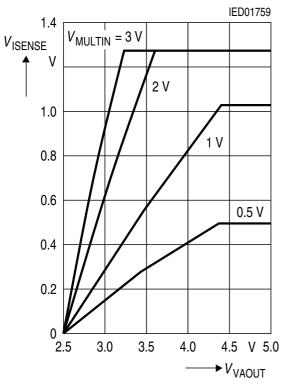

A one quadrant multiplier is the crucial circuitry that regulates the gate driver with respect of the DC output voltage and the AC haversine input voltage of the preregulator. Both inputs are designed for good linearity over a wide dynamic range, 0 V to 4.0 V for the MULTIN and 2.5 V to 4.0 V for the  $V_{\rm AOUT}$ .

#### **Current Sense Comparator and RS Latch**

The multiplier output voltage is compared with the current sense voltage which represents the current through the MOSFET. The current sense comparator in addition with the logic ensures that only a single pulse appears at the drive output during a given cycle. The multiplier output and the current sense threshold are internally clamped at 1.3 V. So the gate drive MOSFET is protected against critical operating, as they occur during start up. To prevent the input from negative pulses a special protection circuitry is implemented. Switch-on current peaks are reduced by an internal RC-Filter.

#### **Zero Current Detector**

The zero current detector senses the inductor current via an auxiliary winding and ensures that the next on-time is initiated immediately when the inductor current has reached zero. This diminishes the reverse recovery losses of the boost converter diode. Output switch conduction is terminated when the voltage drop of the shunt resistor reaches the threshold level of the multiplier output. So the boost current waveform has a triangular shape and there are no deadtime gaps between the cycles. This leads to a continuous AC line current limiting the peak current to twice of the average current.

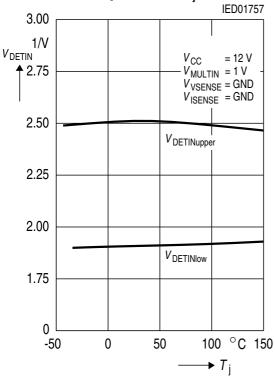

To prevent false tripping the zero current detector is designed as a Schmitt trigger with a hysteresis of 0.6 V. An internal 5 V clamp protects the input from overvoltage breakdown, a 0.6 V clamp prevents substrate injection. An external resistor must be used in series with the auxiliary winding to limit the current through the clamps.

#### **Timer**

A restart timer function was added to the IC to eliminate the need for an oscillator when used in stand-alone applications. The timer starts or restarts the TDA 4862 if the drive output has been off for more than 15  $\mu$ s after the inductor current reaches zero.

#### Functional Description (cont'd)

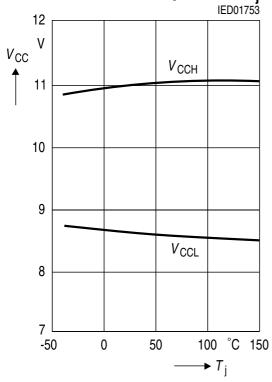

#### **Undervoltage Lockout**

An undervoltage lockout circuitry enables the output stage when  $V_{\rm CC}$  reaches the upper threshold  $V_{\rm CC}$  and terminates the output stage when  $V_{\rm CC}$  is falling below the lower threshold  $V_{\rm CCL}$ . In the standby mode the supply current is typically 75  $\mu$ A. An internal clamp has been added from  $V_{\rm CC}$  to ground to protect the IC from an overvoltage condition. The external circuitry is created with a start-up resistor connected from  $V_{\rm CC}$  to the input supply voltage and a storage capacitor from  $V_{\rm CC}$  to ground. Bootstrap power supply is created with the previous mentioned auxiliary winding and a diode.

#### **Output**

The TDA 4862 totem pole output stage is MOSFET compatible. An internal protection circuitry is activated when  $V_{\rm CC}$  is within the stand by mode and ensures that the MOSFET is turned-OFF. The totem pole output has been optimized to minimize cross conduction current during high speed operation. The addition of two 4  $\Omega$  resistors, one in series with the source output transistor and one in series with the sink output transistor, reduces the cross conduction current.

7

2005-02-17

$V_{\mathsf{TH}} \sim$

$\multimap V_{\mathsf{Ref}}$

Current

OP

$\triangleright \infty$

TDA 4862 G

$C_6$

Multi-

pler

Voltage OP

$\infty \triangleleft$

2

$V_{\mathsf{AOUT}}$

MULTIN 3

GND

6

$\prod_{12 \text{ k}\Omega}^{R_2}$

Q1

**GTDRV**

$I_{\mathsf{SENSE}}$

1 V<sub>SENSE</sub>

BUZ 334

$\Box_{1.6 \text{ M}\Omega}^{R_5}$

IES01750

$\prod_{0.1 \Omega}^{R_7} \prod_{10 \text{ k}\Omega}^{R_6}$

**PWM**

Logic

Driver

$\infty$

### **Absolute Maximum Ratings**

| Parameter             |                  |       | Symbol           | Limit        | Values | Unit | Notes                           |

|-----------------------|------------------|-------|------------------|--------------|--------|------|---------------------------------|

|                       |                  |       |                  | min.         | max.   |      |                                 |

| Supply voltage at     | $V_{\sf CC}$     | Pin 8 | $V_{\sf CC}$     | - 0.3        | _      | V    | _                               |

| supply + Z-current    | $V_{ m CC}$ -GND | Pin 8 | $I_{CCZ}$        | 0            | 70     | mA   | observe $P_{\max}$              |

| Current into          | GTDRV            | Pin 7 | $I_{GTDRV}$      | <b>- 400</b> | 500    | mA   | observe $P_{\text{max}}$        |

| Clamping current into | GTDRV            | Pin 7 | $I_{GTDCH}$      | _            | 100    | mΑ   | $V_{\rm GTDRV} > V_{\rm CC}$    |

| Clamping current into | GTDRV            | Pin 7 | $I_{GTDCL}$      | <b>– 100</b> | _      | mA   | $V_{\rm GTDRV}$ < $-0.3~{ m V}$ |

| Voltage at            | $V_{SENSE}$      | Pin 1 | $V_{\sf VSENSE}$ | - 0.3        | 17     | V    | _                               |

| Voltage at            | $V_{AOUT}$       | Pin 2 | $V_{VAOUT}$      | -0.3         | 6      | V    | _                               |

| Voltage at            | MULTIN           | Pin 3 | $V_{MULTIN}$     | -0.3         | 17     | V    | _                               |

| Voltage at            | $I_{SENSE}$      | Pin 4 | $V_{ISENSE}$     | <b>– 10</b>  | 17     | V    | _                               |

| Current into          | DETIN            | Pin 5 | $I_{DETINH}$     | _            | 50     | mΑ   | $V_{\rm DETIN}$ > 6 V           |

| Current into          | DETIN            |       | $I_{DETINL}$     | <b>– 10</b>  | _      | mA   | $V_{\rm DETIN}$ < 0.9 V         |

| Junction temperature  |                  |       | $T_{j}$          | <b>- 40</b>  | 150    | °C   | _                               |

| Storage temperature   |                  |       | $T_{stg}$        | <b>-</b> 50  | 150    | °C   | _                               |

| Thermal resistance sy |                  |       |                  |              |        |      |                                 |

| TDA 4862              |                  |       | $R_{thSA}$       | _            | 100    | K/W  | PG-DIP-8-1                      |

| TDA 4862 G            |                  |       | $R_{thSA}$       | 1            | 180    | K/W  | PG-DSO-8-1                      |

### **Operating Range**

| Parameter                     | Symbol       | Limit          | Values  | Unit | Notes              |

|-------------------------------|--------------|----------------|---------|------|--------------------|

|                               |              | min.           | max.    |      |                    |

| Supply voltage                | $V_{\sf CC}$ | $V_{\sf CCON}$ | $V_{Z}$ | V    | 1)                 |

| Z-current                     | $I_{Z}$      | 0              | 50      | mA   | observe $P_{\max}$ |

| Junction temperature          | $T_{\rm j}$  | <b>- 40</b>    | 150     | °C   | _                  |

| Voltage at $I_{\text{SENSE}}$ | $V_{ISENSE}$ | <b>-</b> 5     | $V_{Z}$ | ٧    | _                  |

$<sup>^{1)}</sup>$   $V_{\rm CCON}$  means  $V_{\rm CCH}$  has been exceeded but the supply voltage is still above  $V_{\rm CCL}$ . The device has switched from standby to active. For  $V_{\rm CCH}$  and  $V_{\rm CCL}$  values **see Electrical Characteristics**. If 0 V <  $V_{\rm CC}$  <  $V_{\rm CCON}$ , the device is in standby and output GTDRV is active low.

### **Electrical Characteristics**

Unless otherwise stated,  $V_{\rm CC}$  = 12 V, - 40  $^{\circ}$ C <  $T_{\rm j}$  < 150  $^{\circ}$ C.

| Parameter                                         | Symbol            | Limit Values |      |           | Unit | <b>Test Condition</b>                                   |

|---------------------------------------------------|-------------------|--------------|------|-----------|------|---------------------------------------------------------|

|                                                   |                   | min.         | typ. | max.      |      |                                                         |

| Overall                                           |                   |              |      |           |      |                                                         |

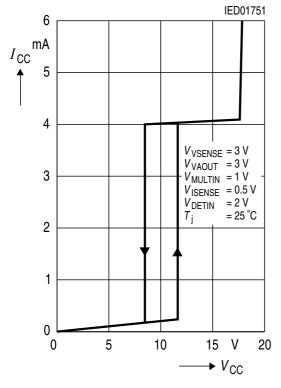

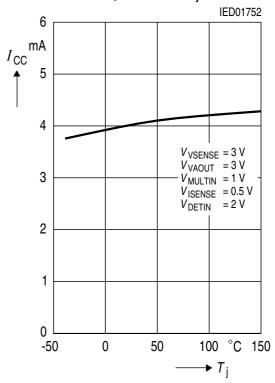

| Supply current, OFF                               | $I_{CCL}$         | _            | 75   | 200       | μΑ   | 0 V < $V_{\rm CC}$ < $V_{\rm CCH}$                      |

| Supply current, ON                                | $I_{CCH}$         | _            | 4    | 6         | mA   | Output low                                              |

| Supply current, dynamic                           | $I_{CCDY}$        | _            | 4.2  | 8         | mA   | $f_{ m DETIN}$ = 50 kHz, $C_{ m GTDRV}$ = 1 nF          |

| $\overline{V_{ m CC}}$ turn-ON threshold          | $V_{CCH}$         | _            | 11   | 11.5      | V    | _                                                       |

| $\overline{V_{\rm CC}}$ turn-OFF threshold        | $V_{CCL}$         | 8.0          | 8.5  | _         | V    | _                                                       |

| $\overline{V_{\text{CC}}}$ turn-ON/OFF hysteresis | $V_{CCHY}$        | 1.8          | 2.3  | 3.0       | V    | _                                                       |

| $\overline{V_{	exttt{CC}}}$ clamp                 | $V_{Z}$           | 15           | 17   | 19        | V    | $I_{\rm CCZ}$ = 50 mA                                   |

| Voltage Amplifier                                 |                   |              |      |           |      |                                                         |

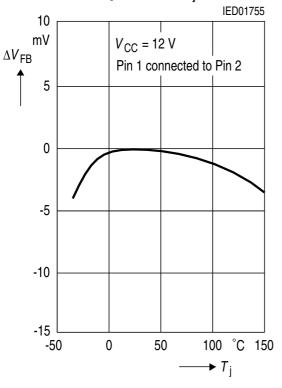

| Voltage feedback threshold                        | $V_{FB}$          | 2.465        | 2.5  | 2.53<br>5 | V    | $T_{\rm j}$ = 25 °C,<br>Pin 1 to Pin 2                  |

| Voltage feedback threshold                        | $V_{FB}$          | 2.45         | _    | 2.55      | V    | Pin 1 to Pin 2                                          |

| Line regulation                                   | $\Delta V_{FBL}$  | _            | _    | 5         | mV   | $V_{\rm CC}$ = 10 V to 15 V                             |

| Input bias current                                | $I_{\sf BVSENSE}$ | <b>–</b> 1   | _    | _         | μΑ   | _                                                       |

| Open loop voltage gain <sup>1)</sup>              | $G_{V}$           | _            | 80   | _         | dB   | _                                                       |

| Unity gain bandwidth <sup>1)</sup>                | $B_{W}$           | _            | 0.8  | _         | MHz  | _                                                       |

| Phase margin <sup>1)</sup>                        | $\Phi_{M}$        | _            | 80   | _         | Degr | _                                                       |

| Inhibit threshold voltage                         | $V_{VAOUTI}$      | _            | 2.2  | _         | V    | _                                                       |

| Output current source                             | $I_{VAOUTH}$      | _            | - 12 | _         | mA   | $V_{ m VAOUT}$ = 0 V,<br>$V_{ m VSENSE}$ = 2.3 V        |

| Output current sink                               | $I_{VAOUTL}$      | _            | 4    | _         | mA   | $V_{ m VAOUT} = 4 \  m V,$ $V_{ m VSENSE} = 2.8 \  m V$ |

<sup>&</sup>lt;sup>1</sup>not subject to production test - verified by characterization.

### Electrical Characteristics (cont'd)

Unless otherwise stated,  $V_{\rm CC}$  = 12 V, - 40 °C <  $T_{\rm j}$  < 150 °C.

| Parameter                       | Symbol       | Limit Values |      |      | Unit | <b>Test Condition</b>                                                                 |

|---------------------------------|--------------|--------------|------|------|------|---------------------------------------------------------------------------------------|

|                                 |              | min.         | typ. | max. |      |                                                                                       |

| Output voltage swing high state | $V_{VAOUTH}$ | 3.8          | 4.3  | 5.0  | V    | $I_{\mathrm{VAOUT}} = -0.2 \mathrm{\ mA}$<br>$V_{\mathrm{VSENSE}} = 2.3 \mathrm{\ V}$ |

| Output voltage swing low state  | $V_{VAOUTL}$ | _            | 0.9  | _    | V    | $I_{\text{VAOUT}} = 0.5 \text{ A}$<br>$V_{\text{VSENSE}} = 2.8 \text{ V}$             |

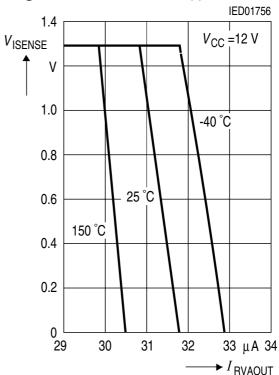

### **Overvoltage Regulator**

| Regulation current | $I_{RVAOUT}$ | 20 | 30 | 45 | μΑ | $V_{VAOUT} = V_{MULTIN}$ |

|--------------------|--------------|----|----|----|----|--------------------------|

|                    |              |    |    |    |    | = 4 V,                   |

|                    |              |    |    |    |    | $V_{ISENSE} = 0.5\;V$    |

### **Current Comparator**

| Input bias current    | $I_{\sf BISENSE}$ | <b>– 1</b> | _    | _   | μΑ | _                                                |

|-----------------------|-------------------|------------|------|-----|----|--------------------------------------------------|

| Input offset voltage  | $V_{ISENSEO}$     | _          | 25   | _   | mV | $V_{MULTIN} = 0 V,$                              |

|                       |                   |            |      |     |    | $V_{ m MULTIN}$ = 0 V,<br>$V_{ m VAOUT}$ = 2.4 V |

| Max threshold voltage | $V_{ISENSEM}$     | 1.05       | 1.25 | 1.5 | V  | _                                                |

| Delay to output1)     | $t_{PHL}$         | _          | 250  | _   | ns | _                                                |

| )                     |                   |            |      |     |    |                                                  |

#### **Detector**

| Upper threshold voltage $(V_{DETIN}$ increasing) | $V_{DETINU}$  | _          | 2.5 | 2.75 | V  | _                                   |

|--------------------------------------------------|---------------|------------|-----|------|----|-------------------------------------|

| Lower threshold voltage $(V_{DETIN}$ decreasing) | $V_{DETINL}$  | 1.5        | 1.9 | _    | V  | _                                   |

| Hysteresis                                       | $V_{DETINHY}$ | _          | 0.6 | _    | V  | _                                   |

| Input current                                    | $I_{BDETIN}$  | <b>–</b> 1 | _   |      | μΑ | 1.5 V < V <sub>DETIN</sub> < 2.75 V |

| Input clamp voltage                              |               |            |     |      |    |                                     |

| High state                                       | $V_{DETINHC}$ | 4          | 5   | _    | V  | $I_{\text{DETIN}} = 5 \text{ mA}$   |

| Low state                                        | $V_{DETINLC}$ | _          | 0.6 | 1    | V  | $I_{\text{DETIN}} = -5 \text{ mA}$  |

<sup>&</sup>lt;sup>1)</sup>not subject to production test - verified by characterization

### Electrical Characteristics (cont'd)

Unless otherwise stated,  $V_{\rm CC}$  = 12 V, - 40 °C <  $T_{\rm j}$  < 150 °C.

| Parameter                                        | Symbol                         | Li                                      | mit Values                                | S    | Unit   | <b>Test Condition</b>                                                                                                                                      |

|--------------------------------------------------|--------------------------------|-----------------------------------------|-------------------------------------------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                  |                                | min.                                    | typ.                                      | max. |        |                                                                                                                                                            |

| Multiplier                                       |                                |                                         |                                           |      |        |                                                                                                                                                            |

| Input bias current                               | $I_{BMULTIN}$                  | <b>– 1</b>                              | _                                         | _    | μΑ     | _                                                                                                                                                          |

| Dynamic voltage range MULTIN $V_{\mathrm{AOUT}}$ | $V_{ m MULTIN} \ V_{ m VAOUT}$ | 0 to 3 $V_{\rm FB}$ to $V_{\rm FB}$ + 1 | 0 to 4 $V_{\rm FB}$ to $V_{\rm FB}$ + 1.5 |      | V      | $V_{ m VAOUT}$ = 2.75 V $V_{ m MULTIN}$ = 1.0 V                                                                                                            |

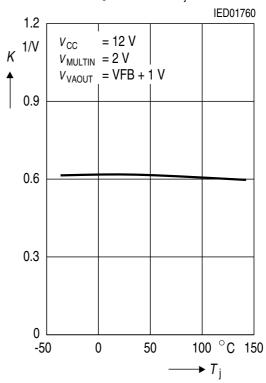

| Multiplier gain 1)                               | K                              | 0.45                                    | 0.65                                      | 0.85 | 1/V    | $V_{ m MULTIN}$ = 2 V<br>$V_{ m VAOUT}$ = $V_{ m FB}$ + 1 V                                                                                                |

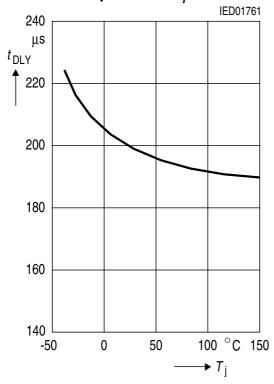

| Restart Timer                                    |                                |                                         |                                           |      |        |                                                                                                                                                            |

| Restart time delay                               | $t_{DLY}$                      | 75                                      | 190                                       | 400  | μs     | _                                                                                                                                                          |

| Gate Driver                                      |                                |                                         |                                           |      |        |                                                                                                                                                            |

| Output voltage low state                         | $V_{GTDRVL}$                   | _                                       | 0.8<br>1.8                                | _    | V<br>V | $I_{\rm GTDRV}$ = 20 mA<br>$I_{\rm GTDRV}$ = 200 mA                                                                                                        |

| Output voltage high state                        | $V_{GTDRVH}$                   | _                                       | 9.4<br>8.7                                | _    | V      | $I_{\rm GTDRV}$ = $-$ 20 mA<br>$I_{\rm GTDRV}$ = $-$ 200 mA                                                                                                |

| Output voltage active shut down                  | $V_{ m GTDRVU}$                | _                                       | 2.0                                       | 2.6  | V      | $I_{\rm GTDRV} = 50 \ \rm mA$ $V_{\rm CC} \ \rm increasing:$ $0 < V_{\rm CC} < V_{\rm CCH},$ $V_{\rm CC} \ \rm decreasing:$ $0 < V_{\rm CC} < V_{\rm CCL}$ |

| Rise time 2)                                     | $t_{r}$                        | _                                       | 100                                       | _    | _      | $C_{\rm GTDRV} = 1 \text{ nF}$                                                                                                                             |

| Fall time <sup>2)</sup>                          | $t_{f}$                        | _                                       | 40                                        | _    | _      | $C_{\rm GTDRV} = 1 \text{ nF}$                                                                                                                             |

<sup>1)</sup>  $K = V_{\text{ISFNSF}} / (V_{\text{MIII TIN}} \times (V_{\text{VAOLIT}} - V_{\text{FB}}))$

<sup>&</sup>lt;sup>2)</sup> not subject to production test - verified by design

# Supply Current $I_{\rm CC}$ versus Supply Voltage $V_{\rm CC}$

# Supply Current $I_{CC}$ versus Junction Temperature $T_i$

# Turn-ON/-OFF Threshold Voltage $V_{\rm CC}$ versus Junction Temperature $T_{\rm i}$

# Open Loop Gain $G_{\mathsf{V}}$ and Phase $\Phi$ versus Frequency f

# Threshold Voltage Change $\Delta V_{ t FB}$ versus Junction Temperature $T_{ t i}$

# Threshold Voltage $V_{\mathsf{ISENSE}}$ versus Regulation Current $I_{\mathsf{RVAOUT}}$

# Threshold Voltage $V_{\mathrm{DETIN}}$ versus Junction Temperature $T_{\mathrm{i}}$

# Current Sense Threshold $V_{\mathsf{ISENSE}}$ versus Multiplier Input $V_{\mathsf{MULTIN}}$

# Current Sense Threshold $V_{\mathsf{ISENSE}}$ versus Voltage Amplifier Output $V_{\mathsf{VAOUT}}$

# Multiplier Gain K versus Junction Temperature $T_i$

# Restart Time Delay $t_{\text{DLY}}$ versus Junction Temperature $T_{\text{i}}$

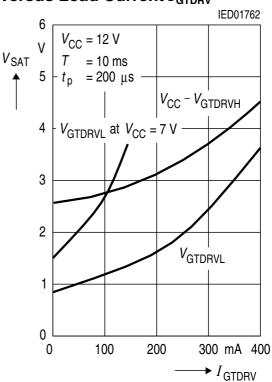

# Output Voltage Low/High State $V_{\mathtt{SAT}}$ versus Load Current $I_{\mathtt{GTDRV}}$

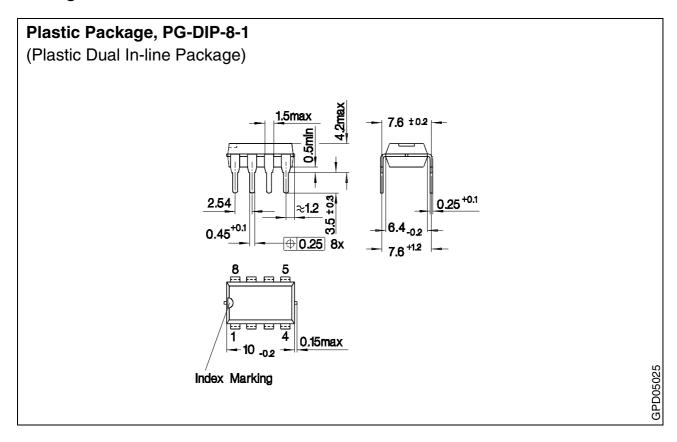

### **Package Outlines**

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

Dimensions in mm

16

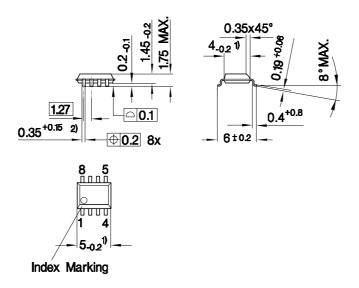

### Plastic Package, PG-DSO-8-1

(Plastic Dual Small Outline Package)

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Lead width can be 0.61 max. in dambar area

GPS05121

#### **Sorts of Packing**

Package outlines for tubes, trays etc. are contained in our Data Book "Package Information".

SMD = Surface Mounted Device

Dimensions in mm

| Revision His                     | story:                          | Current Version: 2005-02-17                  |  |  |  |  |  |  |

|----------------------------------|---------------------------------|----------------------------------------------|--|--|--|--|--|--|

| Previous Ver                     | Previous Version:2003-05-01     |                                              |  |  |  |  |  |  |

| Page<br>(in previous<br>Version) | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |  |  |  |  |  |

| 1                                | 1                               | Pb-free lead plating; RoHS compliant         |  |  |  |  |  |  |

#### Edition 1999-11-08

Published by Infineon Technologies AG St.-Martin-Strasse 53 D-81541 München © Infineon Technologies AG 1999 All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologiesis an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.