Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# PWM-FF IC

**TDA4916GG**

SMPS IC with MOSFET Driver Output

Power Management & Supply

# TDA4916GG Revision History: 1996-05-01 Datasheet Previous Version: Page Subjects (major changes since last revision)

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at <a href="http://www.infineon.com">http://www.infineon.com</a>

Edition 1996-05-01

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München

© Infineon Technologies AG 1999.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

## **SMPS-IC** with MOSFET Driver Output

**TDA 4916 GG**

#### **Features**

- High clock frequency

- · Low current drain

- High reference accuracy

- All monitoring functions

| Туре        | Ordering Code | Package    |

|-------------|---------------|------------|

| TDA 4916 GG | Q67000-A9230  | P-DSO-24-1 |

## **Functional Description and Application**

The general-purpose single-ended switch-mode power supply device for the direct control of SIPMOS power transistors incorporates both digital and analog functions. These are required for the construction of high-quality flyback, forward and choke converters. The device can be likewise used for transformer-less voltage multipliers and variable-speed motors.

Faults occurring during operation of the switch-mode power supply are detected by comparators integrated in the device which initiate protective functions.

In addition, pairs of power supplies can be synchronized in antiphase. In-phase or antiphase synchronization is possible when more than two power supplies are involved.

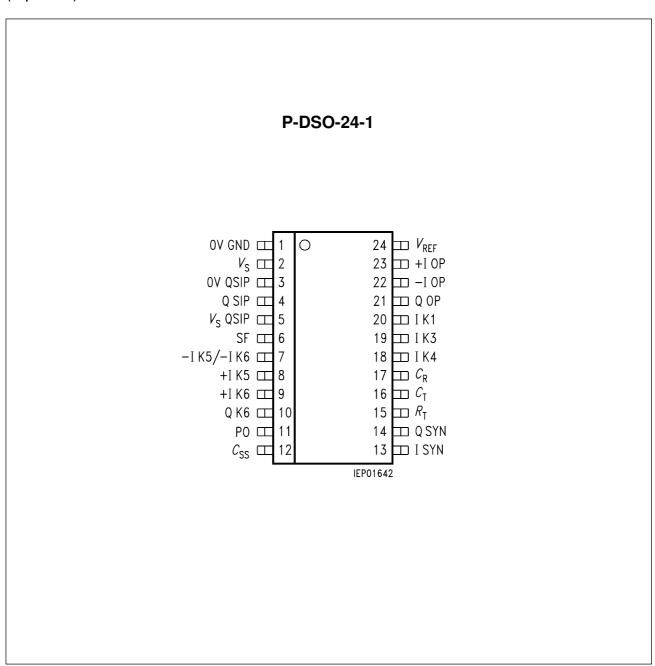

## **Pin Configuration**

(top view)

Figure 1

# **Pin Definitions and Functions**

| Pin No. | Symbol          | Function                      |

|---------|-----------------|-------------------------------|

| 1       | 0V GND          | GND                           |

| 2       | $V_{S}$         | Supply voltage                |

| 3       | 0V QSIP         | Ground QSIP                   |

| 4       | Q SIP           | SIPMOS driver                 |

| 5       | $V_{ m S}$ QSIP | Supply voltage driver         |

| 6       | SF              | Series feed                   |

| 7       | - I K5/- I K6   | Current sensor negative input |

| 8       | + I K5          | Current sensor K5             |

| 9       | + I K6          | Current turn-OFF K6           |

| 10      | Q K6            | Output K6                     |

| 11      | РО              | Pulse omission                |

| 12      | $C_{	t SS}$     | Soft start                    |

| 13      | ISYN            | Input synchronization         |

| 14      | Q SYN           | Output synchronization        |

| 15      | $R_{T}$         | Frequency generator           |

| 16      | $C_{T}$         | Frequency generator           |

| 17      | $C_{R}$         | Ramp generator                |

| 18      | I K4            | Input undervoltage            |

| 19      | I K3            | Input overvoltage             |

| 20      | I K1            | Input K1                      |

| 21      | Q OP            | Output operational amplifier  |

| 22      | -I OP           | Input operational amplifier   |

| 23      | + I OP          | Input operational amplifier   |

| 24      | $V_{REF}$       | Reference voltage             |

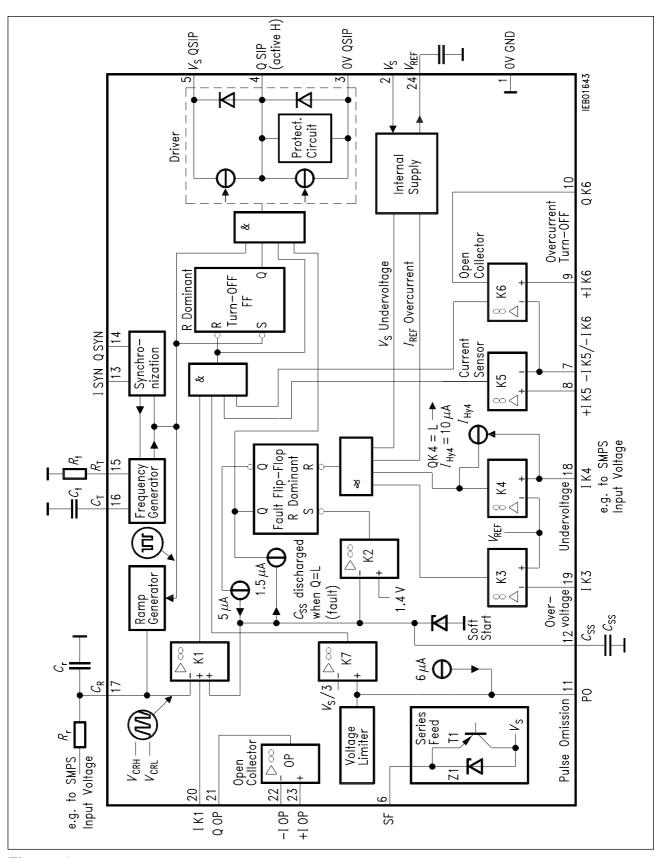

Figure 2 Block Diagram

## **Circuit Description**

The individual functional sections of the device and their interactions are described below.

#### Power Supply at $V_s$

The device does not enable the output until the turn-ON threshold of  $V_{\rm S}$  is exceeded. The duty factor (active time/period) can then rise from zero to the value set with K1 in the time determined by the soft start. The turn-OFF threshold lies below the turn-ON threshold. Below the turn-OFF threshold the output Q SIP is reliably low.

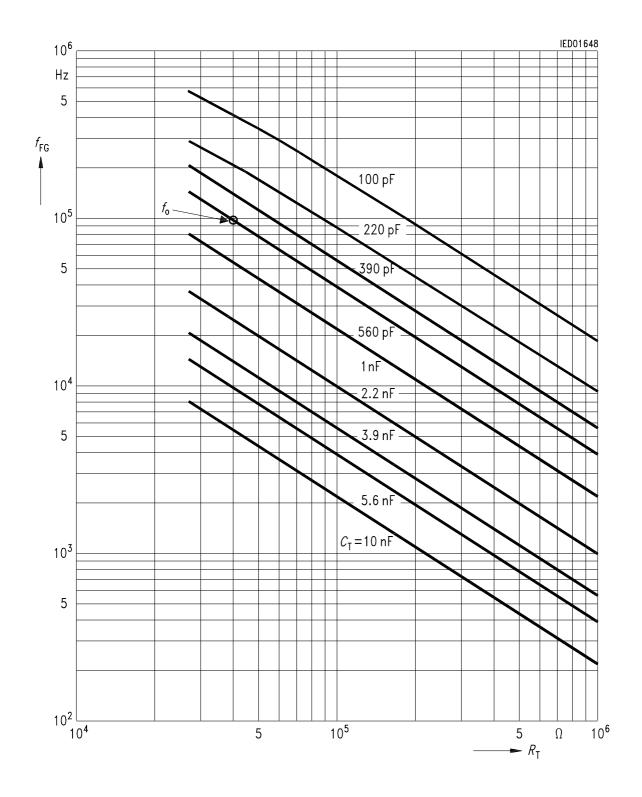

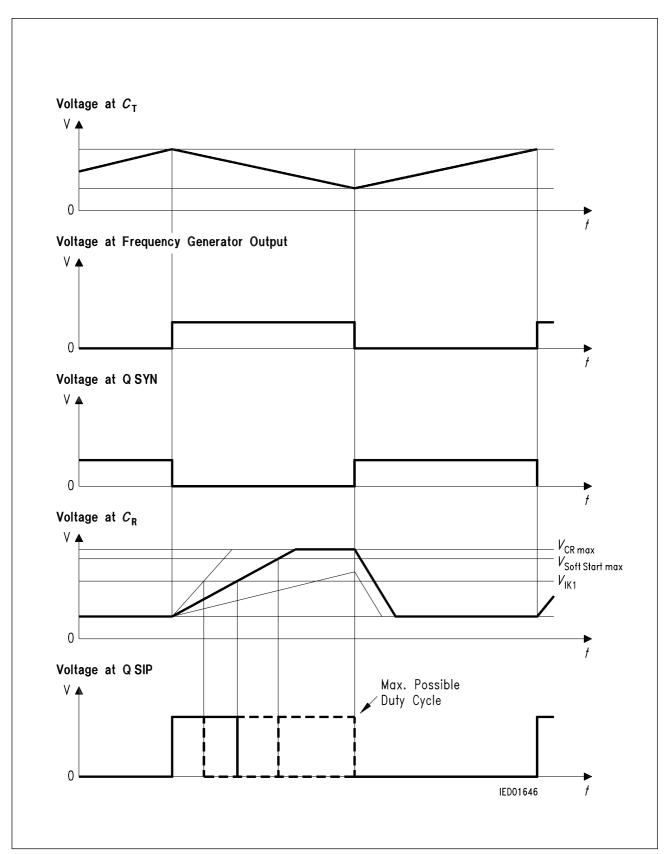

## **Frequency Generator**

The frequency is mainly determined by close-tolerance external components and the calibrated reference voltage.

The switching frequency at the output can be set by suitable choice of  $R_t$  and  $C_t$ .

The maximum possible duty factor can be reduced by a defined amount by means of a resistor from  $C_T$  to 0V GND. The maximum possible duty factor can be increased by a defined amount by means of a resistor from  $C_T$  to  $V_S$ .

## **Ramp Generator**

The ramp generator is controlled by the frequency generator and operates with the same frequency. Capacitor  $C_r$  on the ramp generator is discharged by an internally-set current and charged via a current set externally. The duration of the falling edge of the ramp generator output must be shorter than its rise time. Only then do the upper and lower switching levels of the ramp generator signal have their nominal values.

In "voltage mode control" operation, the rising edge of the ramp generator signal is compared with an externally set dc voltage in comparator K1 for pulse-width control at the output. The slope of the rising edge is set by the current through  $R_r$ . The voltage source connected to  $R_r$  can be the SMPS input voltage. This makes it possible to control the duty factor for a constant volt-second product at the output. This control option (precontrol) permits equalization of known disturbances (e.g. input voltage ripple).

Superimposed load current control (current mode control) can also be implemented. For this purpose the actual current at the source of the SIPMOS transistor is sensed and compared with the specified value in comparator K5.

## Comparator K1 (duty factor setting for voltage mode control)

The two plus inputs of the comparator are so connected that the lower plus level is always compared with the minus input level. As soon as the voltage of the rising edge of the sawtooth (minus input) exceeds the lower of the two plus input levels, the output is inhibited via the turn-OFF Flip-Flop, that is to say the High time of the output can be continuously varied. Since the frequency remains constant, this corresponds to a duty factor change.

## **Comparator K2**

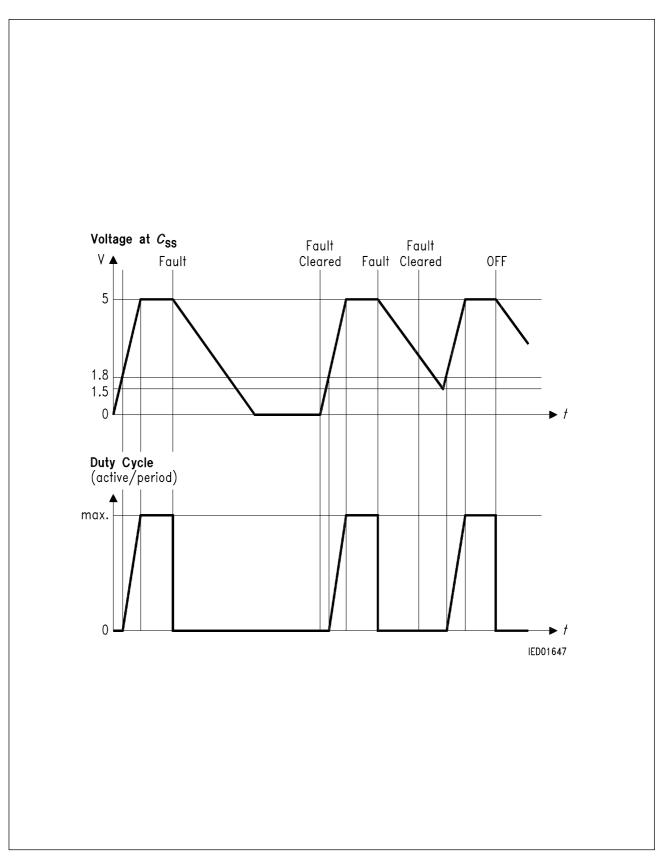

The comparator has a switching threshold at 1.5 V. Its output sets the fault Flip-Flop when the voltage on capacitor  $C_a$  lies below 1.5 V. However, the fault Flip-Flop accepts the setting pulse only if no reset pulse (fault) is applied. This prevents resetting of the output as long as a fault signal is present.

# Comparators K3 (overvoltage), K4 (undervoltage), $V_{\rm S}$ Undervoltage, $V_{\rm REF}$ Overcurrent

These are fault detectors which cause the output to be inhibited immediately by the fault Flip-Flop when faults occur. When faults are no longer present, the duty factor is reestablished via the soft start  $C_{\rm SS}$ . In the event of undervoltage, a current is injected at the input of K4 with the aid of which an adjustable hysteresis or latching is made possible. The value of the hysteresis is determined by the internal resistance of the external drive source and the current injected internally at the input of K4. In the event of undervoltage at K4, the injected current flows into the device.

#### Comparator K5 (duty factor setting for current mode control)

K5 is used to sense the source current at the switching transistor. The plus input of the comparator is fed out. Enabling of output Q SIP after cessation of the fault is effected with an H signal at the turn-OFF Flip-Flop output.

#### Comparator K6 (overcurrent turn-OFF)

The turn-OFF Flip-Flop is reset when overcurrent is detected by K6. In combination with the pulse-omission facility, individual pulses can then be omitted. This then results in a limited rise in the output current with a rising overload at the output.

## **Operational Amplifier OP**

Opamp OP is a high-quality operational amplifier. It can be used in the control circuit to transfer the variations in the voltage to be regulated in amplified form to the free plus input of comparator K1. As a result, a voltage change is converted into a duty factor change. The output of OP is an open collector. The frequency response of OP is already corrected. The plus input is connected internally via a capacitor to ground. This gives the inverting amplifier a more favorable phase response.

## **Turn-OFF Flip-Flop AFF**

A pulse is fed to the set input of the turn-OFF Flip-Flop with the falling edge of the frequency generator signal. However, it can only really be set if no reset signal is applied. With a set turn-OFF Flip-Flop, the output is enabled and can be active. The Flip-Flop inhibits the output in the event of a turn-OFF signal from K1, K5, K6 or K7.

#### **Fault Flip-Flop**

Fault signals fed to the reset input of the fault Flip-Flop cause the output to be immediately disabled (Low), and to be turned on again via the soft start  $C_{\rm SS}$  after removing fault-condition.

## Soft Start $C_{SS}$

The smaller of the two voltages at the plus inputs of K1 - compared with the ramp generator voltage - is a measure of the duty factor at the output. At the instant the device is turned-ON, the voltage on capacitor  $C_{\rm SS}$  equals zero. Provided no fault exists, the capacitor is charged up to its maximum value.

$C_{\rm SS}$  is discharged in the event of a fault. However, the fault Flip-Flop inhibits the output immediately. Below a charging voltage of approx. 1.5 V, a set signal is applied to the fault Flip-Flop and the output is enabled, provided a reset signal is not applied simultaneously. However, since the minimum ramp generator voltage is about 1.8 V, the duty factor at the output is not actually slowly and continuously increased until the voltage on  $C_{\rm SS}$  exceeds a value of 1.8 V.

The Z-diode limits the voltage on capacitor  $C_{\rm SS}$ . The voltage at the ramp generator can reach a higher level than the Zener voltage. With a suitable ramp generator rising edge slope, the duty factor can be limited to a wanted maximum value.

#### **Pulse Omission PO**

In the event of overcurrent in the SIPMOS transistors it is frequently necessary to omit pulses even with minimum duty factor. Only this measure ensures that the SIPMOS transistors cannot be overloaded. This wanted function can be achieved with Pulse Omission PO and Overcurrent Comparator K7 by means of a suitable external circuit.

## Reference Voltage $V_{\mathsf{REF}}$

The reference voltage source makes available a source with a high-stability temperature characteristic which can be used for external connection to the operational amplifier, the fault comparators, the frequency generator, or to other external units. The voltage source is short-circuit-proof to ground.

## Synchronization I SYN, Q SYN

The device has an input and an output for synchronization. In the case of a synchronized device (slave), its output Q SIP is in phase opposition to the output Q SIP of the synchronizing device (master). In the case of an unconnected input I SYN, or with connection to  $V_{\rm REF}$ , or also when a series capacitor (without switching transitions) is connected, the device receives its clock from the internal frequency generator in accordance with the circuit connected to it. As soon as switching transitions appear at I SYN, switchover to external synchronization and vice versa takes place after a delay. After a switchover process, a few clock cycles must elapse in addition to the delay before the frequency and phase achieve their steady states.

#### **Series Feed SF**

The Series Feed circuit section is used to turn-OFF the external series-feed transistor when energy recovery commences. As a result there is minimum power loss in the supply to the device. With the series-feed transistor turned-OFF, its drive current flows via VS to  $V_{\rm S}$ .

### **SIPMOS Driver Output Q SIP**

The output is High active. The time during which the output is active can be continuously varied.

The duration of the rising edge of the frequency generator signal is the minimum time during which the output can be Low.

The duration of the falling edge of the frequency generator signal is the maximum time during which the output can be High.

The output driver is designed as a push-pull stage. The output current is limited internally to the specified values.

Output Q SIP is connected via diodes to the supply  $V_{\rm S}$  QSIP and 0V QSIP.

A protection circuit SS lies between Q SIP and GND to clamp the output to ground at low impedance in the event of undervoltage at  $V_{\rm S}$ .

When the supply to the switch-mode power supply is switched on, the capacitive displacement current from the gate of the SIPMOS transistor is conducted to the smoothing capacitor at  $V_{\rm S}$  QSIP by the diode connected to  $V_{\rm S}$  QSIP. The voltage at  $V_{\rm S}$  QSIP may reach about 2.3 V in the process without the SIPMOS transistor being turned-ON.

The diode connected to ground clamps negative voltages at Q SIP to minus 0.7 V. Capacitive currents which occur with voltage dips at the drain terminal of the SIPMOS transistor can then flow away unimpeded.

The output is active Low with supply voltages at  $V_{\rm S}$  and  $V_{\rm S}$  QSIP from about 4 V on. The function of the diode connected to  $V_{\rm S}$  QSIP and the resistor are then taken over by the pull-down source.

The two ground terminals 0V SQIP and 0V GND can lie at different levels. This permits connections to be made to the SIPMOS transistor in such a way that the drive currents for the gate do not flow to the source via the current-sensing resistor. The maximum permissible level differences between 0V GND and 0V SQIP are given under Functional Range. If greater level differences are anticipated, it is better to join the two terminals.

# **Absolute Maximum Ratings**

$T_{\rm A}$  = - 40 to 85  $^{\circ}$ C

| Parameter                                                                            | Symbol                                                                                               | Limit '                    | Values               | Unit              | Test Condition                                             |  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------|----------------------|-------------------|------------------------------------------------------------|--|

|                                                                                      |                                                                                                      | min.                       | max.                 |                   |                                                            |  |

| Supply voltage; $V_{\rm S}, V_{\rm SQSIP}$ I OP, I K1, I K3, I K4, I K5, I K6, I SYN | $V_{\mathrm{S}}, V_{\mathrm{VS  QSIP}}$ $V_{\mathrm{I}}$ $V_{\mathrm{I  SYN}}$ $I_{\mathrm{I  SYN}}$ | - 0.3<br>- 0.3<br>0<br>- 3 | 17<br>17<br>5<br>3   | V<br>V<br>V<br>mA | $V_{\rm ISYN} > 5 \text{ V or}$                            |  |

| Q SYN                                                                                | $V_{	extsf{Q SYN}}$                                                                                  | - 0.3                      | 5                    | V                 | $V_{\rm ISYN} < 0 \text{ V}$                               |  |

| Frequency Generator; $C_T$ , $R_T$                                                   | $V_{CT,RT}$ $I_{CT,RT}$                                                                              | - 0.3<br>0                 | 5<br>3               | V<br>mA           | $V_{\rm CT}$ > 5 V                                         |  |

| Ramp Generator; $C_R$                                                                | $V_{CR} \ I_{CR}$                                                                                    | - 0.3<br>0                 | $V_{CRH}$            | V<br>mA           | $V_{\rm CRH}$ (see charact.) $V_{\rm CR} > V_{\rm CRH}$    |  |

| Reference voltage; $V_{REF}$                                                         | $V_{REF} \ I_{REF}$                                                                                  | - 0.3<br>- 10              | 6<br>10              | V<br>mA           | $V_{\mathrm{REF}}$ > 6 V or $V_{\mathrm{REF}}$ < $-$ 0.3 V |  |

| Output Opamp; Q OP<br>Inhibited<br>Conducting                                        | $V_{	extsf{Q} 	extsf{OP}} \ I_{	extsf{Q} 	extsf{OP}}$                                                | - 0.3<br>0                 | 17<br>5              | V<br>mA           |                                                            |  |

| Output Overcurrent Turn-OFF;<br>Q K6<br>Inhibited<br>Conducting                      | $V_{ m QK6} \ I_{ m QK6}$                                                                            | - 0.3<br>0                 | 17<br>5              | V<br>mA           |                                                            |  |

| Driver output; Q SIP                                                                 | $V_{QSIP}$                                                                                           | - 0.3                      | $V_{S}$              | V                 | 1)                                                         |  |

| Q SIP clamping diodes                                                                | $I_{ m Q~SIP}$                                                                                       | <b>– 10</b>                | 10                   | mA                | $V_{\rm QSIP} > V_{\rm S}$ or $V_{\rm QSIP} < -0.3~{ m V}$ |  |

| Soft start; $C_{SS}$                                                                 | $V_{	exttt{CSS}}$                                                                                    | - 0.3<br>0                 | V <sub>SSH</sub> 100 | V<br>μ <b>A</b>   | $V_{\rm SSH}$ (see charact.) $V_{\rm SS} > V_{\rm SSH}$    |  |

| Pulse omission; PO                                                                   | $V_{PO} \ I_{PO}$                                                                                    | - 0.3<br>0                 | $V_{POH}$            | V<br>mA           | $V_{\rm POH}$ (see charact.) $V_{\rm PO} > V_{\rm POH}$    |  |

| Series feed; SF                                                                      | $V_{SF}$                                                                                             | - 0.3                      | 17                   | V                 |                                                            |  |

| Junction temperature                                                                 | $T_{\rm j}$                                                                                          | - 65                       | 150                  | °C                |                                                            |  |

| Storage temperature                                                                  | $T_{\rm s}$                                                                                          | - 65                       | 150                  | °C                |                                                            |  |

| Thermal resistance system - ambient                                                  | R <sub>th S/A</sub>                                                                                  |                            | 60                   | K/W               |                                                            |  |

The values refer to the two connected ground terminals.

<sup>1)</sup> Important: observe max. power loss or junction temperature.

# **Operating Range**

| Function            | Symbol                       | Limit '      | Values    | Unit |

|---------------------|------------------------------|--------------|-----------|------|

|                     |                              | min.         | max.      |      |

| Supply voltage      | $V_{ m S} \ V_{ m VS  QSIP}$ | 0            | 15<br>15  | V    |

| Frequency generator | f                            | 0.05         | 400       | kHz  |

| Ramp generator      | f                            | 0.05         | 400       | kHz  |

| Ambient temperature | $T_{A}$                      | <b>- 40</b>  | + 100     | °C   |

| Ground Q SIP        | $V_{ m 0VQSIP}$              | GND – 300 mV | GND + 2 V | V    |

| Resistor at $R_{T}$ | $R_{RT}$                     | 27           | 1000      | kΩ   |

## **Characteristics**

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, – 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter                                 | Symbol            | L    | imit Val   | ues      | Unit                                 | Test Condition                                         |

|-------------------------------------------|-------------------|------|------------|----------|--------------------------------------|--------------------------------------------------------|

|                                           |                   | min. | typ.       | max.     |                                      |                                                        |

| Current in $V_{\rm S}$                    | $I_{ m VS}$       |      |            | 7 8      | mA <sup>1)</sup>                     | FG at 100 kHz<br>FG at 300 kHz<br>Q SYN<br>unconnected |

|                                           |                   |      |            | 8 9      | mA <sup>1)</sup>                     | FG at 100 kHz<br>FG at 300 kHz<br>Q SYN to 0V GND      |

| Current in V <sub>S</sub> QSIP            | $I_{ m VS  QSIP}$ |      | 2.5<br>5.5 |          | mA <sup>1)</sup><br>mA <sup>1)</sup> | FG at 100 kHz<br>FG at 300 kHz                         |

| Current in $V_{\rm S}$ + $V_{\rm S}$ QSIP | $I_{Sum}$         |      |            | 9        | mA <sup>1)</sup>                     | FG at 100 kHz<br>FG at 300 kHz<br>Q SYN<br>unconnected |

|                                           |                   |      |            | 10<br>14 | mA <sup>1)</sup>                     | FG at 100 kHz<br>FG at 300 kHz<br>Q SYN to 0 V GND     |

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, - 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter | Symbol | Lin  | nit Valu | es   | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

## **Current Drain**<sup>2)</sup> Hysteresis at $V_{\rm S}$

| Turn-ON threshold                         | $V_{SH}$ | 8.0 | 9.1 | 10  | V |  |

|-------------------------------------------|----------|-----|-----|-----|---|--|

| for $V_{\rm S}$ rising Turn-OFF threshold | $V_{SL}$ | 7.9 | 9.0 | 9.9 | V |  |

| for $V_{\rm S}$ falling                   | 'SL      | 7.0 | 0.0 | 0.0 | • |  |

## **Reference Voltage**

| Voltage                                 | $V_{REF}$                   | 2.460 | 2.500 | 2.540 | V    | $I_{\text{REF}} = 250 \mu\text{A}; \ V_{\text{S}} = 12 \text{V}$ |

|-----------------------------------------|-----------------------------|-------|-------|-------|------|------------------------------------------------------------------|

| Load current                            | $-I_{REF}$                  | 0     |       | 3     | mA   | $\Delta V_{REF} < 30 \; mV$                                      |

| Voltage change                          | $\Delta V_{REF}$            |       |       | 5     | mV   | $0 \text{ mA} < I_{\text{REF}} < 500  \mu\text{A}$               |

| Voltage change                          | $\Delta V_{REF}$            |       |       | 3     | mV   | 12 V < V <sub>S</sub> < 14 V                                     |

| Temperature response                    | $\Delta V_{REF} / \Delta T$ |       | 0.1   |       | mV/K |                                                                  |

| Operate threshold $V_{REF}$ overcurrent | $-I_{REFO}$                 | 3     | 6     | 10    | mA   |                                                                  |

## **Frequency Generator**

| Nominal frequency spread                      | $\Delta f_{F}/f_{O}$       | - 4 | 4 | % | 20 kHz $<$ $f_{\rm O}$ $<$ 150 kHz; Q SYN to GND; $V_{\rm S}$ = 12 V; $T_{\rm A}$ = 25 °C                                        |

|-----------------------------------------------|----------------------------|-----|---|---|----------------------------------------------------------------------------------------------------------------------------------|

| Voltage dependence<br>of nominal<br>frequency | $\Delta f_{ m V}/f_{ m O}$ | - 1 | 1 | % | 10 V < $V_{\rm S}$ < 14.4 V;<br>$T_{\rm A}$ = 25 °C;<br>relative to<br>$f_{\rm O}$ at 12 V;<br>20 kHz < $f_{\rm O}$<br>< 150 kHz |

$<sup>^{(1)}</sup>$   $C_{\rm T}$ ;  $R_{\rm T}$  (see oscillator nomogram).  $^{(2)}$  The currents as  $V_{\rm S}$  and  $V_{\rm S}$  QSIP are in each case without loads and without internal discharge to  $C_{\rm R}$ , as well as with active output Q SIP.

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, - 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter                                          | Symbol                      | Lir                 | nit Valu | ies                 | Unit                 | Unit Test Condition                                                                                                                                                                                |

|----------------------------------------------------|-----------------------------|---------------------|----------|---------------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                    |                             | min.                | typ.     | max.                |                      |                                                                                                                                                                                                    |

| Temperature-<br>dependence of<br>nominal frequency | $\Delta f_{\tau}/f_{\rm O}$ | -3                  |          | 3                   | %                    | $-25  ^{\circ}\text{C} < T_{\text{A}}$ < $+85  ^{\circ}\text{C}$ ; $V_{\text{S}} = 12  \text{V}$ ; relative to $f_{\text{O}}$ at 25 $^{\circ}\text{C}$ ; $20  \text{kHz} < f_{\text{O}}$ < 150 kHz |

| Nominal frequency                                  | $f_{20150}$                 | 0.92 f <sub>O</sub> | $f_{O}$  | 1.08 f <sub>O</sub> | kHz <sup>1)</sup>    | 20 kHz to 150 kHz                                                                                                                                                                                  |

| Nominal frequency                                  | $f_{150250}$                | 0.88 f <sub>O</sub> | $f_{O}$  | 1.12 f <sub>O</sub> | kHz <sup>1),2)</sup> | 150 kHz to 250 kHz                                                                                                                                                                                 |

| Nominal frequency                                  | $f_{250300}$                | 0.85 f <sub>O</sub> | $f_{O}$  | 1.15 f <sub>O</sub> | kHz <sup>1),2)</sup> | 250 kHz to 300 kHz                                                                                                                                                                                 |

| Maximum duty cycle                                 | ν <sub>20150</sub>          | 48                  |          | 52                  | % <sup>2)</sup>      | 20 kHz to 150 kHz                                                                                                                                                                                  |

| Maximum duty cycle                                 | ν <sub>150200</sub>         | 46                  |          | 54                  | % <sup>2)</sup>      | 150 kHz to 250 kHz                                                                                                                                                                                 |

| Maximum duty cycle                                 | v <sub>250300</sub>         | 44                  |          | 56                  | % <sup>2)</sup>      | 250 kHz to 300 kHz                                                                                                                                                                                 |

## **Ramp Generator**

| Frequency range                                                                                   | f                                        | 0.05 |      | 300  | kHz |                                                                                                                                                              |

|---------------------------------------------------------------------------------------------------|------------------------------------------|------|------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum voltage at $C_{R}$                                                                        | $V_{CRH}$                                | 4.8  | 5.8  | 6.8  | V   |                                                                                                                                                              |

| $\begin{array}{c} \hline \text{Minimum voltage} \\ \text{at } C_{\text{R}} \\ \hline \end{array}$ | $V_{CRL}$                                | 1.4  | 1.8  | 2.2  | V   |                                                                                                                                                              |

| Discharge current at $C_{R}$                                                                      | $I_{dis}$                                | 0.75 | 1.00 | 1.25 | mA  | internally fixed                                                                                                                                             |

| Capacitance at $C_{R}$                                                                            | $C_{R}$                                  | 10   |      |      | рF  |                                                                                                                                                              |

| ON-time spread (limited by $C_{\rm SS}$ )                                                         | $\Delta t_{\mathrm{Ot}}/t_{\mathrm{Ot}}$ | - 9  |      | 9    | %   | $C_{\rm r}$ = 200 pF;<br>$V_{\rm IK1}$ > $V_{\rm SSH}$ ;<br>$I_{\rm Rr}$ = 150 $\mu$ A;<br>$T_{\rm A}$ = 25 °C;<br>relative to<br>$t_{\rm Ot}$ = 4.0 $\mu$ S |

$<sup>^{(1)}</sup>$   $C_{\mathsf{T}}$ ;  $R_{\mathsf{T}}$  (see oscillator nomogram).  $^{(2)}$  See diagram: Tolerance of oscillator frequency, duty cycle.

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, – 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}.$

| Parameter      | Symbol                       | Limit Values |      |      | Unit | Test Condition                                                                                                                 |

|----------------|------------------------------|--------------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------|

|                |                              | min.         | typ. | max. |      |                                                                                                                                |

| ON-time drift  | $\Delta t_{ m Ot}/t_{ m Ot}$ | -2           |      | 2    | %    | $C_{\rm r}$ = 200 pF;<br>$V_{\rm IK1}$ > $V_{\rm CAH}$ ;<br>$I_{\rm Rr}$ = 150 $\mu$ A;<br>relative to<br>$t_{\rm Ot}$ = 25 °C |

| ON-time spread | $t_{\mathrm{Ot}}$            | 3.6          | 4.0  | 4.4  | μs   | $C_{\rm r}$ = 200 pF;<br>$V_{\rm IK1} > V_{\rm CAH}$ ;<br>$I_{\rm Rr}$ = 150 $\mu$ A                                           |

## **Operational Amplifier OP**

| Open-loop gain                    | $G_{o}$             | 60          | 80                                    | 100  | dB   | $I_{QOP} = 100 \mu\text{A}$             |

|-----------------------------------|---------------------|-------------|---------------------------------------|------|------|-----------------------------------------|

| Input offset voltage              | $V_{io}$            | - 5         |                                       | + 5  | mV   | $I_{QOP} = 100 \mu\text{A}$             |

| Input current                     | $-I_{i}$            |             |                                       | 1    | μΑ   |                                         |

| Input common-mode range           | $V_{cm}$            | - 0.2       |                                       | 4    | V    |                                         |

| Output current                    | $I_{QOP}$           | -3          |                                       |      | mA   | $0.5 < V_{Q OP} < 15 V$                 |

| Output voltage                    | $V_{QOP}$           | 0.5         |                                       | 15   | V    | $0 \text{ mA} < I_{QOP} < 2 \text{ mA}$ |

| Transit frequency                 | $f_{t}$             | 2           | 5                                     | 8    | MHz  |                                         |

| Transit phase                     | φ <sub>t</sub>      | 90          | 120                                   | 150  | Deg. |                                         |

| Temp. coeff. of $V_{io}$          | $T_{c}$             | <b>– 10</b> |                                       | + 10 | μV/K |                                         |

| Rate of rise of voltage at output | $\Delta V/\Delta t$ | 1           | ± 3                                   | 6    | V/µs | $I_{QOP} = 100 \mu\text{A}$             |

|                                   |                     | · ·         | · · · · · · · · · · · · · · · · · · · |      |      |                                         |

## **Comparator K1**

| Input current          | $-I_{K1}$ |   |     | 1         | μΑ               |                            |

|------------------------|-----------|---|-----|-----------|------------------|----------------------------|

| Inputcommon-mode range | $V_{cm}$  | 0 |     | $V_{CAH}$ | V                |                            |

| Turn-OFF delay         | $t_{OFF}$ |   | 200 | 400       | ns <sup>1)</sup> | Nominal load 1 nF at Q SIP |

<sup>1)</sup> Step function  $\Delta V - 100 \text{ mV} \longrightarrow \Delta V + 100 \text{ mV}$  (for delay from comparator input to Q SIP).

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, - 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

## Overvoltage K3

| Input current     | $-I_{i}$  |                  |   | 0.2                  | μΑ |  |

|-------------------|-----------|------------------|---|----------------------|----|--|

| Switching voltage | $V_{SW}$  | $V_{REF}$ – 5 mV |   | $V_{\rm REF}$ + 5 mV | V  |  |

| Turn-OFF delay    | $t_{OFF}$ | 1                | 2 | 4                    | μs |  |

## **Undervoltage K4**

| Input current at K4     | $-I_{i}$                    |                  |    | 0.2                     | μΑ                       |                                                                                                       |

|-------------------------|-----------------------------|------------------|----|-------------------------|--------------------------|-------------------------------------------------------------------------------------------------------|

| Switching voltage at K4 | $V_{\sf SW}$                | $V_{REF}$ – 5 mV |    | V <sub>REF</sub> + 5 mV | V                        |                                                                                                       |

| Hysteresis current      | $I_{ m hy4H} \ I_{ m hy4L}$ | 5                | 10 | 15<br>0.1               | μ <b>Α</b><br>μ <b>Α</b> | $\begin{array}{c} V_{+ \text{ IK4}} < V_{\text{sw}} \\ V_{+ \text{ IK4}} > V_{\text{sw}} \end{array}$ |

| Turn-OFF delay          | $t_{o}$                     | 1                | 2  | 4                       | μs <sup>1)</sup>         |                                                                                                       |

## **Current Sensor K5; Overcurrent Turn-OFF K6**

| Input current                 | $-I_{dyn}$       |     |            | 1          | μΑ                                   |                          |

|-------------------------------|------------------|-----|------------|------------|--------------------------------------|--------------------------|

| Input offset voltage          | $V_{io}$         | - 5 |            | + 5        | mV                                   |                          |

| Input<br>common-mode<br>range | $V_{cm}$         | 0   |            | 4          | V                                    |                          |

| Turn-OFF delay                | t <sub>OFF</sub> |     | 150<br>250 | 300<br>400 | ns <sup>2)</sup><br>ns <sup>3)</sup> | Load 1 nF at Q SIP       |

| Output K6 inhibited           | $I_{ m QK6}$     |     |            | 2          | μΑ                                   | $V_{\mathrm{QK6}}$ = 5 V |

| Conducting                    | $V_{QK6}$        |     |            | 1.2        | V                                    | $I_{\rm QK6}$ = 1 mA     |

<sup>1)</sup> Step function  $V_{\rm REF}$  – 100 mV  $\longrightarrow$   $V_{\rm REF}$  + 100 mV (for delay from comparator input to Q SIP). 2) Step function  $\Delta V$  – 100 mV  $\longrightarrow$   $\Delta V$  + 100 mV (for delay from comparator input to Q SIP). 3) Step function  $\Delta V$  – 10 mV  $\longrightarrow$   $\Delta V$  + 10 mV (for delay from comparator input to Q SIP).

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, - 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter                         | Symbol       | L    | imit Val | ues  | Unit | Test Condition            |

|-----------------------------------|--------------|------|----------|------|------|---------------------------|

|                                   |              | min. | typ.     | max. |      |                           |

| Soft Start $C_{ss}$               |              |      | ·        |      |      |                           |

| Charging current at $C_{\rm SS}$  | $-I_{ch}$    | 4    | 5        | 8    | μΑ   |                           |

| Discharge current at $C_{\rm SS}$ | $I_{dis}$    | 0.8  | 1.5      | 3.0  | μΑ   |                           |

| Upper clamping voltage            | $V_{SSH}$    | 4.4  | 4.8      | 5.2  | V    |                           |

|                                   | $V_{	t DSS}$ | 0.1  |          |      | V    | $V_{ m CRH} - V_{ m SSH}$ |

| Switching voltage of K2           | $V_{K2}$     | 1.1  | 1.4      | 1.7  | V    |                           |

## **Pulse Omission PO**

| -                              |                   |                            |                        |                            |    |                                        |

|--------------------------------|-------------------|----------------------------|------------------------|----------------------------|----|----------------------------------------|

| Charging current at PO int.    | $-I_{ch}$         | 4                          | 6                      | 9                          | μΑ |                                        |

| Charging current at PO ext.    | $I_{ch}$          |                            |                        | 1                          | mA |                                        |

| Voltage at – K7                | V <sub>- K7</sub> | V <sub>S</sub> /3<br>- 5 % | V <sub>S</sub> /3      | V <sub>S</sub> /3<br>+ 5 % | V  |                                        |

| Upper clamping voltage at + K7 | $V_{POH}$         | V <sub>-K7</sub><br>+ 0.2  | V <sub>-K7</sub> + 0.7 | V <sub>-K7</sub><br>+ 1.2  | V  | $0 \text{ mA} < I_{PO} < 1 \text{ mA}$ |

| Minimum voltage applied to PO  | $V_{POM}$         | 1                          |                        |                            | V  |                                        |

## **Synchronization**

| Input I SYN                  | $I_{ISYN}$              | <b>- 70</b> |            | 200        | μΑ | $0 \text{ V} < V_{1 \text{ SYN}} < 4.5 \text{ V}$ |

|------------------------------|-------------------------|-------------|------------|------------|----|---------------------------------------------------|

| Switching threshold at I SYN | T7                      | 4 -         | 0.7        | 0.5        | V  |                                                   |

| Open<br>Rising edge          | $V_{ISYNO}$             | 1.5<br>2.5  | 2.7<br>3.4 | 3.5<br>4.0 | V  |                                                   |

| Falling edge                 | $V_{ISYNF} \ V_{ISYNF}$ | 1.0         | 2.0        | 3.0        | V  |                                                   |

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, – 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter                                         | Symbol                               | L    | imit Val | ues  | Unit     | <b>Test Condition</b>                                        |

|---------------------------------------------------|--------------------------------------|------|----------|------|----------|--------------------------------------------------------------|

|                                                   |                                      | min. | typ.     | max. |          |                                                              |

| Switchover delay int. free-running - synchronized | $t_{df-s}$                           | 15   | 35       | 60   | μs       |                                                              |

| synchronized -<br>free-running                    | $t_{\sf ds-f}$                       | 9    | 18       | 35   | μs       |                                                              |

| Limiting diodes                                   | $\frac{-I_{\rm ISYN}}{I_{\rm ISYN}}$ | 0    |          | 2 2  | mA<br>mA | $V_{\rm ISYN} < 1 \text{ V}$<br>$V_{\rm ISYN} > 5 \text{ V}$ |

| Output Q SYN<br>High                              | $V_{QSYNH}$                          | 4.1  |          |      | V        | – 500 μA < I <sub>Q SYN</sub><br>< 0 μA                      |

| Low                                               | $V_{QSYNL}$                          |      |          | 0.6  | V        | 0 μΑ̈< I <sub>Q SYN</sub> < 500 μΑ                           |

| Fan-out of Q SYN for control I SYN                |                                      | 2    |          |      |          | Q SYN to 0V GND allowed                                      |

## **Series Feed**

| Series Feed Threshold at $V_{\rm S}$             | $V_{SFTH}$                        | 9.0        | 10.0    | 10.5   | V        | $I_{\rm SF} > 5  \mu {\rm A};$<br>$V_{\rm SF} = 13  {\rm V}$                                             |

|--------------------------------------------------|-----------------------------------|------------|---------|--------|----------|----------------------------------------------------------------------------------------------------------|

| $V_{ m SH}$ to $V_{ m SFTH}$ Gap Maximum current | $V_{\sf SFGAP} \ I_{\sf SF\ max}$ | 500<br>500 | -<br> - | _<br>_ | mV<br>μA | $V_{\rm SF} = 10 \text{ V}$<br>$V_{\rm S} = 11.5 \text{ V};$<br>$V_{\rm SF} = 12.5 \text{ V}$            |

| Voltage at Z1                                    | $V_{Z11}$                         | 5          | _       | _      | V        | $I_{Z1} = 20 \mu A;$                                                                                     |

| Voltage at Z1                                    | $V_{Z12}$                         | _          | _       | 8      | V        | $0 \le V_{\rm S} \le 8 \text{ V}$<br>$I_{\rm Z1} = 500 \mu\text{A}$<br>$0 \le V_{\rm S} \le 8 \text{ V}$ |

# **Output Driver Q SIP**

| Saturation voltage source | $V_{ m Q~SIPH} \ V_{ m Q~SIPH} \ V_{ m Q~SIPH}$ | 1.8<br>2.2<br>2.5 | 2.0<br>2.5<br>3.0 | V<br>V<br>V | $\begin{split} I_{\text{Q SIP}} &= 0 \text{ mA} \\ I_{\text{Q SIP}} &= -1 \text{ mA} \\ I_{\text{Q SIP}} &= -200 \text{ mA} \\ V_{\text{S}} &= V_{\text{Q SIP}} > V_{\text{Son}} \end{split}$ |

|---------------------------|-------------------------------------------------|-------------------|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Saturation voltage sink   | $V_{ m Q~SIPL} \ V_{ m Q~SIPL}$                 | 0.1<br>1.7        | 0.5<br>2.2        | V           | $I_{\rm QSIP} = 10~\rm mA$ $I_{\rm QSIP} = 200~\rm mA$ $V_{\rm S} = V_{\rm QSIP} > V_{\rm Son}$                                                                                               |

$V_{\rm Son}$  <  $V_{\rm S}$  < 15 V, – 25 °C <  $T_{\rm A}$  < 85 °C;  $V_{\rm Son}$  means that  $V_{\rm S}$  has exceeded  $V_{\rm SH}$ , but has not gone below  $V_{\rm SL}$ .

| Parameter                   | Symbol          | Limit Values |      |      | Unit             | <b>Test Condition</b>                                                                                            |

|-----------------------------|-----------------|--------------|------|------|------------------|------------------------------------------------------------------------------------------------------------------|

|                             |                 | min.         | typ. | max. |                  |                                                                                                                  |

| Saturation voltage sink     | $V_{ m Q~SIPP}$ |              |      | 1.5  | V                | $I_{\text{Q SIP}} = +5 \text{ mA}$ IC passive                                                                    |

| Output current Falling edge | $I_{ m QSIP}$   | 0.7          | 1.0  | 1.5  | A <sup>1)</sup>  | $C_{\text{Q SIP}}$ = 10 nF;<br>$V_{\text{S}} = V_{\text{Q SIP}}$ = 12 V                                          |

| Rising edge                 | $-I_{ m QSIP}$  | 0.7          | 1.0  | 1.5  | A <sup>1)</sup>  | $C_{\text{Q SIP}} = 10 \text{ nF};$<br>$V_{\text{S}} = V_{\text{Q SIP}} = 12 \text{ V}$                          |

| Output voltage<br>Fall time | $t_{Q\;SIPF}$   |              |      | 200  | ns <sup>2)</sup> | $C_{Q SIP} = 10 nF;$                                                                                             |

| Rise time                   | $t_{ m Q~SIPR}$ |              |      | 200  | ns <sup>2)</sup> | $V_{\rm S} = V_{\rm QSIP} = 12{\rm V}$<br>$C_{\rm QSIP} = 10{\rm nF};$<br>$V_{\rm S} = V_{\rm QSIP} = 12{\rm V}$ |

<sup>1)</sup> Maximum dynamic current during rising or falling edge.

2) Voltage level 10 %/90 %.

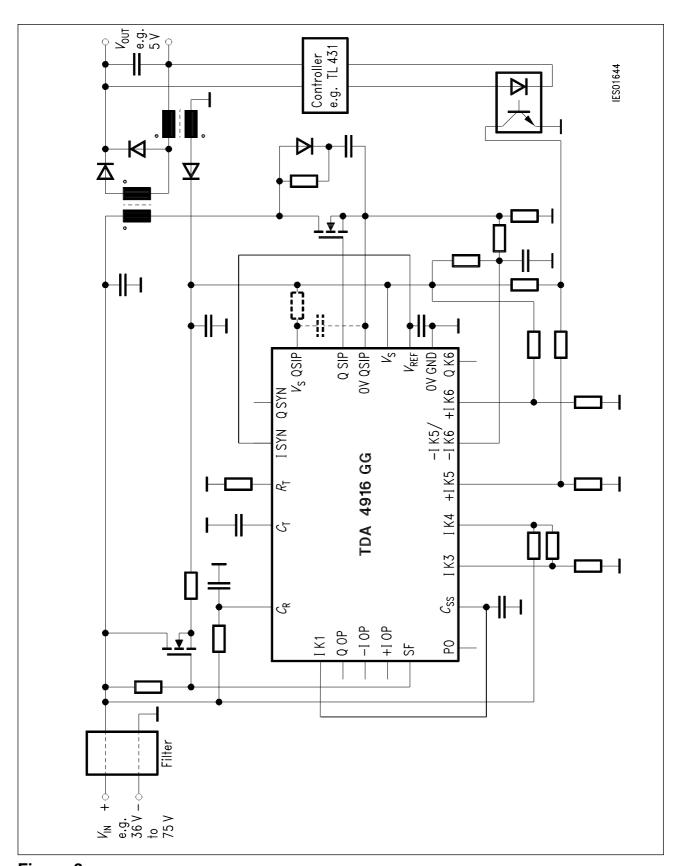

Figure 3

Application Circuit 1: Forward Converter with Output Regulation

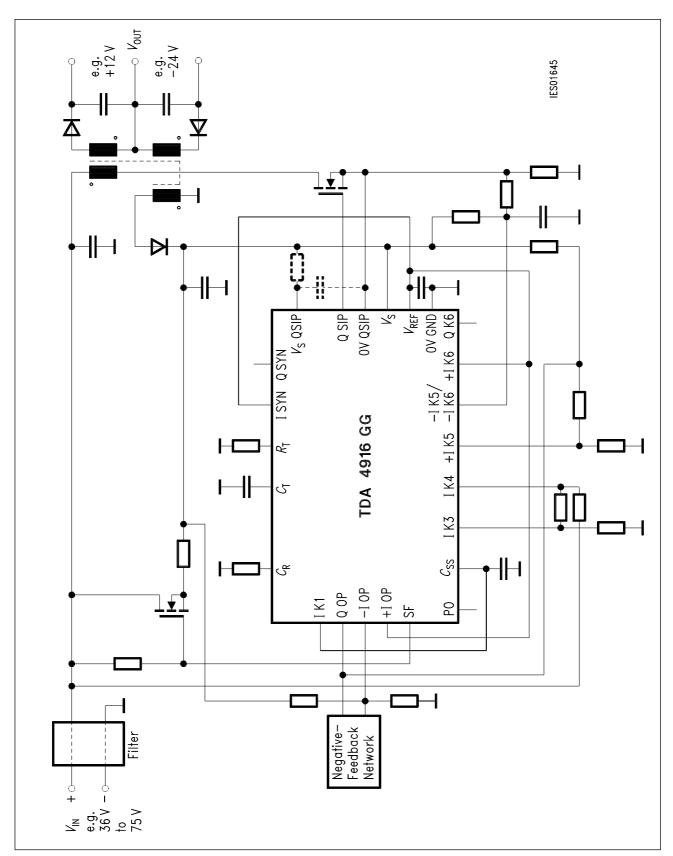

Figure 4

Application Circuit 2: Flyback Converter with EMF Regulation

Figure 5 Timing Diagram

Figure 6 Soft Start  $C_{\rm SS}$  / Fault/ON - OFF

# Nomogram for FG

$f_{\rm o}$  = 97.5 kHz @  $T_{\rm j}$  = 25 °C;  $R_{\rm T}$  = 40.2 kΩ;  $C_{\rm T}$  = 560 pF