Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Wireless Components

Edition 2007-02-26

Published by Infineon Technologies AG, Am Campeon 1-12. D-85579 Neubiberg, Germany © Infineon Technologies AG 3/7/07.

All Rights Reserved.

#### Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

#### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

#### **Warnings**

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# TDA5255 E1 ASK/FSK 434MHz Wireless Transceiver

# Wireless Components

#### **Data Sheet**

| Revision History: |            | 2007-02-26                          | TDA5255 E1 |  |

|-------------------|------------|-------------------------------------|------------|--|

| Previous          | Version:   | Version 1.1 as of 2002-11-28        |            |  |

| Page              | Subjects ( | (major changes since last revision) |            |  |

| 5                 | Indication | of the Ordering Code                |            |  |

| 5, 9              | Correction | n of the Package Name               |            |  |

| 76                | Indication | of the ESD-integrity values         |            |  |

|                   |            |                                     |            |  |

|                   |            |                                     |            |  |

|                   |            |                                     |            |  |

|                   |            |                                     |            |  |

|                   |            |                                     |            |  |

|                   |            |                                     |            |  |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

ABM<sup>®</sup>, AOP<sup>®</sup>, ARCOFI<sup>®</sup>, ARCOFI<sup>®</sup>-BA, ARCOFI<sup>®</sup>-SP, DigiTape<sup>®</sup>, EPIC<sup>®</sup>-1, EPIC<sup>®</sup>-S, ELIC<sup>®</sup>, FALC<sup>®</sup>54, FALC<sup>®</sup>56, FALC<sup>®</sup>-E1, FALC<sup>®</sup>-LH, IDEC<sup>®</sup>, IOM<sup>®</sup>, IOM<sup>®</sup>-1, IOM<sup>®</sup>-2, IPAT<sup>®</sup>-2, ISAC<sup>®</sup>-P, ISAC<sup>®</sup>-S, ISAC<sup>®</sup>-S TE, ISAC<sup>®</sup>-P TE, ITAC<sup>®</sup>, IWE<sup>®</sup>, MUSAC<sup>®</sup>-A, OCTAT<sup>®</sup>-P, QUAT<sup>®</sup>-S, SICAT<sup>®</sup>, SICOFI<sup>®</sup>, SICOFI<sup>®</sup>-2, SICOFI<sup>®</sup>-4, SICOFI<sup>®</sup>-4μC, SLICOFI<sup>®</sup> are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

Controller Area Network (CAN): License of Robert Bosch GmbH

# ASK/FSK 434MHz Wireless Transceiver TDA5255 E1

#### Version 1.2

# **Product Info**

#### **General Description**

The IC is a low power consumption single chip FSK/ASK Transceiver for half duplex low datarate communication in the 433-435MHz band. The IC offers a very high level of integration and needs only a few external components. It contains a highly efficient power amplifier, a low noise amplifier (LNA) with AGC, a double balanced mixer, a complex direct conversion stage, I/Q limiters with RSSI generation, an FSK demodulator, a fully integrated VCO and PLL synthesizer, a tuneable crystal oscillator, an onboard data filter, a data comparator (slicer), positive and negative peak detectors, a data rate detection circuit and a 2/3-wire bus interface. Additionally there is a power down feature to save battery power.

#### **Features**

- Low supply current (I<sub>s</sub> = 9mA typ. receive, I<sub>s</sub>

= 13mA typ. transmit mode)

- Supply voltage range 2.1 5.5V

- Power down mode with very low supply current consumption

- FSK and ASK modulation and demodulation capability

- Fully integrated VCO and PLL synthesizer and loop filter on-chip with on chip crystal oscillator tuning

- I<sup>2</sup>C/3-wire µController Interface

- On-chip low pass channel select filter and data filter with tuneable bandwidth

- Data slicer with self-adjusting threshold and 2 peak detectors

- FSK sensitivity <-109dBm, ASK sensitivity < -109dBm

- Transmit power up to +13dBm

- Datarates up to 100kBit/s Manchester Encoded

- Self-polling logic with ultra fast data rate detection

# Application

- Low Bitrate Communication

Systems

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Telemetry Systems

- Electronic Metering

- Home Automation Systems

| Туре       | Ordering Code | Package     |

|------------|---------------|-------------|

| TDA5255 E1 | SP000014555   | PG-TSSOP-38 |

# **Table of Contents**

|              |                                           | page      |

|--------------|-------------------------------------------|-----------|

| 1            | Product Description                       |           |

| 1.1          | Overview                                  | 8         |

| 1.2          | Features                                  | 8         |

| 1.3          | Application                               | 9         |

| 1.4          | Package Outlines                          | 9         |

| 2            | Functional Description                    | 10        |

| 2.1          | Pin Configuration                         | 10        |

| 2.2          | Pin Definitions and Functions             | 11        |

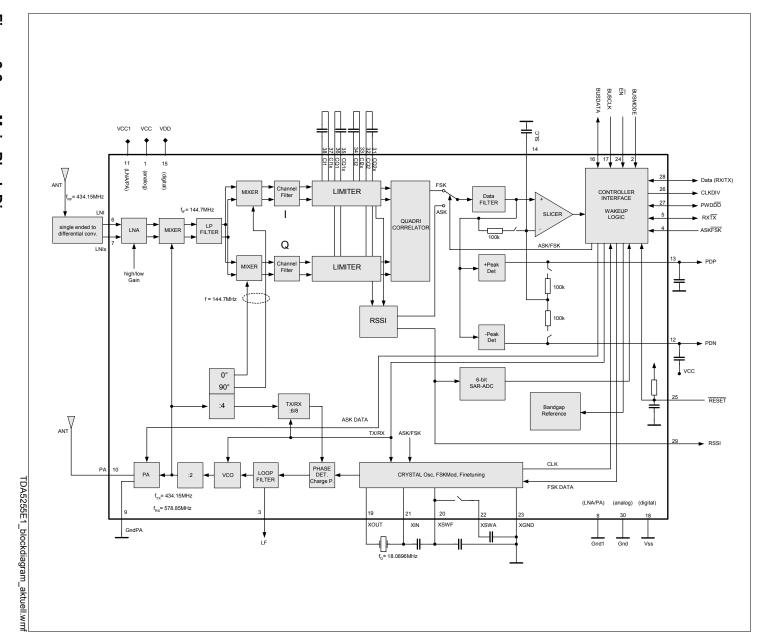

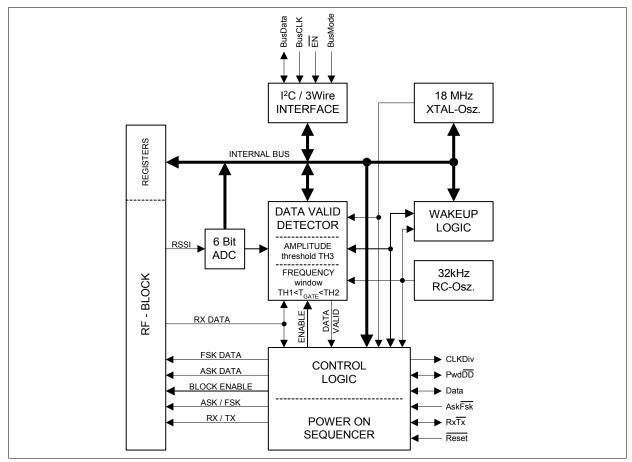

| 2.3          | Functional Block Diagram                  | 17        |

| 2.4          | Functional Block Description              | 18        |

| 2.4.1        | Power Amplifier (PA)                      | 18        |

| 2.4.2        | Low Noise Amplifier (LNA)                 | 18        |

| 2.4.3        | Downconverter 1 <sup>st</sup> Mixer       | 18        |

| 2.4.4        | Downconverter 2 <sup>nd</sup> I/Q Mixers  | 18        |

| 2.4.5        | PLL Synthesizer                           | 19        |

| 2.4.6        | I/Q Filters                               | 19        |

| 2.4.7        | I/Q Limiters                              | 20        |

| 2.4.8        | FSK Demodulator                           | 20        |

| 2.4.9        | Data Filter                               | 21        |

| 2.4.10       | Data Slicer                               | 21        |

| 2.4.11       | Peak Detectors                            | 21        |

| 2.4.12       | Crystal Oscillator                        | 21        |

| 2.4.13       | Bandgap Reference Circuitry and Powerdown | 22        |

| 2.4.14       | Timing and Data Control Unit              | 22        |

| 2.4.15       | Bus Interface and Register Definition     | 23        |

| 2.4.16       | Wakeup Logic                              | 30        |

| 2.4.17       | Data Valid Detection, Data Pin            | 31        |

| 2.4.17       |                                           | 32        |

| 2.4.10       | Sequence Timer                            | 34        |

|              |                                           | _         |

| 2.4.20       | RSSI and Supply Voltage Measurement       | 35        |

| 3            | Application                               | 37        |

| 3.1          | LNA and PA Matching                       | 37        |

| 3.1.1        | RX/TX Switch                              | 37        |

| 3.1.2        |                                           | Switch in |

| <del>-</del> | RX-Mode                                   | 37        |

| 3.1.3        |                                           | Switch in |

|              | TX-Mode                                   | 40        |

|              |                                           |           |

# **Table of Contents**

| 3.1.4          | Power-Amplifier                                  | page<br>42 |

|----------------|--------------------------------------------------|------------|

|                | ·                                                |            |

| 3.2<br>3.2.1   | Crystal Oscillator                               | 48<br>51   |

| 3.2.1          | Transmit/Receive ASK/FSK Frequency Assignment    | 51         |

| 3.2.3          | Parasitics                                       | 53         |

| 3.2.4          | Calculation of the external capacitors           | 55         |

| 3.2.5          | FSK-switch modes                                 | 55         |

| 3.2.6          | Finetuning and FSK modulation relevant registers | 56         |

| 3.2.7          | Chip and System Tolerances                       | 57         |

| 3.3            | IQ-Filter                                        | 58         |

| 3.4            | Data Filter                                      | 59         |

| 3.5            | Limiter and RSSI                                 | 60         |

| 3.6            | Data Slicer - Slicing Level                      | 62         |

| 3.6.1          | RC Integrator                                    | 62         |

| 3.6.2          | Peak Detectors                                   | 63         |

| 3.6.3          | Peak Detector - Analog output signal             | 65         |

| 3.6.4          | Peak Detector – Power Down Mode                  | 65         |

| 3.7            | Data Valid Detection                             | 66         |

| 3.7.1          | Frequency Window for Data Rate Detection         | 68         |

| 3.7.2          | RSSI threshold voltage - RF input power          | 69         |

| 3.8            | Calculation of ON_TIME and OFF_TIME              | 69         |

| 3.9            | Example for Self Polling Mode                    | 70         |

| 3.10           | Sensitivity Measurements                         | 71         |

| 3.10.1         | Test Setup                                       | 71         |

| 3.10.2         | BER performance depending on Supply Voltage      | 73         |

| 3.10.3         | Datarates and Sensitivity                        | 74         |

| 3.11           | Default Setup                                    | 75         |

| 4              | Reference                                        | 76         |

| 4.1            | Electrical Data                                  | 76         |

| 4.1.1          | Absolute Maximum Ratings                         | 76         |

| 4.1.2          | Operating Range                                  | 76         |

| 4.1.3<br>4.1.4 | AC/DC Characteristics                            | 77<br>90   |

| 4.1.4          | Digital Characteristics                          | 80<br>83   |

|                |                                                  |            |

| 4.3            | Test Board Layout                                | 84         |

| 4.4            | Bill of Materials                                | 85         |

## **Product Description**

# 1 Product Description

#### 1.1 Overview

The IC is a low power consumption single chip FSK/ASK Transceiver for the frequency band 433-435 MHz. The IC combines a very high level of integration and minimum external part count. The device contains a low noise amplifier (LNA), a double balanced mixer, a fully integrated VCO, a PLL synthesizer, a crystal oscillator with FSK modulator, a limiter with RSSI generator, an FSK demodulator, a data filter, a data comparator (slicer), a positive and a negative data peak detector, a highly efficient power amplifier and a complex digital timing and control unit with I<sup>2</sup>C/3-wire microcontroller interface. Additionally there is a power down feature to save battery power.

The transmit section uses direct ASK modulation by switching the power amplifier, and crystal oscillator detuning for FSK modulation. The necessary detuning load capacitors are external. The capacitors for fine tuning are integrated. The receive section is using a novel single-conversion/direct-conversion scheme that is combining the advantages of both receive topologies. The IF is contained on the chip, no RF channel filters are necessary as the channel filter is also on the chip.

The self-polling logic can be used to let the device operate autonomously as a master for a decoding microcontroller.

#### 1.2 Features

- Low supply current (I<sub>s</sub> = 9 mA typ. receive, I<sub>s</sub> = 13mA typ. transmit mode, both at 3 V supply voltage, 25°C)

- Supply voltage range 2.1 V to 5.5 V

- Operating temperature range -40°C to +85°C

- Power down mode with very low supply current consumption

- FSK and ASK modulation and demodulation capability without external circuitry changes, FM demodulation capability

- Fully integrated VCO and PLL synthesizer and loop filter on-chip with on-chip crystal oscillator tuning, therefore no additional external components necessary

- Differential receive signal path completely on-chip, therefore no external filters are necessary

- On-chip low pass channel select and data filter with tuneable bandwith

- Data slicer with self-adjusting threshold and 2 peak detectors

- Self-polling logic with adjustable duty cycle and ultrafast data rate detection and timer mode providing periodical interrupt

- FSK and ASK sensitivity < -109 dBm</li>

- Adjustable LNA gain

- Digital RSSI and Battery Voltage Readout

- Provides Clock Out Pin for external microcontroller

- Transmit power up to +13 dBm in 50Ω load at 5V supply voltage

- Maximum datarate up to 100 kBaud Manchester Encoded

- I<sup>2</sup>C/3-wire microcontroller interface, working at max. 400kbit/s

- meets the ETSI EN300 220 regulation and CEPT ERC 7003 recommendation

Data Sheet 8 2007-02-26

# **Product Description**

# 1.3 Application

- Low Bitrate Communication Systems

- Keyless Entry Systems

- Remote Control Systems

- Alarm Systems

- Telemetry Systems

- Electronic Metering

- Home Automation Systems

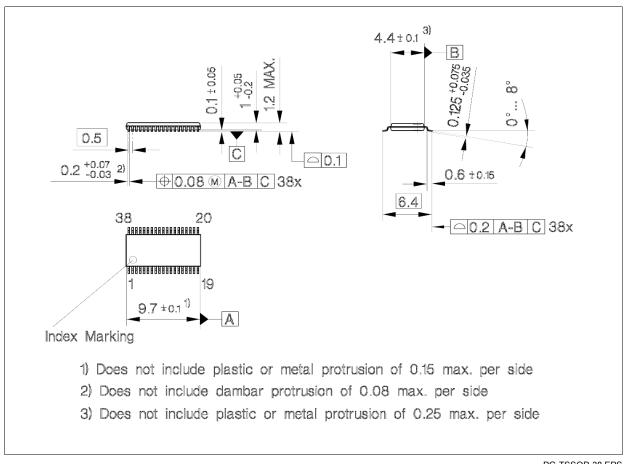

# 1.4 Package Outlines

PG-TSSOP-38.EPS

Figure 1-1 PG-TSSOP-38 package outlines

Data Sheet 9 2007-02-26

# **2** Functional Description

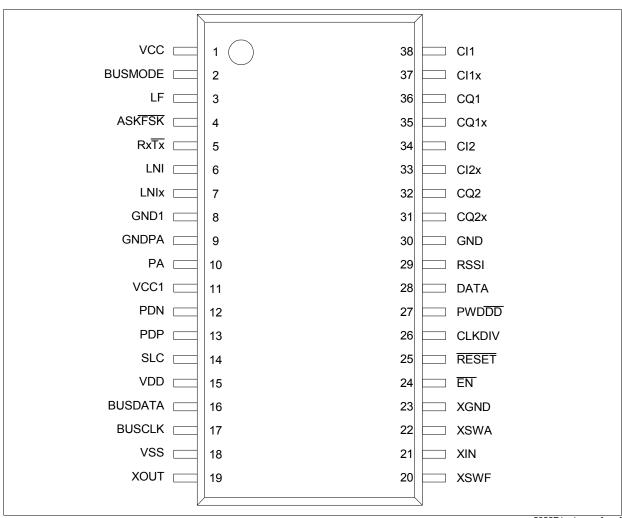

# 2.1 Pin Configuration

Figure 2-1 Pin Configuration

5255E1\_pin\_conf.wmf

# 2.2 Pin Definitions and Functions

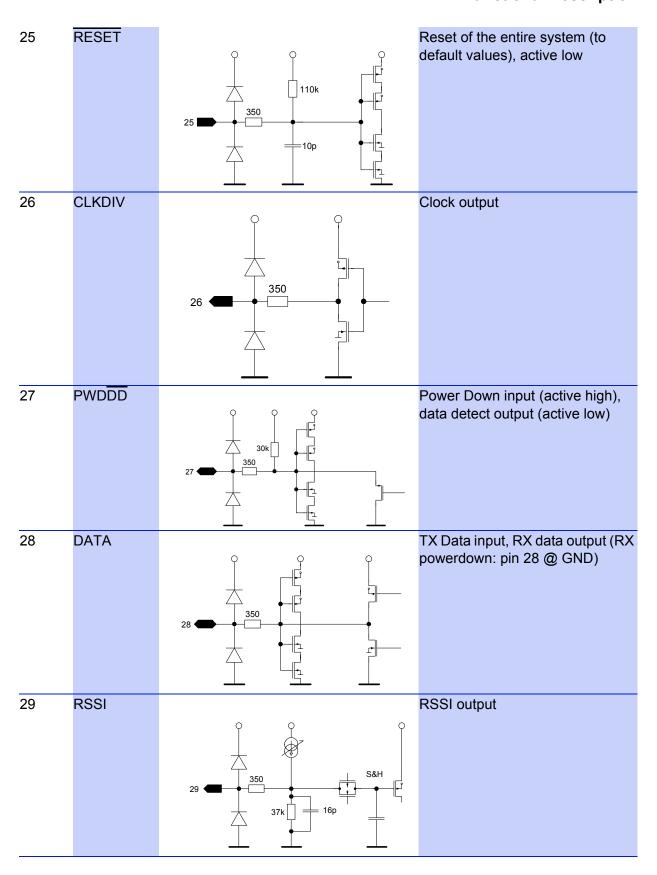

| Table 2 | Table 2-1 Pin Definition and Function |                          |                                                                 |  |  |

|---------|---------------------------------------|--------------------------|-----------------------------------------------------------------|--|--|

|         | Symbol                                | Equivalent I/O-Schematic | Function                                                        |  |  |

| 1       | VCC                                   | 111                      | Analog supply (antiparallel diodes between VCC, VCC1, VDD)      |  |  |

| 2       | BUSMODE                               | 2 350                    | Bus mode selection (I <sup>2</sup> C/3 wire bus mode selection) |  |  |

| 3       | LF                                    | 3 - 200                  | Loop filter and VCO control voltage                             |  |  |

| 4       | ASKFSK                                | 350                      | ASK/FSK- mode switch input                                      |  |  |

| 5  | RXTX  | 5 - 350 TX                             | RX/TX-mode switch input/output                                 |

|----|-------|----------------------------------------|----------------------------------------------------------------|

| 6  | LNI   | 5k 1.1V 5k 7                           | RF input to differential Low Noise<br>Amplifier (LNA))         |

| 7  | LNIX  | see Pin 6                              | Complementary RF input to differential LNA                     |

| 8  | GND1  | 8 ———————————————————————————————————— | Ground return for LNA and Power<br>Amplifier (PA) dirver stage |

| 9  | GNDPA | see Pin 8                              | Ground return for PA output stage                              |

| 10 | PA    | 10 Ω<br>10 Ω<br>9<br>GndPA             | PA output stage                                                |

| 11 | VCC1  | see Pin 1                              | Supply for LNA and PA                                          |

| 12 | PDN     | 12 PWDN 50k 50k 50k                       | Output of the negative peak detector                                                                              |

|----|---------|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 13 | PDP     | 350 PWDN                                  | Output of the positive peakdetector                                                                               |

| 14 | SLC     | 1.2uA 50k 50k 50k 50k 50k 50k 50k 50k 50k | Slicer level for the data slicer                                                                                  |

| 15 | VDD     | see Pin 1                                 | Digital supply; A $10\Omega$ serial resistor in the VDD supply line is strongly recommended; see also Section 4.4 |

| 16 | BUSDATA | 15k   | Bus data in/output                                                                                                |

| 17 | BUSCLK  | 350                                       | Bus clock input                                                                                                   |

| 18 | VSS  | see Pin 8                          | Ground for digital section                                                         |

|----|------|------------------------------------|------------------------------------------------------------------------------------|

| 19 | XOUT | Vcc-860mV<br>150μΑ                 | Crystal oscillator output, can also be used as external reference frequency input. |

| 20 | XSWF | 21<br>125fF 4pF 20<br>250fF 8pF 23 | FSK modulation switch                                                              |

| 21 | XIN  | see Pin 20                         |                                                                                    |

| 22 | XSWA | 22                                 | ASK modulation/FSK center frequency switch                                         |

| 23 | XGND | see Pin 22                         | Crystal oscillator ground return                                                   |

| 24 | ĒN   | 350                                | 3-wire bus enable input                                                            |

| 30 | GND  | see Pin 8                             | Analog ground                                    |

|----|------|---------------------------------------|--------------------------------------------------|

| 31 | CQ2x | Stage1:Vcc-630mV<br>Stage2: Vcc-560mV | Pin for external Capacitor<br>Q-channel, stage 2 |

| 32 | CQ2  | II                                    | Q-channel, stage 2                               |

| 33 | CI2x | II                                    | I-channel, stage 2                               |

| 34 | CI2  | II                                    | I-channel, stage 2                               |

| 35 | CQ1x | II                                    | Q-channel, stage 1                               |

| 36 | CQ1  | II                                    | Q-channel, stage 1                               |

| 37 | CI1x | II                                    | I-channel, stage 1                               |

| 38 | CI1  | II                                    | I-channel, stage 1                               |

# 2.3 **Functional Block Diagram**

Figure 2-2 Main Block Diagram

# 2.4 Functional Block Description

# 2.4.1 Power Amplifier (PA)

The power amplifier is operating in C-mode. It can be used in either high or low power mode. In high-power mode the transmit power is approximately +13dBm into 50 Ohm at 5V and +6dBm at 2.1V supply voltage. In low power mode the transmit power is approximately +10dBm at 5V and -32dBm at 2.1V supply voltage using the same matching network. The transmit power is controlled by the **D0**-bit of the **CONFIG** register (subaddress 00H) as shown in the following **Table 2-2**. The default output power mode is high power mode.

| Table 2 | Table 2-2 Sub Address 00H: CONFIG |                                   |         |  |  |

|---------|-----------------------------------|-----------------------------------|---------|--|--|

| Bit     | Function                          | Description                       | Default |  |  |

| D0      | PA_PWR                            | 0= low TX Power, 1= high TX Power | 1       |  |  |

In case of ASK modulation the power amplifier is turned fully on and off by the transmit baseband data, i.e. 100% On-Off-Keying.

# 2.4.2 Low Noise Amplifier (LNA)

The LNA is an on-chip cascode amplifier with a voltage gain of 15 to 20dB and symmetrical inputs. It is possible to reduce the gain to 0 dB via logic.

| Table 2-3 Sub Address 00H: CONFIG |          |                           |         |  |

|-----------------------------------|----------|---------------------------|---------|--|

| Bit                               | Function | Description               | Default |  |

| D4                                | LNA_GAIN | 0= low Gain, 1= high Gain | 1       |  |

# 2.4.3 Downconverter 1<sup>st</sup> Mixer

The Double Balanced 1<sup>st</sup> Mixer converts the input frequency (RF) in the range of 434-435 MHz down to the intermediate frequency (IF) at approximately 144MHz. The local oscillator frequency is generated by the PLL synthesizer that is fully implemented on-chip as described in **Section 2.4.5**. This local oscillator operates at approximately 578MHz in receive mode providing the above mentioned IF frequency of 144MHz. The mixer is followed by a low pass filter with a corner frequency of approximately 175MHz in order to prevent RF and LO signals from appearing in the 144MHz IF signal.

# 2.4.4 Downconverter 2<sup>nd</sup> I/Q Mixers

The Low pass filter is followed by 2 mixers (inphase I and quadrature Q) that convert the 144MHz IF signal down to zero-IF. These two mixers are driven by a signal that is generated by dividing the local oscillator signal by 4, thus equalling the IF frequency.

Data Sheet 18 2007-02-26

# 2.4.5 PLL Synthesizer

The Phase Locked Loop synthesizer consists of two VCOs (i.e. transmit and receive VCO), a divider by 4, an asynchronous divider chain with selectable overall division ratio, a phase detector with charge pump and a loop filter and is fully implemented on-chip. The VCOs are including spiral inductors and varactor diodes. The center frequency of the transmit VCO is 868MHz, the center frequency of the receive VCO is 1156MHz.

Generally in receive mode the relationship between local oscillator frequency  $f_{OSC}$ , the receive RF frequency  $f_{RF}$  and the IF frequency  $f_{IF}$  and thus the frequency that is applied to the I/Q Mixers is given in the following formula:

$$\frac{f_{osc}}{2} = 4/3 f_{RF} = 4 f_{IF}$$

[2 – 1]

The VCO signal is applied to a divider by 2 and afterwards by 4 which is producing approximately 144MHz signals in quadrature. The overall division ratio of the divider chain following the divider by 2 and 4 is 6 in transmit mode and 8 in receive mode <u>as</u> the nominal crystal oscillator frequency is 18.083MHz. The division ratio is controlled by the **RxTx** pin (pin 5) and the **D10** bit in the **CONFIG** register.

## 2.4.6 I/Q Filters

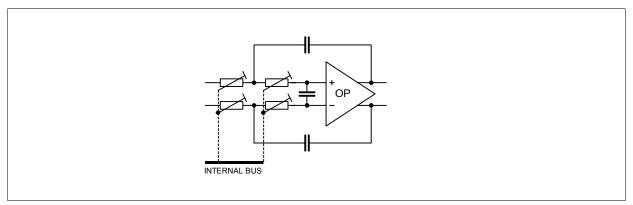

The I/Q IF to zero-IF mixers are followed by baseband 6<sup>th</sup> order low pass filters that are used for RF-channel filtering.

iq\_filter.wmf

# Figure 2-3 One I/Q Filter stage

The bandwidth of the filters is controlled by the values set in the filter-register. It can be adjusted between 50 and 350kHz in 50kHz steps via the bits D1 to D3 of the **LPF** register (subaddress 03H).

Data Sheet 19 2007-02-26

#### 2.4.7 I/Q Limiters

The I/Q Limiters are DC coupled multistage amplifiers with offset-compensating feedback circuit and an overall gain of approximately 80dB each in the frequency range of 100Hz up to 350kHz. Receive Signal Strength Indicator (RSSI) generators are included in both limiters which produce DC voltages that are directly proportional to the input signal level in the respective channels. The resulting I- and Q-channel RSSI-signals are summed to the nominal RSSI signal.

#### 2.4.8 FSK Demodulator

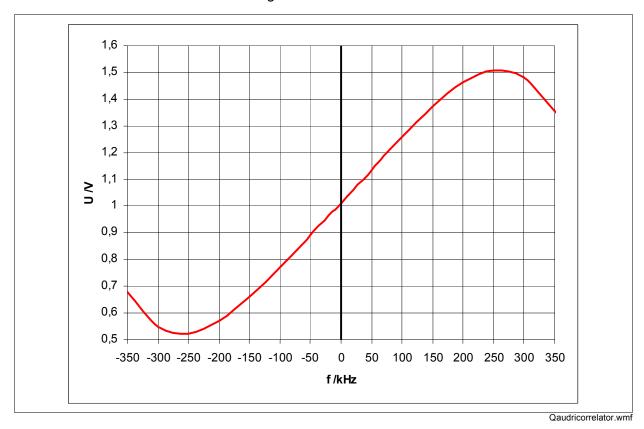

The output differential signals of the I/Q limiters are fed to a quadrature correlator circuit that is used to demodulate frequency shift keyed (FSK) signals. The demodulator gain is 2.4mV/kHz, the maximum frequency deviation is ±300kHz as shown in **Figure 2-4** below.

The demodulated signal is applied to the ASK/FSK mode switch which is connected to the input of the data filter. The switch can be controlled by the **ASKFSK** pin (pin 4) and via the D11 bit in the CONFIG register.

The modulation index *m* must be significantly larger than 2 and the deviation at least larger than 25kHz for correct demodulation of the signal.

Figure 2-4 Quadricorrelator Demodulation Characteristic

Data Sheet 20 2007-02-26

#### 2.4.9 Data Filter

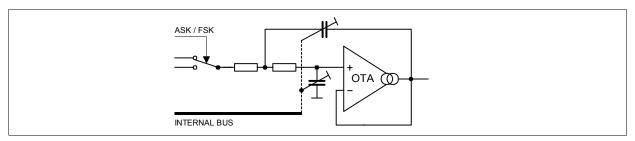

The 2-pole data filter has a Sallen-Key architecture and is implemented fully on-chip. The bandwidth can be adjusted between approximately 5kHz and 102kHz via the bits **D4** to **D7** of the **LPF** register as shown in **Table 3-10**.

data\_filter.wmf

Figure 2-5 Data Filter architecture

#### 2.4.10 Data Slicer

The data slicer is a fast comparator with a bandwidth of 100kHz. The self-adjusting threshold is generated by a RC-network (LPF) or by use of one or both peak detectors depending on the baseband coding scheme as described in **Section 3.6**. This can be controlled by the **D15** bit of the **CONFIG** register as shown in the following table.

| Table 2 | Table 2-4 Sub Address 00H: CONFIG |                                     |         |  |  |

|---------|-----------------------------------|-------------------------------------|---------|--|--|

| Bit     | Function                          | Description                         | Default |  |  |

| D15     | SLICER                            | 0= Lowpass Filter, 1= Peak Detector | 0       |  |  |

#### 2.4.11 Peak Detectors

Two separate Peak Detectors are available. They are generating DC voltages in a fast-attack and slow-release manner that are proportional to the positive and negative peak voltages appearing in the data signal. These voltages may be used to generate a threshold voltage for non-Manchester encoded signals, for example. The time-constant of the fast-attack/slow-release action is determined by the RC network with external capacitor.

# 2.4.12 Crystal Oscillator

The reference oscillator is an NIC oscillator type (Negative Impedance Converter) with a crystal operating in serial resonance. The nominal operating frequency of 18.083MHz and the frequencies for FSK modulation can be adjusted via 3 external capacitors. Via microcontroller and bus interface the chip-internal capacitors can be used for finetuning of the nominal and the FSK modulation frequencies. This finetuning of the crystal oscillator allows to eliminate frequency errors due to crystal or component tolerances.

Data Sheet 21 2007-02-26

# 2.4.13 Bandgap Reference Circuitry and Powerdown

A Bandgap Reference Circuit provides a temperature stable 1.2V reference voltage for the device. A power down mode is available to switch off all subcircuits that are controlled by the bidirectional Powerdown&DataDetect **PwdDD** pin (pin 27) as shown in the following table. Power down mode can either be activated by pin 27 or bit D14 in Register 00h. In power down mode also pin 28 (DATA) is affected (see **Section 2.4.17**).

| Table 2-5 PwdDD Pin Operating States |                 |

|--------------------------------------|-----------------|

| PwdDD                                | Operating State |

| VDD                                  | Powerdown Mode  |

| Ground/VSS                           | Device On       |

# 2.4.14 Timing and Data Control Unit

The timing and data control unit contains a wake-up logic unit, an I<sup>2</sup>C/3-wire microcontroller interface, a "data valid" detection unit and a set of configuration registers as shown in the subsequent figure.

logic.wmf

Figure 2-6 Timing and Data Control Unit

Data Sheet 22 2007-02-26

The I<sup>2</sup>C / 3-wire Bus Interface gives an external microcontroller full control over important system parameters at any time.

It is possible to set the device in three different modes: Slave Mode, Self Polling Mode and Timer Mode. This is done by a state machine which is implemented in the WAKEUP LOGIC unit. A detailed description is given in **Section 2.4.16**.

The DATA VALID DETECTOR contains a frequency window counter and an RSSI threshold comparator. The window counter uses the incoming data signal from the data slicer as the gating signal and the crystal oscillator frequency as the timebase to determine the actual datarate. The result is compared with the expected datarate.

The threshold comparator compares the actual RSSI level with the expected RSSI level.

If both conditions are true the **PwdDD** pin is set to LOW in self polling mode as you can see in **Section 2.4.16**. This signal can be used as an interrupt for an external  $\mu P$ . Because the **PwdDD** pin is bidirectional and open drain driven by an internal pull-up resistor it is possible to apply an external LOW thus enabling the device.

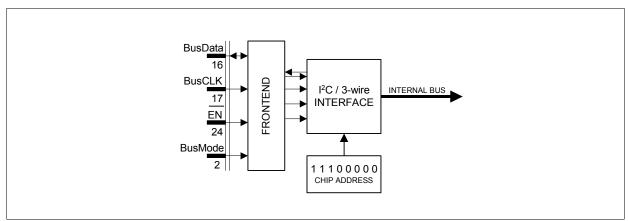

# 2.4.15 Bus Interface and Register Definition

The TDA5255 supports the  $I^2C$  bus protocol (2 wire) and a 3-wire bus protocol. Operation is selectable by the **BusMode** pin (pin 2) as shown in the following table. All bus pins (BusData, BusCLK, **EN**, BusMode) have a Schmitt-triggered input stage. The BusData pin is bidirectional where the output is open drain driven by an internal  $15k\Omega$  pull up resistor.

| Table 2-6 Bus I       | nterface Format |                 |             |             |

|-----------------------|-----------------|-----------------|-------------|-------------|

| Function              | BusMode         | EN              | BusCLK      | BusData     |

| I <sup>2</sup> C Mode | Low             | High= inactive, | Clock input | Data in/out |

| 3-wire Mode           | High            | Low= active     |             |             |

i2c 3w bus.wmf

Figure 2-7 Bus Interface

**Note:** The Interface is able to access the internal registers at any time, even in POWER DOWN mode. There is no internal clock necessary for Interface operation.

Data Sheet 23 2007-02-26

# I<sup>2</sup>C Bus Mode

In this mode the **BusMode** pin (pin 2) = LOW and the  $\overline{EN}$  pin (pin 24) = LOW.

#### **Data Transition:**

Data transition on the pin BusData can only occur when BusCLK is LOW. BusData transitions while BusCLK is HIGH will be interpreted as start or stop condition.

#### Start Condition (STA):

A start condition is defined by a HIGH to LOW transition of the BusData line while BusCLK is HIGH. This start condition must precede any command and initiate a data transfer onto the bus.

#### Stop Condition (STO):

A stop condition is defined by a LOW to HIGH transition of the BusData line while BusCLK is HIGH. This condition terminates the communication between the devices and forces the bus interface into the initial state.

#### Acknowledge (ACK):

Indicates a successful data transfer. The transmitter will release the bus after sending 8 bit of data. During the 9th clock cycle the receiver will set the SDA line to LOW level to indicate it has received the 8 bits of data correctly.

#### Data Transfer Write Mode:

To start the communication, the bus master must initiate a start condition (STA), followed by the 8bit chip address. The chip address for the TDA5255 is fixed as "1110000" (MSB at first). The last bit (LSB=A0) of the chip address byte defines the type of operation to be performed:

A0=0, a write operation is selected and A0=1 a read operation is selected.

After this comparison the TDA5255 will generate an ACK and awaits the desired sub address byte (00H...0FH) and data bytes. At the end of the data transition the master has to generate the stop condition (STO).

#### Data Transfer Read Mode:

To start the communication in the read mode, the bus master must initiate a start condition (STA), followed by the 8 bit chip address (write: A0=0), followed by the sub address to read (80H, 81H), followed by the chip address (read: A0=1). After that procedure the data of the selected register (80H, 81H) is read out. During this time the data line has to be kept in HIGH state and the chip sends out the data. At the end of data transition the master has to generate the stop condition (STO).

Data Sheet 24 2007-02-26

# Bus Data Format in I<sup>2</sup>C Mode

| Table 2-7 | LSB Function |   |   |   |          |   |   |                    |  |  |  |  |  |  |

|-----------|--------------|---|---|---|----------|---|---|--------------------|--|--|--|--|--|--|

| MSB       |              |   |   |   | Function |   |   |                    |  |  |  |  |  |  |

| 1         | 1            | 1 | 0 | 0 | 0        | 0 | 0 | Chip Address Write |  |  |  |  |  |  |

| 1         | 1            | 1 | 0 | 0 | 0        | 0 | 1 | Chip Address Read  |  |  |  |  |  |  |

| Tab | ole 2- | -8 |     | l <sup>2</sup> | C I | 3u: | s V | Vrite | Mod | le 8 | Bit |      |    |    |    |    |     |     |     |    |    |    |     |    |    |     |     |     |

|-----|--------|----|-----|----------------|-----|-----|-----|-------|-----|------|-----|------|----|----|----|----|-----|-----|-----|----|----|----|-----|----|----|-----|-----|-----|

|     | MSB    |    | СНІ |                | DDR | ESS | i   | LSB   |     | MSB  |     | UB A |    | •  |    | ,  | LSB |     | MSB |    |    | D  | ATA | IN |    | LSB |     |     |

| STA | 1      | 1  | 1   | 0              | 0   | 0   | 0   | 0     | ACK | S7   | S6  | S5   | S4 | S3 | S2 | S1 | S0  | ACK | D7  | D6 | D5 | D4 | D3  | D2 | D1 | D0  | ACK | STO |

| Tak | ole 2 | 2-9 |        | l <sup>2</sup> | C   | Bus  | W   | rite | Мо  | de ' | 16 E | 3it |                 |    |    |    |     |     |     |           |     |       |   |     |     |     |

|-----|-------|-----|--------|----------------|-----|------|-----|------|-----|------|------|-----|-----------------|----|----|----|-----|-----|-----|-----------|-----|-------|---|-----|-----|-----|

|     | MSB   | CH  | IIP AI | DDRI           | ESS | (WRI | TE) | LSB  |     | MSB  |      |     | ADDRI<br>08H. 0 | •  |    | ,  | LSB |     | MSB |           | DA  | TA II | N | LSB |     |     |

| STA | 1     | 1   | 1      | 0              | 0   | 0    | 0   | 0    | ACK | S7   | S6   | S5  | S4              | S3 | S2 | S1 | S0  | ACK | D15 | <br>D8 AC | K D | 7 D   | 6 | D0  | ACK | STO |

| Tal | ble | 2    | -10  | )                             |      | <sup>2</sup> C | Вι  | ıs   | Rea | ıd N | /lod | е    |       |      |                |      |    |     |     |     |     |    |       |     |      |     |     |     |     |

|-----|-----|------|------|-------------------------------|------|----------------|-----|------|-----|------|------|------|-------|------|----------------|------|----|-----|-----|-----|-----|----|-------|-----|------|-----|-----|-----|-----|

|     | MS  | SB ( | CHIE | P A [                         | DDRI | ESS            | (WR | ITE) | LSB |      | MSB  | 5    | SUB A |      | ESS (<br>, 81H | REAI | D) | LSB |     |     | MSB | CH | IIP A | DDI | RESS | (RE | AD) | LSB |     |

| STA | . 1 |      | 1    | 1                             | 0    | 0              | 0   | 0    | 0   | ACK  | S7   | S6   | S5    | S4   | S3             | S2   | S1 | S0  | ACK | STA | 1   | 1  | 1     | 0   | 0    | 0   | 0   | 1   | ACK |

| Tal | ble | 2    | -10  | )                             |      | <sup>2</sup> C | Вι  | ıs   | Rea | id N | /lod | e (d | con   | tinı | ıed)           |      |    |     |     |     |     |    |       |     |      |     |     |     |     |

|     | MS  | SB   |      | DATA OUT FROM SUB ADDRESS LSB |      |                |     |      |     |      |      |      |       |      |                |      |    |     |     |     |     |    |       |     |      |     |     |     |     |

|     | R7  | 7    |      |                               | R6   | ,              |     | F    | R5  |      | R    | 4    |       | R3   | 3              |      | R2 |     |     | R1  |     |    | R0    |     |      | ACK | *   | 5   | STO |

<sup>\*</sup> mandatory HIGH

#### 3-wire Bus Mode

In this mode pin 2 (BusMode)= HIGH and Pin 16 (BusData) is in the data input/output pin. Pin 24  $(\overline{\text{EN}})$  is used to activate the bus interface to allow the transfer of data to / from the device. When pin 24  $(\overline{\text{EN}})$  is inactive (HIGH), data transfer is inhibited.

#### Data Transition:

Data transition on pin 16 (BusData) can only occur if the clock BusCLK is LOW. To perform a data transfer the interface has to be enabled. This is done by setting the  $\overline{\text{EN}}$  line to LOW. A serial transfer is done via BusData, BusCLK and  $\overline{\text{EN}}$ . The bit stream needs no chip address.

#### Data Transfer Write Mode:

To start the communication the  $\overline{\text{EN}}$  line has to be set to LOW. The desired sub address byte and data bytes have to follow. The subaddress (00H...0FH) determines which of the data bytes are transmitted. At the end of data transition the  $\overline{\text{EN}}$  must be HIGH.

#### Data transfer Read Mode:

To start the communication in the read mode, the  $\overline{\text{EN}}$  line has to be set to LOW followed by the sub address to read (80H, 81H). Afterwards the device is ready to read out data. At the end of data transition  $\overline{\text{EN}}$  must be HIGH.

Data Sheet 25 2007-02-26