Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

#### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Wireless Components

Gain-controlled IF Amplifier TDA6192 Version 2.1

Specification May 2002

| CONFIDENTIAL Revision History: Current Version: V1.1, October 2000                                                |                 |                                         |  |  |

|-------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|--|--|

| Previous Vers                                                                                                     | ion:target Data | Sheet V1.0, April 2000                  |  |  |

| Page (in previous (in current Version)  Page (in previous (version)  Subjects (major changes since last revision) |                 |                                         |  |  |

| all                                                                                                               | all             | version to V1.1, date to October 2000   |  |  |

| div                                                                                                               | div             | TDA6192-V in VQFN-20 package            |  |  |

| 3-3 ff                                                                                                            | 3-3 ff          | DC levels added                         |  |  |

| 5-2                                                                                                               | 5-2             | Thermal resistance TDA6192-T to 230 K/W |  |  |

| 5-4                                                                                                               | 5-4             | Current consumption: tbfs replaced      |  |  |

| Revision Hist                                                                            | Revision History: Current Version: V1.2, March 2001                                                                                                                                                             |                                                           |  |  |  |

|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|

| Previous Vers                                                                            | ion:target Data                                                                                                                                                                                                 | Sheet V1.1, October 2000                                  |  |  |  |

| Page Page Subjects (major changes since last revision) (in previous (in current Version) |                                                                                                                                                                                                                 |                                                           |  |  |  |

| all                                                                                      | all                                                                                                                                                                                                             | status to preliminary,version to V1.2, date to March 2001 |  |  |  |

| 5-2                                                                                      | 5-2                                                                                                                                                                                                             | Footnote ESD-Protection changed                           |  |  |  |

| 5-4                                                                                      | Current consumption changed, VREF vs temperature: T <sub>amb</sub> changed, IF input voltage: typ value added, Take-over point voltage: typ value added and disable threshold specified, IF AGC voltage deleted |                                                           |  |  |  |

| 5-5                                                                                      | 5-5 Tuner AGC max. slope, Intermodulation, SNR: typ value added, OIP3 added                                                                                                                                     |                                                           |  |  |  |

|                                                                                          | 5-7, 5-8, 5-9                                                                                                                                                                                                   | Diagrams added                                            |  |  |  |

| Revision History: Current Version: V1.3, April 2001 |                                                     |                                                            |  |  |  |

|-----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------|--|--|--|

| Previous Vers                                       | Previous Version:target Data Sheet V1.2, March 2001 |                                                            |  |  |  |

| Page<br>(in previous<br>Version)                    | (in previous   (in current                          |                                                            |  |  |  |

| all                                                 | all                                                 | status to preliminary, version to V1.3, date to April 2001 |  |  |  |

| 3-4                                                 | 3-4                                                 | pins 13, 14: DC level corrected                            |  |  |  |

| 5-4                                                 | 5-4                                                 | Current consumption corrected                              |  |  |  |

| Revision History: Current Version: V2.0, February 2002 |                                 |                                                         |  |

|--------------------------------------------------------|---------------------------------|---------------------------------------------------------|--|

| Previous Version:target Data Sheet V1.3, April 2001    |                                 |                                                         |  |

| Page<br>(in previous<br>Version)                       | Page<br>(in current<br>Version) | Subjects (major changes since last revision)            |  |

| all                                                    | all                             | status to final, version to V2.0, date to February 2002 |  |

| Revision History: Current Version: V2.0, February 2002    |                                        |  |  |

|-----------------------------------------------------------|----------------------------------------|--|--|

| 4-2, 4-3 4-2, 4-3 application circuits changed            |                                        |  |  |

| 5-2                                                       | 5-2 thermal resistance TDA6192-V added |  |  |

| 5-5 5-5 noise figure added, output impedance values added |                                        |  |  |

| Revision History: Current Version: V2.1, May 2002 |                                 |                                              |  |

|---------------------------------------------------|---------------------------------|----------------------------------------------|--|

| Previous Version: Data Sheet V2.0, February 2002  |                                 |                                              |  |

| Page<br>(in previous<br>Version)                  | Page<br>(in current<br>Version) | Subjects (major changes since last revision) |  |

| 3-2, 3-3,<br>3-5, 4-2                             | 3-2, 3-3,<br>3-5, 4-2           | pinning of TDA6192-V changed                 |  |

ABM®, AOP®, ARCOFI®, BA, ARCOFI®-BA, ARCOFI®-SP, DigiTape®, EPIC®-1, EPIC®-S, ELIC®, FALC®54, FALC®56, FALC®-E1, FALC®-LH, IDEC®, IOM®, IOM®-1, IOM®-2, IPAT®-2, ISAC®-P, ISAC®-S, ISAC®-S TE, ISAC®-P TE, ITAC®, IWE®, MUSAC®-A, OCTAT®-P, QUAT®-S, SICAT®, SICOFI®, SICOFI®-2, SICOFI®-4, SICOFI®-4µC, SLICOFI® are registered trademarks of Infineon Technologies AG.

ACE™, ASM™, ASP™, POTSWIRE™, QuadFALC™, SCOUT™ are trademarks of Infineon Technologies AG.

Edition 03.99 Published by Infineon Technologies AG Balanstraße 73, 81541 München

© Infineon Technologies AG 22.05.02. All Rights Reserved.

#### Attention please!

As far as patents or other rights of third parties are concerned, liability is only assumed for components, not for applications, processes and circuits implemented within components or assemblies.

The information describes the type of component and shall not be considered as assured characteristics.

Terms of delivery and rights to change design reserved.

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies AG is an approved CECC manufacturer.

#### **Packing**

Please use the recycling operators known to you. We can also help you – get in touch with your nearest sales office. By agreement we will take packing material back, if it is sorted. You must bear the costs of transport.

For packing material that is returned to us unsorted or which we are not obliged to accept, we shall have to invoice you for any costs incurred.

#### Components used in life-support devices or systems must be expressly authorized for such purpose!

Critical components<sup>1</sup> of the Infineon Technologies AG, may only be used in life-support devices or systems<sup>2</sup> with the express written approval of the Infineon Technologies AG.

- 1 A critical component is a component used in a life-support device or system whose failure can reasonably be expected to cause the failure of that life-support device or system, or to affect its safety or effectiveness of that device or system.

- 2 Life support devices or systems are intended (a) to be implanted in the human body, or (b) to support and/or maintain and sustain human life. If they fail, it is reasonable to assume that the health of the user may be endangered.

**Product Info**

#### **Product Info**

#### **General Description**

The **TDA6192** is a 5 V gain-controlled IF amplifier for digital and analog frontends

#### **Package**

#### **Features**

- Input frequency range 30 to 65 MHz

- Low intermodulation distortion

- 48 dB AGC range

- balanced 1 Vpp buffered output

- Input for gain-control voltage

- Output for tuner AGC with takeover point adjust

- Internal low noise reference voltage

- Full ESD protection

#### **Application**

- IF amplifier in DVB-C, DVB-T, ATSC and ISDB-T frontends with direct IF-sampling.

- IF amplifier in PAL or NTSC frontends

#### **Ordering Information**

| Туре      | Ordering Code               | Package                     |

|-----------|-----------------------------|-----------------------------|

| TDA6192-V | Q67037-A1125(tape and reel) | P-VQFN-20-3<br>(on request) |

| TDA6192-T | Q67037-A1073(tape and reel) | P-TSSOP-16-1                |

Table of Contents

| 1     | Table of Contents                                | . 1-4 |

|-------|--------------------------------------------------|-------|

| 2     | Product Description                              | . 2-1 |

| 2.1   | General Description                              |       |

| 2.2   | Features                                         | . 2-2 |

| 2.3   | Application                                      | . 2-2 |

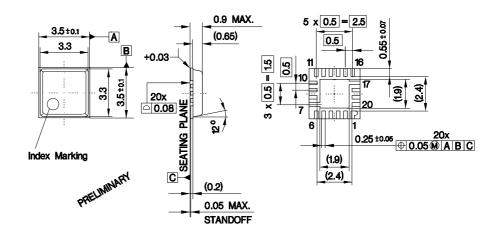

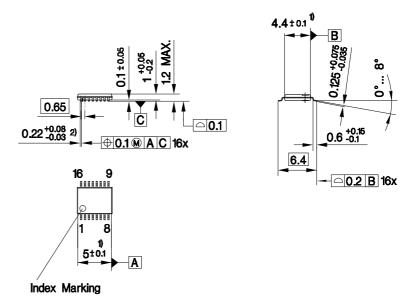

| 2.4   | Package Outlines                                 | . 2-3 |

| 3     | Functional Description                           |       |

| 3.1   | Pin Configuration                                |       |

| 3.2   | Internal Pin Configuration                       |       |

| 3.3   | Block Diagram                                    |       |

| 3.4   | Circuit Description                              | . 3-6 |

| 4     | Applications                                     |       |

| 4.1   | TDA6192-V Evaluation board                       |       |

| 4.2   | TDA6192-T Evaluation board                       | . 4-3 |

| 5     | Reference                                        | . 5-1 |

| 5.1   | Electrical Data                                  |       |

| 5.1.1 | 3                                                |       |

|       | Operating Range                                  |       |

| 5.1.3 | AC/DC Characteristics                            |       |

| 5.2   | Electrical Diagrams                              |       |

|       | Gain vs. IF AGC voltage                          |       |

|       | Intermodulation and output IP3 vs. input voltage |       |

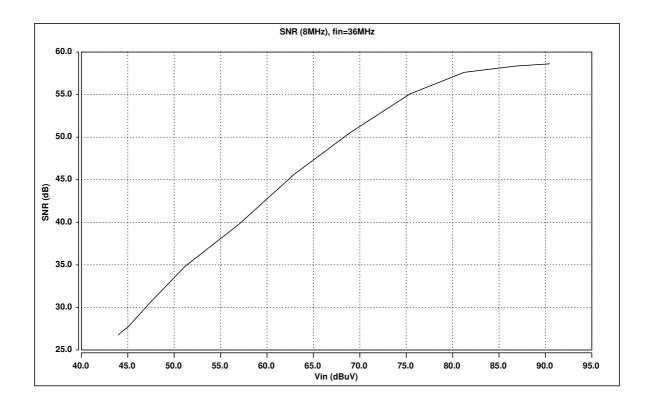

|       | Signal to noise ratio vs. input voltage          |       |

| 5.3   | Measurement Circuit                              |       |

| 5.3.1 | Noise Measurement                                | . 5-9 |

## Product Description

| Con | Contents of this Chapter |       |  |  |  |  |  |

|-----|--------------------------|-------|--|--|--|--|--|

| 2.1 | General Description      | . 2-2 |  |  |  |  |  |

| 2.2 | Features                 | . 2-2 |  |  |  |  |  |

| 2.3 | Application              | . 2-2 |  |  |  |  |  |

| 2.4 | Package Outlines         | 2.2   |  |  |  |  |  |

#### 2.1 General Description

The **TDA6192** device combines a gain-controlled amplifier, an output buffer to drive a following channel decoder IC and a delayed tuner AGC with take-over point adjustment. The gain is controlled by an external voltage.

#### 2.2 Features

- Input frequency range 30 to 65 MHz

- Low intermodulation distortion

- 48 dB AGC range

- balanced 1 Vpp buffered output

- Input for gain-control voltage

- Output for tuner AGC with take-over point adjust

- Internal low noise reference voltage

- Full ESD protection

#### 2.3 Application

- IF amplifier in DVB-C, DVB-T, ATSC and ISDB-T frontends with direct IF- sampling.

- IF amplifier in PAL or NTSC frontends

#### 2.4 Package Outlines

#### P-VQFN-20

#### P-TSSOP-16-1

- 1) Does not include plastic or metal protrusion of 0.15 max. per side

- 2) Does not include dambar protrusion

| Con | Contents of this Chapter   |       |  |  |  |  |

|-----|----------------------------|-------|--|--|--|--|

| 3.1 | Pin Configuration          | . 3-2 |  |  |  |  |

| 3.2 | Internal Pin Configuration | . 3-3 |  |  |  |  |

| 3.3 | Block Diagram              | . 3-5 |  |  |  |  |

| 3 4 | Circuit Description        | 3-6   |  |  |  |  |

#### 3.1 Pin Configuration

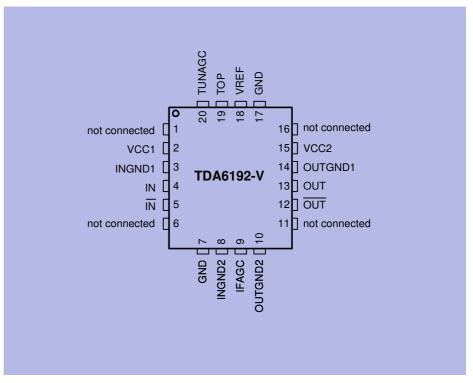

Pin-configVQFN20

Figure 3-1 TDA6192-V, Pin Configuration

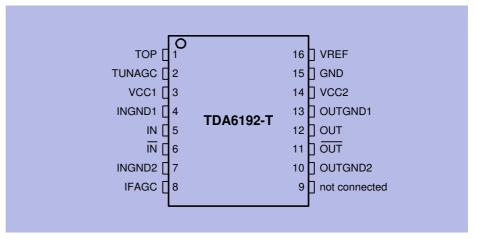

PinconfigT

Figure 3-2 TDA6192-T, Pin Configuration

#### 3.2 Internal Pin Configuration

| Table 3-1     | Table 3-1 Pin Definition and Function |               |                          |            |  |  |  |  |

|---------------|---------------------------------------|---------------|--------------------------|------------|--|--|--|--|

| Pin           | No.                                   | Symbol        | Equivalent I/O-Schematic | Average DC |  |  |  |  |

| TDA<br>6192-V | TDA<br>6192-T                         |               |                          | voltage    |  |  |  |  |

| 1             |                                       | not connected | not connected            | n.a.       |  |  |  |  |

| 2             | 3                                     | VCC1          | supply voltage           | 5.0 V      |  |  |  |  |

| 3             | 4                                     | INGND1        | ground                   | 0.0 V      |  |  |  |  |

| 4             | 5                                     | IN            |                          | 3.6 V      |  |  |  |  |

|               |                                       |               | 4, 5 or 5,6              |            |  |  |  |  |

| 5             | 6                                     | ĪN            | — F                      | 3.6 V      |  |  |  |  |

|               |                                       |               |                          |            |  |  |  |  |

| 6             |                                       | not connected | not connected            | n.a.       |  |  |  |  |

| 7             |                                       | GND           | ground                   | 0.0 V      |  |  |  |  |

| 8             | 7                                     | INGND2        | ground                   | 0.0 V      |  |  |  |  |

| 9             | 8                                     | IFAGC         |                          | 0 to 1.8 V |  |  |  |  |

|               |                                       |               | 8                        |            |  |  |  |  |

|               | 9                                     | not connected | not connected            | n.a.       |  |  |  |  |

| 10            | 10                                    | OUTGND2       | ground                   | 0.0 V      |  |  |  |  |

| 11            |                                       | not connected | not connected            | n.a.       |  |  |  |  |

| Table3-2      | Table3-4      | Table 3-5     |                          |              |

|---------------|---------------|---------------|--------------------------|--------------|

|               |               | Symbol        | Equivalent I/O-Schematic | Average DC   |

| TDA<br>6192-V | TDA<br>6192-T |               |                          | voltage      |

| 12            | 11            | OUT           |                          | 3.2 V        |

|               |               |               |                          |              |

|               |               |               | 13, 14 or 11, 12         |              |

| 13            | 12            | OUT           |                          | 3.2V         |

|               |               |               | $\downarrow$             |              |

|               |               |               | <u> </u>                 |              |

| 14            | 13            | OUTGND1       | ground                   | 0.0 V        |

| 15            | 14            | VCC2          | supply voltage           | 5.0 V        |

| 16            |               | not connected | not connected            | n.a.         |

| 17            | 15            | GND           | ground                   | 0.0 V        |

| 18            | 16            | VREF          |                          | 3.6 V        |

|               |               |               | u                        |              |

|               |               |               | 18 or 16                 |              |

|               |               |               | _                        |              |

|               |               |               | $\bigcirc$               |              |

|               |               |               |                          |              |

|               |               |               |                          |              |

| 19            | 1             | TOP           |                          | 0.2 to 1.6 V |

|               |               |               | П                        |              |

|               |               |               | <del> </del>             |              |

|               |               |               | 19 or 1                  |              |

|               |               |               |                          |              |

|               |               |               |                          |              |

| 20            | 2             | TUNAGC        | 90.00                    | 0.5 to 5 V   |

|               |               |               | 20 or 2                  |              |

|               |               |               | الم                      |              |

|               |               |               |                          |              |

#### 3.3 Block Diagram

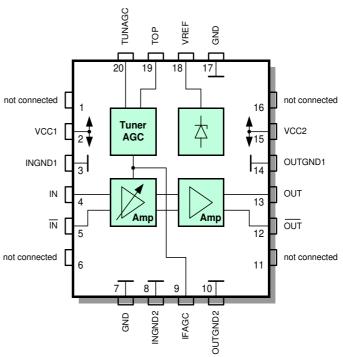

BlockdiagramVQFN20

Figure 3-3 TDA6192-V, Block Diagram

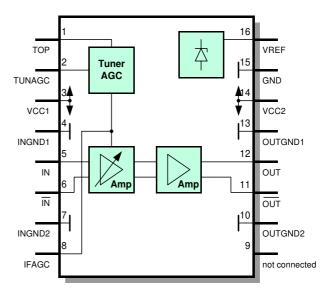

BlockdiagramT

Figure 3-4 TDA6192-T, Block Diagram

#### 3.4 Circuit Description

The **TDA6192** device combines an AGC amplifier, an output buffer to drive a following demodulator IC , a delayed tuner AGC with take-over point adjustment, and a low noise reference source VREF. The gain of the AGC amplifier is controlled by an external voltage. VREF is used as a reference for the take-over point adjustment of the tuner AGC voltage. TUNAGC is an open-collector output.

## 4 Applications

| Con | tents of this Chapter      |     |

|-----|----------------------------|-----|

|     |                            |     |

| 4.1 | TDA6192-V Evaluation board | 4-2 |

| 4.2 | TDA6192-T Evaluation board | 4-3 |

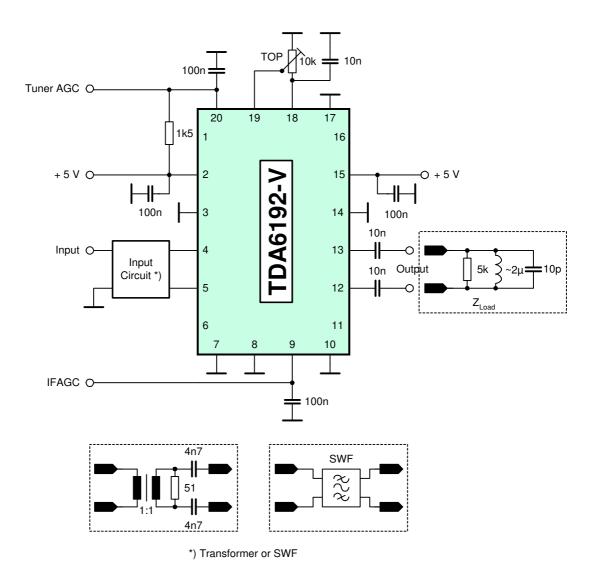

#### 4.1 TDA6192-V Evaluation board

Application Circuit VQFN20

Figure 4-1 TDA6192-V Evaluation board, circuit diagram

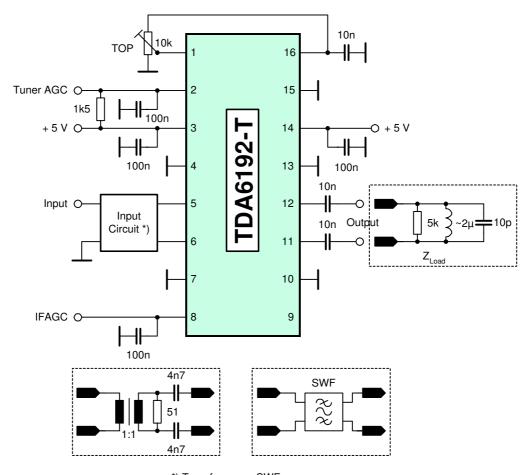

#### 4.2 TDA6192-T Evaluation board

\*) Transformer or SWF

Application Circuit T

Figure 4-2 TDA6192-T Evaluation board, circuit diagram

# 5.1 Electrical Data. 5-2 5.1.1 Absolute Maximum Ratings 5-2 5.1.2 Operating Range 5-3 5.1.3 AC/DC Characteristics 5-4 5.2 Electrical Diagrams 5-6 5.2.1 Gain vs. IF AGC voltage 5-6 5.2.2 Intermodulation and output IP3 vs. input voltage 5-7 5.2.3 Signal to noise ratio vs. input voltage 5-8 5.3 Measurement Circuit 5-9 5.3.1 Noise Measurement 5-9

#### 5.1 Electrical Data

#### 5.1.1 Absolute Maximum Ratings

#### **WARNING**

The maximum ratings may not be exceeded under any circumstances, not even momentarily and individually, as permanent damage to the IC may result.

| Table 5-1 Absolute Maximum Ratings                 |                       |              |                  |      |         |  |  |

|----------------------------------------------------|-----------------------|--------------|------------------|------|---------|--|--|

| Parameter 1).                                      | Symbol                | Limit Values |                  | Unit | Remarks |  |  |

|                                                    |                       | min max      |                  |      |         |  |  |

| Supply voltage                                     | $V_{CC1,}V_{CC2}$     | -0.3         | 6                | V    |         |  |  |

| Supply voltage difference                          | $_{\Delta}$ VCC1,VCC2 | -0.3         | +0.3             | V    |         |  |  |

| Ambient temperature TDA6192-V                      | T <sub>AMB</sub>      | -20          | +85              | °C   |         |  |  |

| Ambient temperature TDA6192-T                      | T <sub>AMB</sub>      | -20          | +70              | °C   |         |  |  |

| Junction temperature                               | T <sub>J</sub>        |              | +125             | °C   |         |  |  |

| Storage temperature                                | T <sub>S</sub>        | -40          | +125             | °C   |         |  |  |

| Thermal resistance TDA6192-V (junction to ambient) | R <sub>thJA</sub>     |              | 70               | K/W  |         |  |  |

| Thermal resistance TDA6192-T (junction to ambient) | R <sub>thJA</sub>     |              | 230              | K/W  |         |  |  |

| IF input                                           | V <sub>IF/IF</sub>    | -0.3         | 4                | V    |         |  |  |

| IF output                                          | I <sub>OUT/OUT</sub>  | -5           | 1                | mA   |         |  |  |

| AGC input                                          | V <sub>IFAGV</sub>    | -0.3         | V <sub>CC1</sub> | V    |         |  |  |

| Tuner AGC take-over point adjust                   | V <sub>TOP</sub>      | -0.3         | V <sub>CC1</sub> | V    |         |  |  |

| Tuner AGC output                                   | V <sub>TUNAGC</sub>   | -0.3         | 6                | V    |         |  |  |

| ESD-Protection <sup>2).</sup>                      |                       |              |                  |      |         |  |  |

| all pins                                           | V <sub>ESD</sub>      | -2           | +2               | kV   | НВМ     |  |  |

<sup>1).</sup> All values are referred to ground (pin), unless stated otherwise.

Currents with a positive sign flow into the pin and currents with a negative sign flow out of pin.

<sup>2).</sup> According to EIA/JESD22-A114-B (HBM incircuit test), as a single device incircuit contact discharge test.

#### 5.1.2 Operating Range

Within the operational range the IC operates as described in the circuit description. The AC / DC characteristic limits are not guaranteed.

| Table 5-2 Operating Range     |                                        |              |      |      |                 |      |  |  |

|-------------------------------|----------------------------------------|--------------|------|------|-----------------|------|--|--|

| Parameter                     | Symbol                                 | Limit Values |      | Unit | Test Conditions | Item |  |  |

|                               |                                        | min          | max  |      |                 |      |  |  |

| Supply voltage                | V <sub>CC1</sub> ,<br>V <sub>CC2</sub> | 4.5          | 5.5  | V    |                 |      |  |  |

| Frequency range               | f                                      | 30           | 65   | MHz  |                 |      |  |  |

| Ambient temperature TDA6192-V | T <sub>AMB</sub>                       | - 20         | + 85 | °C   |                 |      |  |  |

| Ambient temperature TDA6192-T | T <sub>AMB</sub>                       | - 20         | + 70 | °C   |                 |      |  |  |

#### 5.1.3 AC/DC Characteristics

AC / DC characteristics involve the spread of values guaranteed in the specified supply voltage and ambient temperature range. Typical characteristics are the median of the production.

| Table 5-3 AC/DC Cha                               | racteristics wi        | th T <sub>AMB</sub> = 2 | 25 °C, VCC | 1 = VCC2 =      | 5 V             |                                                                    |  |

|---------------------------------------------------|------------------------|-------------------------|------------|-----------------|-----------------|--------------------------------------------------------------------|--|

|                                                   | Symbol                 | Limit Values            |            | Unit            | Test Conditions | L Item                                                             |  |

|                                                   |                        | min                     | typ        | max             |                 |                                                                    |  |

| Power supply, referen                             | ce voltage             |                         |            |                 |                 |                                                                    |  |

| Current consumption                               | I <sub>CC1</sub>       |                         | 18         | 22              | mA              | max. gain                                                          |  |

| Current consumption                               | I <sub>CC1</sub>       |                         | 10         | 12              | mA              | min. gain                                                          |  |

| Current consumption                               | I <sub>CC2</sub>       |                         | 9          |                 | mA              |                                                                    |  |

| Reference voltage                                 | V <sub>REF</sub>       | 3.3                     | 3.6        | 3.9             | V               |                                                                    |  |

| VREF line regulation                              | $\Delta V_{REFLINE}$   |                         |            | 30              | mV              | V <sub>CC1</sub> = V <sub>CC2</sub> = 4.5 to 5.5 V                 |  |

| VREF load regulation                              | $\Delta V_{REFLOAD}$   |                         |            | 30              | mV              | I <sub>VREF</sub> = -0.5 to 0.5 mA                                 |  |

| VREF vs temperature                               | $\Delta V_{REFTEMP}$   | -30                     | 10         | 30              | mV              | T <sub>AMB</sub> = -20 to 70 °C                                    |  |

| AGC amplifier, tuner A                            | AGC                    |                         |            |                 |                 |                                                                    |  |

| Static characteristics                            |                        |                         |            |                 |                 |                                                                    |  |

| IF input voltage                                  | $V_{IF/\overline{IF}}$ |                         | $V_{REF}$  |                 |                 |                                                                    |  |

| Take-over point volt-<br>age                      | V <sub>TOP</sub>       | 0                       |            | 2               | V               | Tuner AGC is enabled                                               |  |

|                                                   | V <sub>TOP</sub>       | 3.0                     |            | V <sub>CC</sub> | V               | Tuner AGC is dis-<br>abled                                         |  |

| Take-over point dis-<br>able threshold            |                        | 2.0                     | 2.3        | 3.0             | V               |                                                                    |  |

| Take-over point cur-<br>rent                      | I <sub>TOP</sub>       | -1                      |            | 1               | μΑ              | $V_{TOP} = 0 V$                                                    |  |

| Tuner AGC current                                 | ITUNAGC                | 2.5                     | 3.5        | 5               | mA              | $V_{TUNAGC} = 0.5 V,$<br>$V_{IFAGC} = 1.0 V,$<br>$V_{TOP} = 1.5 V$ |  |

| Tuner AGC current                                 | ITUNAGC                | 0                       |            | 10              | μΑ              | $V_{TUNAGC} = 6 V,$<br>$V_{IFAGC} = 1.0 V,$<br>$V_{TOP} = 0.5 V$   |  |

| Dynamic characteristics                           |                        |                         |            |                 |                 |                                                                    |  |

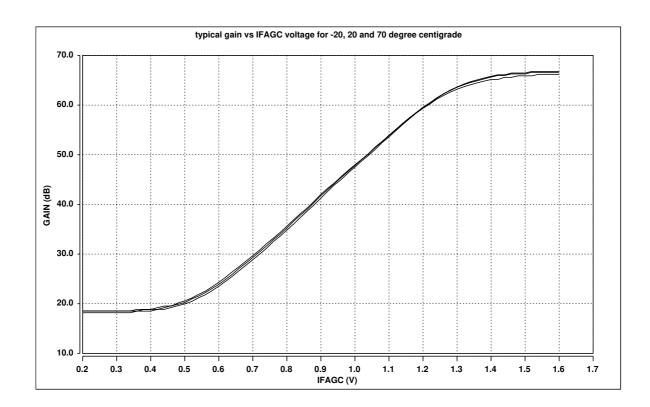

| Voltage gain,                                     | G <sub>max</sub>       | 63                      | 67         | 71              | dB              | V <sub>IFAGC</sub> ≥ 1.6 V                                         |  |

| see 5.2.1 Gain vs. IF<br>AGC voltage on page<br>6 | G <sub>min</sub>       |                         | 19         |                 | dB              | V <sub>IFAGC</sub> ≤ 0.2 V                                         |  |

| Table 5-4 AC/DC Cha                                                                                      |                                               | th $T_{AMB} = 2$ | 25 °C, V <sub>CC</sub> | $_1 = V_{CC2} =$ |      |                                                                                                                                                                                                                                                                                                                                                                                  |        |

|----------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------|------------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

|                                                                                                          | Symbol                                        | L                | imit Value             | s                | Unit | Test Conditions                                                                                                                                                                                                                                                                                                                                                                  | L Item |

|                                                                                                          |                                               | min              | typ                    | max              |      |                                                                                                                                                                                                                                                                                                                                                                                  |        |

| Maximum IF input<br>level                                                                                | V <sub>IF/IF</sub>                            | 88               | 92                     | 96               | dΒμV | min. gain, $f_{IF/\overline{IF}} = 36 \text{ MHz (sine)},$ $V_{IFAGC} = 0.2 \text{ V},$ $V_{OUT/\overline{OUT}} = 1 \text{ V}_{pp}$                                                                                                                                                                                                                                              |        |

| Minimum IF input<br>level                                                                                | V <sub>IF/IF</sub>                            |                  | 44                     |                  |      | max. gain,<br>$f_{IF/\overline{IF}}$ = 36 MHz (sine),<br>$V_{IFAGC}$ = 1.6 V,<br>$V_{OUT/\overline{OUT}}$ = 1 $V_{pp}$                                                                                                                                                                                                                                                           |        |

| Input impedance                                                                                          | R <sub>IF/IF</sub>                            | 1.5              | 2                      | 2.5              | kΩ   | f <sub>IF/IF</sub> = 36 MHz, paral-                                                                                                                                                                                                                                                                                                                                              |        |

|                                                                                                          | C <sub>IF/IF</sub>                            |                  | 1.5                    |                  | pF   | lel equivalent circuit                                                                                                                                                                                                                                                                                                                                                           |        |

| Tuner AGC max.<br>slope                                                                                  | ΔI <sub>TUNAGC</sub> /<br>ΔV <sub>IFAGC</sub> | 25               | 36                     | 50               | mA/V | $V_{IFAGC} = 0.9 \text{ to } 1.1 \text{ V},$<br>$V_{TOP} = 1.0 \text{ V},$<br>$V_{TUNAGC} = 0.5 \text{ V}$                                                                                                                                                                                                                                                                       |        |

| Low end cutoff frequency (-1 dB)                                                                         | fL                                            |                  |                        | 25               | MHz  | $V_{IF/\overline{IF}} = 60 \text{ dB}\mu V_{,}$<br>$R_{LOAD} \ge 5 \text{ k}\Omega,$                                                                                                                                                                                                                                                                                             |        |

| High end cutoff fre-<br>quency (-1 dB)                                                                   | f <sub>H</sub>                                | 65               |                        |                  | MHz  | $C_{LOAD} \le 1.5 \text{ pF},$<br>$V_{OUT/\overline{OUT}} = 1 \text{ V}_{pp} \text{ at}$<br>$f_{IF/\overline{IF}} = 36 \text{ MHz (sine)}$                                                                                                                                                                                                                                       |        |

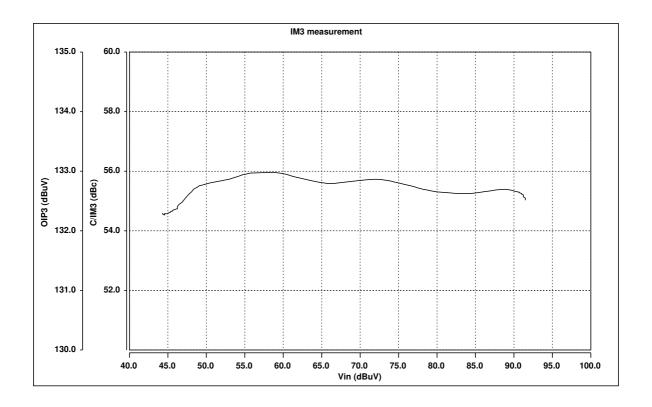

| Intermodulation,<br>see 5.2.2 Intermodu-<br>lation and output IP3<br>vs. input voltage on<br>page 7      | C/IM3                                         | 50               | 56                     |                  | dBc  | $\begin{split} f_{IF/\overline{IF}1} &= 37 \text{ MHz}, \\ f_{IF/\overline{IF}2} &= 38 \text{ MHz}, \\ V_{IF/\overline{IF}1} &= 60 \text{ dB}\mu\text{V}, \\ V_{IF/\overline{IF}2} &= 60 \text{ dB}\mu\text{V} \\ R_{LOAD} &\geq 5 \text{ k}\Omega, \\ C_{LOAD} &\leq 10 \text{ pF}, \\ L_{LOAD} &\sim 2 \mu\text{H}, \\ V_{OUT/\overline{OUT}} &= 1 \text{ V}_{pp} \end{split}$ |        |

| Third order output intercept point, see 5.2.2 Intermodulation and output IP3 vs. input voltage on page 7 | OIP3                                          |                  | 133                    |                  | dΒμV | $\begin{split} f_{IF/\overline{IF}1} &= 37 \text{ MHz}, \\ f_{IF/\overline{IF}2} &= 38 \text{ MHz}, \\ V_{IF/\overline{IF}1} &= 60 \text{ dB}\mu V, \\ V_{IF/\overline{IF}2} &= 60 \text{ dB}\mu V, \\ R_{LOAD} &\geq 5 \text{ k}\Omega, \\ C_{LOAD} &\leq 10 \text{ pF}, \\ L_{LOAD} &\sim 2 \mu H, \\ V_{OUT/\overline{OUT}} &= 1 V_{pp} \end{split}$                          |        |

| Signal to noise ratio,<br>see 5.2.3 Signal to<br>noise ratio vs. input<br>voltage on page 8              | SNR                                           | 35               | 43                     |                  | dB   | $\begin{split} f_{IF/\overline{IF}} &= 36 \text{ MHz (sine)}, \\ V_{IF/\overline{IF}} &= 60 \text{ dB}\mu\text{V}, \\ V_{OUT/\overline{OUT}} &= 1 \text{ V}_{pp,} \\ \text{BW} &= 8 \text{ MHz} \end{split}$                                                                                                                                                                     |        |

| Noise figure                                                                                             |                                               |                  | 10                     | 12               | dB   | max. gain, see 5.3.1<br>on page 9                                                                                                                                                                                                                                                                                                                                                |        |

| Output impedance                                                                                         | R <sub>IF/IF</sub>                            |                  | 60                     | 100              | Ω    | $f_{OUT/\overline{OUT}} = 36 \text{ MHz},$                                                                                                                                                                                                                                                                                                                                       |        |

|                                                                                                          | L <sub>IF/IF</sub>                            |                  | 33                     |                  | nH   | series equivalent cir-<br>cuit                                                                                                                                                                                                                                                                                                                                                   |        |

#### 5.2 Electrical Diagrams

#### 5.2.1 Gain vs. IF AGC voltage

#### 5.2.2 Intermodulation and output IP3 vs. input voltage

#### 5.2.3 Signal to noise ratio vs. input voltage