Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### Delta/sigma cascade 20 bit stereo DAC

#### **Features**

- 20-bit resolution single ended output

- Analog reconstruction third order Chebyshev filter

- I<sup>2</sup>S input data format

- On chip PLL

- System clock: 64 Fs

- 2 output channels

- 0.9 VRMs single ended output dynamic

- 3.3 V power supply

- Reset

- Sampling rate 36 kHz to 48 kHz

The TDA7535 is a stereo, digital-to-analco converter designed for audio application including digital interpolation filter a third order multi-bit Delta-Sigma DAC, a third order Chebyshev's reconstruction tilter and a differential to single ended outou converter. This device is fabricated in highly advanced CMOS, where high speed precision analog circuits are combined with high density logic circuits. The TDA7535, according to standard audio converters, can accept any I<sup>2</sup>S data format.

The TDA7535 is available in SO14 package. The total power consumption is less than 75 mW.

TDA7535 is suitable for a wide variety of applications where high performance are required. Its low cost and single 3.3 V power supply make it ideal for several applications, such as CD players, MPEG audio, MIDI applications, CD-ROM drives, CD-Interactive, digital radio applications and so on. An evaluation board is available to perform measurement and to make listening tests.

Table 1. Device summary

| Order code   | Package | Packing       |

|--------------|---------|---------------|

| TDA7535      | SO14    | Tube          |

| TDA7535013TR | SO14    | Tape and reel |

Contents TDA7535

### **Contents**

| 1     | Block diagram and pin description                            | . 3 |

|-------|--------------------------------------------------------------|-----|

| 2     | Electrical specification                                     | . 4 |

|       | 2.1 Absolute maximum ratings                                 | . 4 |

|       | 2.2 Thermal data                                             | . 4 |

|       | 2.3 Recommended DC operating conditions                      | . 4 |

|       | 2.4 Power consumption                                        | . 5 |

|       | <ul><li>2.4 Power consumption</li></ul>                      | . 5 |

|       | 2.6 Low voltage CMOS interface DC electrical characteristics | . 5 |

|       | 2.7 DAC electrical characteristics                           |     |

| 3     | I <sup>2</sup> S interface                                   | . 7 |

| 4     | Application circuit                                          | . 9 |

| 5     | Package information                                          | 10  |

| 6     | Revision history                                             | 11  |

| Obsol | leje Produlce                                                |     |

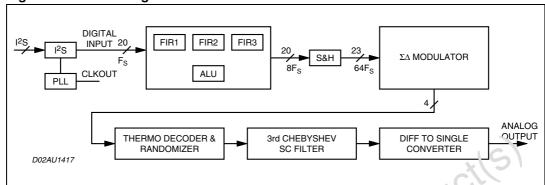

## 1 Block diagram and pin description

Figure 1. Block diagram

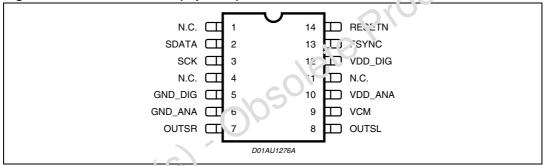

Figure 2. Pin connection (top view)

Table 2. Pin function.

|      | Pin # | Pin name | Input/output power | Description                          |

|------|-------|----------|--------------------|--------------------------------------|

|      | 2011  | N.C.     | -                  | -                                    |

|      | 2     | SDATA    | I                  | I2S digital data input               |

| 0/8  | 3     | SCK      | I                  | I2S clock input                      |

|      | 4     | N.C.     | -                  | -                                    |

| 0105 | 5     | GND_DIG  | Р                  | Digital ground                       |

| Ob   | 6     | GND_ANA  | Р                  | Analog ground                        |

|      | 7     | OUTSR    | 0                  | Right channel single ended output    |

|      | 8     | OUTSL    | 0                  | Left channel single ended output     |

|      | 9     | VCM      | Р                  | Reference 1.65 V externally filtered |

|      | 10    | VDD_ANA  | Р                  | Analog 3.3 V supply                  |

|      | 11    | N.C.     | -                  | -                                    |

|      | 12    | VDD_DIG  | Р                  | Digital 3.3 V-supply                 |

|      | 13    | FSYNC    | I                  | I2S Left-right channel selector      |

|      | 14    | RESETN   | I                  | Reset (active low)                   |

## 2 Electrical specification

### 2.1 Absolute maximum ratings

Table 3. Absolute maximum ratings

| Symbol                             | Parameter                            |                   | Value                          | Unit       |

|------------------------------------|--------------------------------------|-------------------|--------------------------------|------------|

| V <sub>DD</sub><br>V <sub>CC</sub> | Power supplies                       | Digital<br>Analog | -0.5 to +4.6<br>-0.5 to +4.6   | V<br>V     |

| V <sub>aio</sub>                   | Analog input and output voltage      |                   | -0.5 to (V <sub>CC</sub> +0.5) | V          |

| V <sub>dio</sub>                   | Digital input and output voltage     |                   | -0.5 to (V <sub>DD</sub> +0.5) | V          |

| V <sub>di5</sub>                   | Digital input voltage (5 V tolerant) |                   | -0.5 to 6.5                    | <b>9</b> V |

| T <sub>j</sub>                     | Operating junction temperature range |                   | -40 to 12.5                    | °C         |

| T <sub>stg</sub>                   | Storage temperature                  |                   | -55 tc 150                     | °C         |

Warning: Operation at or beyond these limit nay result in permanent

damage to the device. Normal operation is not guaranteed at

these extremes.

### 2.2 Thermal data

Table 4. Thermal data

| Symbol                | Parameter                                  | Value | Unit |

|-----------------------|--------------------------------------------|-------|------|

| R <sub>th j-cmb</sub> | Thermal resistance junction to ambient (1) | 85    | °C/W |

<sup>1.</sup> in still air.

### 2.3 Recommended DC operating conditions

Table 5.

Recommended DC operating conditions

| Symbol          | Parameter                          | Test condition | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------------|----------------|------|------|------|------|

| $V_{DD}$        | 3.3 V digital power supply voltage |                | 3.15 | 3.3  | 3.45 | V    |

| V <sub>CC</sub> | 3.3 V analog power supply voltage  |                | 3.15 | 3.3  | 3.45 | V    |

### 2.4 Power consumption

Table 6. Power consumption

| Symbol          | Parameter             | Test condition                          | Min. | Тур. | Max. | Unit |

|-----------------|-----------------------|-----------------------------------------|------|------|------|------|

| I <sub>dd</sub> | Total maximum current | Power supply @ 3.3 V and $T_j = 125$ °C |      | 21.5 | 25   | mA   |

### 2.5 General interface electrical characteristics

Table 7. General interface electrical characteristics

| Symbol               | Parameter                                       | Test condition               | Min. | Тур. | Max. | Unit |

|----------------------|-------------------------------------------------|------------------------------|------|------|------|------|

| l <sub>il</sub>      | Low level input current without pull-up device  | $V_i = 0 \ V^{(1)}$          |      |      | C.T. | μА   |

| l <sub>ih</sub>      | High level input current without pull-up device | $V_i = V_{dd}^{(1)}$         | - 10 | 29/  | 1    | μА   |

| I <sub>latchup</sub> | I/O latch-up current                            | $V < 0 V, V > V_{dd}$        | 250  |      |      | mA   |

| V <sub>esd</sub>     | Electrostatic protection                        | Leakage, 1 μA <sup>(2)</sup> | 2000 |      |      | V    |

<sup>1.</sup> The leakage currents are generally very small, <1nA. The value given here, 1 nA is the maximum that can occur after an Electrostatic Stress on the pin.

### 2.6 Low voltage CMOS interface DC electrical characteristics

Table 8. Low voltage CMOS interface DC electrical characteristics

| Symbol            | Parameter                   | Test Condition | Min.               | Тур. | Max.               | Unit |

|-------------------|-----------------------------|----------------|--------------------|------|--------------------|------|

| V <sub>il</sub>   | Low Level Input (of age     |                |                    |      | 0.2*V <sub>d</sub> | V    |

| V <sub>ih</sub>   | High .svel Input Voltage    |                | 0.8*V <sub>d</sub> |      |                    | ٧    |

| V <sub>hy</sub> , | Sc/imitt trigger hysteresis |                | 0.8                |      |                    | V    |

<sup>2.</sup> Human body model.

#### **DAC** electrical characteristics 2.7

Table 9. **DAC** electrical characteristics

V<sub>dd</sub> = 3.3 V; T<sub>amb</sub> = 25 °C; Input signal frequency = sinus wave generated by audio precision Sys.2; Input signal amplitude (see notes); Noise integration bandwidth = 20 Hz to 22 kHz (A- weighted)

| Parameter                  | Test condition                                       | Min.              | Тур. | Max.  | Unit |

|----------------------------|------------------------------------------------------|-------------------|------|-------|------|

|                            | @0 dB                                                |                   | 89   |       | dB   |

| Noise + distortion (1)     | @-6 dBb                                              |                   | 94   |       | dB   |

| Noise + distortion         | @-40 dB                                              |                   | 96   |       | dB   |

|                            | @-60 dB                                              |                   | 96   |       | dB   |

| Total harmonic distortion  | see note (2)                                         | 70 <sup>(3)</sup> | 94   |       | åВ   |

| Dynamic range              | see note (4)                                         | 84 <sup>(5)</sup> | 96   |       | dB   |

| Crosstalk                  | see note <sup>(6)</sup>                              |                   | -95  | 100   | dB   |

| Full scale output voltage  | V <sub>dd</sub> = 3.15 to 3.45 V<br>Full scale input | 0.8               | 0.9  | 1.0   | Vrms |

| Input sampling rate        |                                                      | 36                |      | 48    | kHz  |

| Passband ripple            |                                                      | 8                 | 0.12 |       | dB   |

| Stopband                   | @ 3dB<br>@ 90dB<br>44.1kHz sam bling rate            | 21.53             |      | 24.80 | kHz  |

| Interchannel gain mismatch |                                                      | ·                 | 0.05 | 0.1   | dB   |

<sup>1.</sup> It is the ratio between the mɛ xi. ເພດ ກ່າງput signal and the integration of the in-band noise after deducing the power of signal fundameກະປາ. 't depends on the input signal amplitude. In this case 0dB means full scale digital, 1 kHz frequency used.

<sup>2.</sup> It is the ratio of the rams value of the signal fundamental component at 0 dB (full scale digital) to the rms value of all of the harmonic components in the band.

<sup>3.</sup> By considion to beuch results. ATE limits are 60 dB.

בים און signal, with 60dB added to compensate fo . عy correlation to beuch results. ATE limits are 80 dB.

ε. Left channel on with 0dB/1kHz input signal, Right channel on with DC input signal. 4. Measured using the SNR at -60dB input signal, with 60dB added to compensate for small input signal.

TDA7535 I<sup>2</sup>S interface

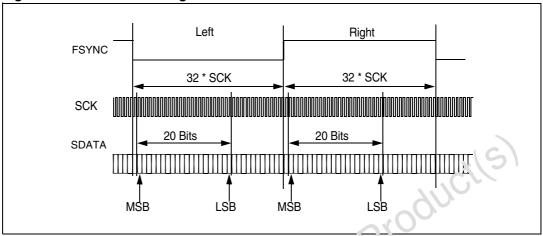

# 3 I<sup>2</sup>S interface

Figure 3. I<sup>2</sup>S interface diagram

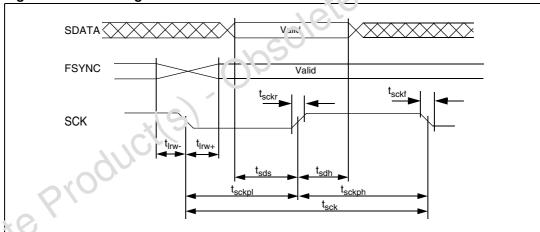

Figure 4. I<sup>2</sup>S timings

Table 10 Timing characteristics

| iming              | Description                                                        | Min.                             | Max.                             | Unit |

|--------------------|--------------------------------------------------------------------|----------------------------------|----------------------------------|------|

| t <sub>sck</sub>   | Clock cycle <sup>(1)</sup>                                         | 1/(64*Fs) - 150ps <sub>RMS</sub> | 1/(64*Fs) + 150ps <sub>RMS</sub> | ns   |

| t <sub>sckpl</sub> | SCK phase low                                                      | 0.5*t <sub>sck</sub> - 1%        | 0.5*t <sub>sck</sub> +1%         | ns   |

| t <sub>sckph</sub> | SCK phase high                                                     | 0.5*t <sub>sck</sub> - 1%        | 0.5*t <sub>sck</sub> +1%         | ns   |

| t <sub>lrw-</sub>  | FSYNC switching time window before SCK falling edge <sup>(2)</sup> | 0                                | 0.125*t <sub>sck</sub> -10       | ns   |

| t <sub>lrw+</sub>  | FSYNC switching time window after SCK falling edge <sup>(2))</sup> | 0                                | 0.125*t <sub>sck</sub> -10       | ns   |

| t <sub>sds</sub>   | SDATA setup time                                                   | 60                               |                                  | ns   |

| t <sub>sdh</sub>   | SDATA hold time                                                    | 30                               |                                  | ns   |

I<sup>2</sup>S interface TDA7535

Table 10. Timing characteristics (continued)

| Timing            | Description   | Min. | Max. | Unit |

|-------------------|---------------|------|------|------|

| t <sub>sckr</sub> | SCK rise time |      | 22   | ns   |

| t <sub>sckf</sub> | SCK fall time |      | 20   | ns   |

- 1. SCK clock defines the Fs, being the Sample Rate. This input clock needs a jitter below  $\sim$ 212ps<sub>RMS</sub>.

- 2. FSYNC switches inside the time window as specified w.r.t. to falling edge of SCK.

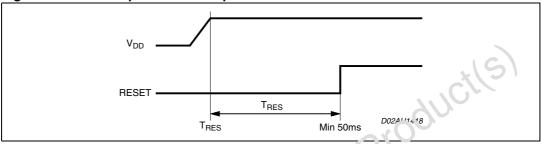

Figure 5. Power up and reset sequence

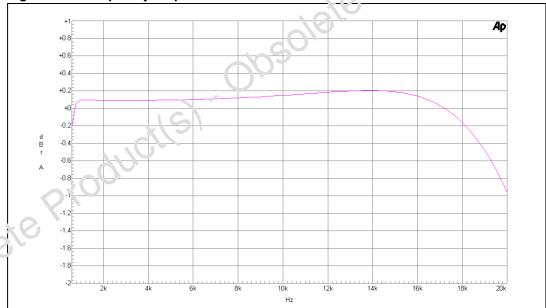

Figure 6. Frequency response

TDA7535 Application circuit

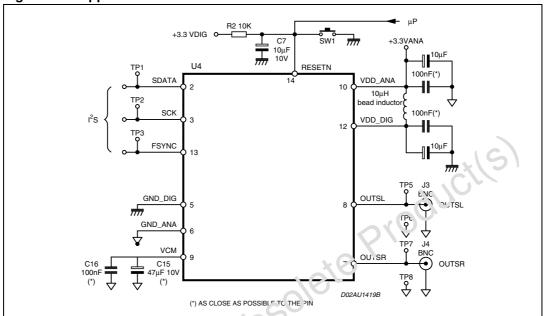

# 4 Application circuit

Obsolete Product(s)

Figure 7. Application circuit

**5**//

Package information TDA7535

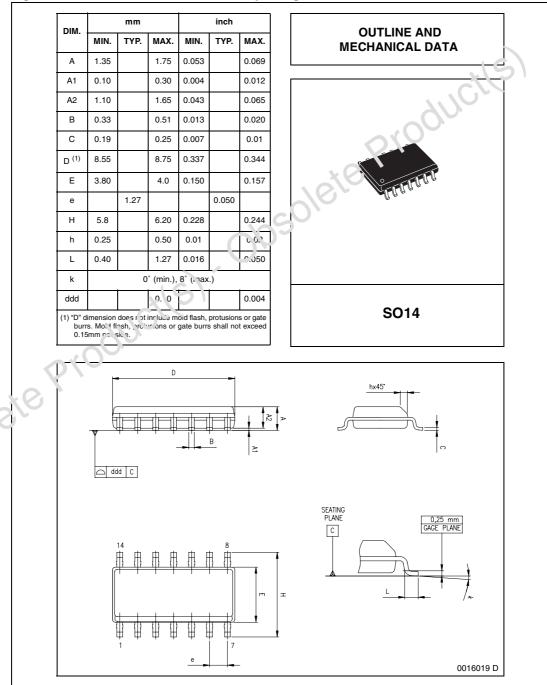

### 5 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <u>www.st.com</u>.

$\mathsf{ECOPACK}^{\mathbb{R}}$  is an ST trademark.

Figure 8. SO14 mechanical data and package dimensions

TDA7535 Revision history

# 6 Revision history

Table 11. Document revision history

|                     | Date         | Revision | Changes                                                                               |

|---------------------|--------------|----------|---------------------------------------------------------------------------------------|

|                     | 13-Dec- 2003 | 5        | Initial release.                                                                      |

|                     | 21-Dec- 2005 | 6        | Update electrical characteristics. Add revision history table.                        |

|                     | 03-Feb-2006  | 7        | Updated max. value of t <sub>sckr</sub> and t <sub>sck</sub> t parameter on page 5/9. |

|                     | 06-Feb-2009  | 8        | Document reformatted. Updated Section 5: Package information on page 10.              |

| Obsolete Producits) |              |          |                                                                                       |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its suinsidia. 'ec.' (ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and sen ice's described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and solvices described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property Liquis is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a training arms to evering the use in any manner whatsoever of such third party products or services or any intellectual property contained under this document. If any part of this document refers to any third party products or services or any intellectual property contained under this document. If any part of this document refers to any third party products or services or any intellectual property contained under this document. If any part of this document refers to any third party products or services or any intellectual property contained under this document. If any part of this document refers to any third party products or services or any intellectual property contained under this document. If any part of this document under this document is a grant by ST for the use of such third party products or services or any intellectual property contained under this document.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE ANCIOR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNE'SE FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN VIRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARHANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCT'S OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PF OP ENTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of S. p oducts with provisions different from the statements and/or technical features set forth in this document shall immediately void any war and granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liabi. To S.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2009 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com