# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

INTEGRATED CIRCUITS

Product specification Supersedes data of 2002 Nov 15

2003 Feb 18

### TDA8007B

| CONTEN | TS                     |

|--------|------------------------|

| 1      | FEATURES               |

| 2      | APPLICATIONS           |

| 3      | GENERAL DESCRIPTION    |

| 4      | QUICK REFERENCE DATA   |

| 5      | ORDERING INFORMATION   |

| 6      | BLOCK DIAGRAM          |

| 7      | PINNING                |

| 8      | FUNCTIONAL DESCRIPTION |

### 8.1 Interface control

- 8.1.1 Multiplexed configuration8.1.2 Non-multiplexed configuration

- 8.1.2 Non-multiplexed co8.2 Control registers

- 8.2.1 General registers

- 8.2.2 ISO UART registers

- 8.2.3 Card registers

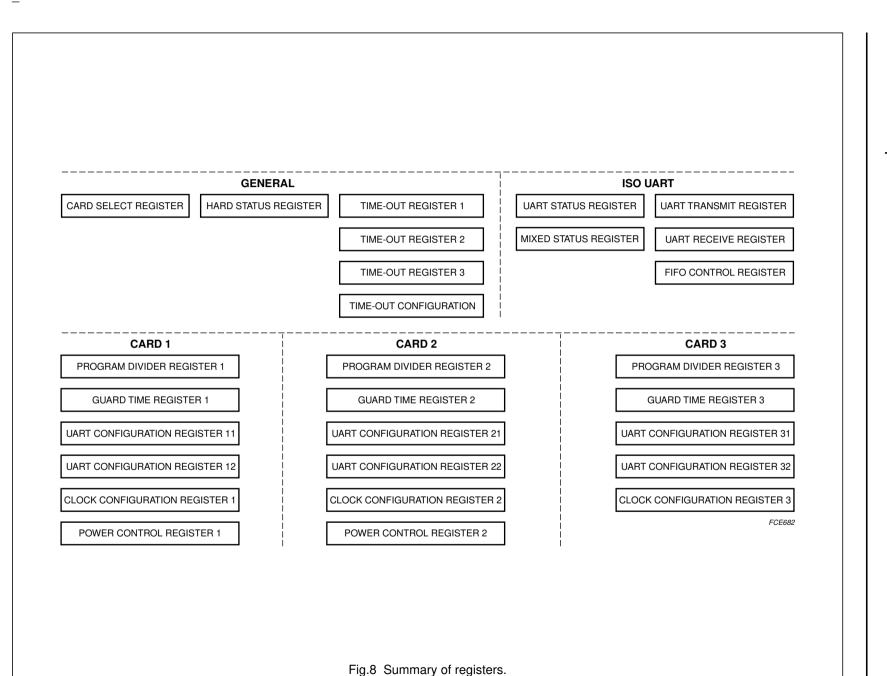

- 8.2.4 Register summary

- 8.3 Supplies and voltage supervisor

- 8.4 Step-up converter

- 8.5 ISO 7816 security

- 8.6 Activation sequence

- 8.7 Deactivation sequence

- 9 LIMITING VALUES

- 10 HANDLING

- 11 THERMAL CHARACTERISTICS

- 12 CHARACTERISTICS

- 13 TIMING

- 14 APPLICATION INFORMATION

15 PACKAGE OUTLINE 16 SOLDERING 16.1 Introduction to soldering surface mount packages 16.2 **Reflow soldering** 16.3 Wave soldering 16.4 Manual soldering 16.5 Suitability of surface mount IC packages for wave and reflow soldering methods 17 DATA SHEET STATUS 18 DEFINITIONS 19 DISCLAIMERS

### TDA8007B

#### **1 FEATURES**

- Control and communication through an 8-bit parallel interface, compatible with multiplexed or non-multiplexed memory access

- Specific ISO UART with parallel access input/output for automatic convention processing, variable baud rate through frequency or division ratio programming, error management at character level for T = 0 and extra guard time register

- FIFO for 1 to 8 characters in reception mode

- Parity error counter in reception mode and in transmission mode with automatic re-transmission

- Dual V<sub>CC</sub> generation: 5 V  $\pm$  5%, 65 mA (max.); 3 V  $\pm$  8%, 50 mA (max.) or 1.8 V  $\pm$  10%, 30 mA (max.); with controlled rise and fall times

- Dual cards clock generation (up to 10 MHz), with three times synchronous frequency doubling ( $f_{XTAL}$ ,  $^{1}/_{2}f_{XTAL}$ ,  $^{1}/_{4}f_{XTAL}$  and  $^{1}/_{8}f_{XTAL}$ )

- Cards clock stop (at HIGH or LOW level) or 1.25 MHz (from internal oscillator) for cards Power-down mode

- Automatic activation and deactivation sequence through an independent sequencer

- Supports the asynchronous protocols T = 0 and T = 1 in accordance with:

- ISO 7816 and EMV 3.1.1 (TDA8007BHL/C2 and TDA8007BHL/C3)

- ISO 7816 and EMV 2000 (TDA8007BHL/C3)

- Versatile 24-bit time-out counter for Answer To Reset (ATR) and waiting times processing

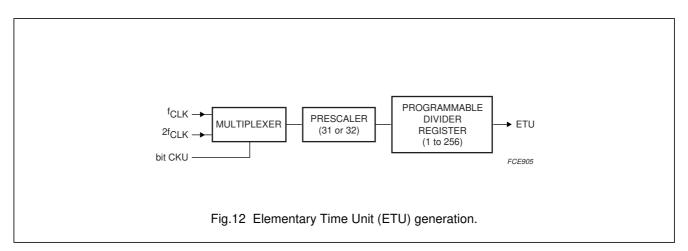

- Specific Elementary Time Unit (ETU) counter for Block Guard Time (BGT): 22 in T = 1 and 16 in T = 0

- Minimum delay between two characters in reception mode:

- in Protocol T = 0:

12 ETU (TDA8007BHL/C2)

11.8 ETU (TDA8007BHL/C3)

- in Protocol T = 1:

11 ETU (TDA8007BHL/C2)

- 10.8 ETU (TDA8007BHL/C3)

- Supports synchronous cards

- Current limitations in the event of short-circuit (pins I/O1, I/O2, V\_{CC1}, V\_{CC2}, RST1 and RST2)

- Special circuitry for killing spikes during power-on/power-off

- Supply supervisor for power-on/power-off reset

- Step-up converter (supply voltage from 2.7 to 6 V), doubler, tripler or follower according to  $V_{CC}$  and  $V_{DD}$

- Additional input/output pin allowing use of the ISO UART for another analog interface (pin I/OAUX)

- Additional interrupt pin allowing detection of level toggling on an external signal (pin INTAUX)

- Fast and efficient swapping between the three cards due to separate buffering of parameters for each card

- Chip select input allowing use of several devices in parallel and memory space paging

- Enhanced ESD protections on card side: 6 kV (min.)

- Software library for easy integration within the application

- Power-down mode for reducing current consumption when no activity.

#### 2 APPLICATIONS

• Multiple smart card readers for multiprocessor applications (EMV banking, digital pay TV and access control, etc.).

#### **3 GENERAL DESCRIPTION**

The TDA8007BHL/C is a cost-effective card interface for dual smart card readers. Controlled through a parallel bus, it meets all requirements of:

ISO 7816, GSM 11-11 and EMV 3.1.1 (TDA8007BHL/C2 and TDA8007BHL/C3)

ISO 7816, GSM 11-11 and EMV 2000 (TDA8007BHL/C3).

It may be interfaced to the ports P0, P1 and P2 of a 80C51 family microcontroller, and be addressed as a memory through MOVX instructions. It may also be addressed on a non-multiplexed 8-bit data bus, by means of address registers AD0, AD1, AD2 and AD3. The integrated ISO UART and the time-out counters allow easy use even at high baud rates with no real time constraints. Due to its chip select, external input/output and interrupt features, it greatly simplifies the realization of a reader of any number of cards. It gives the cards and the reader a very high level of security, due to its special hardware against ESD, short-circuiting, power failure, etc. The integrated step-up converter allows operation within a supply voltage range of 2.7 to 6 V; it may be supplied with a voltage higher than the IC's supply.

A software library has been developed that covers all actions required for T = 0 and T = 1 and synchronous protocols (see application note "AN01054").

### TDA8007B

#### 4 QUICK REFERENCE DATA

| SYMBOL                | PARAMETER                                                        | CONDITIONS                                                                                                                                          | MIN.            | TYP. | MAX. | UNIT |

|-----------------------|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|------|------|

| V <sub>DD</sub>       | supply voltage                                                   |                                                                                                                                                     | 2.7             | -    | 6    | V    |

| V <sub>DDA</sub>      | supply voltage for step-up converter                             |                                                                                                                                                     | V <sub>DD</sub> | -    | 6    | V    |

| I <sub>DD(pd)</sub>   | supply current in Power-down mode                                | V <sub>DD</sub> = 3.3 V; cards inactive; XTAL oscillator stopped                                                                                    | -               | -    | 350  | μA   |

|                       |                                                                  | $V_{DD}$ = 3.3 V; cards active at<br>$V_{CC}$ = 5 V; CLK stopped; XTAL<br>oscillator stopped                                                        | -               | -    | 3    | mA   |

| I <sub>DD(sm)</sub>   | supply current in sleep mode cards powered at 5 V; clock stopped |                                                                                                                                                     | -               | -    | 5.5  | mA   |

| I <sub>DD(oper)</sub> | supply current in operating mode                                 | $\label{eq:VDD} \begin{array}{l} V_{DD} = 3.3 \ V; \ f_{XTAL} = 20 \ MHz; \\ V_{CC1} = V_{CC2} = 5 \ V; \\ I_{CC1} + I_{CC2} = 80 \ mA \end{array}$ | _               | -    | 315  | mA   |

| V <sub>CC</sub>       | card supply output voltage                                       | 5 V card                                                                                                                                            |                 |      |      |      |

|                       |                                                                  | including static loads                                                                                                                              | 4.75            | 5.0  | 5.25 | V    |

|                       |                                                                  | with 40 nC dynamic loads on 200 nF capacitor                                                                                                        | 4.6             | -    | 5.4  | V    |

|                       |                                                                  | 3 V card                                                                                                                                            |                 |      |      |      |

|                       |                                                                  | including static loads                                                                                                                              | 2.78            | -    | 3.22 | V    |

|                       |                                                                  | with 24 nC dynamic loads on 200 nF capacitor                                                                                                        | 2.75            | -    | 3.25 | V    |

|                       |                                                                  | 1.8 V card                                                                                                                                          |                 |      |      |      |

|                       |                                                                  | including static loads                                                                                                                              | 1.65            | _    | 1.95 | V    |

|                       |                                                                  | with 12 nC dynamic loads on 200 nF capacitor                                                                                                        | 1.62            | -    | 1.98 | V    |

| I <sub>CC</sub>       | card supply output current                                       | 5 V card; operating                                                                                                                                 | -               | -    | 65   | mA   |

|                       |                                                                  | 3 V card; operating                                                                                                                                 | _               | -    | 50   | mA   |

|                       |                                                                  | 1.8 V card; operating                                                                                                                               | -               | -    | 30   | mA   |

|                       |                                                                  | overload detection                                                                                                                                  | -               | 100  | -    | mA   |

| $I_{CC1} + I_{CC2}$   | sum of both card supply output currents                          | operating; 5 and 3 V cards                                                                                                                          | -               | -    | 80   | mA   |

| SR                    | slew rate on $V_{CC}$ (rise and fall)                            | C <sub>L(max)</sub> = 300 nF                                                                                                                        | 0.05            | 0.16 | 0.22 | V/µs |

| t <sub>deact</sub>    | deactivation cycle duration                                      |                                                                                                                                                     | -               | -    | 150  | μs   |

| t <sub>act</sub>      | activation cycle duration                                        |                                                                                                                                                     | _               | -    | 225  | μs   |

| f <sub>XTAL</sub>     | crystal frequency                                                |                                                                                                                                                     | 4               | -    | 20   | MHz  |

| f <sub>ext</sub>      | external frequency                                               | applied to pin XTAL1                                                                                                                                | 0               | -    | 20   | MHz  |

| T <sub>amb</sub>      | ambient temperature                                              |                                                                                                                                                     | -40             | _    | +85  | °C   |

### 5 ORDERING INFORMATION

| TYPE NUMBER              |        | PACKAGE                                                                          |          |  |

|--------------------------|--------|----------------------------------------------------------------------------------|----------|--|

| NAME         DESCRIPTION |        |                                                                                  |          |  |

| TDA8007BHL/C2            | LQFP48 | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm | SOT313-2 |  |

| TDA8007BHL/C3            | LQFP48 | plastic low profile quad flat package; 48 leads; body $7 \times 7 \times 1.4$ mm | SOT313-2 |  |

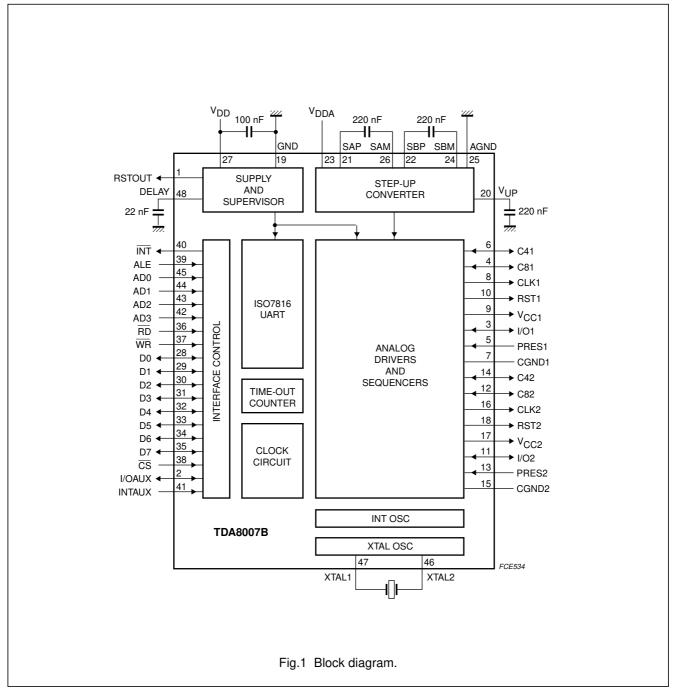

#### 6 BLOCK DIAGRAM

### TDA8007B

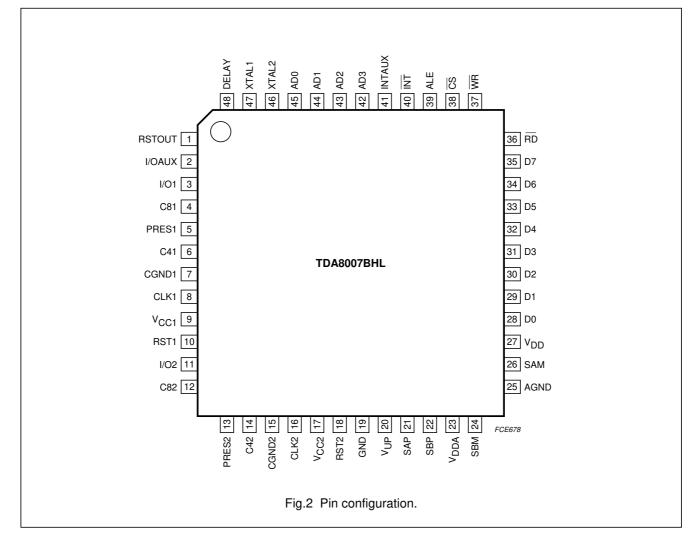

#### 7 PINNING

| SYMBOL           | PIN | DESCRIPTION                                                                                                                           |

|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| RSTOUT           | 1   | PMOS open-drain output for resetting external devices                                                                                 |

| I/OAUX           | 2   | input or output for an I/O line from an auxiliary smart card interface                                                                |

| I/O1             | 3   | input or output for the data line to/from card 1 (ISO C7 contact)                                                                     |

| C81              | 4   | auxiliary I/O for ISO C8 contact (synchronous cards, for instance) for card 1                                                         |

| PRES1            | 5   | card 1 presence contact input (active HIGH)                                                                                           |

| C41              | 6   | auxiliary I/O for ISO C4 contact (synchronous cards, for instance) for card 1                                                         |

| CGND1            | 7   | ground for card 1; must be connected to GND                                                                                           |

| CLK1             | 8   | clock output to card 1 (ISO C3 contact)                                                                                               |

| V <sub>CC1</sub> | 9   | card 1 supply output voltage (ISO C1 contact)                                                                                         |

| RST1             | 10  | card 1 reset output (ISO C2 contact)                                                                                                  |

| I/O2             | 11  | input or output for the data line to/from card 2 (ISO C7 contact)                                                                     |

| C82              | 12  | auxiliary I/O for ISO C8 contact (synchronous cards, for instance) for card 2                                                         |

| PRES2            | 13  | card 2 presence contact input (active HIGH)                                                                                           |

| C42              | 14  | auxiliary I/O for ISO C4 contact (synchronous cards, for instance) for card 2                                                         |

| CGND2            | 15  | ground for card 2; must be connected to GND                                                                                           |

| CLK2             | 16  | clock output to card 2 (ISO C3 contact)                                                                                               |

| V <sub>CC2</sub> | 17  | card 2 supply output voltage (ISO C1 contact)                                                                                         |

| RST2             | 18  | card 2 reset output (ISO C2 contact)                                                                                                  |

| GND              | 19  | ground                                                                                                                                |

| V <sub>UP</sub>  | 20  | connection for the step-up converter capacitor; connect a low ESR capacitor of 220 nF to AGND                                         |

| SAP              | 21  | contact 1 for the step-up converter; connect a low ESR capacitor of 220 nF between pins SAP and SAM                                   |

| SBP              | 22  | contact 3 for the step-up converter; connect a low ESR capacitor of 220 nF between pins SBP and SBM                                   |

| V <sub>DDA</sub> | 23  | positive analog supply voltage for the step-up converter; may be higher than $V_{DD}$ ; decouple with a good quality capacitor to GND |

| SBM              | 24  | contact 4 for the step-up converter; connect a low ESR capacitor of 220 nF between pins SBP and SBM                                   |

| AGND             | 25  | analog ground for the step-up converter                                                                                               |

| SAM              | 26  | contact 2 for the step-up converter; connect a low ESR capacitor of 220 nF between pins SAP and SAM                                   |

| V <sub>DD</sub>  | 27  | positive supply voltage; decouple with a good quality capacitor to GND                                                                |

| D0               | 28  | input/output of data 0 or address 0                                                                                                   |

| D1               | 29  | input/output of data 1 or address 1                                                                                                   |

| D2               | 30  | input/output of data 2 or address 2                                                                                                   |

| D3               | 31  | input/output of data 3 or address 3                                                                                                   |

| D4               | 32  | input/output of data 4 or address 4                                                                                                   |

| D5               | 33  | input/output of data 5 or address 5                                                                                                   |

|                  |     |                                                                                                                                       |

| D6               | 34  | input/output of data 6 or address 6                                                                                                   |

| SYMBOL | PIN | DESCRIPTION                                                                                                                  |

|--------|-----|------------------------------------------------------------------------------------------------------------------------------|

| RD     | 36  | read selection input; read or write in non-multiplexed configuration (active LOW)                                            |

| WR     | 37  | write selection input; enable in case of non-multiplexed configuration (active LOW)                                          |

| CS     | 38  | chip select input (active LOW)                                                                                               |

| ALE    | 39  | address latch enable input in case of multiplexed configuration; connect to $V_{\text{DD}}$ in non-multiplexed configuration |

| INT    | 40  | NMOS interrupt output (active LOW)                                                                                           |

| INTAUX | 41  | auxiliary interrupt input                                                                                                    |

| AD3    | 42  | register selection address 3 input                                                                                           |

| AD2    | 43  | register selection address 2 input                                                                                           |

| AD1    | 44  | register selection address 1 input                                                                                           |

| AD0    | 45  | register selection address 0 input                                                                                           |

| XTAL2  | 46  | connection for an external crystal                                                                                           |

| XTAL1  | 47  | connection for an external crystal or input for an external clock signal                                                     |

| DELAY  | 48  | connection for an external delay capacitor                                                                                   |

2003 Feb 18

### TDA8007B

#### 8 FUNCTIONAL DESCRIPTION

Throughout this specification, it is assumed that the reader is aware of *"ISO 7816 norm"* terminology.

#### 8.1 Interface control

The TDA8007BHL/C can be controlled via an 8-bit parallel bus (bits D0 to D7).

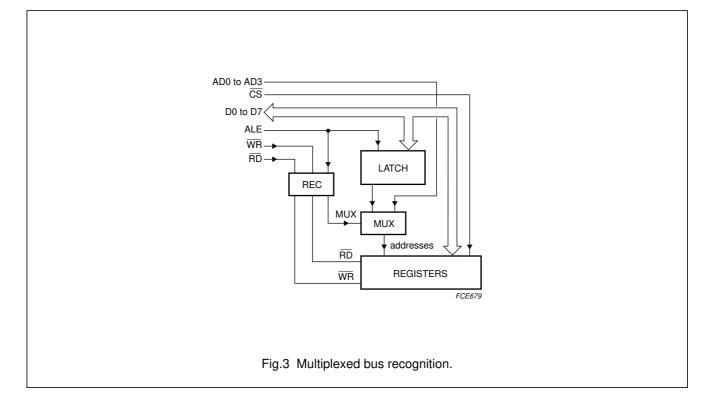

#### 8.1.1 MULTIPLEXED CONFIGURATION

If a microcontroller with a multiplexed address and data bus (such as the 80C51) is used, then pins D0 to D7 may be directly connected to ports P0 to P7.

Automatic switching to the multiplexed bus configuration (see Fig.3) occurs:

- In TDA8007BHL/C2; if a rising edge is detected on signal ALE and  $\overline{\text{CS}}$  is LOW

- In TDA8007BHL/C3; if a rising edge is detected on signal ALE.

In this event, pins AD0 to AD3 play no role and may be tied to  $V_{\text{DD}}$  or ground.

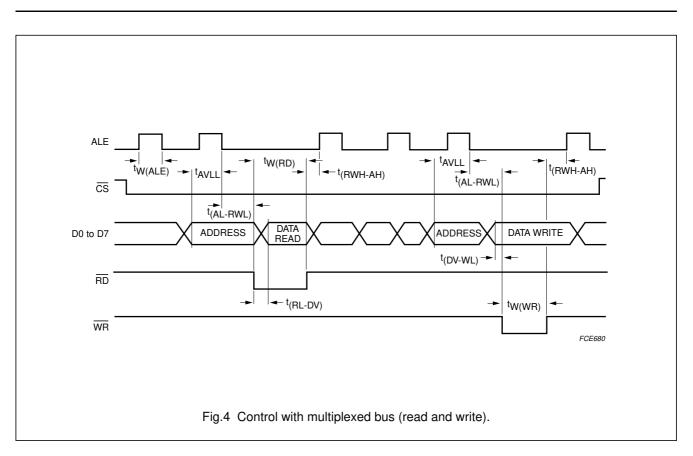

When signal  $\overline{CS}$  = LOW (see Fig.4), the demultiplexing of address and data is performed internally using signal ALE, a LOW pulse on pin  $\overline{RD}$  allows the selected register to be

read, a LOW pulse on pin  $\overline{\text{WR}}$  allows the selected register to be written to.

Using a 80C51 microcontroller, the TDA8007BHL/C is simply controlled with MOVX instructions.

#### 8.1.2 NON-MULTIPLEXED CONFIGURATION

If pin ALE is tied to  $V_{DD}$  or ground, the TDA8007BHL/C will be in the non-multiplexed configuration. In this case, the address bits are determined by means of pins AD0 to AD3; the read or write control signal is on pin  $\overline{RD}$  and a data write or read active LOW enable signal is on pin  $\overline{WR}$ .

In non-multiplexed bus configuration, signals  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  play the same role.

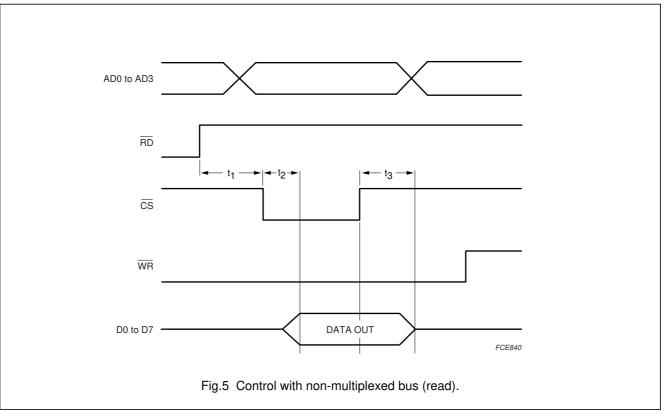

In read operations (see Fig.5) with signal  $\overline{RD}$  = HIGH, the data corresponding to the chosen address is available on the bus when both signals  $\overline{CS}$  and  $\overline{WR}$  are LOW.

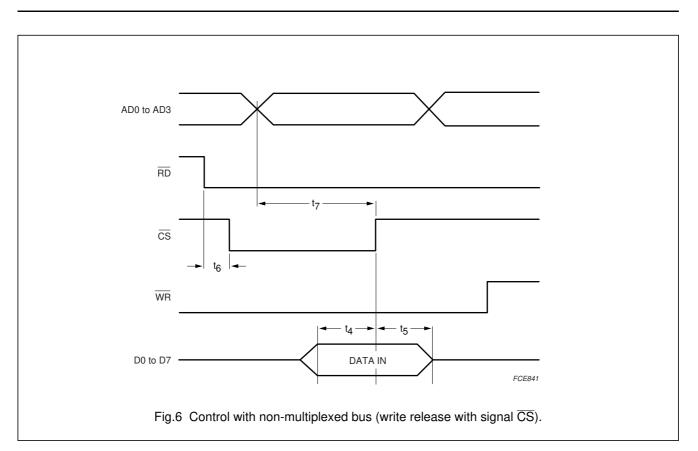

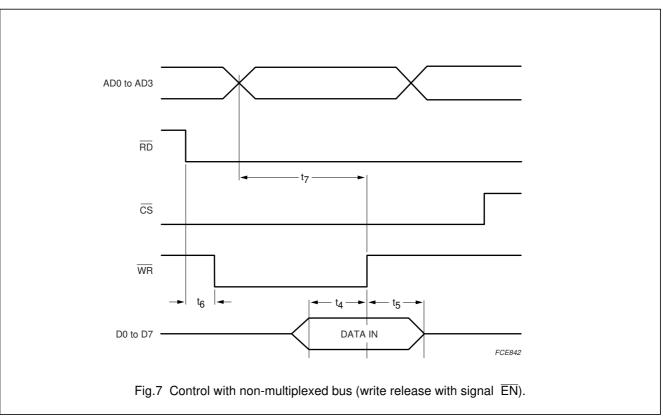

In write operations (see Figs.6 and 7) with signal  $\overline{RD}$  = LOW, the data present on the bus is written when signals  $\overline{CS}$  and  $\overline{WR}$  are LOW.

In both configurations, the TDA8007BHL/C is selected only when signal  $\overline{CS}$  = LOW. Signal  $\overline{INT}$  is an active LOW interrupt signal.

### TDA8007B

#### 8.2 Control registers

The TDA8007BHL/C has two complete analog interfaces which can drive cards 1 and 2. The data to and from these two cards shares the same ISO UART. The data to and from a third card (card 3), externally interfaced (with a TDA8020 or TDA8004 for example), may also share the same ISO UART.

Cards 1, 2 and 3 have dedicated registers for setting the parameters of the ISO UART (see Fig.8):

- Programmable Divider Register (PDR)

- Guard Time Register (GTR)

- UART Configuration Register 1 (UCR1)

- UART Configuration Register 2 (UCR2)

- Clock Configuration Register (CCR).

Cards 1 and 2 also have dedicated registers for controlling their power and clock configuration. The Power Control Register (PCR) for card 3 is controlled externally. Register PCR is also used for writing or reading on the auxiliary card contacts C4 and C8.

Card 1, 2 or 3 can be selected via the Card Select Register (CSR). When one card is selected, the corresponding parameters are used by the ISO UART. Register CSR also contains one bit for resetting the ISO UART (bit  $\overline{RIU} = 0$ ). This bit is reset after power-on and must be set to logic 1 before starting with any one of the cards. It may be reset by software when necessary.

When the specific parameters of the cards have been programmed, the UART may be used with the following registers:

- UART Receive Register (URR)

- UART Transmit Register (UTR)

- UART Status Register (USR)

- Mixed Status Register (MSR).

In reception mode, a FIFO of 1 to 8 characters may be used and is configured with the FIFO Control Register (FCR). This register is also used for the automatic re-transmission of Not AcKnowledged (NAK) characters in transmission mode.

The Hardware Status Register (HSR) gives the status of the supply voltage, of the hardware protections and of the card movements.

Registers HSR and USR give interrupts on pin  $\overline{\text{INT}}$  when some of their bits have been changed.

Register MSR does not give interrupts and may be used in the polling mode for some operations; for this use, some of the interrupt sources within the registers USR and HSR may be masked.

A 24-bit time-out counter may be started to give an interrupt after a number of ETU programmed into the Time-Out Registers TOR1, TOR2 and TOR3. This will help the microcontroller in processing different real-time tasks (ATR, WWT, BWT, etc.). This counter is configured with a Time-Out counter Configuration (TOC) register. It may be used as a 24-bit counter or as a 16-bit plus 8-bit counter. Each counter can be set to start counting once data has been written, or on detection of a START bit on the I/O, or as auto-reload.

Philips Semiconductors

TDA8007B

Product specification

8.2.1 GENERAL REGISTERS

#### 8.2.1.1 Card select register

The Card Select Register (CSR) is used for selecting the card on which the UART will act, and also to reset the ISO UART.

#### Table 1 Register CSR (address 00H; write and read); note 1

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CS7 | CS6 | CS5 | CS4 | RIU | SC3 | SC2 | SC1 |

#### Note

1. Register value at reset: all significant bits are cleared after reset, except bits CS7 to CS4 which are set to their default value.

#### Table 2 Description of CSR bits; note 1

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                        |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CS7    | IC identification. Default value for identifying the IC:                                                                                                                                                                                                                                                           |

| 6   | CS6    | 0010 = TDA8007BHL/C2                                                                                                                                                                                                                                                                                               |

| 5   | CS5    | 0011 = TDA8007BHL/C3                                                                                                                                                                                                                                                                                               |

| 4   | CS4    |                                                                                                                                                                                                                                                                                                                    |

| 3   | RIU    | <b>Reset ISO UART.</b> When reset, this bit resets a large part of the UART registers to their initial value. Bit $\overline{RIU}$ must be reset before any activation; logic 0 for at least 10 ns duration. Bit $\overline{RIU}$ must be set to logic 1 by software before any action on the UART can take place. |

| 2   | SC3    | Select Card 3. If bit SC3 = 1, then card 3 is selected.                                                                                                                                                                                                                                                            |

| 1   | SC2    | Select Card 2. If bit SC2 = 1, then card 2 is selected.                                                                                                                                                                                                                                                            |

| 0   | SC1    | Select Card 1. If bit SC1 = 1, then card 1 is selected.                                                                                                                                                                                                                                                            |

#### Note

1. Bits SC1, SC2 and SC3 must be set one at a time. After reset, no card is selected by default.

#### 8.2.1.2 Hardware status register

The Hardware Status Register (HSR) gives the status of the chip after a hardware problem has been detected.

Table 3 Register HSR (address 0FH; read only); note 1

| 7   | 6     | 5     | 4    | 3    | 2    | 1       | 0   |

|-----|-------|-------|------|------|------|---------|-----|

| HS7 | PRTL2 | PRTL1 | SUPL | PRL2 | PRL1 | INTAUXL | PTL |

#### Note

1. Register value at reset: all significant bits are cleared after reset, except bit SUPL which is set within pulse RSTOUT.

### TDA8007B

| Table 4 | Description of HSR bits. |

|---------|--------------------------|

|---------|--------------------------|

| BIT | SYMBOL  | DESCRIPTION                                                                                                                                                         |

|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | HS7     | not used                                                                                                                                                            |

| 6   | PRTL2   | <b>Protection 2</b> . Bit PRTL2 = 1 when a fault has been detected on card reader 2. Bit PRTL 2 is the OR-function of the protection on pin $V_{CC2}$ and pin RST2. |

| 5   | PRTL1   | <b>Protection 1</b> . Bit PRTL1 = 1 when a fault has been detected on card reader 1. Bit PRTL 1 is the OR-function of the protection on pin $V_{CC1}$ and pin RST1. |

| 4   | SUPL    | Supervisor Latch. Bit SUPL = 1 when the supervisor has been activated.                                                                                              |

| 3   | PRL2    | Presence Latch 2. Bit PRL2 = 1 when a level change has occurred on pin PRES2.                                                                                       |

| 2   | PRL1    | Presence Latch 1. Bit PRL1 = 1 when a level change has occurred on pin PRES1.                                                                                       |

| 1   | INTAUXL | Auxiliary interrupt change. Bit INTAUXL = 1 if the level on pin INTAUX has been changed.                                                                            |

| 0   | PTL     | <b>Overheating</b> . Bit PTL = 1 if overheating has occurred.                                                                                                       |

When at least one of the bits PRTL2, PRTL1, PRL2, PRL1 or PTL is HIGH, then INT is LOW. The bits having caused the interrupt are cleared when register HSR has been read-out. The same occurs with INTAUXL, if not disabled.

In case of an emergency deactivation (by bits PRTL2, PRTL1, SUPL, PRL2, PRL1 or PTL), bit START (bit 0 in the PCR) is automatically reset by hardware.

At power-on, or after a supply voltage drop-out, bit SUPL is set and pin  $\overline{INT} = LOW$ . Pin  $\overline{INT}$  will return to HIGH level at the end of the alarm pulse RSTOUT (see Fig.13). Bit SUPL will be reset only after a status register read-out outside the alarm pulse. A minimum time of 2  $\mu$ s is needed between two successive read operations of register HSR, as well as between reading of register HSR and activation (write in register PCR).

#### 8.2.1.3 Time-out registers

The three Time-Out Registers (TOR1, TOR2 and TOR3) form a programmable 24-bit ETU counter, or two independant counters (one 16-bit and one 8-bit). The value to load in registers TOR1, TOR2 and TOR3 is the number of ETU to count. The time-out counters may only be used when a card is active with a running clock.

| Table 5 | Register TOR1 | (address 09H; write only); note 1 |

|---------|---------------|-----------------------------------|

|---------|---------------|-----------------------------------|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TOL7 | TOL6 | TOL5 | TOL4 | TOL3 | TOL2 | TOL1 | TOL0 |

#### Note

1. Register value at reset: all bits are cleared after reset.

Table 6 Register TOR2 (address 0AH; write only); note 1

| 7     | 6     | 5     | 4     | 3     | 2     | 1    | 0    |

|-------|-------|-------|-------|-------|-------|------|------|

| TOL15 | TOL14 | TOL13 | TOL12 | TOL11 | TOL10 | TOL9 | TOL8 |

#### Note

1. Register value at reset: all bits are cleared after reset.

| Table 7 | Register TOR3 | (address 0BH; write only); note 1 |

|---------|---------------|-----------------------------------|

|---------|---------------|-----------------------------------|

| 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|

| TOL23 | TOL22 | TOL21 | TOL20 | TOL19 | TOL18 | TOL17 | TOL16 |

#### Note

1. Register value at reset: all bits are cleared after reset.

### TDA8007B

#### 8.2.1.4 Time-out configuration register

The Time-Out Configuration (TOC) register is used for setting different configurations of the time-out counter as given in Table 9; all other configurations are undefined.

| Table 8 Register TOC (address 08H; read and write); not |

|---------------------------------------------------------|

|---------------------------------------------------------|

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TOC7 | TOC6 | TOC5 | TOC4 | TOC3 | TOC2 | TOC1 | TOC0 |

#### Note

#### 1. Register value at reset: all bits are cleared after reset.

#### Table 9CARD REGISTERS

| TOC<br>VALUE | OPERATING MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00H          | All counters are stopped.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 05H          | Counters 2 and 3 are stopped; counter 1 continues to operate in auto-reload mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 61H          | Counter 1 is stopped, and counters 3 and 2 form a 16-bit counter. Counting the value stored in registers TOR3 and TOR2 is started after 61H is written in register TOC. An interrupt is given, and bit TO3 is set within register USR when the terminal count is reached. The counter is stopped by writing 00H in register TOC, and should be stopped before reloading new values in registers TOR2 and TOR3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 65H          | Counter 1 is an 8-bit auto-reload counter, and counters 3 and 2 form a 16-bit counter. Counter 1 starts counting the content of register TOR1 on the first START bit (reception or transmission) detected on pin I/O after 65H is written in register TOC. When counter 1 reaches its terminal count, an interrupt is given, bit TO1 in register USR is set, and the counter automatically restarts the same count until it is stopped. It is not allowed to change the content of register TOR1 during a count. Counters 3 and 2 are wired as a single 16-bit counter and start counting the value in registers TOR3 and TOR2 when 65H is written in register TOC. When the counter reaches its terminal count, an interrupt is given and bit TO3 is set within register USR. Both counters are stopped when 00H is written in register TOC. Counters 3 and 2 shall be stopped by writing 05H in register TOC before reloading new values in registers TOR2 and TOR3.                                                                                        |

| 68H          | Counters 3, 2 and 1 are wired as a single 24-bit counter. Counting the value stored in registers TOR3, TOR2 and TOR1 is started after 68H is written in register TOC. The counter is stopped by writing 00H in register TOC. It is not allowed to change the content of registers TOR3, TOR2 and TOR1 within a count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 71H          | Counter 1 is stopped, and counters 3 and 2 form a 16-bit counter. Counting the value stored in registers TOR3 and TOR2 and is started on the first START bit detected on pin I/O (reception or transmission) after the value has been written, and then on each subsequent START bit. It is possible to change the content of registers TOR3 and TOR2 during a count; the current count will not be affected and the new count value will be taken into account at the next START bit. The counter is stopped by writing 00H in register TOC. In this configuration, registers TOR3, TOR2 and TOR1 must not be all zero.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 75H          | Counter 1 is an 8-bit auto-reload counter, and counters 3 and 2 form a 16-bit counter. Counter 1 starts counting the content of register TOR1 on the first START bit (reception or transmission) detected on pin I/O after 75H is written in register TOC. When counter 1 reaches its terminal count, an interrupt is given, bit TO1 in register USR is set, and the counter automatically restarts the same count until it is stopped. Changing the content of register TOR1 during a count is not allowed. Counting the value stored in registers TOR3 and TOR2 is started on the first START bit detected on pin I/O (reception or transmission) after the value has been written, and then on each subsequent START bit. It is possible to change the count of registers TOR3 and TOR2 during a count; the current count will not be affected and the new count value will be taken into account at the next START bit. The counter is stopped by writing 00H in register TOC. In this configuration, registers TOR3, TOR2 and TOR1 must not be all zero. |

### TDA8007B

| TOC<br>VALUE | OPERATING MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7CH          | Counters 3, 2 and 1 are wired as a single 24-bit counter. Counting the value stored in registers TOR3, TOR2 and TOR1 is started on the first START bit detected on pin I/O (reception or transmission) after the value has been written, and then on each subsequent START bit. It is possible to change the content of registers TOR3, TOR2 and TOR1 during a count; the current count will not be affected and the new count value will be taken into account at the next START bit. The counter is stopped by writing 00H in register TOC. In this configuration, registers TOR3, TOR2 and TOR1 must not be all zero. |

| 85H          | Same as value 05H, except that all the counters will be stopped at the end of the 12th ETU following the first received START bit detected after 85H has been written in register TOC.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| E5H          | Same configuration as value 65H, except that counter 1 will be stopped at the end of the 12th ETU following the first START bit detected after E5H has been written in register TOC.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F1H          | Same configuration as value 71H, except that the 16-bit counter will be stopped at the end of the 12th ETU following the first START bit detected after F1H has been written in register TOC.                                                                                                                                                                                                                                                                                                                                                                                                                            |

| F5H          | Same configuration as value 75H, except the two counters will be stopped at the end of the 12th ETU following the first START bit detected after F5H has been written in register TOC.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

The time-out counter is very useful for processing the clock counting during ATR, the Work Waiting Time (WWT) or the waiting times defined in protocol T = 1. It should be noted that the 200 and  $n_{max}$  clock counter ( $n_{max}$  = 384 for TDA8007BHL/C2;  $n_{max}$  = 368 for TDA8007BHL/C3) used

during ATR is done by hardware when the start session is set, specific hardware controls the functionality of BGT in T = 1 and T = 0 protocols and a specific register is available for processing the extra guard time. Writing to register TOC is not allowed as long as the card is not activated with a running clock.

Before restarting the 16-bit counter (counters 3 and 2) by writing 61H, 65H, 71H, 75H, F1H or F5H in the TOC; or the 24-bit counter (counters 3, 2 and 1) by writing 68H in the TOC; it is mandatory to stop them by writing 00H in the TOC.

Detailed examples of how to use these specific timers can be found in application note "AN01054".

### TDA8007B

#### 8.2.2 ISO UART REGISTERS

#### 8.2.2.1 UART transmit register

#### Table 10 Register UTR (address 0DH; write only); note 1

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| UT7 | UT6 | UT5 | UT4 | UT3 | UT2 | UT1 | UT0 |

#### Note

1. Register value at reset: all bits are cleared after reset.

When the microcontroller wants to transmit a character to the selected card, it writes the data in direct convention in the UART Transmit Register (UTR). The transmission:

- Starts at the end of writing (on the rising edge of signal WR) if the previous character has been transmitted and if the extra guard time has expired

- Starts at the end of the extra guard time if this one has not expired

- Does not start if the transmission of the previous character is not completed

- With a synchronous card (bit SAN within register UCR2 is set), only signal D0 is relevant and is copied on pin I/O of the selected card.

#### 8.2.2.2 UART receive register

Table 11 Register URR (address 0DH; read only); note 1

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| UR7 | UR6 | UR5 | UR4 | UR3 | UR2 | UR1 | UR0 |

#### Note

1. Register value at reset: all bits are cleared after reset.

When the microcontroller wants to read data from the card, it reads it from the UART Receive Register (URR) in direct convention:

- With a synchronous card, only D0 is relevant and is a copy of the state of the selected card I/O

- When needed, this register may be tied to a FIFO whose length 'n' is programmable between 1 and 8; if n > 1, then no interrupt is given until the FIFO is full and the controller may empty the FIFO when required

- With a parity error:

- In protocol T = 0; the received byte is not stored in the FIFO and the error counter is incremented. The error counter is programmable between 1 and 8. When the programmed number is reached, then the bit PE is set in the status register USR and INTO falls LOW. The error counter must be reprogrammed to the desired value after its count has been reached

- In protocol T = 1; the character is loaded in the FIFO and the bit PE is set whatever the programmed value in the parity error counter

- When the FIFO is full, then the bit RBF in the status register USR is set. This bit is reset when at least one character has been read from URR

- When the FIFO is empty, then the bit FE is set in the status register USR as long as no character has been received.

#### 8.2.2.3 Mixed status register

The Mixed Status Register (MSR) relates the status of pin INTAUX, the cards presence contacts PRES1 and PRES2, the BGT counter, the FIFO empty indication and the transmit or receive ready indicator TBE/RBF. It also gives useful indications when switching the clock to or from  $1/2f_{int}$  and when driving the TDA8007BHL/C with fast controllers.

No bits within register MSR act upon signal INT.

### TDA8007B

Table 12

Register MSR (address 0CH; read only); note 1

| 7     | 6  | 5   | 4    | 3   | 2   | 1      | 0       |

|-------|----|-----|------|-----|-----|--------|---------|

| CLKSW | FE | BGT | CRED | PR2 | PR1 | INTAUX | TBE/RBF |

#### Note

1. Register value at reset: bits TBE/RBF, BGT and CLKSW are cleared after reset; bits FE and CRED are set after reset.

| BIT | SYMBOL  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CLKSW   | <b>Clock switch</b> . Bit CLKSW is set when the TDA8007BHL/C has performed a required clock switch from $1/nf_{XTAL}$ to $1/2f_{int}$ , and is reset when the TDA8007BHL/C has performed a required clock switch from $1/2f_{int}$ to $1/2f_{int}$ . The application must wait until this bit is set or reset before sending a new command to the card. This bit is reset at power-on.                                 |

| 6   | FE      | <b>FIFO Empty</b> . Bit FE is set when the reception FIFO is empty. It is reset when at least one character has been loaded in the FIFO.                                                                                                                                                                                                                                                                               |

| 5   | BGT     | <b>Block Guard Time</b> . In protocol $T = 1$ , bit BGT is linked with a 22-ETU counter which is started at every START bit on pin I/O. Bit BGT is set if the count is finished before the next START bit. This helps to verify that the card has not answered before 22 ETU after the last transmitted character, or that the reader is not transmitting a character before 22 ETU after the last received character. |

|     |         | In protocol T = 0, bit BGT is linked with a 16-ETU counter which is started at every START bit on pin I/O. Bit BGT is set if the count is finished before the next START bit. This helps to verify that the reader is not transmitting a character before 16 ETU after the last received character.                                                                                                                    |

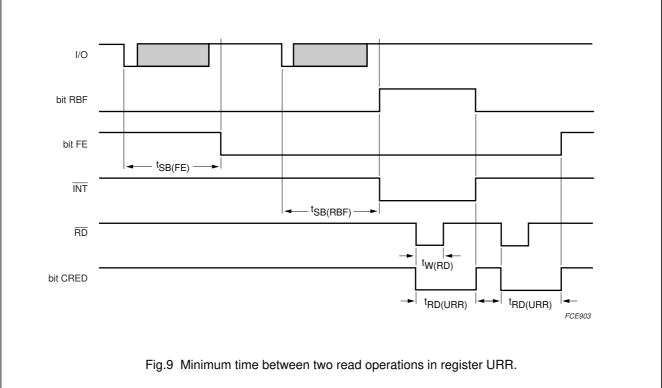

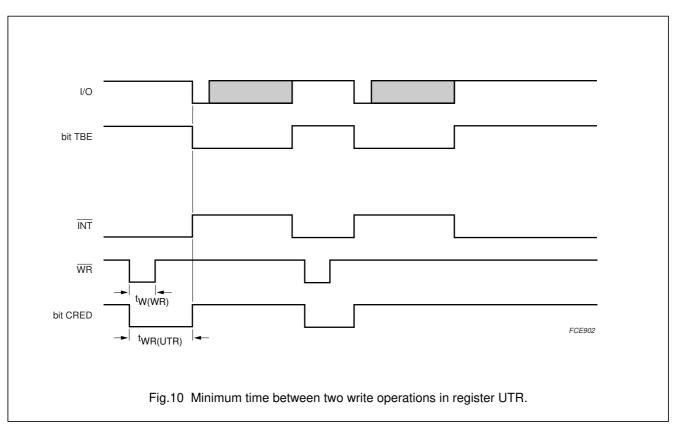

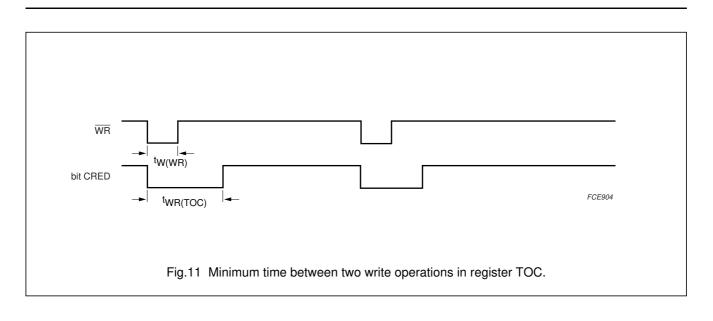

| 4   | CRED    | <b>Control ready</b> . It is advised bit CRED is used for driving the TDA8007BHL/C with high speed controllers. Before writing in registers TOC or UTR, or reading from register URR, check if bit CRED is set. If reset, it means that the writing or reading operation will not be correct because the controller is acting faster than the required time for this operation:                                        |

|     |         | • 3 clock cycles after rising edge $\overline{RD}$ for reading from register URR: $t_{RD(URR)} - t_{W(RD)}$ (see Fig.9).                                                                                                                                                                                                                                                                                               |

|     |         | • 3 clock cycles after rising edge $\overline{WR}$ for writing in register UTR: $t_{WR(UTR)} - t_{W(WR)}$ (see Fig.10)                                                                                                                                                                                                                                                                                                 |

|     |         | • $\frac{3}{31}$ or $\frac{3}{32}$ ETU after rising edge $\overline{WR}$ for writing in register TOC: $t_{WR(TOC)} - t_{W(WR)}$ (see Fig.11)                                                                                                                                                                                                                                                                           |

|     |         | Bit CRED is set at power-on.                                                                                                                                                                                                                                                                                                                                                                                           |

| 3   | PR2     | Card 2 present. Bit PR2 = 1 when card 2 is present.                                                                                                                                                                                                                                                                                                                                                                    |

| 2   | PR1     | <b>Card 1 present</b> . Bit PR1 = 1 when card 1 is present.                                                                                                                                                                                                                                                                                                                                                            |

| 1   | INTAUX  | <b>Auxiliary interrupt</b> . Bit INTAUX is set when pin INTAUX = HIGH and it is reset when pin INTAUX = LOW.                                                                                                                                                                                                                                                                                                           |

| 0   | TBE/RBF | Transmit Buffer Empty/Receive Buffer Full. Bit TBE/RBF = 1 when:                                                                                                                                                                                                                                                                                                                                                       |

|     |         | <ul> <li>Changing from reception mode to transmission mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |

|     |         | <ul> <li>A character has been transmitted by the UART</li> </ul>                                                                                                                                                                                                                                                                                                                                                       |

|     |         | The reception FIFO is full.                                                                                                                                                                                                                                                                                                                                                                                            |

|     |         | Bit TBE/RBF = 0 after power-on or after one of the following:                                                                                                                                                                                                                                                                                                                                                          |

|     |         | When bit RIU is reset                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |         | <ul> <li>When a character has been written to register UTR</li> </ul>                                                                                                                                                                                                                                                                                                                                                  |

|     |         | <ul> <li>When at least one character has been read in the FIFO</li> </ul>                                                                                                                                                                                                                                                                                                                                              |

|     |         | <ul> <li>When changing from transmission mode to reception mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                            |

#### Table 13Description of MSR bits.

### TDA8007B

#### 8.2.2.4 FIFO control register

The FIFO Control Register (FCR) relates the parity error count and the FIFO length.

Table 14 Register FCR (address 0CH; write only); note 1

| 7   | 6    | 5    | 4    | 3   | 2   | 1   | 0   |

|-----|------|------|------|-----|-----|-----|-----|

| FC7 | PEC2 | PEC1 | PEC0 | FC3 | FL2 | FL1 | FL0 |

#### Note

1. Register value at reset: all relevant bits are cleared after reset.

#### **Table 15**Description of FCR bits.

| BIT | SYMBOL | DESCRIPTION                                                                                                                                                                                                                        |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | FC7    | not used                                                                                                                                                                                                                           |

| 6   | PEC2   | Parity Error Count. Bits PEC2, PEC1 and PEC0 determine the number of allowed repetitions in                                                                                                                                        |

| 5   | PEC1   | reception or in transmission before setting bit PE in register USR and pulling pin INT to LOW level.                                                                                                                               |

| 4   | PEC0   | The value 000 indicates that, if only one parity error has occurred, bit PE is set; the value 111 indicates that bit PE will be set after 8 parity errors.                                                                         |

|     |        | In protocol $T = 0$ :                                                                                                                                                                                                              |

|     |        | <ul> <li>If a correct character is received before the programmed error number is reached, the error<br/>counter will be reset</li> </ul>                                                                                          |

|     |        | <ul> <li>If the programmed number of allowed parity errors is reached, bit PE in register USR will be set<br/>as long as register USR has not been read</li> </ul>                                                                 |

|     |        | • If a transmitted character has been NAK by the card, then the TDA8007BHL/C will automatically re-transmit it a number of times equal to the value programmed in bits PEC2, PEC1 and PEC0; the character will be resent at 15 ETU |

|     |        | <ul> <li>In transmission mode, if bits PEC2, PEC1 and PEC0 are logic 0, then the automatic<br/>re-transmission is invalidated; the character manually rewritten in register UTR will start at<br/>13.5 ETU.</li> </ul>             |

|     |        | In protocol T = 1:                                                                                                                                                                                                                 |

|     |        | • The error counter has no action: bit PE is set at the first incorrectly received character.                                                                                                                                      |

| 3   | FC3    | not used                                                                                                                                                                                                                           |

| 2   | FL2    | FIFO length. Bits FL2, FL1 and FL0 determine the depth of the FIFO:                                                                                                                                                                |

| 1   | FL1    | • 000 = length 1                                                                                                                                                                                                                   |

| 0   | FL0    | • 111 = length 8.                                                                                                                                                                                                                  |

#### 8.2.2.5 UART status register

The UART Status Register (USR) is used by the microcontroller to monitor the activity of the ISO UART and that of the time-out counter. If any of the status bits FER, OVR, PE, EA, TO1, TO2 or TO3 are set, then signal  $\overline{INT}$  = LOW. The bit having caused the interrupt is reset 2 µs after the rising edge of signal  $\overline{RD}$  during a read operation of register USR.

If bit TBE/RBF is set and if the mask bit DISTBE/RBF within register UCR2 is not set, then also

signal  $\overline{INT}$  = LOW. Bit TBE/RBF is reset 3 clock cycles after data has been written in register UTR, or 3 clock cycles after data has been read from register URR, or when changing from transmission mode to reception mode.

In order to avoid counting these clock cycles, bit CRED (described in register MSR) may be used.

If LCT mode is used for transmitting the last character, then bit TBE is not set at the end of the transmission.

### TDA8007B

Table 16

Register USR (address 0EH; read only); note 1

| 7   | 6   | 5   | 4  | 3  | 2   | 1   | 0       |

|-----|-----|-----|----|----|-----|-----|---------|

| TO3 | TO2 | TO1 | EA | PE | OVR | FER | TBE/RBF |

#### Note

1. Register value at reset: all bits are cleared after reset.

| BIT | SYMBOL  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | TO3     | Time-Out counter 3. Bit TO3 is set when counter 3 has reached its terminal count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 6   | TO2     | Time-Out counter 2. Bit TO2 is set when counter 2 has reached its terminal count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | TO1     | Time-Out counter 1. Bit TO1 is set when counter 1 has reached its terminal count.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4   | EA      | <b>Early Answer</b> is HIGH if the first START bit on the I/O during ATR has been detected between the first 200 and $n_{max}^{(1)}$ clock pulses with RST LOW (all activities on the I/O during the first 200 clock pulses with RST LOW are not taken into account) and before the first $n_{max}^{(1)}$ clock pulses with RST HIGH. These two features are re-initialized at each toggling of RST                                                                                                                                                                                                |

| 3   | PE      | <b>Parity Error</b> . In protocol $T = 0$ , bit PE = 1 if the UART has detected a number of received characters with parity errors equal to the number written in bits PEC2, PEC1 and PEC0 or if a transmitted character has been NAK by the card a number of times equal to the value programmed in bits PEC2, PEC1 and PEC0. It is set at 10.5 ETU in the reception mode and at 11.5 ETU in the transmission mode.                                                                                                                                                                               |

|     |         | In protocol $T = 0$ , a character received with a parity error is not stored in register FIFO (the card should repeat this character). In protocol $T = 1$ , a character with a parity error is stored in the FIFO and the parity error counter is not active.                                                                                                                                                                                                                                                                                                                                     |

| 2   | OVR     | <b>Overrun</b> . Bit OVR = 1 if the UART has received a new character whilst register FIFO was full. In this case, at least one character has been lost.                                                                                                                                                                                                                                                                                                                                                                                                                                           |