# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 1. General description

The TDA8035 is the cost efficient successor of the established integrated contact smart card reader IC TDA8024. It offers a high level of security for the card by performing current limitation, short-circuit detection, ESD protection as well as supply supervision. The current consumption during the standby mode of the contact reader is very low as it operates in the 3 V supply domain. The TDA8035 is therefore the ideal component for a power efficient contact reader.

## 2. Features and benefits

### 2.1 Protection of the contact smart card

- Thermal and short-circuit protection on all card contacts

- V<sub>CC</sub> regulation:

- $\blacklozenge$  5 V, 3 V, 1.8 V  $\pm$  5 % on 2  $\times$  220 nF multilayer ceramic capacitors with low ESR

- Current spikes of 40 nA/s (V<sub>CC</sub> = 5 V and 3 V) or 15 nA/s (V<sub>CC</sub> = 1.8 V) up to 20 MHz, with controlled rise and fall times. Filtered overload detection is approximately 120 mA.

- Automatic activation and deactivation sequences initiated by software or by hardware in the event of a short-circuit, card take-off, overheating, falling V<sub>REG</sub> V<sub>DD(INTF)</sub>, V<sub>DDP</sub>

- Enhanced card-side ElectroStatic Discharge (ESD) protection of (> 8 kV)

- Supply supervisor for killing spikes during power on and off:

- threshold internally fixed

- externally by a resistor bridge

### 2.2 Easy integration into your contact reader

- SW compatible to TDA8024 and TDA8034

- 5 V, 3 V, 1.8 V smart card supply

- DC-to-DC converter for V<sub>CC</sub> generation separately powered from 2.7 V to 5.5 V supply (V<sub>DDP</sub> and GNDP)

- Very low power consumption in Deep Shutdown mode

- Three protected half-duplex bidirectional buffered I/O lines (C4, C7 and C8)

- External clock input up to 26 MHz

- Card clock generation up to 20 MHz using pins CLKDIV1 and CLKDIV2 with synchronous frequency changes of f<sub>XTAL</sub>, fXTAL/2, fXTAL/4 or fXTAL/8

- Non-inverted control of pin RST using pin RSTIN

- Built-in debouncing on card presence contact

- Multiplexed status signal using pin OFFN

Chip Select digital input for parallel operation of several TDA8035 ICs.

#### 2.2.1 Other

- HVQFN32 package

- Compliant with ISO 7816, NDS and EMV 4.3 (\*) payment systems

<sup>(\*)</sup> for C2 version

### 3. Applications

- Pay TV

- Electronic payment

- Identification

- IC card readers for banking

### 4. Quick reference data

#### Table 1. Quick reference data

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>Xtal</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub> = 25 °C; unless otherwise specified

| Symbol                | Parameter                | Conditions                                                                             | Min  | Тур | Max  | Unit |

|-----------------------|--------------------------|----------------------------------------------------------------------------------------|------|-----|------|------|

| Supply                |                          | I                                                                                      |      | I   | I    |      |

| V <sub>DDP</sub>      | power supply voltage     |                                                                                        | 2.7  | 3.3 | 5.5  | V    |

| V <sub>DD(INTF)</sub> | interface supply voltage |                                                                                        | 1.6  | 3.3 | 3.6  | V    |

| DDP                   | power supply current     | deep shutdown mode;                                                                    | -    | 0.1 | 3    | μA   |

|                       |                          | $f_{XTAL} = stopped;$                                                                  |      |     |      |      |

|                       |                          | shutdown mode;                                                                         | -    | 300 | 500  | μA   |

|                       |                          | f <sub>XTAL</sub> = stopped;                                                           |      |     |      |      |

|                       |                          | active mode; $V_{CC} = +5 V$<br>CLK = $f_{XTAL}/2$ ; no load                           | -    | -   | 5    | mA   |

|                       |                          | active mode; $CLK = f_{XTAL}/2$ ;<br>$V_{CC} = +5 V$ ; $I_{CC} = 65 mA$                | -    | -   | 220  | mA   |

|                       |                          | active mode; $CLK = f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +3 V; I <sub>CC</sub> = 65 mA   | -    | -   | 160  | mA   |

|                       |                          | active mode; $CLK = f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +1.8 V; I <sub>CC</sub> = 35 mA | -    | -   | 120  | mA   |

| I <sub>DD(INTF)</sub> | interface supply current | deep shutdown mode;<br>f <sub>XTAL</sub> = stopped;<br>present card                    | -    | -   | 1    | μA   |

|                       |                          | shutdown mode;<br>f <sub>XTAL</sub> = stopped;<br>present card                         | -    | -   | 1    | μA   |

| Internal sup          | oply voltage             |                                                                                        |      |     |      |      |

| V <sub>DD</sub>       | supply voltage           |                                                                                        | 1.62 | 1.8 | 1.98 | V    |

TDA8035 Product data sheet

#### High integrated and low power smart card interface

| Symbol                   | Parameter                             | Conditions                               | Min  | Тур | Max  | Unit |

|--------------------------|---------------------------------------|------------------------------------------|------|-----|------|------|

| Card supply              | y voltage: pin VCC                    |                                          |      |     | I    |      |

| V <sub>CC</sub>          | supply voltage                        | 5 V card; DC ICC < 65 mA                 | 4.75 | 5.0 | 5.25 | V    |

|                          |                                       | 5 V card; AC current spikes of 40 nA/s   | 4.65 | 5.0 | 5.25 | V    |

|                          |                                       | 3 V card; DC $I_{CC}$ < 65 mA            | 2.85 | -   | 3.15 | V    |

|                          |                                       | 3 V card; AC current spikes of 40 nA/s   | 2.76 | -   | 3.24 | V    |

|                          |                                       | 1.8 V card; DC $I_{CC}$ < 35 mA          | 1.71 | -   | 1.89 | V    |

|                          |                                       | 1.8 V card; AC current spikes of 15 nA/s | 1.66 | -   | 1.94 | V    |

| V <sub>ripple(p-p)</sub> | peak-to-peak ripple voltage           | from 20 kHz to 200 MHz                   | -    | -   | 300  | mV   |

| I <sub>CC</sub>          | supply current                        | V <sub>CC = 5</sub> V or 3 V             | -    | -   | 65   | mA   |

|                          |                                       | V <sub>CC = 1.8 V</sub>                  | -    | -   | 35   | mA   |

| General                  | · · · · · · · · · · · · · · · · · · · |                                          |      |     |      |      |

| t <sub>deact</sub>       | deactivation time                     | total sequence                           | 35   | 90  | 250  | μS   |

| P <sub>tot</sub>         | total power dissipation               |                                          | -    | -   | 0.45 | W    |

| T <sub>amb</sub>         | ambient temperature                   |                                          | -25  | -   | +85  | °C   |

|                          |                                       |                                          |      |     |      |      |

#### Table 1. Quick reference data ... continued

#### **Ordering information** 5.

The TDA8035 is available in 2 versions, which have the same functionalities. The C2 version is compliant with the EMVC0 4.3 standard.

| Type number     | Package |                                                                                                                                |          |  |  |  |

|-----------------|---------|--------------------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

|                 | Name    | Description                                                                                                                    | Version  |  |  |  |

| TDA8035HN/C1    | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5 \times 5 \times 0.85$ mm                 | SOT617-7 |  |  |  |

| TDA8035HN/C1/S1 | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5 \times 5 \times 0.85$ mm; <sup>[1]</sup> | SOT617-7 |  |  |  |

| TDA8035HN/C2/S1 | HVQFN32 | plastic thermal enhanced very thin quad flat package; no leads; 32 terminals; body $5 \times 5 \times 0.85$ mm; <sup>[1]</sup> | SOT617-7 |  |  |  |

#### Table 2. **Ordering information**

[1] copper wiring

High integrated and low power smart card interface

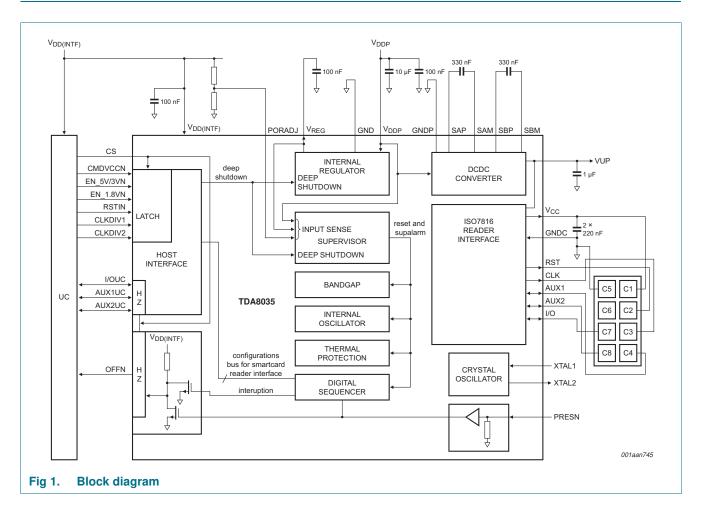

## 6. Block diagram

High integrated and low power smart card interface

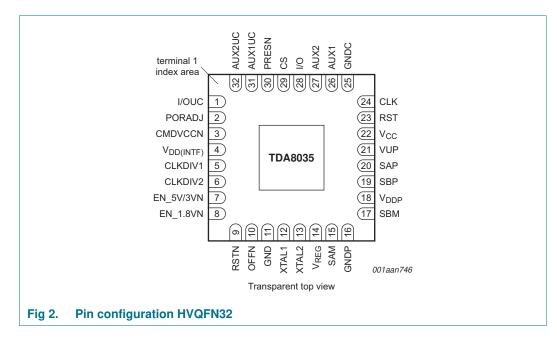

## 7. Pinning information

### 7.1 Pinning

### 7.2 Pin description

#### Table 3. Pin description

| Symbol                | Pin | Supply                | Туре   | Description                                                                                                                                |

|-----------------------|-----|-----------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------|

| I/OUC                 | 1   | V <sub>DD(INTF)</sub> | I/O    | host data I/O line (internal 10 k $\Omega$ pull-up resistor to V <sub>DD(INTF)</sub> )                                                     |

| PORADJ                | 2   | V <sub>DD(INTF)</sub> | I      | Input for $V_{\text{DD}(\text{INTF})}$ supervisor. PORADJ threshold can be changed with an external R bridge                               |

| CMDVCCN               | 3   | V <sub>DD(INTF)</sub> | I      | start activation sequence input from the host (active LOW)                                                                                 |

| V <sub>DD(INTF)</sub> | 4   | V <sub>DD(INTF)</sub> | supply | interface supply voltage                                                                                                                   |

| CLKDIV1               | 5   | V <sub>DD(INTF)</sub> | I      | control with CLKDIV2 for choosing CLK frequency (see Table 4)                                                                              |

| CLKDIV2               | 6   | V <sub>DD(INTF)</sub> | I      | control with CLKDIV1 for choosing CLK frequency (see Table 4)                                                                              |

| EN_5V/3VN             | 7   | V <sub>DD(INTF)</sub> | I      | control signal for selecting V <sub>CC</sub> = 5 V (HIGH) or V <sub>CC</sub> = 3 V (LOW) if EN_1.8 VN = High                               |

| EN_1.8 VN             | 8   | V <sub>DD(INTF)</sub> | I      | control signal for selecting $V_{CC} = 1.8 V$ (low)                                                                                        |

| RSTIN                 | 9   | V <sub>DD(INTF)</sub> | I      | card reset input from the host (active HIGH)                                                                                               |

| OFFN                  | 10  | V <sub>DD(INTF)</sub> | 0      | NMOS interrupt to the host (active LOW) with 10 k $\Omega$ internal pull-up resistor to $V_{DD(INTF)}$ (See fault detection)               |

| GND                   | 11  | -                     | supply | ground                                                                                                                                     |

| XTAL1                 | 12  | V <sub>DD(INTF)</sub> | I      | crystal connection 1                                                                                                                       |

| XTAL2                 | 13  | V <sub>DD(INTF)</sub> | 0      | crystal connection 2                                                                                                                       |

| V <sub>REG</sub>      | 14  | V <sub>DDP</sub>      | supply | Internal supply voltage                                                                                                                    |

| SAM                   | 15  | V <sub>DDP</sub>      | I/O    | DC-to-DC converter capacitor; connected between SAM and SAP; C = 330 nF or 100 nF (see Figure 13) with ESR < 100 m $\Omega$ at Freq=100kHz |

| GNDP                  | 16  | -                     | supply | DC-to-DC converter power supply ground                                                                                                     |

### High integrated and low power smart card interface

| Symbol           | Pin | Supply                | Туре   | Description                                                                                                                                              |

|------------------|-----|-----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBM              | 17  | V <sub>DDP</sub>      | I/O    | DC-to-DC converter capacitor; connected between SBM and SBP; C = 330 nF or 100nF (see Figure 13) with ESR < 100 m $\Omega$ at Freq=100kHz                |

| V <sub>DDP</sub> | 18  | V <sub>DDP</sub>      | supply | Power supply voltage                                                                                                                                     |

| SBP              | 19  | V <sub>DDP</sub>      | I/O    | DC-to-DC converter capacitor; connected between SBM and SBP; C = 330 nF or 100nF (see Figure 13) with ESR < 100 m $\Omega$ at Freq=100kHz                |

| SAP              | 20  | V <sub>DDP</sub>      | I/O    | DC-to-DC converter capacitor; connected between SAM and SAP; C = 330 nF or 100nF (see Figure 13) with ESR < 100 m $\Omega$ at Freq=100kHz                |

| VUP              | 21  | V <sub>DDP</sub>      | I/O    | DC-to-DC converter output decoupling capacitor connected between VUP and GNDP; C = 1 $\mu F$ with ESR < 100 m $\Omega$ at Freq=100kHz                    |

| V <sub>CC</sub>  | 22  | V <sub>CC</sub>       | 0      | supply for the card (C1), decouple to GND with 2 $\times$ 220 nF capacitors with ESR < 100 m $\Omega$                                                    |

| RST              | 23  | V <sub>CC</sub>       | 0      | card reset (C2)                                                                                                                                          |

| CLK              | 24  | V <sub>CC</sub>       | 0      | clock to the card (C3)                                                                                                                                   |

| GNDC             | 25  | -                     | supply | card signal ground                                                                                                                                       |

| AUX1             | 26  | V <sub>CC</sub>       | I/O    | auxiliary data line to and from the card (C4), internal 10 k $\Omega$ pull-up resistor to $V_{CC}$                                                       |

| AUX2             | 27  | V <sub>CC</sub>       | I/O    | auxiliary data line to and from the card (C8), internal 10 k $\Omega$ pull-up resistor to $V_{CC}$                                                       |

| I/O              | 28  | V <sub>CC</sub>       | I/O    | data line to and from the card (C7), internal 10 k $\Omega$ pull-up resistor to $V_{CC}$                                                                 |

| CS               | 29  | V <sub>DD(INTF)</sub> | I      | Chip Select input from the host (active High)                                                                                                            |

| PRESN            | 30  | V <sub>DD(INTF)</sub> | I      | Card presence contact input (active LOW); if PRESN is true, then the card is considered as present. A debouncing feature of 4.05 ms typical is built in. |

| AUX1UC           | 31  | V <sub>DD(INTF)</sub> | I/O    | auxiliary data line to and from the host, internal 10 $k\Omega$ pull-up resistor to $V_{DD(INTF)}$                                                       |

| AUX2UC           | 32  | V <sub>DD(INTF)</sub> | I/O    | auxiliary data line to and from the host, internal 10 k $\Omega$ pull-up resistor to $V_{DD(INTF)}$                                                      |

### Table 3. Pin description ...continued

### 8. Functional description

**Remark:** The ISO 7816 terminology convention has been adhered to throughout this document, and it is assumed that the reader is familiar with this convention.

### 8.1 Power supply

Power supply voltage V<sub>DDP</sub> is from 2.7 V to 5.5 V

All interface signals with the system controller are referenced to  $V_{DD(INTF)}$ . All card contacts remain inactive during powering up or powering down.

Internal regulator V<sub>REG</sub> is 1.8 V

After powering the device, OFFN remains low until CMDVCCN is set high and PRESN is low.

During power off, OFFN falls low when V<sub>DDP</sub> is below the threshold voltage falling.

While the card is not activated, CMDVCCN is kept at high level. To save power consumption, the frequency of the internal oscillator ( $f_{osc(int)}$ ) used for the activation sequences is put in low frequency mode.

This device includes a DC-to-DC converter to generate the 5 V, 3 V or 1.8 V card supply voltage ( $V_{CC}$ ). The DC-to-DC converter is separately supplied by  $V_{DDP}$  and  $G_{NDP}$ . The DC-to-DC converter operates as a voltage tripler, doubler or follower according to the respective values of  $V_{CC}$  and  $V_{DDP}$ .

Special care has to me made in the selection of the capacitors of the DC/DC converter specially with respect to capacitor value versus voltage and ESR (see Table 7)

The operating mode is as follows (see Figure 3):

- $V_{CC} = 5 \text{ V}$  and  $V_{DDP} > 3.8 \text{ V}$ ; voltage doubler

- $V_{CC} = 5 \text{ V}$  and  $V_{DDP} < 3.6 \text{ V}$ ; voltage tripler

- V<sub>CC</sub> = 3 V and V<sub>DDP</sub> > 3.8 V; voltage follower

- $V_{CC} = 3 V$  and  $V_{DDP} < 3.6 V$ ; voltage doubler

- $V_{CC} = 1.8$  V and  $V_{DDP} > 3.8$  V; voltage doubler

- V<sub>CC</sub> = 1.8 V and V<sub>DDP</sub> < 3.6 V; voltage tripler</li>

TDA8035

#### High integrated and low power smart card interface

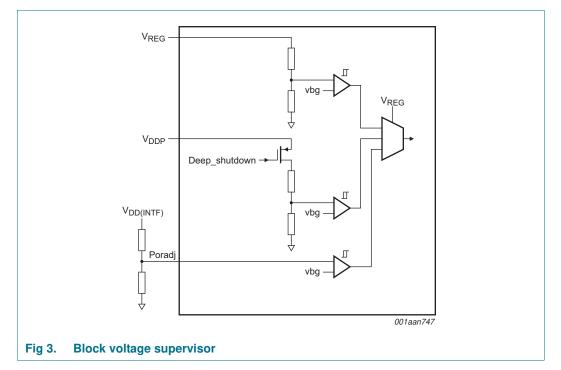

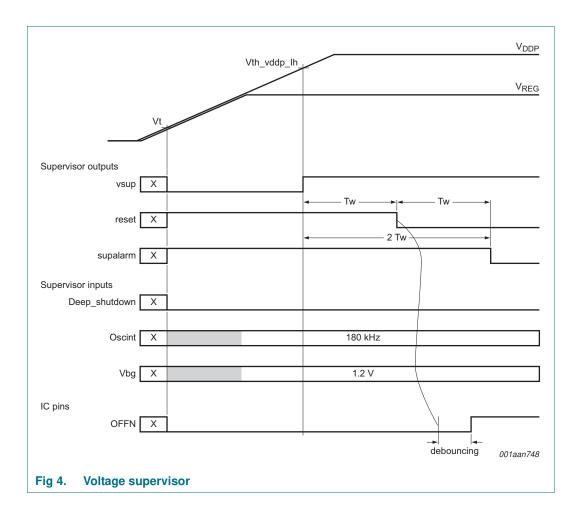

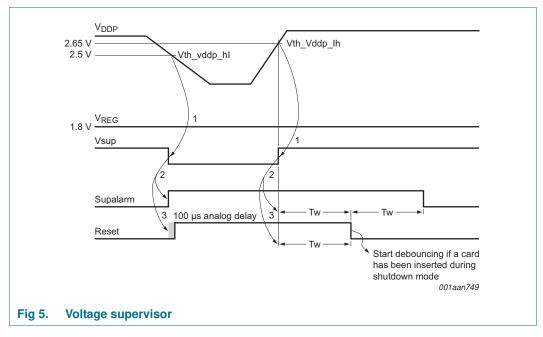

### 8.2 Voltage supervisor

The voltage supervisor is used as a power-on reset, and also as supply drop detection during a card session. The threshold of the voltage supervisor is set internally in the IC for VDDP and VREG. The threshold can be adjusted externally for VDD(INTF) using the PORADJ pin. As long as VREG is less than  $V_{th(VREG)} + V_{hys(VREG)}$ , the IC remains inactive whatever the levels on the command lines are. The inactivity lasts for the duration of  $t_w$  after VREG has reached a level higher than  $V_{th(VREG)} + V_{hys(VREG)}$ . The outputs of the VDDP, VREG and VDD(INTF) supervisors are combined and sent to a digital controller in order to reset the TDA8035. The reset pulse of approximately 5.7 ms ( $t_w = 2048 \times 1/(f_{osc(int)\_Low})$ ) is used internally for maintaining the IC in an inactive mode during the supply voltage power-on (see Figure 4 and Figure 5). A deactivation sequence is performed when:

- VREG falls below V<sub>th(VREG)</sub>

- V<sub>DD(INTF)</sub> falls below V<sub>th(PORADJ)</sub>

- VDDP falls below V<sub>th(VDDP)</sub>

TDA8035

#### High integrated and low power smart card interface

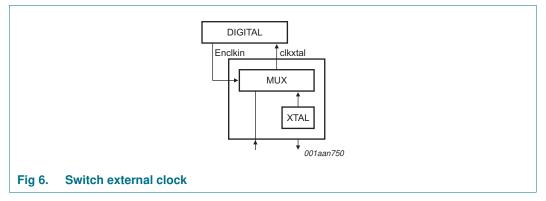

### 8.3 Clock circuitry

To generate the card clock CLK, the TDA8035 can either use an external clock provided on XTAL1 pin or a crystal oscillator connected on both XTAL1 and XTAL2 pins. The TDA8035 automatically detects when an external clock is provided on XTAL1. Consequently, there is no need for an extra pin to configure the clock source (external clock or crystal).

The automatic clock source detection is performed on each activation command (CMDVCCN pin falling edge). During a time window defined by the internal oscillator, the presence of an external clock on XTAL1 pin is checked. If a clock is detected, the crystal oscillator is kept stopped, else, the crystal oscillator is started. It is mandatory when an external clock is used, that the clock is applied on XTAL1 before CMDVCCN falling edge signal.

The frequency is chosen as  $f_{XTAL}$ ,  $f_{XTAL/2}$ ,  $f_{XTAL/4}$  or  $f_{XTAL/8}$  via the pins CLKDIV1 and CLKDIV2. Both selection inputs are not changed simultaneously. A minimum of 10 ns is required between changes on CLKDIV1 and CLKDIV2.

The frequency change is synchronous, which means that during transition, no pulse is shorter than 45 % of the smallest period. This ensures that the first and last clock pulse around the change has the correct width. When changing the frequency dynamically, the change is effective for only 10 periods of XTAL1 after the command.

The duty cycle on pin CLK is between 45 % and 55 %:

- When an external clock is used on XTAL1 pin and f<sub>XTAL</sub> is used, the duty cycle is between 48 % and 52 %. The subsequent rise and fall times (t<sub>r(i)</sub> and t<sub>f(i)</sub>) conform to values listed in <u>Table 7</u>. It has to connect a 56 pF serial capacitor (see <u>Figure 13</u>).

- CLK frequency is f<sub>XTAL</sub>, f<sub>XTAL/2</sub>, f<sub>XTAL/4</sub> or f<sub>XTAL/8</sub>: It is guaranteed between 45 % and 55 % of the period by the frequency dividers.

| CLKDIV1 | CLKDIV2 | CLK                 |

|---------|---------|---------------------|

| 0       | 0       | f <sub>XTAL/8</sub> |

| 0       | 1       | f <sub>XTAL/4</sub> |

| 1       | 1       | f <sub>XTAL/2</sub> |

| 1       | 0       | f <sub>XTAL</sub>   |

#### Table 4. Clock configuration

### 8.4 I/O circuitry

The three data lines I/O, AUX1 and AUX2 are identical.

To enter the idle state, both lines (I/O and I/OUC) are pulled HIGH via a 10 k $\Omega$  resistor (I/O to V<sub>CC</sub> and I/OUC to V<sub>DD(INTF)</sub>).

I/O is referenced to  $V_{CC},$  and I/OUC to  $V_{DD(INTF)}$  which allows operation with  $V_{CC} \neq V_{DD(INTF)}.$

The first side on which a falling edge occurs becomes the master. An anti-latch circuit disables the detection of falling edges on the other line, which becomes the slave.

After a time delay  $t_{d(edge)}$ , the logic 0 present on the master side is transmitted to the slave side.

When the master side returns to logic 1, the slave side transmits the logic 1 during the time delay  $t_{pu}$  and both sides return to their idle states.

The active pull-up feature ensures fast Low to High transitions. It is able to deliver more than 1 mA to an output voltage of 0.9  $V_{CC}$  on an 80 pF load. At the end of the active pull-up pulse, the output voltage depends on the internal pull-up resistor and on the load current.

The current to and from the cards I/O lines is internally limited to 15 mA.

The maximum frequency on these lines is 1.5 MHz.

TDA8035

#### 8.5 CS control

The CS (Chip Select) input allows multiple devices to operate in parallel. When CS is high, the system interface signals operate as described. When CS is low, the signals CMDVCCN, RSTIN, CLKDIV1, CLKDIV2, EN\_5V/3VN and EN\_1.8VN are latched. I/OUC, AUX1UC and AUX2UC are set to high impedance pull-up mode and data is no longer passed to or from the smart card. The OFFN output is a 3-state output.

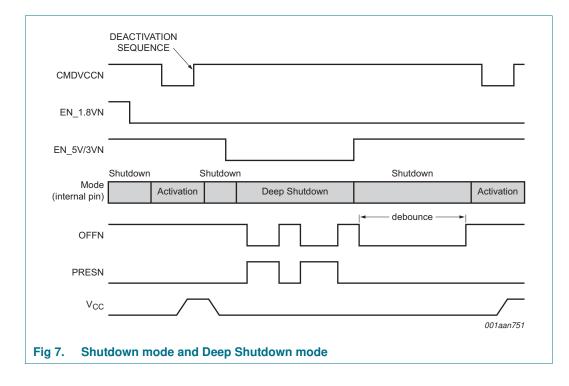

### 8.6 Shutdown mode and Deep Shutdown mode

After power-on reset, the circuit enters the Shutdown mode if CMDVCCN input pin is set to a logic high. A minimum number of circuits are active while waiting for the microcontroller to start a session.

- 1. All card contacts are inactive (approximately 200  $\Omega$  to GND).

- I/OUC, AUX1UC and AUX2UC are high impedance (10 kW pull-up resistor connected to V<sub>DD(INTF)</sub>).

- 3. Voltage generators are stopped.

- 4. Voltage supervisor is active.

- 5. The internal oscillator runs at its low frequency.

A Deep Shutdown mode can be entered by forcing CMDVCCN input pin to a logic-High state and EN\_5V/3VN, EN\_1.8VN input pins to a logic-Low state. Deep Shutdown mode can only be entered when the smart card reader is inactive. In Deep Shutdown mode, all circuits are disabled. The OFFN pin follows the status of PRESN pin. To exit Deep Shutdown mode, change the state of one or more of the three control pins. Figure 8 shows the control sequence for entering and exiting.

#### 8.7 Activation sequence

The following sequence then occurs with crystal oscillator (see Figure 8):

$T = 64 \times T_{oscint}$  (freq high)

- 1. CMDVCCN is pulled low (t0)

- 2. Crystal oscillator start-up time (t0).

- 3. The internal oscillator changes to its high frequency and DC-to-DC starts t1 = t0 + 768  $\times$  T<sub>osc (freq low)</sub>

- 4.  $V_{CC}$  rises from 0 to selected  $V_{CC}$  value (5 V, 3 V, 1.8 V) with a controlled slope  $(t_2$  =  $t_1$  + 3T/2)

- 5. I/O, AUX1 and AUX2 are enabled ( $t_3 = t_1 + 10T$ ), until now, they were pulled LOW

- 6. CLK is applied to the C3 contact ( $t_4 = t_3 + x$ ) with 200 ns < x < 10 x 1/f<sub>Xtal</sub>

- 7. RST is enabled ( $t_5 = t_1 + 13T$ ).

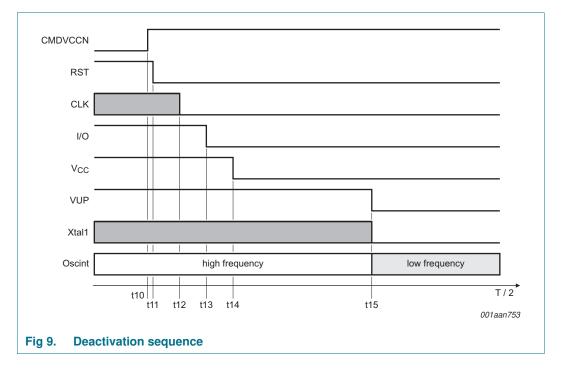

#### 8.8 Deactivation sequence

When a session is completed, the microcontroller sets the CMDVCCN line to the HIGH state. The circuit then executes an automatic deactivation sequence by counting the sequencer back and ends in the inactive state (see Figure 9):

- 1. RST goes LOW ( $t_{11} = t_{10} + 3T/64$ )

- 2. CLK is stopped LOW ( $t_{12} = t_{11} + T/2$ )

- 3. I/O, AUX1 and AUX2 are pulled LOW ( $t_{13} = t_{11} + T$ )

- 4.  $V_{CC}$  falls to zero ( $t_{14} = t_{11} + 3T/2$ ). The deactivation sequence is completed when  $V_{CC}$  reaches its inactive state

- 5. VUP falls to zero ( $t_{15} = t_{11} + 7T/2$ )

- 6.  $V_{CC} < 0.4 \text{ V}$  (t<sub>de</sub> = t<sub>11</sub> + 3T/2 + V<sub>CC</sub> fall time)

- 7. All card contacts become low-impedance to GND. I/OUC, AUX1UC and AUX2UC remain pulled up to  $V_{DD(INTF)}$  via a 10 k $\Omega$  resistor.

- 8. The internal oscillator reverts to its lower frequency.

#### 8.9 V<sub>CC</sub> regulator

$V_{CC}$  buffer is able to deliver up to 65 mA continuously at  $V_{CC}$  = 5 V and  $V_{CC}$  = 3 V, and 35 mA at  $V_{CC}$  = 1.8 V.

V<sub>CC</sub> buffer has an internal overload detection at approximately 125 mA.

This detection is internally filtered, allowing the card to draw spurious current pulses of up to 200 mA for some milliseconds, without causing a deactivation. The average current value must remain below the maximum.

TDA8035

#### 8.10 Fault detection

The circuit monitors the following fault conditions:

- short-circuit or high current on V<sub>CC</sub>

- Card removal during transaction

- +  $V_{DDP}$  or  $V_{DD(INTF)}$  or  $V_{reg}$  dropping

- overheating.

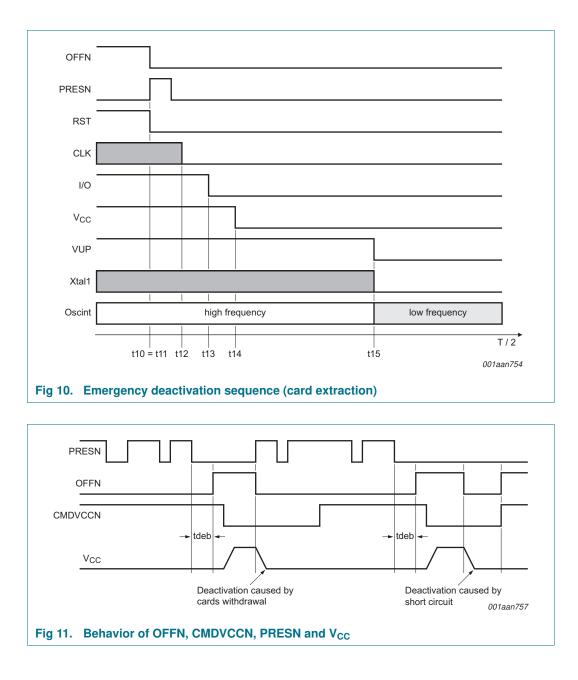

There are two different cases (see Figure 10 on page 16):

- CMDVCCN High (outside a card session): OFFN is Low when the card is not in the reader, and High when the card is in the reader. The supply supervisor detects a supply voltage drop on V<sub>DDP</sub> and generates an internal power-on reset pulse, but it does not act upon OFFN. The card is not powered-up, so no short-circuit or overheating is detected.

- 2. CMDVCCN Low (within a card session): OFFN falls Low in any of the previously mentioned cases. As soon as the fault is detected, an emergency deactivation is automatically performed. When the system controller sets CMDVCCN back to High, it senses OFFN again. After a complete deactivation sequence, the system controller sets CMDVCCN back to High and it senses OFFN again. This is to distinguish between a hardware problem or a card extraction. OFFN reverts to High when the card is still present.

A bounce can occur on the PRESN signal during card insertion or withdrawal. The bounce depends on the type of card presence switch within the connector (normally closed or normally open), and on the mechanical characteristics of the switch. To prevent this bounce, a debounce function of approximately 4.05 ms (tdeb =  $1280 \times 1/(f_{osc(int)\_Low})$ ) is integrated in the device.

When the card is inserted, OFFN goes High only at the end of the debounce time (see Figure 11 on page 16).

When the card is extracted, an automatic deactivation sequence of the card is performed on the first true/false transition on PRESN. OFFN goes Low.

#### High integrated and low power smart card interface

#### **Limiting values** 9.

All card contacts are protected against a short-circuit with any other card contact.

Stress beyond the limiting values can damage the device permanently. The values are stress ratings only and functional operation of the device under these conditions is not implied.

| Table 5.   | Limiting values       |

|------------|-----------------------|

| In accorda | nce with the Absolute |

| Symbol                | Parameter                          | Conditions                                                                                                                                      | Min  | Max  | Unit |

|-----------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|

| V <sub>DDP</sub>      | power supply voltage               |                                                                                                                                                 | -0.3 | 6    | V    |

| V <sub>DD(INTF)</sub> | interface supply voltage           |                                                                                                                                                 | -0.3 | 4.1  | V    |

| V <sub>IH</sub>       | HIGH-level input<br>voltage        | CS, PRESN,<br>CMDVCCN, CLKDIV2,<br>CLKDIV1, EN_1.8VN,<br>EN_5V/3VN, RSTIN,<br>OFFN, PORADJ, XTAL1,<br>I/OUC, AUX1UC, AUX2UC,<br>VDDP, VDD(INTF) | -0.3 | 4.1  | V    |

|                       |                                    | I/O, RST, AUX1, AUX2 and CLK                                                                                                                    | -0.3 | 5.75 | V    |

| T <sub>amb</sub>      | ambient temperature                |                                                                                                                                                 | -25  | +85  | °C   |

| T <sub>stg</sub>      | storage temperature                |                                                                                                                                                 | -55  | +150 | °C   |

| Tj                    | junction temperature               |                                                                                                                                                 |      | +125 | °C   |

| P <sub>tot</sub>      | total power dissipation            |                                                                                                                                                 |      | 0.45 | W    |

| V <sub>ESD</sub>      | electrostatic discharge<br>voltage | Human Body Model (HBM)<br>on card pins I/O, RST, V <sub>CC</sub> ,<br>AUX1, CLK, AUX2, PRESN                                                    | -10  | +10  | kV   |

|                       |                                    | within typical application                                                                                                                      |      |      |      |

|                       |                                    | Human Body Model (HBM)<br>on all other pins                                                                                                     | -2   | +2   | kV   |

|                       |                                    | Machine Model (MM) on all pins                                                                                                                  | -200 | +200 | V    |

|                       |                                    | Field Charged Device<br>Model (FCDM) on all pins                                                                                                | -500 | +500 | V    |

#### Table 5 Limiting . .

In accordance with the Absolute Maximum Rating System (IEC 60134).

## **10. Thermal characteristics**

| Table 6.         Thermal characteristics |              |                                             |                                         |     |      |  |  |  |

|------------------------------------------|--------------|---------------------------------------------|-----------------------------------------|-----|------|--|--|--|

| Symbol                                   | Package name | Parameter                                   | Conditions                              | Тур | Unit |  |  |  |

| R <sub>th(j-a)</sub>                     | HVQFN32      | thermal resistance from junction to ambient | in free air with 4 thermal vias on PCB  | 55  | K/W  |  |  |  |

|                                          |              |                                             | in free air without thermal vias on PCB | 63  | K/W  |  |  |  |

## **11. Characteristics**

#### Table 7. Characteristics of IC

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol                     | Parameter                                     | Conditions                                                                             | Min  | Тур  | Max  | Unit |

|----------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------|------|------|------|------|

| Supply voltage             | e                                             |                                                                                        |      |      |      |      |

| V <sub>DDP</sub>           | power supply voltage                          |                                                                                        | 2.7  | 3.3  | 5.5  | V    |

| V <sub>DD(INTF)</sub>      | interface supply voltage                      |                                                                                        | 1.6  | 3.3  | 3.6  | V    |

| I <sub>DDP</sub>           | power supply current                          | deep Shutdown mode;                                                                    | -    | 0.1  | 3    | μA   |

|                            |                                               | $f_{XTAL} = stopped$                                                                   |      |      |      |      |

|                            |                                               | Shutdown mode;                                                                         | -    | 300  | 500  | μA   |

|                            |                                               | f <sub>XTAL</sub> = stopped                                                            |      |      |      |      |

|                            |                                               | active mode; CLK = $f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +5 V; no load                   | -    | -    | 5    | mA   |

|                            |                                               | active mode; CLK = $f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +5 V; I <sub>CC</sub> = 65 mA   | -    | -    | 220  | mA   |

|                            |                                               | active mode; CLK = $f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +3 V; I <sub>CC</sub> = 65 mA   | -    | -    | 160  | mA   |

|                            |                                               | active mode; CLK = $f_{XTAL}/2$ ;<br>V <sub>CC</sub> = +1.8 V; I <sub>CC</sub> = 35 mA | -    | -    | 120  | mA   |

| I <sub>DD(INTF)</sub>      | interface supply current                      | deep Shutdown mode                                                                     | -    | -    | 1    | μA   |

|                            |                                               | f <sub>XTAL</sub> = stopped;                                                           |      |      |      |      |

|                            |                                               | present card                                                                           |      |      |      |      |

|                            |                                               | Shutdown mode                                                                          | -    | -    | 1    | μA   |

|                            |                                               | $f_{XTAL} = stopped;$                                                                  |      |      |      |      |

|                            |                                               | present card                                                                           |      |      |      |      |

| $V_{th(VREG)}$             | threshold voltage on pin<br>V <sub>REG</sub>  | internal voltage regulator<br>falling                                                  | 1.38 | 1.45 | 1.52 | V    |

| V <sub>hys(VREG)</sub>     | hysteresis voltage on pin<br>V <sub>REG</sub> |                                                                                        | 90   | 100  | 110  | mV   |

| $V_{th(VDDP)}$             | threshold voltage on pin<br>V <sub>DDP</sub>  | pin VDDP falling                                                                       | 2.15 | 2.25 | 2.35 | V    |

| $V_{hys(VDDP)}$            | hysteresis voltage on pin $V_{\text{DDP}}$    |                                                                                        | 90   | 100  | 110  | mV   |

| t <sub>w</sub>             | pulse width                                   |                                                                                        | 3.0  | 6.5  | 8.9  | ms   |

| V <sub>th(L)(PORADJ)</sub> | LOW-level threshold voltage on pin PORADJ     | external resistors on PORADJ                                                           | 0.81 | 0.85 | 0.89 | V    |

| V <sub>hys(PORADJ)</sub>   | hysteresis voltage on pin<br>PORADJ           |                                                                                        | 30   | 60   | 90   | mV   |

| IL                         | leakage current                               | pin PORADJ                                                                             | -1   | -    | +1   | μA   |

| VREG                       | ·                                             |                                                                                        |      |      |      |      |

| Vo                         | output voltage                                |                                                                                        | 1.62 | 1.80 | 1.98 | V    |

| t <sub>r</sub>             | rise time                                     | exit of deep Shutdown mode                                                             | -    | -    | 200  | μs   |

#### High integrated and low power smart card interface

#### Table 7. Characteristics of IC ...continued

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol              | Parameter                     | Conditions                                                      | Min  | Тур      | Max  | Uni |

|---------------------|-------------------------------|-----------------------------------------------------------------|------|----------|------|-----|

| VUP (DC-to-         | DC converter)                 |                                                                 |      | I        |      | I   |

| V <sub>OH</sub>     | HIGH-level output voltage     | VDDP=3.3V, VCC = 5 V,<br>ICC < 65 mA DC                         | 5.10 | 5.60     | 7.00 | V   |

|                     |                               | VDDP=3.3V, VCC = 3 V,<br>ICC < 65 mA DC                         | 3.50 | 3.95     | 5.00 | V   |

|                     |                               | VDDP=3.3V, VCC = 1.8 V,<br>ICC < 35 mA DC                       | 5.10 | 5.60     | 7.00 | V   |

|                     |                               | VDDP=5V, VCC = 5 V,<br>ICC < 65 mA DC                           | 5.10 | 5.80     | 7.00 | V   |

|                     |                               | VDDP=5V, VCC = 3 V,<br>ICC < 65 mA DC                           | -    | 5.00     | -    | V   |

|                     |                               | VDDP=5V, VCC = 1.8 V,<br>ICC < 35 mA DC                         | 5.10 | 5.80     | 7.00 | V   |

| SAP (DC-to-I        | DC converter)                 | -                                                               |      | <u>.</u> |      |     |

| V <sub>OH</sub>     | HIGH-level output voltage     | VDDP=3.3V, VCC = 5 V,<br>ICC < 65 mA DC                         | -    | -        | 8.20 | V   |

|                     |                               | VDDP=3.3V, VCC = 3 V,<br>ICC < 65 mA DC                         | -    | -        | 6.00 | V   |

|                     |                               | VDDP=3.3V, VCC = 1.8 V,<br>ICC < 35 mA DC                       | -    | -        | 8.20 | V   |

|                     |                               | VDDP=5V, VCC = 5 V,<br>ICC < 65 mA DC                           | -    | -        | 8.20 | V   |

|                     |                               | VDDP=5V, VCC = 3 V,<br>ICC < 65 mA DC                           | -    | 5.00     | -    | V   |

|                     |                               | VDDP=5V, VCC = 1.8 V,<br>ICC < 35 mA DC                         | -    | -        | 8.20 | V   |

| DC-to-DC co         | nverter capacitors            |                                                                 |      |          |      |     |

| C <sub>SAPSAM</sub> | DC/DC converter capacitance   | connected between SAP and<br>SAM (330 nF [4]) with<br>VDDP=3.3v | 231  | -        | 429  | nF  |

|                     |                               | connected between SAP and<br>SAM (100 nF [4]) with<br>VDDP=5v   | 70   | -        | 130  | nF  |

| C <sub>SBPSBM</sub> | DC/DC converter capacitance   | connected between SBP and<br>SBM (330 nF 4) with<br>VDDP=3.3v   | 231  | -        | 429  | nF  |

|                     |                               | connected between SBP and<br>SBM (100 nF 4) with<br>VDDP=5v     | 70   | -        | 130  | nF  |

| C <sub>VUP</sub>    | DC/DC converter capacitance   | connected on VUP(1uF [4])                                       | 700  | -        | 1300 | nF  |

| Card supply         | voltage (V <sub>CC</sub> )[1] |                                                                 |      |          |      |     |

| C <sub>dec</sub>    | decoupling capacitance        | connected on V <sub>CC</sub> (220 nF + 220 nF 10 %)             | 396  | -        | 484  | nF  |

| Vo                  | output voltage                | inactive mode; no load                                          | -0.1 | -        | +0.1 | V   |

|                     |                               | inactive mode; lo = 1 mA                                        | -0.1 | -        | +0.3 | V   |

#### High integrated and low power smart card interface

#### Table 7. Characteristics of IC ... continued

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol                   | Parameter                         | Conditions                                                                                       | Min                       | Тур  | Мах                         | Unit |

|--------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------|-----------------------------|------|

| l <sub>o</sub>           | output current                    | inactive mode<br>at grounded pin VCC                                                             | -                         | -    | -1                          | mA   |

| V <sub>CC</sub>          | supply voltage                    | active mode; 5 V card;<br>ICC < 65 mA DC                                                         | 4.75                      | 5.0  | 5.25                        | V    |

|                          |                                   | active mode; 3 V card;<br>ICC < 65 mA DC                                                         | 2.85                      | 3.05 | 3.15                        | V    |

|                          |                                   | active mode; 1.8 V card;<br>ICC < 35 mA DC                                                       | 1.71                      | 1.83 | 1.89                        | V    |

|                          |                                   | active mode; current pulses of<br>40 nA/s with ICC < 200 mA,<br>t < 400 ns; 5 V card             | 4.65                      | 5.0  | 5.25                        | V    |

|                          |                                   | active mode; current pulses of<br>40 nA/s with ICC < 200 mA,<br>t < 400 ns; 3 V card             | 2.76                      | -    | 3.20                        | V    |

|                          |                                   | active mode; current pulses of<br>15 nA/s with ICC < 200 mA,<br>t < 400 ns; 1.8 V card           | 1.66                      | -    | 1.94                        | V    |

| V <sub>ripple(p-p)</sub> | peak-to-peak ripple<br>voltage    | from 20 kHz to 200 MHz                                                                           | -                         | -    | 350                         | mV   |

| I <sub>CC</sub>          | supply current                    | VCC = 0 V to 5 V, 3 V                                                                            | -                         | -    | 65                          | mA   |

|                          |                                   | VCC = 0 V to 1.8 V                                                                               | -                         | -    | 35                          | mA   |

| SR                       | slew rate                         | 5 V card                                                                                         | 0.055                     | 0.18 | 0.8                         | V/µs |

|                          |                                   | 3 V card                                                                                         | 0.040                     | 0.18 | 0.8                         | V/µs |

|                          |                                   | 1.8 V card                                                                                       | 0.025                     | 0.18 | 0.8                         | V/µs |

| Crystal osci             | llator (XTAL1 and XTAL2)          |                                                                                                  |                           |      |                             |      |

| C <sub>ext</sub>         | external capacitance              | connected on pins<br>XTAL1/XTAL2 (depending on<br>specification of crystal or<br>resonator used) | -                         | -    | 33                          | pF   |

| f <sub>xtal</sub>        | crystal frequency                 |                                                                                                  | 2                         | -    | 27                          | MHz  |

| f <sub>xtal(XTAL1)</sub> | crystal frequency on pin<br>XTAL1 | with 56 pF serial capacitor                                                                      | 0                         | -    | 27                          | MHz  |

| V <sub>IL</sub>          | LOW-level input voltage           |                                                                                                  | -0.3                      | -    | +0.3 V <sub>DD(INTF)</sub>  | V    |

| V <sub>IH</sub>          | HIGH-level input voltage          |                                                                                                  | 0.7 V <sub>DD(INTF)</sub> | -    | V <sub>DD(INTF)</sub> + 0.3 | V    |

| t <sub>r(i)</sub>        | input rise time                   | $f_{CLK} = f_{XTAL1} = 20 \text{ MHz on}$<br>external clock                                      | -                         | -    | 4                           | ns   |

|                          |                                   | $f_{CLK} = f_{XTAL1} = 10 \text{ MHz on}$<br>external clock                                      | -                         | -    | 8                           | ns   |

|                          |                                   | $f_{CLK} = f_{XTAL1} = 5 \text{ MHz on}$<br>external clock                                       | -                         | -    | 16                          | ns   |

#### High integrated and low power smart card interface

#### Table 7. Characteristics of IC ...continued

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol             | Parameter                      | Conditions                                                  | Min                   | Тур       | Max                   | Unit |  |

|--------------------|--------------------------------|-------------------------------------------------------------|-----------------------|-----------|-----------------------|------|--|

| t <sub>f(i)</sub>  | input fall time                | $f_{CLK} = f_{XTAL1} = 20 \text{ MHz on}$<br>external clock | -                     | -         | 4                     | ns   |  |

|                    |                                | $f_{CLK} = f_{XTAL1} = 10 \text{ MHz on}$<br>external clock | -                     | -         | 8                     | ns   |  |

|                    |                                | $f_{CLK} = f_{XTAL1} = 5 \text{ MHz on}$<br>external clock  | -                     | -         | 16                    | ns   |  |

| Data lines (       | oins I/O, I/OUC, AUX1, AUX2,   | AUXIUC, AUX2UC)                                             |                       |           |                       | ·    |  |

| t <sub>d</sub>     | delay time                     | falling edge on pins I/O and I/OUC or I/OUC and I/O         | -                     | -         | 200                   | ns   |  |

| t <sub>w(pu)</sub> | pull-up pulse width            |                                                             | 200                   |           | 400                   | ns   |  |

| f <sub>max</sub>   | maximum frequency              | on data lines                                               | -                     | -         | 1                     | MHz  |  |

| Ci                 | input capacitance              | on data lines                                               | -                     | -         | 10                    | pF   |  |

| Data lines to      | o the card (pins I/O, AUX1, AU | JX2); (Integrated 10 kΩ pull-u                              | o resistor con        | nected to | V <sub>CC</sub> )     | I    |  |

| Vo                 | output voltage                 | inactive mode; no load                                      | 0                     | -         | 0.1                   | V    |  |

|                    |                                | inactive mode; lo= 1 mA                                     | 0                     | -         | 0.3                   | V    |  |

| lo                 | output current                 | inactive mode<br>at grounded pin I/O                        | -                     | -         | -1                    | mA   |  |

| V <sub>OL</sub>    | LOW-level output voltage       | I <sub>OL</sub> = 1 mA - C1 version                         | 0                     | -         | 0.3                   | V    |  |

|                    |                                | I <sub>OL</sub> = 1 mA - C2 version                         | 0                     | -         | 0.15 V <sub>CC</sub>  | V    |  |

|                    |                                | $I_{OL} \ge 15 \text{ mA}$                                  | V <sub>CC</sub> - 0.4 | -         | V <sub>CC</sub>       | V    |  |

| V <sub>OH</sub>    | HIGH-level output voltage      | No DC load                                                  | 0.9 V <sub>CC</sub>   | -         | V <sub>CC</sub> + 0.1 | V    |  |

|                    |                                | I <sub>OH</sub> ≥ -15 mA                                    | 0                     | -         | 0.4                   | V    |  |

|                    |                                | C1 version                                                  |                       |           |                       |      |  |

|                    |                                | I <sub>OH</sub> < -40 μA 5 V or 3 V                         | 0.75 V <sub>CC</sub>  |           | V <sub>CC</sub> + 0.1 | V    |  |

|                    |                                | I <sub>OH</sub> < -20 μA 1.8 V                              | 0.75 V <sub>CC</sub>  |           | V <sub>CC</sub> + 0.1 | V    |  |

|                    |                                | C2 version                                                  |                       |           |                       |      |  |

|                    |                                | I <sub>OH</sub> < -40 μA 5 V or 3 V                         | 0.8 V <sub>CC</sub>   |           | V <sub>CC</sub> + 0.1 | V    |  |

|                    |                                | I <sub>OH</sub> < -20 μA 1.8 V                              | 1.28                  |           | V <sub>CC</sub> + 0.1 | V    |  |

| V <sub>IL</sub>    | LOW-level input voltage        | C1 version                                                  | -0.3                  | -         | +0.8                  | V    |  |

|                    |                                | C2 version                                                  | -0.3                  |           | 0.2 V <sub>CC</sub>   |      |  |

| V <sub>IH</sub>    | HIGH-level input voltage       | C1 Version                                                  |                       |           |                       |      |  |

|                    |                                | VCC = +5 V                                                  | 0.6 V <sub>CC</sub>   | -         | V <sub>CC</sub> + 0.3 | V    |  |

|                    |                                | VCC = +3 V or 1.8 V                                         | 0.7 V <sub>CC</sub>   | -         | V <sub>CC</sub> + 0.3 | V    |  |

|                    |                                | C2 Version                                                  | 00                    |           |                       |      |  |

|                    |                                | VCC = +5 V or 3V                                            | 0.6 V <sub>CC</sub>   | -         | V <sub>CC</sub> + 0.3 | V    |  |

|                    |                                | VCC =1.8 V                                                  | 1.4                   | -         | V <sub>CC</sub> + 0.3 | V    |  |

| V <sub>hys</sub>   | hysteresis voltage             | on I/O                                                      | 30                    | 75        | 120                   | mV   |  |

|                    | LOW-level input current        | on I/O; VIL = 0                                             | -                     | -         | 600                   | μA   |  |

| I <sub>LH</sub>    | HIGH-level leakage<br>current  | on I/O; $V_{IH} = V_{CC}$                                   | -                     | -         | 10                    | μA   |  |

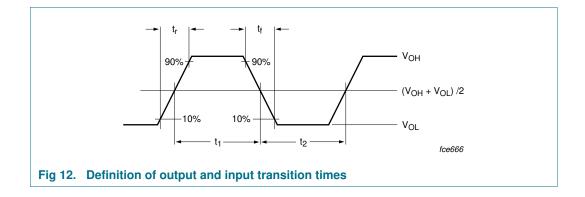

| t <sub>r(i)</sub>  | input rise time                | from $V_{IL}$ max to $V_{IH}$ min                           | _                     |           | 1.2                   | μS   |  |

#### High integrated and low power smart card interface

### Table 7. Characteristics of IC ...continued

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol                | Parameter                     | Conditions                                                                                                              | Min                        | Тур                | Max                         | Unit |

|-----------------------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------------|-----------------------------|------|

| t <sub>f(i)</sub>     | input fall time               | from $V_{IL}$ max to $V_{IH}$ min                                                                                       | -                          | -                  | 1.2                         | μs   |

| t <sub>r(0)</sub>     | output rise time              | $C_L$ < = 80 pF; 10 % to 90 % from 0 to $V_{CC}$                                                                        | -                          | -                  | 0.1                         | μS   |

| t <sub>f(0)</sub>     | output fall time              | $C_L$ < = 80 pF; 10 % to 90 % from 0 to $V_{CC}$                                                                        | -                          | -                  | 0.1                         | μS   |

| R <sub>pu</sub>       | pull-up resistance            | connected to VCC                                                                                                        | 8                          | 10                 | 12                          | kΩ   |

| I <sub>pu</sub>       | pull-up current               | $V_{OH} = 0.9 V_{CC}, C = 80 \text{ pF}$                                                                                | -8                         | -6                 | -4                          | mA   |

| Data lines to         | o the system; pins Ι/ΟμC, AU) | (1μC, AUX2μC (Integrated kΩ                                                                                             | pull-up resistor           | to V <sub>DD</sub> | (INTF))                     |      |

| V <sub>OL</sub>       | LOW-level output voltage      | I <sub>OL</sub> = 1 mA                                                                                                  | 0                          | -                  | 0.3                         | V    |

| V <sub>OH</sub>       | HIGH-level output voltage     | No DC load                                                                                                              | 0.9 V <sub>DD(INTF)</sub>  | -                  | $V_{DD(INTF)} + 0.1$        | V    |

|                       |                               | $I_{OH} \le 40 \ \mu A; \ V_{DD(INTF)} > 2 \ V$                                                                         | 0.75 V <sub>DD(INTF)</sub> | -                  | V <sub>DD(INTF)</sub> + 0.1 | V    |

|                       |                               | $I_{OH} \le 20 \ \mu A; \ V_{DD(INTF)} < 2 \ V$                                                                         | 0.75 V <sub>DD(INTF)</sub> | -                  | $V_{DD(INTF)}$ + 0.1        | V    |

| V <sub>IL</sub>       | LOW-level input voltage       |                                                                                                                         | -0.3                       | -                  | 0.3 V <sub>DD(INTF)</sub>   | V    |

| V <sub>IH</sub>       | HIGH-level input voltage      |                                                                                                                         | 0.7 V <sub>DD(INTF)</sub>  |                    | $V_{DD(INTF)} + 0.3$        | V    |

| V <sub>hys</sub>      | hysteresis voltage            | on I/Ouc                                                                                                                | 0.05 V <sub>DD(INTF)</sub> | -                  | 0.25 V <sub>DD(INTF)</sub>  | V    |

| I <sub>LH</sub>       | HIGH-level leakage<br>current | $V_{IH} = V_{DD(INTF)}$                                                                                                 |                            |                    | 10                          | μA   |

| IIL                   | LOW-level input current       | $V_{IL} = 0$                                                                                                            |                            |                    | 600                         | μA   |

| R <sub>pu</sub>       | pull-up resistance            | connected to VDD(INTF)                                                                                                  | 8                          | 10                 | 12                          | kΩ   |

| t <sub>r(i)</sub>     | input rise time               | from V <sub>IL</sub> max to V <sub>IH</sub> min                                                                         | -                          | -                  | 1.2                         | μS   |

| t <sub>f(i)</sub>     | input fall time               | from $V_{IL}$ max to $V_{IH}$ min                                                                                       | -                          | -                  | 1.2                         | μS   |

| t <sub>r(0)</sub>     | output rise time              | $C_L \le 30 \text{ pF}$ ; 10 % to 90 % from 0 to $V_{DD(INTF)}$                                                         | -                          | -                  | 0.1                         | μS   |

| t <sub>f(0)</sub>     | output fall time              | $\label{eq:CL} \begin{array}{l} C_L \leq 30 \ pF; \ 10 \ \% \ to \ 90 \ \% \\ from \ 0 \ to \ V_{DD(INTF)} \end{array}$ | -                          | -                  | 0.1                         | μs   |

| I <sub>pu</sub>       | pull-up current               | $V_{OH} = 0.9 V_{DD}, C = 30 pF$                                                                                        | -1                         | -                  | -                           | mA   |

| Internal osc          | illator                       |                                                                                                                         |                            |                    |                             |      |

| f <sub>osc(int)</sub> | internal oscillator           | inactive state: osc(int)_Low                                                                                            | 230                        | 315                | 430                         | kHz  |

| · · ·                 | frequency                     | active state: osc(int)_High                                                                                             | 2.0                        | 2.5                | 3.0                         | MHz  |

| Reset outpu           | It to the card (RST)          |                                                                                                                         |                            |                    |                             |      |

| Vo                    | output voltage                | inactive mode; no load                                                                                                  | 0                          | -                  | 0.1                         | V    |

| 0                     |                               | inactive mode; lo= 1 mA                                                                                                 | 0                          | -                  | 0.3                         | V    |

| lo                    | output current                | inactive mode                                                                                                           | -                          | -                  | -1                          | mA   |

| J                     |                               | at grounded pin RST                                                                                                     |                            |                    |                             |      |

| t <sub>d</sub>        | delay time                    | between RSTIN and RST,                                                                                                  | -                          | -                  | 200                         | ns   |

|                       | -                             | RST enabled                                                                                                             |                            |                    |                             |      |

| V <sub>OL</sub>       | LOW-level output voltage      | I <sub>OL</sub> = 200 μA, VCC = +5 V                                                                                    | 0                          | -                  | 0.3                         | V    |

|                       |                               | $I_{OL} = 200 \ \mu\text{A}, \ \text{VCC} = +3 \ \text{V or}$<br>1.8 V                                                  | 0                          | -                  | 0.2                         | V    |

|                       |                               | I <sub>OL</sub> = 20 mA (current limit)                                                                                 | V <sub>CC</sub> - 0.4      | -                  | V <sub>CC</sub>             | V    |

|                       |                               | - · /                                                                                                                   |                            | 1                  |                             | 1    |

#### High integrated and low power smart card interface

#### Table 7. Characteristics of IC ...continued

V<sub>DDP</sub> = 3.3 V; V<sub>DD(INTF)</sub> = 3.3 V; f<sub>XTAL</sub> = 10 MHz; GND = 0 V; T<sub>amb</sub>=25 °C; unless otherwise specified

| Symbol           | Parameter                    | Conditions                                                                    | Min                        | Тур           | Max                        | Unit |

|------------------|------------------------------|-------------------------------------------------------------------------------|----------------------------|---------------|----------------------------|------|

| V <sub>OH</sub>  | HIGH-level output voltage    | I <sub>OH</sub> = -200 μA                                                     | 0.9 V <sub>CC</sub>        | -             | V <sub>CC</sub>            | V    |

|                  |                              | I <sub>OH</sub> = -20 mA (current limit)                                      | 0                          | -             | 0.4                        | V    |

| t <sub>r</sub>   | rise time                    | $C_L = 100 \text{ pF}$<br>$V_{CC} = +5 \text{ V and } +3 \text{ V}$           | -                          | -             | 0.1                        | μS   |

|                  |                              | C <sub>L</sub> = 100 pF<br>V <sub>CC</sub> = +18 V                            | -                          | -             | 0.2                        | μS   |

| t <sub>f</sub>   | fall time                    | $C_L = 100 \text{ pF}$<br>$V_{CC} = +5 \text{ V} \text{ and } +3 \text{ V}$   | -                          | -             | 0.1                        | μS   |

|                  |                              | $\begin{array}{l} C_L = 100 \text{ pF} \\ V_{CC} = +18 \text{ V} \end{array}$ | -                          | -             | 0.2                        | μS   |

| Clock outpu      | It to the card (CLK)         | 1                                                                             |                            |               | 1                          |      |

| Vo               | output voltage               | inactive mode; no load                                                        | 0                          | -             | 0.1                        | V    |

|                  |                              | inactive mode; I <sub>o</sub> = 1 mA                                          | 0                          | -             | 0.3                        | V    |

| lo               | output current               | inactive mode                                                                 | -                          | -             | -1                         | mA   |

|                  |                              | at grounded pin CLK                                                           |                            |               |                            |      |

| V <sub>OL</sub>  | LOW-level output voltage     | I <sub>OL</sub> = 70 mA (current limit)                                       | V <sub>CC</sub> - 0.4      | -             | V <sub>CC</sub>            | V    |

|                  |                              | C1 version                                                                    |                            |               |                            |      |

|                  |                              | I <sub>OL</sub> = 200 μA                                                      | 0                          | -             | 0.3                        | V    |

|                  |                              | C2 Version                                                                    | J                          |               |                            |      |

|                  |                              | I <sub>OL</sub> = 200 μA                                                      | 0                          | -             | 0.15 V <sub>CC</sub>       | V    |

| V <sub>OH</sub>  | HIGH-level output voltage    | I <sub>OH</sub> = -200 μA                                                     | 0.9 V <sub>CC</sub>        | -             | V <sub>CC</sub>            | V    |

| -                |                              | I <sub>OH</sub> = -70 mA (current limit)                                      | 0                          | -             | 0.4                        | V    |

| t <sub>r</sub>   | rise time                    | C <sub>L</sub> = 30 pF [2]                                                    | -                          | -             | 16                         | ns   |

| t <sub>f</sub>   | fall time                    | C <sub>L</sub> = 30 pF [2]                                                    | -                          | -             | 16                         | ns   |

| f <sub>CLK</sub> | frequency on pin CLK         | operational                                                                   | 0                          | -             | 20                         | MHz  |

|                  | duty cycle                   | C <sub>L</sub> = 30 pF [2]                                                    | 45                         | -             | 55                         | %    |

| SR               | slew rate                    | rise and fall; $C_L = 30 \text{ pF}$ ;<br>VCC = +5 V                          | 0.2                        | -             | -                          | V/ns |

|                  |                              | rise and fall; $C_L = 30 \text{ pF}$ ;<br>VCC = +3 V                          | 0.12                       | -             | -                          | V/ns |

|                  |                              | rise and fall; $C_L = 30 \text{ pF}$ ;<br>VCC = +1.8 V                        | 0.072                      | -             | -                          | V/ns |

| Control inp      | uts (pins CS, CMDVCCN, CLK   | DIV1, CLKDIV2, RSTIN, EN_5                                                    | V/ 3VN, EN_1.8V            | N) <u>[3]</u> |                            |      |

| V <sub>IL</sub>  | LOW-level input voltage      |                                                                               | -0.3                       | -             | +0.3 V <sub>DD(INTF)</sub> | V    |

| V <sub>IH</sub>  | HIGH-level input voltage     |                                                                               | 0.7 V <sub>DD(INTF)</sub>  | -             | $V_{DD(INTF)} + 0.3$       | V    |

| V <sub>hys</sub> | hysteresis voltage           | on control input                                                              | 0.05 V <sub>DD(INTF)</sub> | -             | 0.25 V <sub>DD(INTF)</sub> | V    |

| I <sub>LL</sub>  | LOW-level leakage<br>current | $V_{IL} = 0$                                                                  | -                          | -             | 1                          | μA   |

| I <sub>LH</sub>  | HIGH-level leakage current   | $V_{IH} = V_{DD(INTF)}$                                                       | -                          | -             | 1                          | μA   |

| Card presen      | ce input (PRESN); PRESN has  | an integrated pull down resisto                                               | r <u>[3]</u>               |               |                            |      |

| VIL              | LOW-level input voltage      |                                                                               | -0.3                       | -             | +0.3 $V_{DD(INTF)}$        | V    |

| V <sub>IH</sub>  | HIGH-level input voltage     |                                                                               | 0.7 V <sub>DD(INTF)</sub>  |               | $V_{DD(INTF)}$ + 0.3       | V    |