## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

INTEGRATED CIRCUITS

Product specification Supersedes data of 1998 Jun 02 2002 Jan 04

## 2 x 1.4 W BTL audio amplifiers with digital volume control and headphone sensing TDA8552T; TDA8552TS

### FEATURES

- One pin digital volume control (for each channel)

- · Volume setting with up/down pulses

- Auto repeat function on volume setting

- · Headphone sensing

- Maximum gain set by selection pin

- Low sensitivity for EMC radiation

- Internal feedback resistors

- Flexibility in use

- Few external components

- Low saturation voltage of output stage

- · Standby mode controlled by CMOS compatible levels

- · Low standby current

- No switch-on/switch-off plops

- High supply voltage ripple rejection

- Protected against electrostatic discharge

- Outputs short-circuit safe to ground,  $V_{\text{DD}}$  and across the load

- Thermally protected.

### GENERAL DESCRIPTION

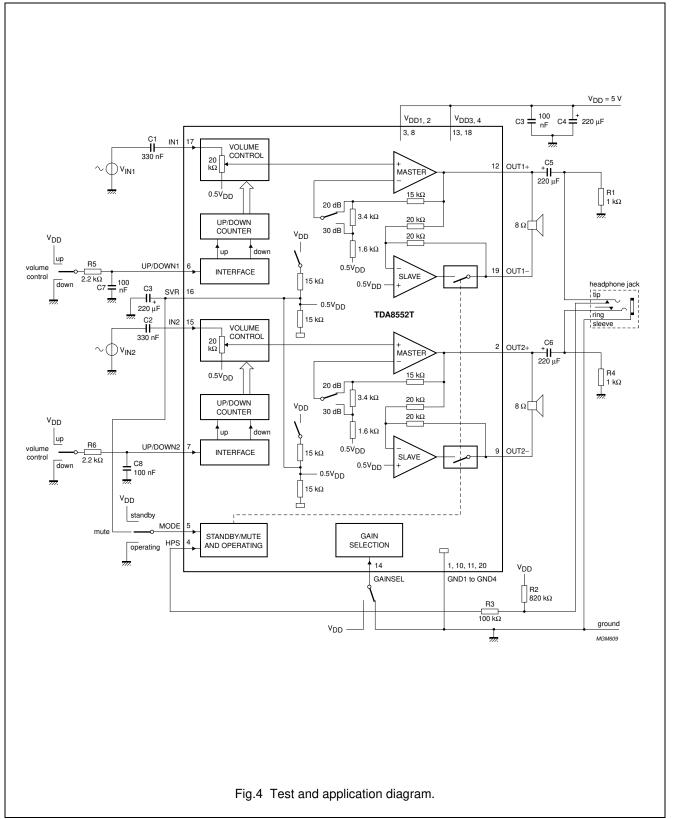

The TDA8552T is a two channel audio power amplifier that provides an output power of  $2 \times 1.4$  W into an 8  $\Omega$  load using a 5 V power supply. The circuit contains two BTL power amplifiers, two digital volume controls and standby/mute logic. Volume and balance of the amplifiers are controlled using two digital input pins which can be driven by simple push-buttons or by a microcontroller.

Using the selection pin (GAINSEL) the maximum gain can be set at 20 or 30 dB. The headphone sense input (HPS) can be used to detect if a headphone is plugged into the jack connector. If a headphone is plugged into the jack connector the amplifier switches from the BTL to the SE mode and the BTL loudspeakers are switched off. This also results in a reduction of quiescent current consumption.

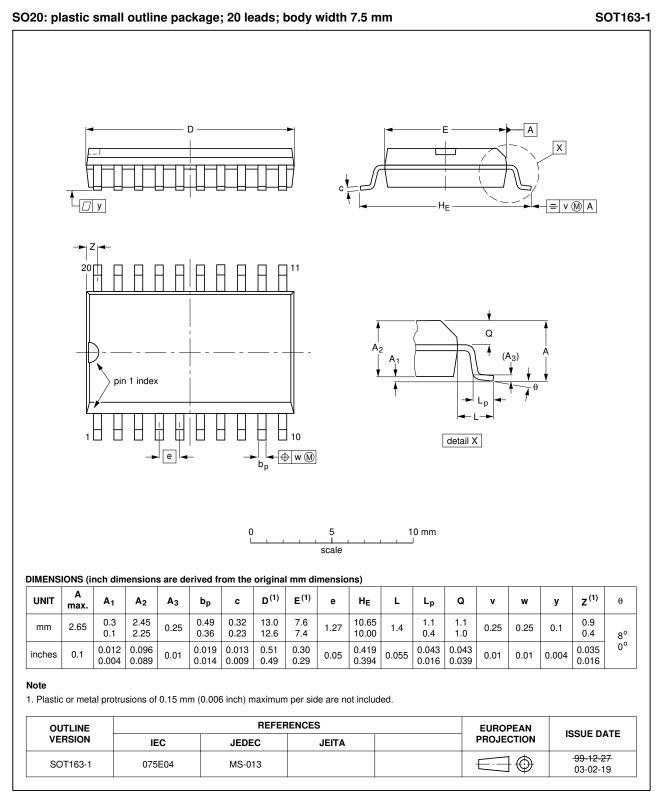

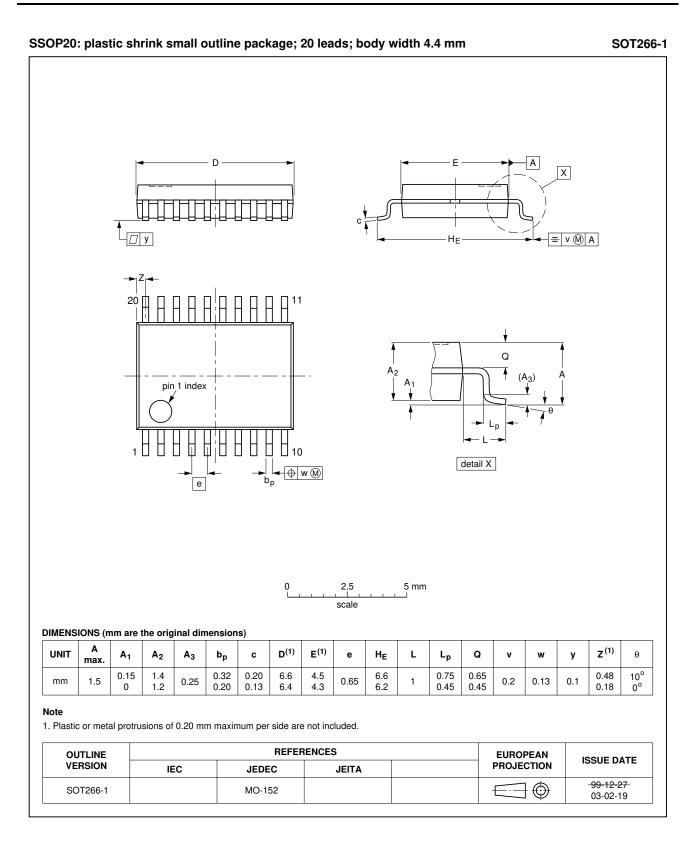

The TDA8552T is contained in a 20-pin small outline package. For the TDA8552TS, which is contained in a 20-pin very small outline package, the maximum output power is limited by the maximum allowed ambient temperature. More information can be found in Section "Thermal design considerations". The SO20 package has the four corner leads connected to the die pad so that the thermal behaviour can be improved by the PCB layout.

#### APPLICATIONS

- Portable consumer products

- Notebook computers

- Communication equipment.

### **ORDERING INFORMATION**

| TYPE      |        | PACKAGE                                                           |          |  |  |  |

|-----------|--------|-------------------------------------------------------------------|----------|--|--|--|

| NUMBER    | NAME   | DESCRIPTION                                                       | VERSION  |  |  |  |

| TDA8552T  | SO20   | plastic small outline package; 20 leads; body width 7.5 mm        | SOT163-1 |  |  |  |

| TDA8552TS | SSOP20 | plastic shrink small outline package; 20 leads; body width 4.4 mm | SOT266-1 |  |  |  |

## TDA8552T; TDA8552TS

### QUICK REFERENCE DATA

| SYMBOL            | PARAMETER                       | CONDITIONS                                   | MIN. | TYP. | MAX. | UNIT |

|-------------------|---------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>DD</sub>   | supply voltage                  |                                              | 2.7  | 5    | 5.5  | V    |

| lq                | quiescent supply current        | BTL mode; V <sub>DD</sub> = 5 V              | -    | 14   | 20   | mA   |

|                   |                                 | BTL mode; V <sub>DD</sub> = 3.3 V            | -    | 10   | 15   | mA   |

|                   |                                 | SE mode; V <sub>DD</sub> = 5 V               | -    | 8.5  | 12   | mA   |

|                   |                                 | SE mode; $V_{DD} = 3.3 V$                    | _    | 5    | 8    | mA   |

| I <sub>stb</sub>  | standby current                 |                                              | -    | 1    | 10   | μA   |

| Po                | output power                    | THD = 10%; $R_L = 8 \Omega$ ; $V_{DD} = 5 V$ | 1    | 1.4  | -    | W    |

| G <sub>v</sub>    | voltage gain                    | low gain; maximum volume                     | _    | 20   | -    | dB   |

|                   |                                 | low gain; minimum volume                     | -    | -60  | -    | dB   |

|                   |                                 | high gain; maximum volume                    | -    | 30   | -    | dB   |

|                   |                                 | high gain; minimum volume                    | _    | -50  | -    | dB   |

| N <sub>step</sub> | number of volume steps          |                                              | -    | 64   | -    |      |

| THD               | total harmonic distortion       | P <sub>o</sub> = 0.5 W                       | -    | 0.1  | -    | %    |

| SVRR              | supply voltage ripple rejection |                                              | 50   | -    | -    | dB   |

## TDA8552T; TDA8552TS

### **BLOCK DIAGRAM**

TDA8552T; TDA8552TS

## 2 x 1.4 W BTL audio amplifiers with digital volume control and headphone sensing

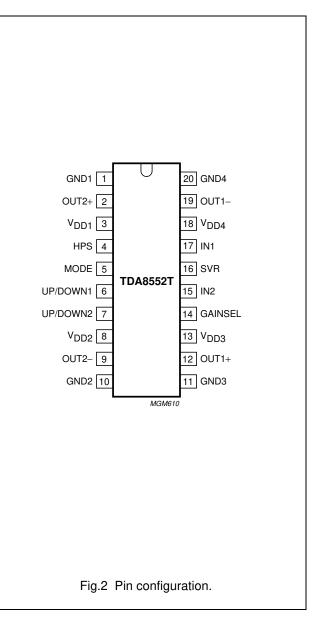

### PINNING

| SYMBOL           | <b>PIN</b> <sup>(1)</sup> | DESCRIPTION                                                                  |

|------------------|---------------------------|------------------------------------------------------------------------------|

|                  |                           |                                                                              |

| GND1             | 1                         | ground 1, substrate/leadframe                                                |

| OUT2+            | 2                         | positive loudspeaker terminal output channel 2                               |

| V <sub>DD1</sub> | 3                         | supply voltage 1                                                             |

| HPS              | 4                         | digital input for headphone sensing                                          |

| MODE             | 5                         | digital trinary input for mode<br>selection (standby, mute and<br>operating) |

| UP/DOWN1         | 6                         | digital trinary input for volume control channel 1                           |

| UP/DOWN2         | 7                         | digital trinary input for volume control channel 2                           |

| V <sub>DD2</sub> | 8                         | supply voltage 2                                                             |

| OUT2-            | 9                         | negative loudspeaker terminal output channel 2                               |

| GND2             | 10                        | ground 2, substrate/leadframe                                                |

| GND3             | 11                        | ground 3, substrate/leadframe                                                |

| OUT1+            | 12                        | positive loudspeaker terminal output channel 1                               |

| V <sub>DD3</sub> | 13                        | supply voltage 3                                                             |

| GAINSEL          | 14                        | digital input for gain selection                                             |

| IN2              | 15                        | audio input channel 2                                                        |

| SVR              | 16                        | half supply voltage, decoupling ripple rejection                             |

| IN1              | 17                        | audio input channel 1                                                        |

| V <sub>DD4</sub> | 18                        | supply voltage 4                                                             |

| OUT1-            | 19                        | negative loudspeaker terminal output channel 1                               |

| GND4             | 20                        | ground 4, substrate/leadframe                                                |

### Note

1. For the SO20 (SOT163-1) package only: the ground pins 1, 10, 11 and 20 are mechanically connected to the leadframe and electrically to the substrate of the die. On the PCB the ground pins can be connected to a copper area to decrease the thermal resistance.

## FUNCTIONAL DESCRIPTION

The TDA8552T is a  $2 \times 1.4$  W BTL audio power amplifier capable of delivering  $2 \times 1.4$  W output power into an 8  $\Omega$ load at THD = 10% using a 5 V power supply. The gain of the amplifier can be set by the digital volume control. The gain in the maximum volume setting is 20 dB (low gain) or 30 dB (high gain). This maximum gain can be selected by the gain selection pin. The headphone sense input (HPS) can be used to detect if a headphone is plugged into the jack connector. If a headphone is plugged into the jack connector the amplifier switches from the BTL to the SE mode and the BTL loudspeakers are switched off. This also results in a reduction of quiescent current consumption. Using the MODE pin the device can be switched to the standby condition, the mute condition or the normal operating condition. The device is protected by an internal thermal shutdown protection mechanism.

### Power amplifier

The power amplifier is a Bridge-Tied Load (BTL) amplifier with a complementary CMOS output stage. The total voltage loss for both output power MOS transistors is within 1 V and with a 5 V supply and an 8  $\Omega$  loudspeaker an output power of 1.4 W can be delivered. The total gain of this power amplifier can be set at 20 or 30 dB by the gain selection pin.

## Gain selection

The gain selection can be used for a fixed gain setting, depending on the application. The gain selection pin must be hard wired to ground (20 dB) or to  $V_{DD}$  (30 dB). Gain selecting during the operation is not advised, switching is not guaranteed plop free.

## Input attenuator

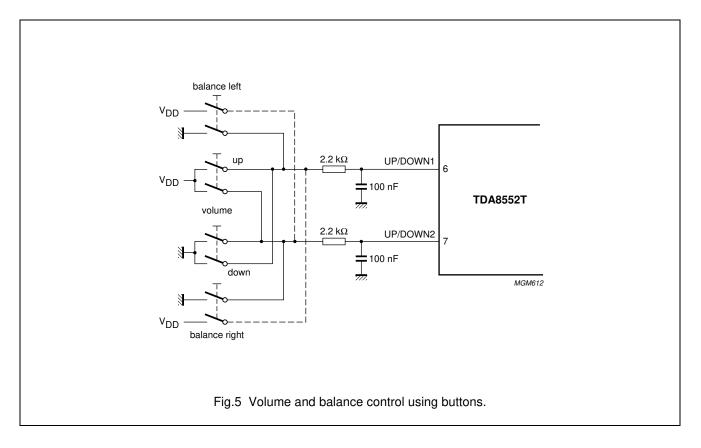

The volume control operates as a digitally controlled input attenuator between the audio input pin and the power amplifier. In the maximum volume control setting the attenuation is 0 dB and in the minimum volume control setting the typical attenuation is 80 dB. The attenuation can be set in 64 steps by the UP/DOWN pin. Both attenuators for channels 1 and 2 are separated from each other and are controlled by there own UP/DOWN pin. Balance control can be arranged by applying UP/DOWN pulses only on pins 6 and 7, see Fig.5.

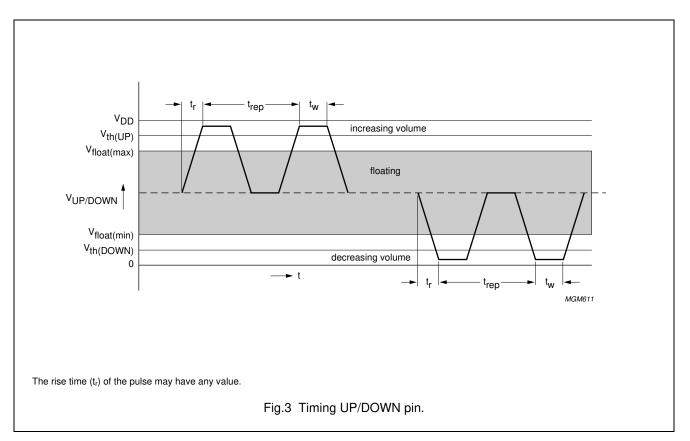

### Volume control

Each attenuator is controlled with its own UP/DOWN pin (trinary input):

TDA8552T; TDA8552TS

- Floating UP/DOWN pin: volume remains unchanged

- Negative pulses: decreasing volume

- Positive pulses: increasing volume.

Each pulse on the UP/DOWN pin results in a change in

gain of  $\frac{80}{64}$  = 1.25 dB (typical value).

In the basic application the UP/DOWN pin is switched to ground or  $V_{DD}$  by a double push-button. When the supply voltage is initially connected, after a complete removal of the supply, the initial state of the volume control is an attenuation of 40 dB (low volume), so the gain of the total amplifier is -20 dB in the low gain setting or -10 dB in the high gain setting. After powering-up, some positive pulses have to be applied to the UP/DOWN pin for turning up to listening volume.

### Auto repeat

If the UP/DOWN pin is LOW or HIGH for the wait time ( $t_{wait}$  in seconds) (one of the keys is pressed) then the device starts making up or down pulses by itself with a frequency

given by  $\frac{1}{t_{rep}}$  (repeat function).

The wait time and the repeat frequency are set using an internal RC oscillator with an accuracy of  $\pm 10\%$ .

### Volume settings in standby mode

When the device is switched with the MODE select pin to the mute or the standby condition, the volume control attenuation setting keeps its value, under the assumption that the voltage on the V<sub>DD</sub> pin does not fall below the minimum supply voltage. After switching the device back to the operation mode, the previous volume setting is maintained. In the standby mode the volume setting is available. The current consumption is very low, approximately 1  $\mu$ A (typ.). In battery fed applications the volume setting can be maintained during battery exchange if there is a supply capacitor available.

#### Mode select pin

The device is in the standby mode (with a very low current consumption) if the voltage at the MODE pin is between  $V_{DD}$  and  $V_{DD} - 0.5$  V. At a mode select voltage level of less than 0.5 V the amplifier is fully operational. In the range between 1 V and  $V_{DD} - 1$  V the amplifier is in the mute condition. The mute condition is useful for using it as a 'fast mute', in this mode the output signal is suppressed, while the volume setting remains at its value. It is advised to keep the device in the mute condition while the input capacitor is being charged. This can be achieved by holding the MODE pin at a level of 0.5V<sub>DD</sub>, or by waiting approximately 100 ms before giving the first volume-UP pulses.

#### Headphone sense pin (HPS)

A headphone can be connected to the amplifier by using a coupling capacitor for each channel. The common ground pin of the headphone is connected to the ground of the amplifier, see Fig.4. By using the HPS pin as illustrated in Fig.4, the TDA8552T detects if a headphone jack plug is inserted into the connector.

## TDA8552T; TDA8552TS

When no headphone is plugged in, the voltage level at the HPS pin will remain LOW. A voltage less than  $V_{DD} - 1$  V at the HPS pin will keep the device in the BTL mode, thus the loudspeakers can be operational. If the HPS pin is not connected then the device will remain in the BTL mode.

When a headphone is plugged into the connector, the voltage at the HPS pin will be set to  $V_{DD}$ . The device then switches to the Single-Ended (SE) mode, this means that the slave power amplifiers at the outputs OUT1– and OUT2– will be switched to the standby mode. This results in floating outputs OUT1– and OUT2–, the loudspeaker signal is thus attenuated by approximately 80 dB and only the headphone can operate.

One of the benefits of this system is that the loudspeaker current does not flow through the jack connector switch, which could give some output power loss. The other benefit is that the quiescent current is reduced when the headphone jack is inserted.

## TDA8552T; TDA8552TS

### LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL           | PARAMETER                            | CONDITIONS | MIN. | MAX.                  | UNIT |

|------------------|--------------------------------------|------------|------|-----------------------|------|

| V <sub>DD</sub>  | supply voltage                       | operating  | -0.3 | +5.5                  | V    |

| Vi               | input voltage                        |            | -0.3 | V <sub>DD</sub> + 0.3 | V    |

| I <sub>ORM</sub> | repetitive peak output current       |            | _    | 1                     | A    |

| T <sub>stg</sub> | storage temperature                  |            | -55  | +150                  | °C   |

| T <sub>amb</sub> | operating ambient temperature        |            | -40  | +85                   | °C   |

| V <sub>sc</sub>  | AC and DC short-circuit safe voltage |            | _    | 5.5                   | V    |

| P <sub>tot</sub> | maximum power dissipation            | SO20       | _    | 2.2                   | W    |

|                  |                                      | SSOP20     | _    | 1.1                   | W    |

### THERMAL CHARACTERISTICS

See Section "Thermal design considerations" in Chapter "Test and application information".

| SYMBOL               | PARAMETER                                   | CONDITIONS   | VALUE | UNIT |

|----------------------|---------------------------------------------|--------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |              |       |      |

|                      | for the TDA8552T (SO20)                     | in free air  | 60    | K/W  |

|                      |                                             | extra copper | 55    | K/W  |

|                      | for the TDA8552TS (SSOP20)                  | in free air  | 110   | K/W  |

|                      |                                             | extra copper | 80    | K/W  |

### Table 1Power rating; note 1

|                     |                                   |                                 |           | MUSIC POWER          |                            |        |  |

|---------------------|-----------------------------------|---------------------------------|-----------|----------------------|----------------------------|--------|--|

| V <sub>DD</sub> (V) | <b>R<sub>L</sub> (</b> Ω <b>)</b> | P <sub>o (w)</sub><br>THD = 10% | OPERATION | D (M)                | T <sub>amb(max)</sub> (°C) |        |  |

|                     |                                   |                                 |           | P <sub>max</sub> (W) | SO20                       | SSOP20 |  |

| 3.3                 | 4                                 | 0.9                             | BTL       | 0.55                 | 120                        | 106    |  |

| 3.3                 | 8                                 | 0.6                             | BTL       | 0.28                 | 134                        | 127    |  |

| 3.3                 | 16                                | 0.3                             | BTL       | 0.14                 | 142                        | 139    |  |

| 3.3                 | 32SE                              | 0.035                           | headphone | 0.03                 | 150                        | 150    |  |

| 5.0                 | 4                                 | 2.0                             | BTL       | 1.25                 | 81                         | 50     |  |

| 5.0                 | 8                                 | 1.4                             | BTL       | 0.65                 | 114                        | 98     |  |

| 5.0                 | 16                                | 0.8                             | BTL       | 0.32                 | 132                        | 124    |  |

| 5.0                 | 32SE                              | 0.09                            | headphone | 0.07                 | 146                        | 144    |  |

|                     |                                   |                                 |           | continuous sine wave |                            |        |  |

| 3.3                 | 4                                 | 0.9                             | BTL       | 1.1                  | 89                         | 62     |  |

| 5                   | 8                                 | 1.4                             | BTL       | 1.25                 | 81                         | 50     |  |

### Note

1. The power rating is based on  $R_{th(j-a)}$  with recommended copper pattern of at least  $4 \times 1 \text{ cm}^2$  to the corner leads and copper under the IC package.

## TDA8552T; TDA8552TS

### QUALITY SPECIFICATION

Quality specification in accordance with "SNW-FQ-611 part E", if this type is used as an audio amplifier.

#### **DC CHARACTERISTICS**

$V_{DD}$  = 5 V;  $T_{amb}$  = 25 °C;  $R_L$  = 8  $\Omega$ ;  $V_{MODE}$  = 0 V; total gain setting at 7 dB; according to Fig.4.; unless otherwise specified.

| SYMBOL                  | PARAMETER                  | CONDITIONS                                              | MIN.         | TYP. | MAX.            | UNIT |

|-------------------------|----------------------------|---------------------------------------------------------|--------------|------|-----------------|------|

| V <sub>DD</sub>         | supply voltage             |                                                         | 2.7          | 5    | 5.5             | V    |

| I <sub>DD</sub>         | supply current             | BTL mode; $V_{DD} = 5 V$ ;<br>$R_L = \infty$ ; note 1   | -            | 14   | 20              | mA   |

|                         |                            | SE mode; V <sub>DD</sub> = 5 V                          | _            | 8.5  | 12              | mA   |

|                         |                            | BTL mode; $V_{DD} = 3.3 V$ ;<br>$R_L = \infty$ ; note 1 | -            | 10   | 15              | mA   |

|                         |                            | SE mode; $V_{DD}$ = 3.3 V                               | _            | 5    | 8               | mA   |

| I <sub>stb</sub>        | standby current            | $V_{MODE} = V_{DD}$                                     | _            | 1    | 10              | μA   |

| Vo                      | DC output voltage          | note 2                                                  | _            | 2.5  | -               | V    |

| $ V_{OUT+} - V_{OUT-} $ | differential output offset | GAINSEL = 0 V                                           | _            | _    | 50              | mV   |

|                         | voltage                    | $GAINSEL = V_{DD}$                                      | -            | -    | 150             | mV   |

| Mode select pin         |                            |                                                         |              |      |                 | •    |

| V <sub>MODE</sub>       | input voltage              | standby                                                 | $V_{DD}-0.5$ | _    | V <sub>DD</sub> | V    |

|                         |                            | mute                                                    | 1            | _    | $V_{DD}-1.4$    | V    |

|                         |                            | operating                                               | 0            | _    | 0.5             | V    |

| I <sub>MODE</sub>       | input current              | $0 < V_{MODE} < V_{DD}$                                 | _            | _    | 1               | μA   |

| $\alpha_{mute}$         | mute attenuation           | note 3                                                  | 80           | tbf  | -               | dB   |

| Gain select pin         |                            |                                                         |              |      |                 | •    |

| V <sub>GAINSEL</sub>    | input voltage              | low gain (20 dB)                                        | 0            | -    | 0.6             | V    |

|                         |                            | high gain (30 dB)                                       | 4.1          | —    | V <sub>DD</sub> | V    |

| IGAINSEL                | input current              |                                                         | -            | _    | 1               | μA   |

| Headphone sens          | se pin                     |                                                         |              |      |                 | •    |

| V <sub>HPS</sub>        | input voltage              | SE mode; headphone detected                             | $V_{DD} - 1$ | _    | V <sub>DD</sub> | V    |

| I <sub>HPS</sub>        | input current              |                                                         | _            | _    | 1               | μA   |

## TDA8552T; TDA8552TS

| SYMBOL                   | PARAMETER                                                | CONDITIONS                 | MIN. | TYP. | MAX.            | UNIT |

|--------------------------|----------------------------------------------------------|----------------------------|------|------|-----------------|------|

| Volume contro            | I<br>I                                                   | 1                          |      |      |                 |      |

| t <sub>W</sub>           | pulse width                                              |                            | 50   | -    | -               | ns   |

| t <sub>rep</sub>         | pulse repetition time                                    |                            | 100  | -    | -               | ns   |

| V <sub>th(up)</sub>      | UP/DOWN pin UP threshold level                           |                            | 4.1  | -    | V <sub>DD</sub> | V    |

| V <sub>float(max)</sub>  | UP/DOWN pin floating high level                          |                            | -    | _    | 3.4             | V    |

| V <sub>float(min)</sub>  | UP/DOWN pin floating low level                           |                            | 1.0  | -    | -               | V    |

| V <sub>th(down)</sub>    | UP/DOWN pin DOWN<br>threshold level                      |                            | 0    | _    | 0.6             | V    |

| I <sub>I(up/down)</sub>  | input current UP/DOWN pin                                | $0 < V_{UP/DOWN} < V_{DD}$ | -    | -    | 200             | μA   |

| t <sub>wait</sub>        | auto repeat wait time                                    |                            | -    | 500  | _               | ms   |

| t <sub>rep</sub>         | repeat time                                              | key pressed                | -    | 130  | -               | ms   |

| Volume attenua           | ator                                                     |                            |      |      |                 |      |

| G <sub>v(l)</sub>        | low gain; maximum volume<br>(including power amplifier)  |                            | 19   | 20   | 21              | dB   |

|                          | low gain; minimum volume<br>(including power amplifier)  |                            | tbf  | -60  | tbf             | dB   |

| G <sub>v(h)</sub>        | high gain; maximum volume<br>(including power amplifier) |                            | 29   | 30   | 31              | dB   |

|                          | high gain; minimum volume<br>(including power amplifier) |                            | tbf  | -50  | tbf             | dB   |

| N <sub>step</sub>        | number of gain steps                                     |                            | -    | 64   | _               |      |

| $\Delta G_v$             | variation of gain per step                               |                            | -    | 1.25 | -               | dB   |

| Zi                       | input impedance                                          |                            | 14   | 20   | -               | kΩ   |

| V <sub>i(max)(rms)</sub> | maximum input voltage<br>(RMS value)                     |                            | -    | -    | 1.75            | V    |

- 1. With a load connected at the outputs the quiescent current will increase, the maximum of this increase being equal to  $2 \times \left(\frac{DC \text{ output offset voltage}}{R_L}\right)$

- 2. The DC output voltage with respect to ground is approximately  $0.5V_{DD}$ .

- 3. Output voltage in mute position is measured with an input of 1 V (RMS) in a bandwidth of 20 kHz, so including noise, gain select pin is LOW (0 V).

## TDA8552T; TDA8552TS

### AC CHARACTERISTICS (V<sub>DD</sub> = 3.3 V)

$T_{amb} = 25 \text{ °C}$ ;  $R_L = 8 \Omega$ ; f = 1 kHz; total gain setting at 7 dB;  $V_{MODE} = 0 \text{ V}$ ; gain select pin is at 0 V (maximum gain = 20 dB); according to Fig.4.

| SYMBOL              | PARAMETER                       | CONDITIONS                                        | MIN. | TYP. | MAX. | UNIT |

|---------------------|---------------------------------|---------------------------------------------------|------|------|------|------|

| Po                  | output power                    | THD = 10%; $R_L$ = 4 $\Omega$                     | -    | 0.9  | _    | W    |

|                     |                                 | THD = 10%; $R_L$ = 8 $\Omega$                     | -    | 0.6  | -    | W    |

|                     |                                 | THD = 10%; $R_L$ = 16 $\Omega$                    | -    | 0.3  | -    | W    |

|                     |                                 | THD = 0.5%; $R_L$ = 4 $\Omega$                    | -    | 0.6  | -    | W    |

|                     |                                 | THD = 0.5%; R <sub>L</sub> = 8 $\Omega$           | -    | 0.4  | -    | W    |

|                     |                                 | THD = 0.5%; $R_L$ = 16 $\Omega$                   | -    | 0.2  | -    | W    |

| THD                 | total harmonic distortion       | P <sub>o</sub> = 0.1 W; note 1                    | -    | 0.1  | -    | %    |

| V <sub>o(n)</sub>   | noise output voltage            | note 2                                            | -    | 60   | -    | μV   |

| SVRR                | supply voltage ripple rejection | note 3                                            | tbf  | 55   | _    | dB   |

| V <sub>i(max)</sub> | maximum input voltage           | THD = 1%;<br>$G_v = -50 \text{ to } 0 \text{ dB}$ | -    | -    | 1.1  | V    |

| $\alpha_{sup}$      | channel suppression             | $V_{HPS} = V_{DD}$ ; note 4                       | -    | 80   | -    | dB   |

| $\alpha_{cs}$       | channel separation              |                                                   | -    | 55   | -    | dB   |

- 1. Volume setting at maximum.

- 2. The noise output voltage is measured at the output in a frequency band from 20 Hz to 20 kHz (unweighted),  $R_{source} = 0 \Omega$ , gain select pin is LOW (0 V).

- 3. Supply voltage ripple rejection is measured at the output, with a source impedance of  $R_{source} = 0 \Omega$  at the input. The ripple voltage is a sine wave with a frequency of 1 kHz and an amplitude of 100 mV (RMS) is applied to the positive supply rail, gain select pin is LOW (0 V).

- 4. Channel suppression is measured at the output with a source impedance of  $R_{source} = 0 \Omega$  at the input and a frequency of 1 kHz. The output level in the operating single-ended channel (OUT+) is set at 2 V (RMS).

## TDA8552T; TDA8552TS

### AC CHARACTERISTICS (V<sub>DD</sub> = 5 V)

$T_{amb} = 25 \text{ °C}; R_L = 8 \Omega; f = 1 \text{ kHz};$  total gain setting at 7 dB;  $V_{MODE} = 0 \text{ V};$  Gain select pin is at 0 V (maximum gain = 20 dB); according to Fig.4; package is SO20.

| SYMBOL              | PARAMETER                       | CONDITIONS                                        | MIN. | TYP. | MAX. | UNIT |

|---------------------|---------------------------------|---------------------------------------------------|------|------|------|------|

| Po                  | output power                    | THD = 10%; $R_L = 8 \Omega$                       | 1.0  | 1.4  | -    | W    |

|                     |                                 | THD = 10%; $R_L$ = 16 $\Omega$                    | -    | 0.8  | -    | W    |

|                     |                                 | THD = 0.5%; R <sub>L</sub> = 8 $\Omega$           | 0.6  | 1.0  | -    | W    |

|                     |                                 | THD = 0.5%; $R_L$ = 16 $\Omega$                   | -    | 0.6  | -    | W    |

| THD                 | total harmonic distortion       | P <sub>o</sub> = 0.1 W; note 1                    | -    | 0.15 | 0.4  | %    |

|                     |                                 | P <sub>o</sub> = 0.5 W; note 1                    | -    | 0.1  | 0.3  | %    |

| V <sub>o(n)</sub>   | noise output voltage            | GAINSEL. = 0 V; note 2                            | -    | 60   | 100  | μV   |

|                     |                                 | GAINSEL. = V <sub>DD</sub> ; note 2               | -    | 100  | -    | μV   |

| SVRR                | supply voltage ripple rejection | note 3                                            | 50   | 55   | _    | dB   |

| V <sub>i(max)</sub> | a maximum input voltage         | THD = 1%;<br>$G_v = -50 \text{ to } 0 \text{ dB}$ | -    | -    | 1.75 | V    |

| $\alpha_{sup}$      | channel suppression             | $V_{HPS} = V_{DD}$ ; note 4                       | 70   | 80   | -    | dB   |

| $\alpha_{cs}$       | channel separation              |                                                   | 50   | -    | -    | dB   |

- 1. Volume setting at maximum.

- 2. The noise output voltage is measured at the output in a frequency band from 20 Hz to 20 kHz (unweighted),  $R_{source} = 0 \Omega$ .

- 3. Supply voltage ripple rejection is measured at the output, with a source impedance of  $R_{source} = 0 \Omega$  at the input. The ripple voltage is a sine wave with a frequency of 1 kHz and an amplitude of 100 mV (RMS) is applied to the positive supply rail, gain select pin is LOW (0 V).

- 4. Channel suppression is measured at the output with a source impedance of  $R_{source} = 0 \Omega$  at the input and a frequency of 1 kHz. The output level in the operating single-ended channel (OUT+) is set at 1 V (RMS).

## TDA8552T; TDA8552TS

## AC CHARACTERISTICS (FOR HEADPHONE; $R_L = 32 \Omega$ ; CONNECTED SE)

$V_{DD} = 5 \text{ V}$ ;  $T_{amb} = 25 \text{ °C}$ ; f = 1 kHz; total gain setting at 20 dB;  $V_{MODE} = 0 \text{ V}$ ; gain select pin is 0 V (maximum gain = 20 dB); according to Fig.4.

| SYMBOL              | PARAMETER                       | CONDITIONS                         | MIN. | TYP. | MAX. | UNIT |

|---------------------|---------------------------------|------------------------------------|------|------|------|------|

| Po                  | output power                    | THD = 10%; V <sub>DD</sub> = 3.3 V | -    | 35   | -    | mW   |

|                     |                                 | THD = 10%; $V_{DD}$ = 5.0 V        | -    | 90   | -    | mW   |

|                     |                                 | THD = 0.5%; $V_{DD}$ = 3.3 V       | -    | 25   | -    | mW   |

|                     |                                 | THD = 0.5%; $V_{DD}$ = 5.0 V       | -    | 60   | -    | mW   |

| THD                 | total harmonic distortion       | $P_0 = 60 \text{ mW}$              | -    | 0.04 | -    | %    |

| V <sub>o(n)</sub>   | noise output voltage            | note 1                             | -    | 60   | 100  | μV   |

| SVRR                | supply voltage ripple rejection | note 2                             | 50   | 55   | -    | dB   |

| V <sub>i(max)</sub> | maximum input voltage           | THD = 1%;<br>$G_v = -50$ to 0 dB   | _    | _    | 1.75 | V    |

| $\alpha_{cs}$       | channel separation              |                                    | 50   | -    | -    | dB   |

- 1. The noise output voltage is measured at the output in a frequency band from 20 Hz to 20 kHz (unweighted),  $R_{source} = 0 \Omega$ , gain select pin is LOW (0 V).

- 2. Supply voltage ripple rejection is measured at the output, with a source impedance of  $R_{source} = 0 \Omega$  at the input. The ripple voltage is a sine wave with a frequency of 1 kHz and an amplitude of 100 mV (RMS) is applied to the positive supply rail, gain select pin is LOW (0 V).

## TDA8552T; TDA8552TS

### TEST AND APPLICATION INFORMATION

#### **Test conditions**

$\begin{array}{l} T_{amb}=25^\circ C \mbox{ if not specially mentioned; } V_{DD}=5 \mbox{ V;} \\ f=1 \mbox{ kHz}, \mbox{ R}_L=8 \ \Omega, \mbox{ G}_v=20 \mbox{ dB, audio band-pass} \\ 22 \mbox{ Hz to } 22 \mbox{ kHz}. \mbox{ The thermal resistance (in standard print, without extra copper) = 110 \mbox{ K/W for the SSOP20; the maximum sine wave power dissipation is:} \end{array}$

$\frac{150 - 25}{110} = 1.14 \text{ W}$

For  $T_{amb} = 60$  °C the maximum total power dissipation is: 150 - 60 0.82 W

$\frac{150 - 60}{110} = 0.82 \text{ W}$

#### Thermal design considerations

The 'measured' thermal resistance of the IC package is highly dependent on the configuration and size of the application board. All surface mount packages rely on the traces of the PCB to conduct heat away from the package. To improve the heat flow, a significant area on the PCB must be attached to the (ground) pins. Data may not be comparable between different semiconductor manufacturers because the application boards and test methods are not (yet) standardized. Also, the thermal performance of packages for a specific application may be different than presented here, because the configuration of the application boards (copper area) may be different. NXP Semiconductors uses FR-4 type application boards with 1 oz copper traces with solder coating Solder Resist Mask (SRM).

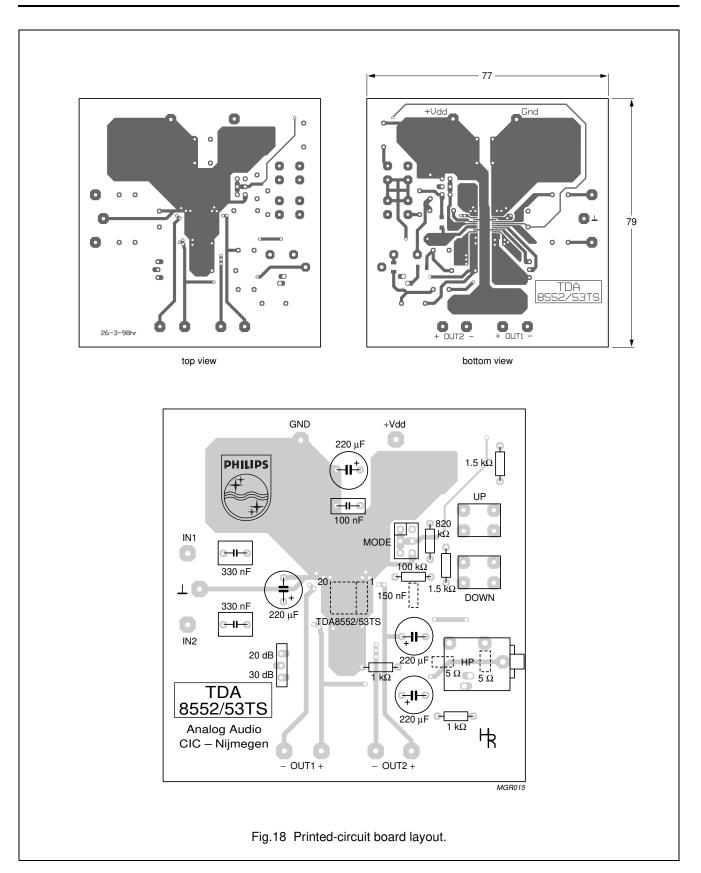

The SSOP20 package has improved thermal conductivity which reduces the thermal resistance. Using a practical PCB layout (see Fig.18) with wider copper tracks to the corner pins and just under the IC, the thermal resistance from junction to ambient can be reduced to approximately 80 K/W. For  $T_{amb} = 60$  °C the maximum total power

dissipation for this PCB layout is:  $\frac{150-60}{80} = 1.12 \text{ W}$

The thermal resistance for the SO20 is approximately 55 K/W if applied to a PCB with wider copper tracks to the corner pins and just under the body of the IC. The maximum total power dissipation for this practical application is:

$$\frac{150-60}{55} = 1.63 \text{ W}$$

## TDA8552T; TDA8552TS

#### **BTL** application

The BTL application diagram is illustrated in Fig.4.

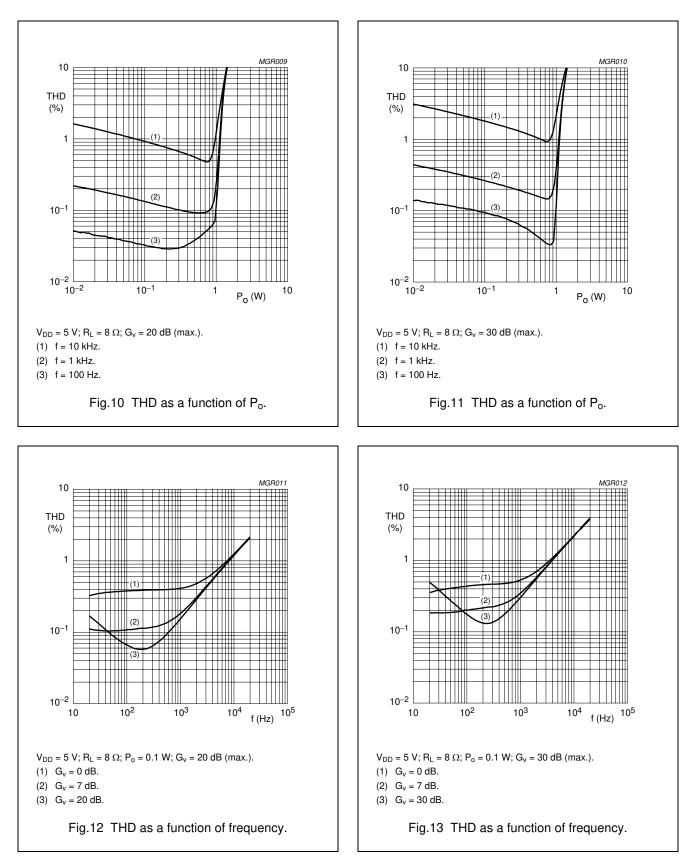

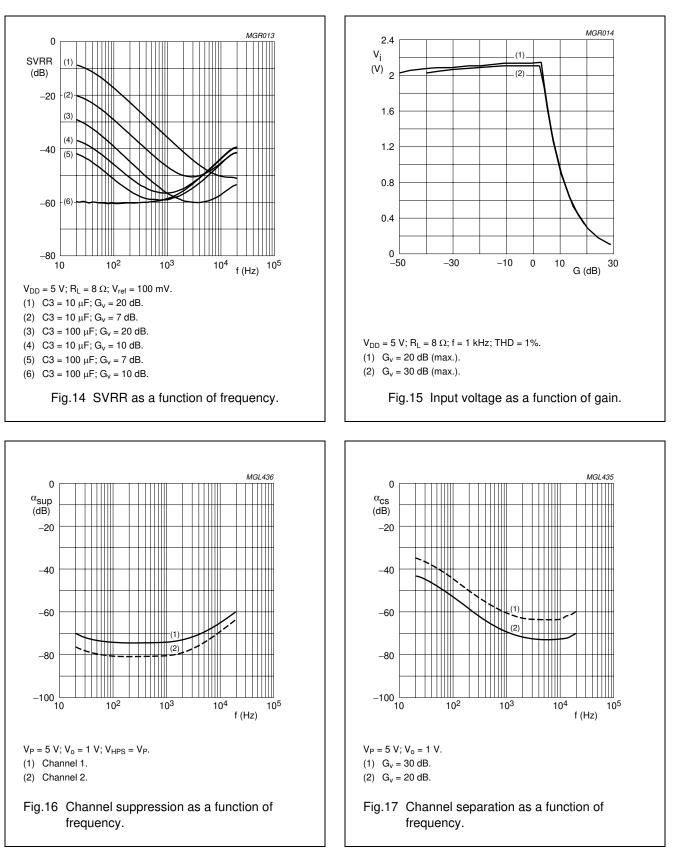

The quiescent current has been measured without any load impedance. The total harmonic distortion as a function of frequency was measured with a low-pass filter of 80 kHz. The value of capacitor C3 influences the behaviour of the SVRR at low frequencies, increasing the value of C3 increases the performance of the SVRR.

#### **Headphone application**

$\label{eq:Tamb} \begin{array}{l} T_{amb}=25\,^{\circ}C \text{ if not specially mentioned, } V_{DD}=5 \text{ V},\\ f=1 \text{ kHz}, \text{ R}_L=32 \ \Omega, \ G_v=14 \text{ dB}, \text{ audio band-pass}\\ 22 \text{ Hz to } 22 \text{ kHz}. \end{array}$

For headphone application diagram see: Fig.4

If a headphone is plugged into the headphone jack, the HPS pin will switch-off the outputs of the SLAVE output stage, this results in a mute attenuation >80 dB for the loudspeakers. In this condition the quiescent current will be reduced.

#### **General remarks**

Reduction of the value of capacitor C3 results in a decrease of the SVRR performance at low frequencies.

The capacitor value of C5 and C6 in combination with the load impedance of the headphone determines the low frequency behaviour.

To prevent against high output currents during inserting the headphone into the headphone jack, resistors of 5.1  $\Omega$  have to be connected in series with the SE output lines.

The UP/DOWN pin can be driven by a 3-state logic output stage (microprocessor) without extra external components. If the UP/DOWN pin is driven by push-buttons, then it is advised to have an RC-filter between the buttons and the UP/DOWN pin. Advised values for the RC-filter are 2.2 k $\Omega$  and 100 nF. Resistor R4 is not necessary for basic operation, but is advised to keep C6 charged to a voltage of  $0.5V_{DD}$  This has the advantage that the plop noise when inserting the headphone plug is minimal. If the headphone sense function (HPS) is not used then the HPS-pin 4 should be hard-wired to ground. This pin should never be left unconnected.

Using double push buttons, the volume step for both channels can be controlled. When for the balance control only a single contact is used, the balance steps are 1.25 dB. If double contacts are used for the balance buttons and the dashed connection is made, then the balance steps are 2.5 dB.

#### Application without volume control

If pins 6, 7 and 8 are hardwired together the device operates with the volume control setting at maximum.

When the supply voltage is connected and the device is switched from standby to mute or operating for the first time then the gain is ramped up from -20 dB to +20 dB. This takes approximately 5 s.

This maximum gain setting is maintained until the supply voltage drops below the minimum value.

### PACKAGE OUTLINES

### SOLDERING

### Introduction to soldering surface mount packages

This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our *"Data Handbook IC26; Integrated Circuit Packages"* (document order number 9398 652 90011).

There is no soldering method that is ideal for all surface mount IC packages. Wave soldering can still be used for certain surface mount ICs, but it is not suitable for fine pitch SMDs. In these situations reflow soldering is recommended.

### **Reflow soldering**

Reflow soldering requires solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the printed-circuit board by screen printing, stencilling or pressure-syringe dispensing before package placement.

Several methods exist for reflowing; for example, convection or convection/infrared heating in a conveyor type oven. Throughput times (preheating, soldering and cooling) vary between 100 and 200 seconds depending on heating method.

Typical reflow peak temperatures range from 215 to 250 °C. The top-surface temperature of the packages should preferable be kept below 220 °C for thick/large packages, and below 235 °C for small/thin packages.

### Wave soldering

Conventional single wave soldering is not recommended for surface mount devices (SMDs) or printed-circuit boards with a high component density, as solder bridging and non-wetting can present major problems.

To overcome these problems the double-wave soldering method was specifically developed.

If wave soldering is used the following conditions must be observed for optimal results:

- Use a double-wave soldering method comprising a turbulent wave with high upward pressure followed by a smooth laminar wave.

- For packages with leads on two sides and a pitch (e):

- larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be parallel to the transport direction of the printed-circuit board;

- smaller than 1.27 mm, the footprint longitudinal axis must be parallel to the transport direction of the printed-circuit board.

The footprint must incorporate solder thieves at the downstream end.

• For packages with leads on four sides, the footprint must be placed at a 45° angle to the transport direction of the printed-circuit board. The footprint must incorporate solder thieves downstream and at the side corners.

During placement and before soldering, the package must be fixed with a droplet of adhesive. The adhesive can be applied by screen printing, pin transfer or syringe dispensing. The package can be soldered after the adhesive is cured.

Typical dwell time is 4 seconds at 250 °C. A mildly-activated flux will eliminate the need for removal of corrosive residues in most applications.

### Manual soldering

Fix the component by first soldering two diagonally-opposite end leads. Use a low voltage (24 V or less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds at up to  $300 \,^{\circ}$ C.

When using a dedicated tool, all other leads can be soldered in one operation within 2 to 5 seconds between 270 and 320  $^\circ C.$

## TDA8552T; TDA8552TS

### Suitability of surface mount IC packages for wave and reflow soldering methods

| PACKAGE                                             | SOLDERING METHOD                  |                       |  |

|-----------------------------------------------------|-----------------------------------|-----------------------|--|

| PACKAGE                                             | WAVE                              | REFLOW <sup>(1)</sup> |  |

| BGA, HBGA, LFBGA, SQFP, TFBGA                       | not suitable                      | suitable              |  |

| HBCC, HLQFP, HSQFP, HSOP, HTQFP, HTSSOP, HVQFN, SMS | not suitable <sup>(2)</sup>       | suitable              |  |

| PLCC <sup>(3)</sup> , SO, SOJ                       | suitable                          | suitable              |  |

| LQFP, QFP, TQFP                                     | not recommended <sup>(3)(4)</sup> | suitable              |  |

| SSOP, TSSOP, VSO                                    | not recommended <sup>(5)</sup>    | suitable              |  |

- 1. All surface mount (SMD) packages are moisture sensitive. Depending upon the moisture content, the maximum temperature (with respect to time) and body size of the package, there is a risk that internal or external package cracks may occur due to vaporization of the moisture in them (the so called popcorn effect). For details, refer to the Drypack information in the *"Data Handbook IC26; Integrated Circuit Packages; Section: Packing Methods"*.

- 2. These packages are not suitable for wave soldering. On versions with the heatsink on the bottom side, the solder cannot penetrate between the printed-circuit board and the heatsink. On versions with the heatsink on the top side, the solder might be deposited on the heatsink surface.

- 3. If wave soldering is considered, then the package must be placed at a 45° angle to the solder wave direction. The package footprint must incorporate solder thieves downstream and at the side corners.

- 4. Wave soldering is only suitable for LQFP, TQFP and QFP packages with a pitch (e) equal to or larger than 0.8 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.65 mm.

- 5. Wave soldering is only suitable for SSOP and TSSOP packages with a pitch (e) equal to or larger than 0.65 mm; it is definitely not suitable for packages with a pitch (e) equal to or smaller than 0.5 mm.

TDA8552T; TDA8552TS

#### DATA SHEET STATUS

| DOCUMENT<br>STATUS <sup>(1)</sup> | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITION                                                                            |

|-----------------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| Objective data sheet              | Development                      | This document contains data from the objective specification for product development. |

| Preliminary data sheet            | Qualification                    | This document contains data from the preliminary specification.                       |

| Product data sheet                | Production                       | This document contains the product specification.                                     |

#### Notes

- 1. Please consult the most recently issued document before initiating or completing a design.

- The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### DISCLAIMERS

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.