Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **INTEGRATED CIRCUITS**

## DATA SHEET

# **TDA8922** $2 \times 25$ W class-D power amplifier

Objective specification

2003 Mar 20

## $\ensuremath{\text{2}} \times \ensuremath{\text{25}}$ W class-D power amplifier

**TDA8922**

| CONTENT        | rs                                                                             | 17               | PACKAGE OUTLINE                                                    |

|----------------|--------------------------------------------------------------------------------|------------------|--------------------------------------------------------------------|

| 1              | FEATURES                                                                       | 18               | SOLDERING                                                          |

| 2              | APPLICATIONS                                                                   | 18.1             | Introduction                                                       |

| 3              | GENERAL DESCRIPTION                                                            | 18.2<br>18.2.1   | Through-hole mount packages Soldering by dipping or by solder wave |

| 4              | QUICK REFERENCE DATA                                                           | 18.2.2           | Manual soldering                                                   |

| 5              | ORDERING INFORMATION                                                           | 18.3             | Surface mount packages                                             |

| 6              | BLOCK DIAGRAM                                                                  | 18.3.1<br>18.3.2 | Reflow soldering Wave soldering                                    |

| 7              | PINNING                                                                        | 18.3.3           | Manual soldering                                                   |

| 8              | FUNCTIONAL DESCRIPTION                                                         | 18.4             | Suitability of IC packages for wave, reflow and                    |

| 8.1            | General                                                                        | 40               | dipping soldering methods                                          |

| 8.2            | Pulse width modulation frequency                                               | 19               | DATA SHEET STATUS                                                  |

| 8.3            | Protections                                                                    | 20               | DEFINITIONS                                                        |

| 8.3.1<br>8.3.2 | Overtemperature Short-circuit across loudspeaker terminals and to supply lines | 21               | DISCLAIMERS                                                        |

| 8.3.3          | Start-up safety test                                                           |                  |                                                                    |

| 8.3.4          | Supply voltage alarm                                                           |                  |                                                                    |

| 8.4            | Differential audio inputs                                                      |                  |                                                                    |

| 9              | LIMITING VALUES                                                                |                  |                                                                    |

| 10             | THERMAL CHARACTERISTICS                                                        |                  |                                                                    |

| 11             | QUALITY SPECIFICATION                                                          |                  |                                                                    |

| 12             | STATIC CHARACTERISTICS                                                         |                  |                                                                    |

| 13             | SWITCHING CHARACTERISTICS                                                      |                  |                                                                    |

| 14             | DYNAMIC AC CHARACTERISTICS (STEREO AND DUAL SE APPLICATION)                    |                  |                                                                    |

| 15             | DYNAMIC AC CHARACTERISTICS (MONO<br>BTL APPLICATION)                           |                  |                                                                    |

| 16             | APPLICATION INFORMATION                                                        |                  |                                                                    |

| 16.1           | BTL application                                                                |                  |                                                                    |

| 16.2<br>16.3   | Pin MODE Output power estimation                                               |                  |                                                                    |

| 16.4           | External clock                                                                 |                  |                                                                    |

| 16.5           | Heatsink requirements                                                          |                  |                                                                    |

| 16.6           | Output current limiting                                                        |                  |                                                                    |

| 16.7           | Pumping effects                                                                |                  |                                                                    |

| 16.8           | Reference design                                                               |                  |                                                                    |

| 16.9           | PCB information for HSOP24 package                                             |                  |                                                                    |

| 16.10          | Classification  Pill of materials for reference design                         |                  |                                                                    |

| 16.11<br>16.12 | Bill of materials for reference design Curves measured in reference design     |                  |                                                                    |

| 16.12          | Application schematics                                                         |                  |                                                                    |

## 2 × 25 W class-D power amplifier

TDA8922

#### 1 FEATURES

- High efficiency (~90%)

- Operating supply voltage from ±12.5 to ±30 V

- · Very low quiescent current

- Low distortion

- Usable as a stereo Single-Ended (SE) amplifier or as a mono amplifier in Bridge-Tied Load (BTL)

- Fixed gain of 30 dB in Single-Ended (SE) and 36 dB in Bridge-Tied Load (BTL)

- · High output power

- · Good ripple rejection

- Internal switching frequency can be overruled by an external clock

- · No switch-on or switch-off plop noise

- · Short-circuit proof across load and to supply lines

- · Electrostatic discharge protection

- Thermally protected.

#### 2 APPLICATIONS

- · Television sets

- · Home-sound sets

- · Multimedia systems

- · All mains fed audio systems

- Car audio (boosters).

#### 3 GENERAL DESCRIPTION

The TDA8922 is a high efficiency class-D audio power amplifier with very low dissipation. The typical output power is  $2 \times 25$  W.

The device is available in the HSOP24 power package with a small internal heatsink and in the DBS23P through-hole power package. Depending on the supply voltage and load conditions, a very small or even no external heatsink is required. The amplifier operates over a wide supply voltage range from  $\pm 12.5$  to  $\pm 30$  V and consumes a very low quiescent current.

#### 4 QUICK REFERENCE DATA

| SYMBOL                            | PARAMETER                           | RAMETER CONDITIONS                                      |       | TYP. | MAX. | UNIT |  |  |

|-----------------------------------|-------------------------------------|---------------------------------------------------------|-------|------|------|------|--|--|

| General; $V_P = \pm 20 \text{ V}$ |                                     |                                                         |       |      |      |      |  |  |

| V <sub>P</sub>                    | supply voltage                      |                                                         | ±12.5 | ±20  | ±30  | ٧    |  |  |

| I <sub>q(tot)</sub>               | total quiescent supply current      | no load connected                                       | _     | 55   | 75   | mA   |  |  |

| η                                 | efficiency                          | $P_0$ = 25 W; SE: $R_L$ = 2 × 8 Ω; $f_i$ = 1 kHz        | _     | 90   | _    | %    |  |  |

| Stereo single-                    | ended configuration                 |                                                         |       |      |      |      |  |  |

| Po                                | output power                        | $R_L = 8 \Omega$ ; THD = 10%; $V_P = \pm 20 V$ ; note 1 | 22    | 25   | _    | W    |  |  |

|                                   |                                     | $R_L = 4 \Omega$ ; THD = 10%; $V_P = \pm 15 V$ ; note 1 | 22    | 25   | _    | W    |  |  |

| Mono bridge-ti                    | Mono bridge-tied load configuration |                                                         |       |      |      |      |  |  |

| Po                                | output power                        | $R_L = 8 \Omega$ ; THD = 10%; $V_P = \pm 15 V$ ; note 1 | 46    | 50   | _    | W    |  |  |

#### Note

1. See Section 16.5.

#### 5 ORDERING INFORMATION

| TYPE PACKAGE |        |                                                                            |          |

|--------------|--------|----------------------------------------------------------------------------|----------|

| NUMBER       | NAME   | DESCRIPTION                                                                | VERSION  |

| TDA8922TH    | HSOP24 | plastic, heatsink small outline package; 24 leads; low stand-off height    | SOT566-3 |

| TDA8922J     | DBS23P | plastic DIL-bent-SIL power package; 23 leads (straight lead length 3.2 mm) | SOT411-1 |

## $2 \times 25$ W class-D power amplifier

TDA8922

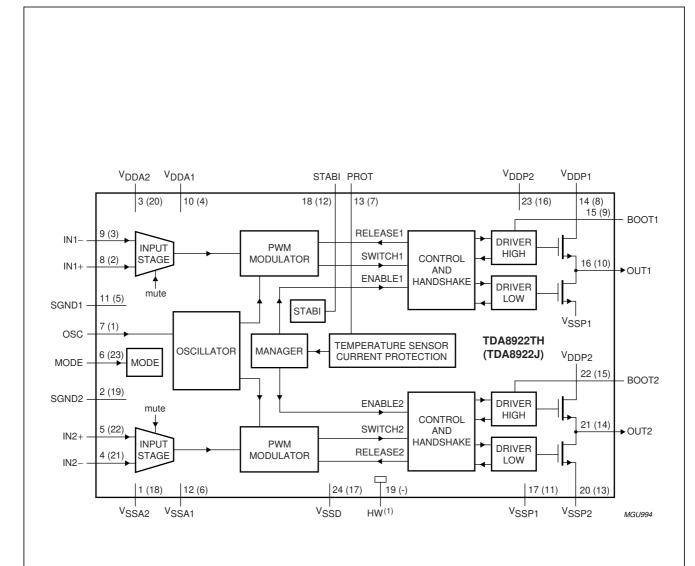

#### 6 BLOCK DIAGRAM

(1) Pin HW (TDA8922TH only) should be connected to pin  $V_{SSD}$  in the application. Pin numbers in parenthesis refer to the TDA8922J.

Fig.1 Block diagram.

## $2\times25\ W$ class-D power amplifier

TDA8922

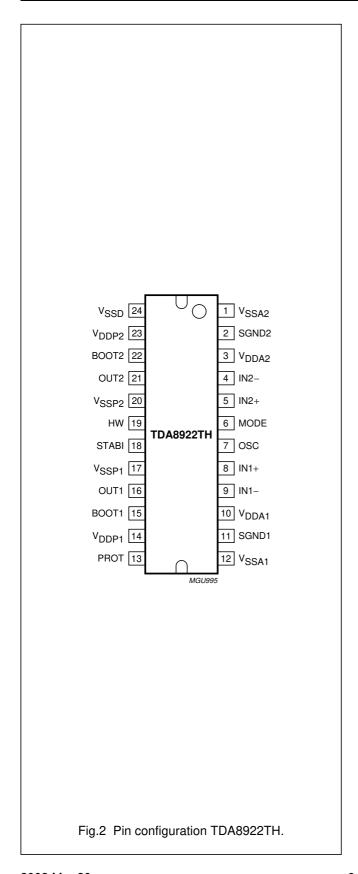

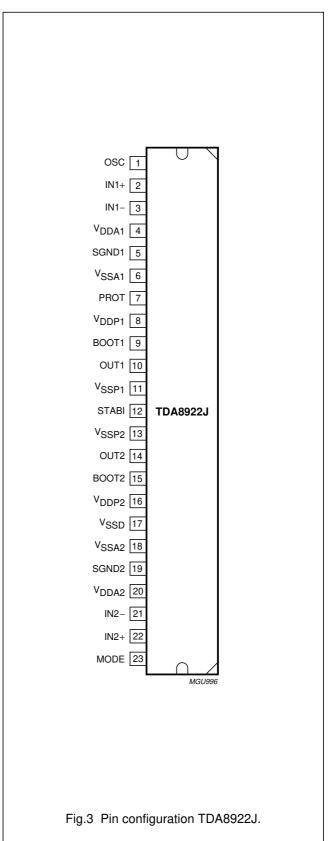

#### 7 PINNING

| CVMDOL            | PIN       |          | DECODIDATION                                            |

|-------------------|-----------|----------|---------------------------------------------------------|

| SYMBOL            | TDA8922TH | TDA8922J | DESCRIPTION                                             |

| V <sub>SSA2</sub> | 1         | 18       | negative analog supply voltage for channel 2            |

| SGND2             | 2         | 19       | signal ground for channel 2                             |

| V <sub>DDA2</sub> | 3         | 20       | positive analog supply voltage for channel 2            |

| IN2-              | 4         | 21       | negative audio input for channel 2                      |

| IN2+              | 5         | 22       | positive audio input for channel 2                      |

| MODE              | 6         | 23       | mode selection input: standby, mute or operating        |

| OSC               | 7         | 1        | oscillator frequency adjustment or tracking input       |

| IN1+              | 8         | 2        | positive audio input for channel 1                      |

| IN1-              | 9         | 3        | negative audio input for channel 1                      |

| V <sub>DDA1</sub> | 10        | 4        | positive analog supply voltage for channel 1            |

| SGND1             | 11        | 5        | signal ground for channel 1                             |

| V <sub>SSA1</sub> | 12        | 6        | negative analog supply voltage for channel 1            |

| PROT              | 13        | 7        | time constant capacitor for protection delay            |

| V <sub>DDP1</sub> | 14        | 8        | positive power supply voltage for channel 1             |

| BOOT1             | 15        | 9        | bootstrap capacitor for channel 1                       |

| OUT1              | 16        | 10       | PWM output from channel 1                               |

| V <sub>SSP1</sub> | 17        | 11       | negative power supply voltage for channel 1             |

| STABI             | 18        | 12       | decoupling of internal stabilizer for logic supply      |

| HW                | 19        | _        | handle wafer; must be connected to pin V <sub>SSD</sub> |

| V <sub>SSP2</sub> | 20        | 13       | negative power supply voltage for channel 2             |

| OUT2              | 21        | 14       | PWM output from channel 2                               |

| BOOT2             | 22        | 15       | bootstrap capacitor for channel 2                       |

| V <sub>DDP2</sub> | 23        | 16       | positive power supply voltage for channel 2             |

| V <sub>SSD</sub>  | 24        | 17       | negative digital supply voltage                         |

## $2 \times 25 \text{ W class-D power amplifier}$

TDA8922

## 2 × 25 W class-D power amplifier

#### TDA8922

#### 8 FUNCTIONAL DESCRIPTION

#### 8.1 General

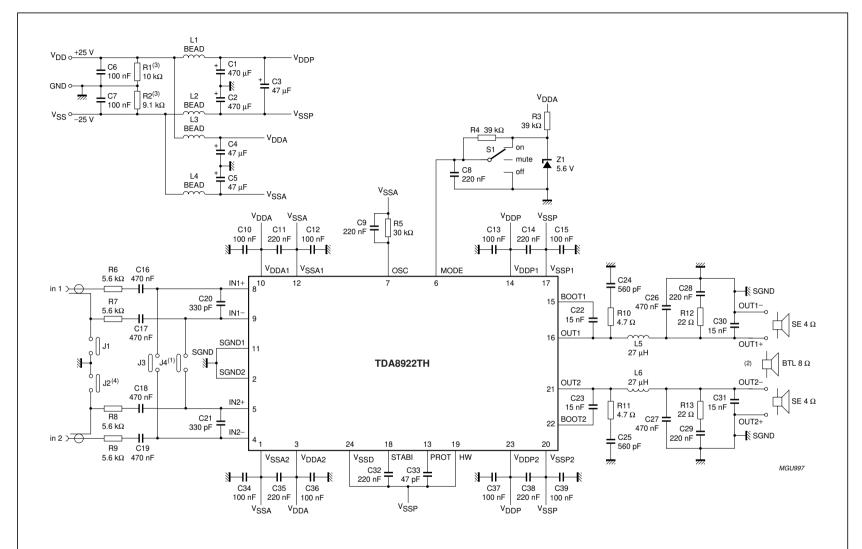

The TDA8922 is a two channel audio power amplifier using class-D technology. A detailed application reference design is shown in Fig.10. Typical application schematics are shown in Figs 37 and 38.

The audio input signal is converted into a digital Pulse Width Modulated (PWM) signal via an analog input stage and PWM modulator. To enable the output power transistors to be driven, this digital PWM signal is applied to a control and handshake block and driver circuits for both the high side and low side. In this way a level shift is performed from the low power digital PWM signal (at logic levels) to a high power PWM signal which switches between the main supply lines.

A 2nd-order low-pass filter converts the PWM signal to an analog audio signal across the loudspeakers.

The TDA8922 one-chip class-D amplifier contains high power D-MOS switches, drivers, timing and handshaking between the power switches and some control logic. For protection a temperature sensor and a maximum current detector are built-in.

The two audio channels of the TDA8922 contain two PWMs, two analog feedback loops and two differential input stages. It also contains circuits common to both channels such as the oscillator, all reference sources, the mode functionality and a digital timing manager.

The TDA8922 contains two independent amplifier channels with high output power, high efficiency (90%), low distortion and a low quiescent current. The amplifier channels can be connected in the following configurations:

- Mono Bridge-Tied Load (BTL) amplifier

- Stereo Single-Ended (SE) amplifiers.

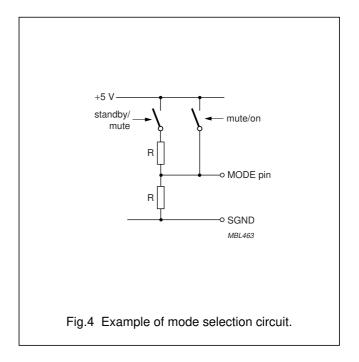

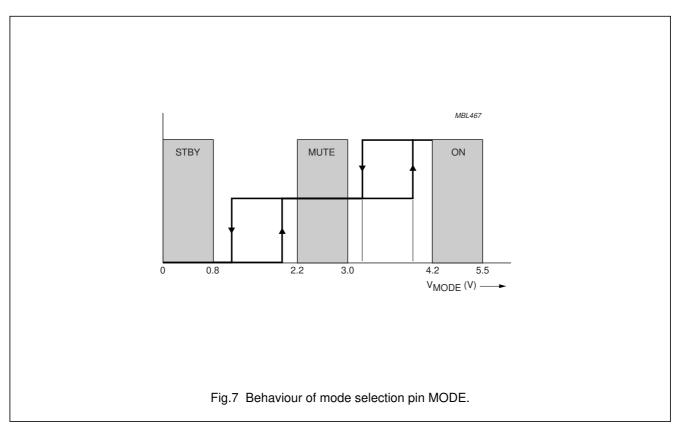

The amplifier system can be switched in three operating modes with pin MODE:

- Standby mode; with a very low supply current

- Mute mode; the amplifiers are operational, but the audio signal at the output is suppressed

- Operating mode; the amplifiers fully are operational with output signal.

An example of a switching circuit for driving pin MODE is illustrated in Fig.4.

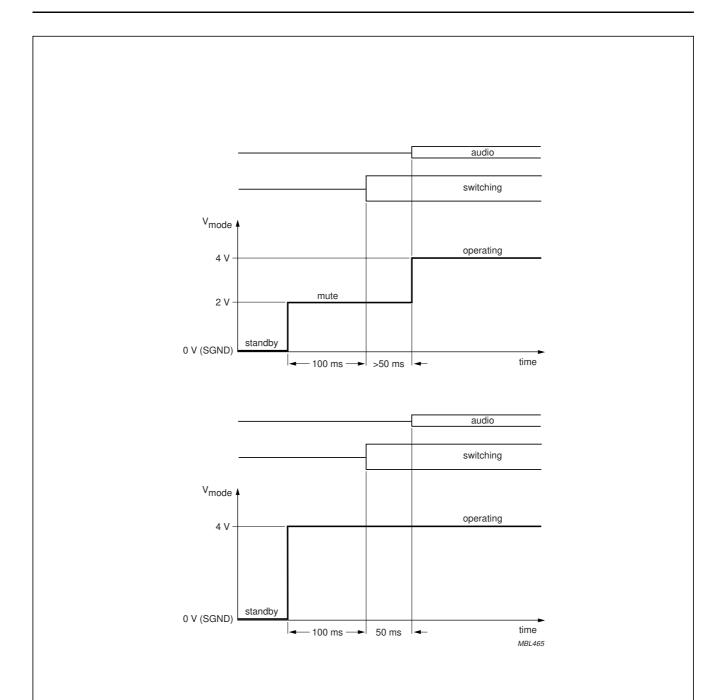

For suppressing plop noise, the amplifier will remain automatically in the mute mode for approximately 150 ms before switching to the operating mode (see Fig.5). During this time, the coupling capacitors at the input are fully charged.

## $2 \times 25$ W class-D power amplifier

TDA8922

When switching from standby to mute, there is a delay of 100 ms before the output starts switching. The audio signal is available after  $V_{\text{mode}}$  has been set to operating, but not earlier than 150 ms after switching to mute.

When switching from standby to operating, there is a first delay of 100 ms before the outputs starts switching. The audio signal is available after a second delay of 50 ms.

Fig.5 Timing on mode selection input.

## 2 × 25 W class-D power amplifier

TDA8922

#### 8.2 Pulse width modulation frequency

The output signal of the amplifier is a PWM signal with a carrier frequency of approximately 350 kHz. Using a 2nd-order LC demodulation filter in the application results in an analog audio signal across the loudspeaker. This switching frequency is fixed by an external resistor  $R_{\rm OSC}$  connected between pin OSC and  $V_{\rm SSA}.$  With the resistor value given in the schematic diagram of the reference design, the carrier frequency is typical 350 kHz. The carrier frequency can be calculated using the

following equation:

$$f_{osc} = \frac{9 \times 10^9}{R_{OSC}}$$

Hz

If two or more class-D amplifiers are used in the same audio application, it is advisable to have all devices operating at the same switching frequency.

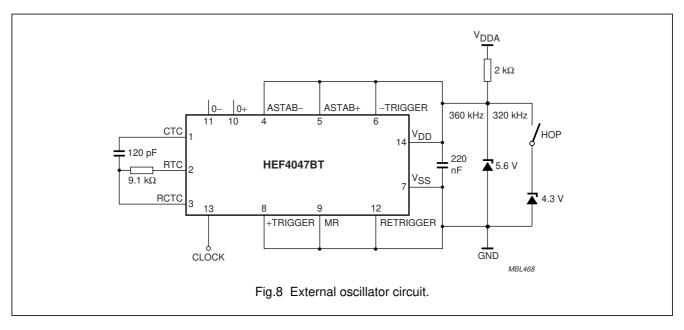

This can be realized by connecting all OSC pins together and feed them from a external central oscillator. Using an external oscillator it is necessary to force pin OSC to a DC-level above SGND for switching from the internal to an external oscillator. In this case the internal oscillator is disabled and the PWM will be switched on the external frequency. The frequency range of the external oscillator must be in the range as specified in the switching characteristics; see Chapter 13.

In an application circuit:

- Internal oscillator: R<sub>OSC</sub> connected between pin OSC and V<sub>SSA</sub>

- External oscillator: connect the oscillator signal between pins OSC and SGND; delete R<sub>OSC</sub> and C<sub>OSC</sub>.

#### 8.3 Protections

Temperature, supply voltage and short-circuit protections sensors are included on the chip. In the event that the maximum current or maximum temperature is exceeded the system will shut down.

#### 8.3.1 OVERTEMPERATURE

If the junction temperature  $T_j > 150~^{\circ}\text{C}$ , then the power stage will shut down immediately. The power stage will start switching again if the temperature drops to approximately 130  $^{\circ}\text{C}$ , thus there is a hysteresis of approximately 20  $^{\circ}\text{C}$ .

## 8.3.2 SHORT-CIRCUIT ACROSS LOUDSPEAKER TERMINALS AND TO SUPPLY LINES

When the loudspeaker terminals are short-circuited or if one of the demodulated outputs of the amplifier is short-circuited to one of the supply lines, this will be detected by the current protection. If the output current exceeds the maximum output current of 4 A, then the power stage will shut down within less than 1  $\mu s$  and the high current will be switched off. In this state the dissipation is very low. Every 100 ms the system tries to restart again. If there is still a short-circuit across the loudspeaker load or to one of the supply lines, the system is switched off again as soon as the maximum current is exceeded. The average dissipation will be low because of this low duty cycle.

#### 8.3.3 START-UP SAFETY TEST

During the start-up sequence, when pin MODE is switched from standby to mute, the conditions at the output terminals of the power stage are checked. In the event of a short-circuit at one of the output terminals to  $V_{\text{DD}}$  or  $V_{\text{SS}}$  the start-up procedure is interrupted and the systems waits for open-circuit outputs. Because the test is done before enabling the power stages, no large currents will flow in the event of a short-circuit. This system protects for short-circuits at both sides of the output filter to both supply lines. When there is a short-circuit from the power PWM output of the power stage to one of the supply lines (before the demodulation filter) it will also be detected by the start-up safety test. Practical use of this test feature can be found in detection of short-circuits on the printed-circuit board.

**Remark:** This test is only operational prior to or during the start-up sequence, and not during normal operation.

During normal operation the maximum current protection is used to detect short-circuits across the load and with respect to the supply lines.

## 2 × 25 W class-D power amplifier

TDA8922

#### 8.3.4 SUPPLY VOLTAGE ALARM

If the supply voltage drops below  $\pm 12.5$  V, the undervoltage protection circuit is activated and the system will shut down correctly. If the internal clock is used, this switch-off will be silent and without plop noise. When the supply voltage rises above the threshold level, the system is restarted again after 100 ms. If the supply voltage exceeds  $\pm 32$  V the overvoltage protection circuit is activated and the power stages will shut down. They are re-enabled as soon as the supply voltage drops below the threshold level.

An additional balance protection circuit compares the positive ( $V_{DD}$ ) and the negative ( $V_{SS}$ ) supply voltages and is triggered if the voltage difference between them exceeds a certain level. This level depends on the sum of both supply voltages. An expression for the unbalanced threshold level is as follows:  $V_{th(unb)} \approx 0.15 \times (V_{DD} + V_{SS})$ .

Example: With a symmetrical supply of  $\pm 30$  V, the protection circuit will be triggered if the unbalance exceeds approximately 9 V; see Section 16.7.

#### 8.4 Differential audio inputs

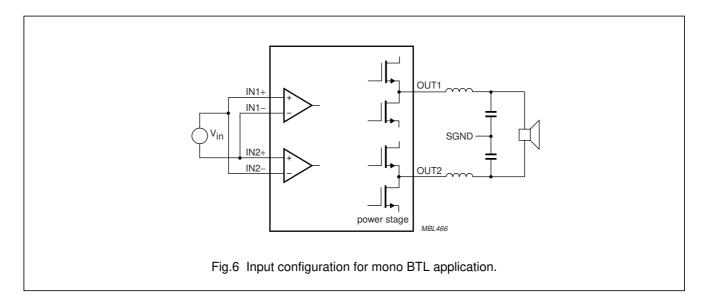

For a high common mode rejection ratio and a maximum of flexibility in the application, the audio inputs are fully differential. By connecting the inputs anti-parallel the phase of one of the channels can be inverted, so that a load can be connected between the two output filters. In this case the system operates as a mono BTL amplifier and with the same loudspeaker impedance an approximately four times higher output power can be obtained.

The input configuration for a mono BTL application is illustrated in Fig.6; for more information see Chapter 16.

In the stereo single-ended configuration it is also recommended to connect the two differential inputs in anti-phase. This has advantages for the current handling of the power supply at low signal frequencies.

2003 Mar 20

## $2 \times 25 \text{ W}$ class-D power amplifier

TDA8922

#### 9 LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC 60134).

| SYMBOL            | PARAMETER                             | CONDITIONS           | MIN. | MAX. | UNIT |

|-------------------|---------------------------------------|----------------------|------|------|------|

| V <sub>P</sub>    | supply voltage                        |                      | _    | ±30  | V    |

| V <sub>MODE</sub> | input voltage on pin MODE             | with respect to SGND | _    | 5.5  | V    |

| V <sub>sc</sub>   | short-circuit voltage on output pins  |                      | _    | ±30  | V    |

| I <sub>ORM</sub>  | repetitive peak current in output pin | note 1               | _    | 4    | Α    |

| T <sub>stg</sub>  | storage temperature                   |                      | -55  | +150 | °C   |

| T <sub>amb</sub>  | ambient temperature                   |                      | -40  | +85  | °C   |

| $T_{vj}$          | virtual junction temperature          |                      | _    | 150  | °C   |

#### **Notes**

1. See Section 16.6.

#### 10 THERMAL CHARACTERISTICS

| SYMBOL               | PARAMETER                                   | CONDITIONS          | VALUE | UNIT |

|----------------------|---------------------------------------------|---------------------|-------|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air; note 1 |       |      |

|                      | TDA8922TH                                   |                     | 35    | K/W  |

|                      | TDA8922J                                    |                     | 35    | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    | note 1              |       |      |

|                      | TDA8922TH                                   |                     | 1.3   | K/W  |

|                      | TDA8922J                                    |                     | 1.3   | K/W  |

#### Note

1. See Section 16.5.

#### 11 QUALITY SPECIFICATION

In accordance with "General Quality Specification for Integrated Circuits: SNW-FQ-611D" if this device is used as an audio amplifier.

## $2 \times 25 \text{ W}$ class-D power amplifier

TDA8922

#### 12 STATIC CHARACTERISTICS

$V_P = \pm 25$  V;  $T_{amb} = 25$  °C; measured in Fig.10; unless otherwise specified.

| SYMBOL                    | PARAMETER CONDITIONS                 |                                       | MIN.  | TYP.     | MAX. | UNIT |  |  |  |

|---------------------------|--------------------------------------|---------------------------------------|-------|----------|------|------|--|--|--|

| Supply                    | Supply                               |                                       |       |          |      |      |  |  |  |

| V <sub>P</sub>            | supply voltage                       | note 1                                | ±12.5 | ±20      | ±30  | V    |  |  |  |

| I <sub>q(tot)</sub>       | total quiescent supply current       | no load connected                     | _     | 55       | 75   | mA   |  |  |  |

| I <sub>stb</sub>          | standby supply current               |                                       | _     | 100      | 500  | μΑ   |  |  |  |

| Mode select in            | nput; pin MODE                       |                                       |       |          | •    |      |  |  |  |

| V <sub>MODE</sub>         | input voltage                        | note 2                                | 0     | <u> </u> | 5.5  | V    |  |  |  |

| I <sub>MODE</sub>         | input current                        | V <sub>MODE</sub> = 5.5 V             | _     | -        | 1000 | μΑ   |  |  |  |

| V <sub>stb</sub>          | input voltage for standby mode       | notes 2 and 3                         | 0     | Ī-       | 0.8  | V    |  |  |  |

| V <sub>mute</sub>         | input voltage for mute mode          | notes 2 and 3                         | 2.2   | _        | 3.0  | V    |  |  |  |

| V <sub>on</sub>           | input voltage for operating mode     | notes 2 and 3                         | 4.2   | _        | 5.5  | V    |  |  |  |

| Audio inputs;             | pins IN1-, IN1+, IN2+ and IN2-       |                                       |       |          |      |      |  |  |  |

| VI                        | DC input voltage                     | note 2                                | _     | 0        | _    | V    |  |  |  |

| Amplifier outp            | outs; pins OUT1 and OUT2             |                                       |       |          |      |      |  |  |  |

| V <sub>OO(SE)</sub>       | output offset voltage                | SE; operating and mute                | _     | _        | 150  | mV   |  |  |  |

| ΔV <sub>OO(SE)</sub>      | variation of output offset voltage   | SE; operating $\leftrightarrow$ mute  | _     | -        | 80   | mV   |  |  |  |

| V <sub>OO(BTL)</sub>      | output offset voltage                | BTL; operating and mute               | _     | -        | 215  | mV   |  |  |  |

| $ _{\Delta V_{OO(BTL)}} $ | variation of output offset voltage   | BTL; operating $\leftrightarrow$ mute | _     | _        | 115  | mV   |  |  |  |

| Stabilizer outp           | out; pin STABI                       |                                       |       | •        | •    |      |  |  |  |

| V <sub>o(stab)</sub>      | stabilizer output voltage            | mute and operating; note 4            | 11    | 13       | 15   | V    |  |  |  |

| Temperature p             | protection                           |                                       |       |          |      |      |  |  |  |

| T <sub>prot</sub>         | temperature protection activation    |                                       | 150   | -        | -    | °C   |  |  |  |

| T <sub>hys</sub>          | hysteresis on temperature protection |                                       | _     | 20       | _    | °C   |  |  |  |

#### **Notes**

- 1. The circuit is DC adjusted at  $V_P = \pm 12.5$  to  $\pm 30$  V.

- 2. With respect to SGND (0 V).

- 3. The transition regions between standby, mute and operating mode contain hysteresis (see Fig.7).

- 4. With respect to V<sub>SSP1</sub>.

## $2\times25\ W$ class-D power amplifier

TDA8922

#### 13 SWITCHING CHARACTERISTICS

$V_{DD}$  =  $\pm 25$  V;  $T_{amb}$  = 25 °C; measured in Fig.10; unless otherwise specified.

| SYMBOL                   | PARAMETER                                                              | CONDITIONS                       | MIN.       | TYP.       | MAX.     | UNIT |

|--------------------------|------------------------------------------------------------------------|----------------------------------|------------|------------|----------|------|

| Internal osc             | cillator                                                               |                                  | •          | •          | •        |      |

| f <sub>osc</sub>         | typical internal oscillator frequency                                  | $R_{OSC} = 30.0 \text{ k}\Omega$ | 290        | 317        | 344      | kHz  |

| f <sub>osc(int)</sub>    | internal oscillator frequency range                                    | note 1                           | 210        | _          | 600      | kHz  |

| External os              | cillator or frequency tracki                                           | ng                               | ·          |            | •        | •    |

| Vosc                     | voltage on pin OSC                                                     |                                  | SGND + 4.5 | SGND + 5   | SGND + 6 | V    |

| V <sub>OSC(trip)</sub>   | trip level for tracking on pin OSC                                     |                                  | -          | SGND + 2.5 | -        | V    |

| f <sub>track</sub>       | frequency range for tracking                                           |                                  | 210        | _          | 600      | kHz  |

| V <sub>P(OSC)(ext)</sub> | minimum symmetrical supply voltage for external oscillator application |                                  | 15         | -          | _        | V    |

#### Note

1. Frequency set with  $R_{\mbox{\scriptsize OSC}}$  according to the formula in Section 8.2.

## 2 × 25 W class-D power amplifier

TDA8922

#### 14 DYNAMIC AC CHARACTERISTICS (STEREO AND DUAL SE APPLICATION)

$V_P = \pm 20$  V;  $R_L = 8$   $\Omega$ ;  $f_i = 1$  kHz;  $f_{osc} = 310$  kHz;  $R_{sL} < 0.1$   $\Omega$  (note 1);  $T_{amb} = 25$  °C; measured in Fig.10; unless otherwise specified.

| SYMBOL               | PARAMETER                       | CONDITIONS                                                | MIN. | TYP. | MAX. | UNIT |

|----------------------|---------------------------------|-----------------------------------------------------------|------|------|------|------|

| Po                   | output power                    | $R_L = 8 \Omega; V_P = \pm 20 V; \text{ note 2}$          |      |      |      |      |

|                      |                                 | THD = 0.5%                                                | 18   | 20   | _    | W    |

|                      |                                 | THD = 10%                                                 | 22   | 25   | _    | W    |

|                      |                                 | $R_L = 8 \Omega; V_P = \pm 25 V; \text{ note } 2$         |      |      |      |      |

|                      |                                 | THD = 0.5%                                                | 29   | 33   | _    | W    |

|                      |                                 | THD = 10%                                                 | 36   | 40   | _    | W    |

|                      |                                 | $R_L = 4 \Omega$ ; $V_P = \pm 15 V$ ; note 2              |      |      |      |      |

|                      |                                 | THD = 0.5%                                                | 18   | 20   | _    | W    |

|                      |                                 | THD = 10%                                                 | 22   | 25   | _    | W    |

| THD                  | total harmonic distortion       | P <sub>o</sub> = 1 W; note 3                              |      |      |      |      |

|                      |                                 | f <sub>i</sub> = 1 kHz                                    | _    | 0.02 | 0.05 | %    |

|                      |                                 | $f_i = 10 \text{ kHz}$                                    | _    | 0.15 | _    | %    |

| G <sub>v(cl)</sub>   | closed loop voltage gain        |                                                           | 29   | 30   | 31   | dB   |

| η                    | efficiency                      | $P_0 = 25 \text{ W}; f_i = 1 \text{ kHz}; \text{ note 4}$ | 85   | 90   | _    | %    |

| SVRR                 | supply voltage ripple rejection | operating; note 5                                         |      |      |      |      |

|                      |                                 | f <sub>i</sub> = 100 Hz                                   | _    | 55   | _    | dB   |

|                      |                                 | f <sub>i</sub> = 1 kHz                                    | 40   | 50   | _    | dB   |

|                      |                                 | mute; f <sub>i</sub> = 100 Hz; note 5                     | _    | 55   | _    | dB   |

|                      |                                 | standby; f <sub>i</sub> = 100 Hz; note 5                  | _    | 80   | _    | dB   |

| Z <sub>i</sub>       | input impedance                 |                                                           | 45   | 68   | _    | kΩ   |

| V <sub>n(o)</sub>    | noise output voltage            | operating                                                 |      |      |      |      |

|                      |                                 | $R_s = 0 \Omega$ ; note 6                                 | _    | 200  | 400  | μV   |

|                      |                                 | $R_s = 10 \text{ k}\Omega; \text{ note } 7$               | _    | 230  | _    | μV   |

|                      |                                 | mute; note 8                                              | _    | 220  | _    | μV   |

| $\alpha_{cs}$        | channel separation              | note 9                                                    | _    | 70   | _    | dB   |

| $ \Delta G_v $       | channel unbalance               |                                                           |      | _    | 1    | dB   |

| V <sub>o(mute)</sub> | output signal in mute           | note 10                                                   | _    | _    | 400  | μV   |

| CMRR                 | common mode rejection ratio     | V <sub>i(CM)</sub> = 1 V (RMS)                            | _    | 75   | _    | dB   |

#### **Notes**

- 1.  $R_{sL}$  is the series resistance of inductor of low-pass LC filter in the application.

- 2. Output power is measured indirectly; based on R<sub>DSon</sub> measurement.

- Total harmonic distortion is measured in a bandwidth of 22 Hz to 22 kHz. When distortion is measured using a lower order low-pass filter a significantly higher value is found, due to the switching frequency outside the audio band. Maximum limit is guaranteed but may not be 100% tested.

- 4. Output power measured across the loudspeaker load.

- 5.  $V_{ripple} = V_{ripple(max)} = 2 V (p-p); R_s = 0 \Omega.$

- 6. B = 22 Hz to 22 kHz;  $R_s$  = 0  $\Omega$ ; maximum limit is guaranteed, but may not be 100% tested.

- 7. B = 22 Hz to 22 kHz;  $R_s$  = 10 k $\Omega$ .

## 2 × 25 W class-D power amplifier

TDA8922

- 8. B = 22 Hz to 22 kHz; independent of  $R_s$ .

- 9.  $P_0 = 1 \text{ W}$ ;  $R_s = 0 \Omega$ ;  $f_i = 1 \text{ kHz}$ .

- 10.  $V_i = V_{i(max)} = 1 \text{ V (RMS)}$ ; maximum limit is guaranteed, but may not be 100% tested.

#### 15 DYNAMIC AC CHARACTERISTICS (MONO BTL APPLICATION)

$V_P = \pm 15 \text{ V}$ ;  $R_L = 8 \Omega$ ;  $f_i = 1 \text{ kHz}$ ;  $f_{osc} = 310 \text{ kHz}$ ;  $R_{sL} < 0.1 \Omega$  (note 1);  $T_{amb} = 25 \,^{\circ}\text{C}$ ; measured in Fig.10; unless otherwise specified.

| SYMBOL               | PARAMETER                       | CONDITIONS                                                | MIN. | TYP.  | MAX. | UNIT |

|----------------------|---------------------------------|-----------------------------------------------------------|------|-------|------|------|

| Po                   | output power                    | $R_L = 8 \Omega; V_P = \pm 15 V; \text{ note } 2$         |      |       |      |      |

|                      |                                 | THD = 0.5%                                                | 37   | 40    | _    | W    |

|                      |                                 | THD = 10%                                                 | 46   | 50    | _    | W    |

| THD                  | total harmonic distortion       | P <sub>o</sub> = 1 W; note 3                              |      |       |      |      |

|                      |                                 | f <sub>i</sub> = 1 kHz                                    | _    | 0.015 | 0.05 | %    |

|                      |                                 | f <sub>i</sub> = 10 kHz                                   | _    | 0.02  | _    | %    |

| G <sub>v(cl)</sub>   | closed loop voltage gain        |                                                           | 35   | 36    | 37   | dB   |

| η                    | efficiency                      | $P_0 = 50 \text{ W}; f_i = 1 \text{ kHz}; \text{ note 4}$ | 85   | 90    | _    | %    |

| SVRR                 | supply voltage ripple rejection | operating; note 5                                         |      |       |      |      |

|                      |                                 | f <sub>i</sub> = 100 Hz                                   | _    | 49    | _    | dB   |

|                      |                                 | f <sub>i</sub> = 1 kHz                                    | 36   | 44    | _    | dB   |

|                      |                                 | mute; f <sub>i</sub> = 100 Hz; note 5                     | _    | 49    | _    | dB   |

|                      |                                 | standby; f <sub>i</sub> = 100 Hz; note 5                  | _    | 80    | _    | dB   |

| Z <sub>i</sub>       | input impedance                 |                                                           | 22   | 34    | _    | kΩ   |

| V <sub>n(o)</sub>    | noise output voltage            | operating                                                 |      |       |      |      |

|                      |                                 | $R_s = 0 \Omega$ ; note 6                                 | _    | 280   | 560  | μV   |

|                      |                                 | $R_s = 10 \text{ k}\Omega$ ; note 7                       | _    | 300   | _    | μV   |

|                      |                                 | mute; note 8                                              | _    | 280   | _    | μV   |

| V <sub>o(mute)</sub> | output signal in mute           | note 9                                                    | _    | _     | 500  | μV   |

| CMRR                 | common mode rejection ratio     | V <sub>i(CM)</sub> = 1 V (RMS)                            | _    | 75    | _    | dB   |

#### Notes

- 1. R<sub>sL</sub> is the series resistance of inductor of low-pass LC filter in the application.

- 2. Output power is measured indirectly; based on R<sub>DSon</sub> measurement.

- 3. Total harmonic distortion is measured in a bandwidth of 22 Hz to 22 kHz. When distortion is measured using a low order low-pass filter a significant higher value will be found, due to the switching frequency outside the audio band. Maximum limit is guaranteed but may not be 100% tested.

- 4. Output power measured across the loudspeaker load.

- 5.  $V_{ripple} = V_{ripple(max)} = 2 V (p-p); R_s = 0 \Omega.$

- 6. B = 22 Hz to 22 kHz;  $R_s$  = 0  $\Omega$ ; maximum limit is guaranteed, but may not be 100% tested.

- 7.  $B = 22 \text{ Hz to } 22 \text{ kHz}; R_s = 10 \text{ k}\Omega.$

- 8. B = 22 Hz to 22 kHz; independent of  $R_s$ .

- 9.  $V_i = V_{i(max)} = 1 \text{ V (RMS)}$ ;  $f_i = 1 \text{ kHz}$ ; maximum limit is guaranteed, but may not be 100% tested.

## 2 × 25 W class-D power amplifier

TDA8922

#### 16 APPLICATION INFORMATION

#### 16.1 BTL application

When using the power amplifier in a mono BTL application (for more output power), the inputs of both channels must be connected in parallel and the phase of one of the inputs must be inverted (see Fig.6). In principle the loudspeaker can be connected between the outputs of the two single-ended demodulation filters.

#### 16.2 Pin MODE

For correct operation the switching voltage at pin MODE should be debounced. If pin MODE is driven by a mechanical switch an appropriate debouncing low-pass filter should be used. If pin MODE is driven by an electronic circuit or microcontroller then it should remain at the mute voltage level for at least 100 ms before switching back to the standby voltage level.

#### 16.3 Output power estimation

The output power in several applications (SE and BTL) can be estimated using the following expressions:

$$\text{SE: P}_{\text{o(1\%)}} = \frac{\left[\frac{R_{L}}{R_{L} + 0.6} \times V_{P} \times (1 - t_{min} \times f_{osc})\right]^{2}}{2 \times R_{L}}$$

Maximum current:

$$I_{o(peak)} \, = \, \frac{V_P \times (1 - t_{min} \times f_{osc})}{R_L + 0.6} \, \text{ should not exceed 4 A}.$$

BTL:

$$P_{o(1\%)} = \frac{\left[\frac{R_L}{R_L + 1.2} \times 2V_P \times (1 - t_{min} \times f_{osc})\right]^2}{2 \times R_L}$$

Maximum current:

$$I_{o(peak)} = \frac{2V_p \times (1 - t_{min} \times f_{osc})}{R_1 + 1.2} \text{ should not exceed 4 A.}$$

Legend:

R<sub>L</sub> = load impedance

f<sub>osc</sub> = oscillator frequency

t<sub>min</sub> = minimum pulse width (typical 190 ns)

$V_P$  = single-sided supply voltage (so, if supply is  $\pm 30$  V symmetrical, then  $V_P$  = 30 V)

P<sub>o(1%)</sub> = output power just at clipping

$P_{o(10\%)}$  = output power at THD = 10%

$P_{o(10\%)} = 1.25 \times P_{o(1\%)}$ .

#### 16.4 External clock

The minimum required symmetrical supply voltage for external clock application is  $\pm 15$  V (equally, the minimum asymmetrical supply voltage for applications with an external clock is 30 V).

When using an external clock the following accuracy of the duty cycle of the external clock has to be taken into account:  $47.5\% < \delta < 52.5\%$ .

A possible solution for an external clock oscillator circuit is illustrated in Fig.8.

## 2 × 25 W class-D power amplifier

#### TDA8922

#### 16.5 Heatsink requirements

In some applications it may be necessary to connect an external heatsink to the TDA8922. The determining factor is the 150 °C maximum junction temperature  $T_{j(max)}$  which cannot be exceeded. The expression below shows the relationship between the maximum allowable power dissipation and the total thermal resistance from junction to ambient:

$$R_{th(j-a)} = \frac{T_{j(max)} - T_{amb}}{P_{diss}}$$

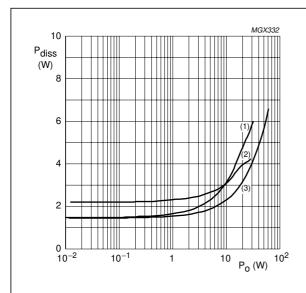

$P_{diss}$  is determined by the efficiency ( $\eta$ ) of the TDA8922. The efficiency measured in the TDA8922 as a function of output power is given in Fig.19. The power dissipation can be derived as function of output power (see Fig.18).

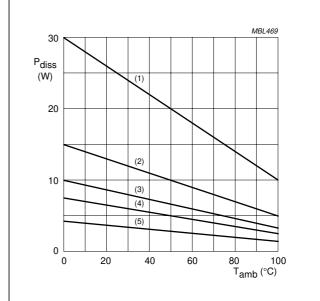

The derating curves (given for several values of the  $R_{th(j-a)}$ ) are illustrated in Fig.9. A maximum junction temperature  $T_j = 150~^{\circ}\text{C}$  is taken into account. From Fig.9 the maximum allowable power dissipation for a given heatsink size can be derived or the required heatsink size can be determined at a required dissipation level.

#### Example 1:

$P_0 = 2 \times 25 \text{ W into } 8 \Omega$

$T_{j(max)} = 150 \, ^{\circ}C$

$T_{amb} = 60 \, ^{\circ}C$

$P_{diss(tot)} = 4.2 \text{ W (from Fig.18)}$

The required  $R_{th(j-a)} = 21.4$  K/W can be calculated.

The  $R_{th(j-a)}$  of the TDA8922 in free air is 35 K/W; the  $R_{th(j-c)}$  of the TDA8922 is 1.3 K/W, thus a heatsink of 20.1 K/W is required for this example.

In actual applications, other factors such as the average power dissipation with music source (as opposed to a continuous sine wave) will determine the size of the heatsink required.

#### Example 2:

$P_0 = 2 \times 25 \text{ W into } 4 \Omega$

$T_{i(max)} = 150 \, ^{\circ}C$

$T_{amb} = 60 \, ^{\circ}C$

$P_{diss(tot)} = 5.5 \text{ W (from Fig.18)}$

The required  $R_{th(i-a)} = 16.4 \text{ K/W}.$

The  $R_{th(j-a)}$  of the TDA8922 in free air is 35 K/W; the  $R_{th(j-c)}$  of the TDA8922 is 1.3 K/W, thus a heatsink of 15.1 K/W is required for this example.

- (1)  $R_{th(j-a)} = 5 \text{ K/W}.$

- (2)  $R_{th(j-a)} = 10 \text{ K/W}.$

- (3)  $R_{th(j-a)} = 15 \text{ K/W}.$

- (4)  $R_{th(j-a)} = 20 \text{ K/W}.$

- (5)  $R_{th(j-a)} = 35 \text{ K/W}.$

Fig.9 Derating curves for power dissipation as a function of maximum ambient temperature.

#### 16.6 Output current limiting

To guarantee the robustness of the class-D amplifier the maximum output current which can be delivered by the output stage is limited. An overcurrent protection is included for each output power switch. When the current flowing through any of the power switches exceeds a defined internal threshold (e.g. in case of a short-circuit to the supply lines or a short-circuit across the load), the amplifier will shut down immediately and an internal timer will be started. After a fixed time (e.g. 100 ms) the amplifier is switched on again. If the requested output current is still too high the amplifier will switch-off again. Thus the amplifier will try to switch to the operating mode every 100 ms. The average dissipation will be low in this situation because of this low duty cycle. If the overcurrent condition is removed the amplifier will remain operating.

Because the duty cycle is low the amplifier will be switched off for a relatively long period of time which will be noticed as a so-called audio-hole; an audible interruption in the output signal.

## 2 × 25 W class-D power amplifier

TDA8922

To trigger the maximum current protection in the TDA8922, the required output current must exceed 4 A. This situation occurs in case of:

- Short-circuits from any output terminal to the supply lines (V<sub>DD</sub> or V<sub>SS</sub>)

- Short-circuit across the load or speaker impedances or a load impedance below the specified values of 4 and 8  $\Omega$ .

Even if load impedances are connected to the amplifier outputs which have an impedance rating of 4  $\Omega$ , this impedance can be lower due to the frequency characteristic of the loudspeaker; practical loudspeaker impedances can be modelled as an RLC network which will have a specific frequency characteristic: the impedance at the output of the amplifier will vary with the input frequency. A high supply voltage in combination with a low impedance will result in large current requirements.

Another factor which must be taken into account is the ripple current which will also flow through the output power switches. This ripple current depends on the inductor values which are used, supply voltage, oscillator frequency, duty factor and minimum pulse width. The maximum available output current to drive the load impedance can be calculated by subtracting the ripple current from the maximum repetitive peak current in the output pin, which is 4 A for the TDA8922.

As a rule of thumb the following expressions can be used to determine the minimum allowed load impedance without generating audio holes:

$$Z_{L} \ge \frac{V_{P} \times (1 - t_{min} \times f_{osc})}{I_{ORM} - I_{ripple}} - 0.6 \text{ for SE application.}$$

$$Z_L \ge \frac{2V_P \times (1 - t_{min} \times f_{osc})}{I_{OBM} - I_{ripple}} - 1.2$$

for BTL application.

Where:

Z<sub>L</sub> = load impedance

fosc = oscillator frequency

t<sub>min</sub> = minimum pulse width (typical 190 ns)

V<sub>P</sub> = single-sided supply voltage

(so, if the supply is  $\pm 30$  V symmetrical, then  $V_P = 30$  V)

$I_{ORM}$  = maximum repetitive peak current in output pin; see also Chapter 9

$I_{ripple}$  = ripple current.

See the application notes (tbf) for a more detailed description of the implications of output current limiting.

#### 16.7 Pumping effects

The TDA8922 class-D amplifier is supplied by a symmetrical voltage (e.g  $V_{DD} = +25\ V$  and  $V_{SS} = -25\ V$ ). When the amplifier is used in a SE configuration, a so-called 'pumping effect' can occur. During one switching interval, energy is taken from one supply (e.g.  $V_{DD}$ ), while a part of that energy is delivered back to the other supply line (e.g.  $V_{SS}$ ) and visa versa. When the voltage supply source cannot sink energy, the voltage across the output capacitors of that voltage supply source will increase: the supply voltage is pumped to higher levels. The voltage increase caused by the pumping effect depends on:

- Speaker impedance

- Supply voltage

- Audio signal frequency

- · Capacitor value present on supply lines

- · Source and sink currents of other channels.

The pumping effect should not cause a malfunction of either the audio amplifier and/or the voltage supply source. For instance, this malfunction can be caused by triggering of the undervoltage or overvoltage protection or unbalance protection of the amplifier.

See the application notes (tbf) for a more detailed description of the implications of output current limiting.

#### 16.8 Reference design

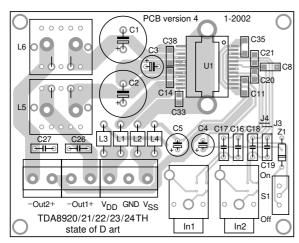

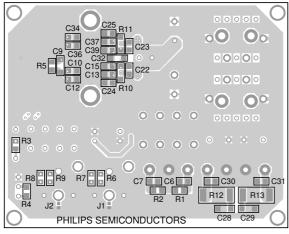

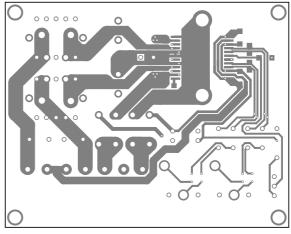

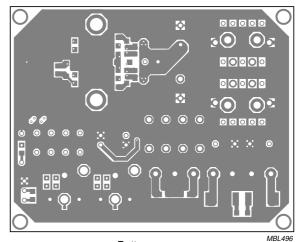

The reference design for a single-chip class-D audio amplifier using the TDA8922TH is illustrated in Fig.10. The Printed-Circuit Board (PCB) layout is shown in Fig.11. The Bill Of Materials (BOM) is given in Table 1.

#### 16.9 PCB information for HSOP24 package

The size of the PCB is 74.3  $\times$  59.10 mm, dual sided 35  $\mu m$  copper with 121 metallized through holes.

The standard configuration has a symmetrical supply (typical  $\pm 20$  V) with stereo SE outputs (typical  $2\times 8~\Omega$ ). The PCB is also suitable for a mono BTL configuration (1  $\times 8~\Omega$ ) with symmetrical and asymmetrical supply.

It is possible to use several different output filter inductors such as 16RHBP or EP13 types to evaluate the performance against the price or size.

#### 16.10 Classification

The application shows optimized signal and EMI performance.

TDA8922

Every decoupling to ground (plane) must be made as close as possible to the pin. To handle 20 Hz under all conditions in stereo SE mode, the external power supply needs to have a capacitance of at least 4700  $\mu$ F per supply line;  $V_P = \pm 27 \text{ V (max)}$ .

- (1) BTL: remove In2, R8, R9, C18, C19, C21 and close J3 and J4.

- (2) BTL: connect loudspeaker between OUT1+ and OUT2-.

- (3) BTL: R1 and R2 are only required when an asymmetrical supply is used  $(V_{SS} = 0 \text{ V})$ .

- (4) In case of hum, close J1 and J2.

Fig.10 Single-chip class-D audio amplifier application diagram (reference design for SE and BTL).

## $2\times25\ W$ class-D power amplifier

## TDA8922

Top silk screen

Bottom silk screen

Top copper

Bottom copper

Fig.11 Printed-circuit board layout for the TDA8922TH.

## $2\times25\ W$ class-D power amplifier

TDA8922

#### 16.11 Bill of materials for reference design

**Table 1** Single-chip class-D audio amplifier printed-circuit board (PCB version 4; 1-2002) for TDA8922TH (see Figs 10 and 11).

| BOM ITEM | QUANTITY | REFERENCE                                         | PART                                                                                                             | DESCRIPTION                        |  |

|----------|----------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------|--|

| 1        | 1        | U1                                                | TDA8922TH                                                                                                        | Philips Semiconductors B.V.        |  |

| 2        | 2        | in1 and in2                                       | cinch inputs                                                                                                     | Farnell 152-396                    |  |

| 3        | 2        | out1 and out2                                     | output connector                                                                                                 | Augat 5KEV-02                      |  |

| 4        | 1        | V <sub>DD</sub> , GND and V <sub>SS</sub>         | supply connector                                                                                                 | Augat 5KEV-03                      |  |

| 5        | 2        | L6 and L5                                         | 27 μΗ                                                                                                            | EP13 or 16RHBP                     |  |

| 6        | 4        | L1, L2, L3 and L4                                 | BEAD                                                                                                             | Murata BL01RN1-A62                 |  |

| 7        | 1        | S1                                                | PCB switch                                                                                                       | Knitter ATE1E M-O-M                |  |

| 8        | 1        | Z1                                                | 5V6                                                                                                              | BZX 79C5V6 DO-35                   |  |

| 9        | 2        | C1 and C2                                         | 470 μF; 35 V                                                                                                     | Panasonic M series<br>ECA1VM471    |  |

| 10       | 3        | C3, C4 and C5                                     | 47 μF; 63 V                                                                                                      | Panasonic NHG series<br>ECA1JHG470 |  |

| 11       | 6        | C16, C17, C18, C19, C26 and C27                   | 470 nF; 63 V                                                                                                     | MKT EPCOS B32529-C474-K            |  |

| 12       | 9        | C8, C9, C11, C14, C28, C29, C32, C35 and C38      | 220 nF; 63 V                                                                                                     | SMD 1206                           |  |

| 13       | 10       | C6, C7, C10, C12, C13, C15, C34, C36, C37 and C39 | 100 nF; 50 V                                                                                                     | SMD 0805                           |  |

| 14       | 2        | C20 and C21                                       | 330 pF; 50 V                                                                                                     | SMD 0805                           |  |

| 15       | 4        | C22, C23, C30 and C31                             | 15 nF; 50 V                                                                                                      | SMD 0805                           |  |

| 16       | 2        | C24, C25                                          | 560 pF; 100 V                                                                                                    | SMD 0805                           |  |

| 17       | 1        | C33                                               | 47 pF; 25V                                                                                                       | SMD 0805                           |  |

| 18       | 2        | R4 and R3                                         | 39 kΩ; 0.1 W                                                                                                     | SMD 0805                           |  |

| 19       | 1        | R5                                                | 30 kΩ; 0.1 W                                                                                                     | SMD 1206                           |  |

| 20       | 1        | R1                                                | 10 kΩ; 0.1 W; optional                                                                                           | SMD 0805                           |  |

| 21       | 1        | R2                                                | 9.1 kΩ; 0.1 W; optional                                                                                          | SMD 0805                           |  |

| 22       | 4        | R6, R7, R8 and R9                                 | 5.6 kΩ; 0.1 W                                                                                                    | SMD 0805                           |  |

| 23       | 2        | R13 and R12                                       | 22 Ω; 1 W                                                                                                        | SMD 2512                           |  |

| 24       | 2        | R10 and R11                                       | 4.7 Ω; 0.25 W                                                                                                    | SMD 1206                           |  |

| 25       | 2        | J1 and J2                                         | solder dot jumpers for gr<br>(60 Hz noise)                                                                       | round reference in case of hum     |  |

| 26       | 2        | J3 and J4                                         | wire jumpers for BTL ap                                                                                          | plication                          |  |

| 27       | 1        | heatsink                                          | 30 mm SK400; OK for maximum music dissipation;<br>1/8 Prated (2 × 75 W/8) in 2 × 4 $\Omega$ at $T_{amb}$ = 70 °C |                                    |  |

| 28       | 1        | printed-circuit board material                    | 1.6 mm thick epoxy FR4 material, double sided 35 μm copper; clearances 300 μm; minimum copper track 400 μm       |                                    |  |

## 2 × 25 W class-D power amplifier

#### TDA8922

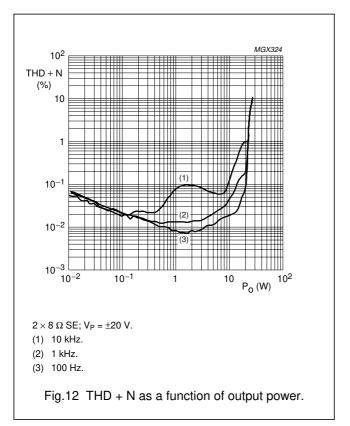

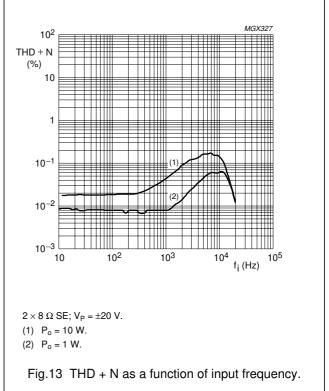

#### 16.12 Curves measured in reference design

The curves illustrated in Figs 20 and 21 are measured with a specified load impedance. Spread in  $Z_L$  (e.g. due to the frequency characteristics of the loudspeaker) can trigger the maximum current protection circuit; see Section 16.6.

The curves illustrated in Figs 30 and 31 show the effects of supply pumping when only one single-ended channel is driven with a low frequency signal; see Section 16.7.

## $2 \times 25$ W class-D power amplifier

## TDA8922

## $2\times25\ W$ class-D power amplifier

TDA8922

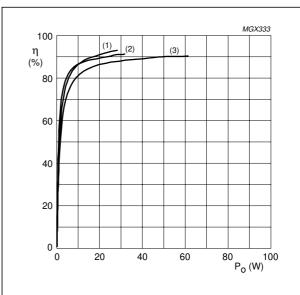

$f_i = 1 \text{ kHz}.$

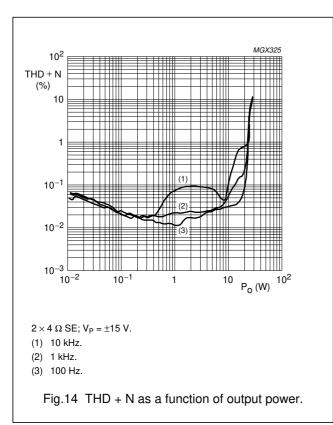

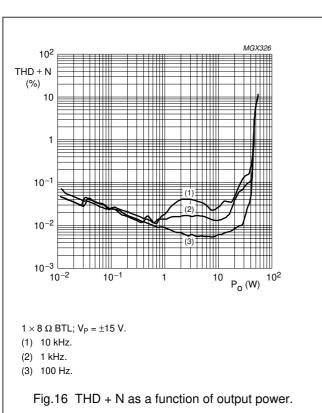

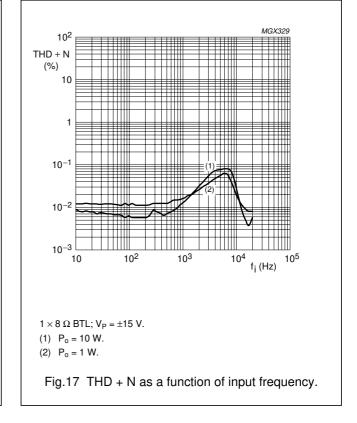

- (1)  $2 \times 4 \Omega$  SE,  $V_P = \pm 15 \text{ V}$ .

- (2)  $2 \times 8 \Omega \text{ SE}, V_P = \pm 20 \text{ V}.$

- (3)  $1 \times 8 \Omega$  BTL,  $V_P = \pm 15 \text{ V}$ .

Fig.18 Power dissipation as a function of output power.

$f_i = 1 \text{ kHz}.$

- (1)  $2 \times 8 \Omega$  SE,  $V_P = \pm 20 \text{ V}$ .

- (2)  $2 \times 4 \Omega$  SE,  $V_P = \pm 15 V$ .

- (3)  $1 \times 8 \Omega$  BTL,  $V_P = \pm 15 \text{ V}$ .

Fig.19 Efficiency as a function of output power.

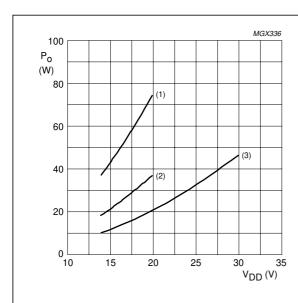

THD + N = 0.5%;  $f_i = 1 \text{ kHz}$ .

- (1)  $1 \times 8 \Omega$  BTL.

- (2)  $2 \times 4 \Omega$  SE.

- (3)  $2 \times 8 \Omega$  SE.

Fig.20 Output power as a function of supply voltage.

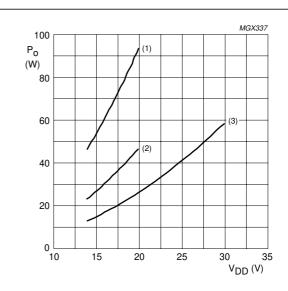

THD + N = 10%;  $f_i = 1 \text{ kHz}$ .

- (1)  $1 \times 8 \Omega$  BTL.

- (2)  $2 \times 4 \Omega$  SE.

- (3)  $2 \times 8 \Omega$  SE.

Fig.21 Output power as a function of supply voltage.

## $2 \times 25$ W class-D power amplifier

TDA8922

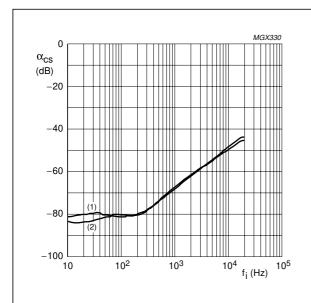

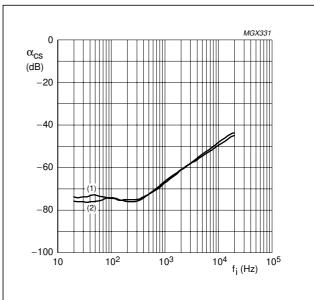

$2\times 8~\Omega$  SE; VP =  $\pm 20~V.$

- (1)  $P_0 = 1 W$ .

- (2)  $P_0 = 10 \text{ W}.$

Fig.22 Channel separation as a function of input frequency.

$2 \times 4 \Omega$  SE;  $V_P = \pm 15 V$ .

- (1)  $P_o = 1 W$ .

- (2)  $P_0 = 10 \text{ W}.$

Fig.23 Channel separation as a function of input frequency.

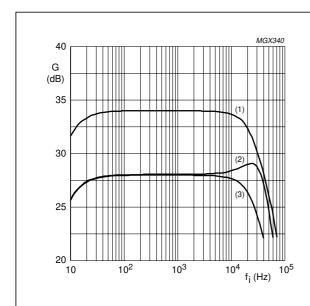

$V_i$  = 100 mV;  $R_s$  = 5.6 k $\Omega;$   $C_i$  = 330 pF.

- (1)  $1 \times 8~\Omega$  BTL,  $V_P = \pm 15~V$ .

- (2)  $2 \times 8 \Omega$  SE,  $V_P = \pm 20 \text{ V}$ .

- (3)  $2 \times 4 \Omega \text{ SE}, V_P = \pm 15 \text{ V}.$

Fig.24 Gain as a function of input frequency.

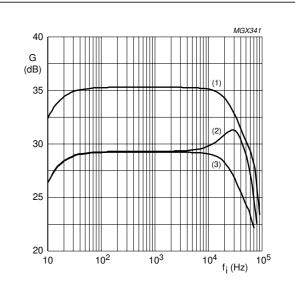

$V_i = 100 \text{ mV}; R_s = 0 \text{ k}\Omega.$

- (1)  $1 \times 8 \Omega$  BTL,  $V_P = \pm 15 V$ .

- (2)  $2 \times 8 \Omega$  SE,  $V_P = \pm 20 \text{ V}$ .

- (3)  $2 \times 4 \Omega$  SE,  $V_P = \pm 15 V$ .

Fig.25 Gain as a function of input frequency.