Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **TDF8599A**

I<sup>2</sup>C-bus controlled dual channel 135 W/4  $\Omega$ , single channel 250 W/2  $\Omega$  class-D power amplifier with load diagnostics

Rev. 3 — 2 May 2013

**Product data sheet**

## 1. General description

The TDF8599A is a dual Bridge-Tied Load (BTL) car audio amplifier comprising an NDMOST-NDMOST output stage based on SOI BCDMOS technology. Low power dissipation enables the TDF8599A high-efficiency, class-D amplifier to be used with a smaller heat sink than those normally used with standard class-AB amplifiers.

The TDF8599A can operate in either non- $I^2C$ -bus mode or  $I^2C$ -bus mode. When in  $I^2C$ -bus mode, DC load detection results and fault conditions can be easily read back from the device. Up to 15  $I^2C$ -bus addresses can be selected depending on the value of the external resistor connected to pins ADS and MOD.

When pin ADS is short circuited to ground, the TDF8599A operates in non-I<sup>2</sup>C-bus mode. Switching between Operating mode and Mute mode in non-I<sup>2</sup>C-bus mode is only possible using pins EN and SEL\_MUTE.

## 2. Features and benefits

- High-efficiency

- Low quiescent current

- Operating voltage from 8 V to 35 V

- Two 4  $\Omega/2$   $\Omega$  capable BTL channels or one 1  $\Omega$  capable BTL channel

- Differential inputs

- I<sup>2</sup>C-bus mode with 15 I<sup>2</sup>C-bus addresses or non-I<sup>2</sup>C-bus mode operation

- Clip detect

- Independent short circuit protection for each channel

- Advanced short circuit protection for load, GND and supply

- Load dump protection

- Thermal foldback and thermal protection

- DC offset protection

- Selectable AD or BD modulation

- Parallel channel mode for high current drive capability

- Advanced clocking:

- Switchable oscillator clock source: internal for Master mode or external for Slave mode

- Spread spectrum mode

- Phase staggering

- Frequency hopping

- No 'pop noise' caused by DC output offset voltage

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

- I<sup>2</sup>C-bus mode:

- ◆ DC load detection

- ◆ AC load detection

- Thermal pre-warning diagnostic level setting

- Identification of activated protections or warnings

- Selectable diagnostic information available using pins DIAG and CLIP

- Qualified in accordance with AEC-Q100

## 3. Applications

Car audio

## 4. Quick reference data

**Table 1.** Quick reference data  $V_P = 14.4 \text{ V}$  unless otherwise stated.

| Symbol         | Parameter               | Conditions                                             | Mir   | т Тур | Max | Unit |

|----------------|-------------------------|--------------------------------------------------------|-------|-------|-----|------|

| $V_P$          | supply voltage          |                                                        | [1] 8 | 14.4  | 35  | ٧    |

| I <sub>P</sub> | supply current          | off state; $T_j \le 85$ °C; $V_P = 14.4$ V             | -     | 2     | 10  | μΑ   |

| $I_{q(tot)}$   | total quiescent current | Operating mode; no load, snubbers and filter connected | -     | 90    | 120 | mA   |

| Po             | output power            | Stereo mode:                                           | [2]   |       |     |      |

|                |                         | $V_P$ = 14.4 V; THD = 1 %; $R_L$ = 4 $\Omega$          | 18    | 20    | -   | W    |

|                |                         | $V_P$ = 14.4 V; THD = 10 %; $R_L$ = 4 $\Omega$         | 23    | 25    | -   | W    |

|                |                         | square wave (EIAJ); $R_L = 4 \Omega$                   | -     | 40    | -   | W    |

|                |                         | $V_P$ = 35 V; THD = 10 %; $R_L$ = 4 $\Omega$           | -     | 135   | -   | W    |

|                |                         | $V_P$ = 14.4 V; THD = 1 %; $R_L$ = 2 $\Omega$          | 26    | 29    | -   | W    |

|                |                         | $V_P$ = 14.4 V; THD = 10 %; $R_L$ = 2 $\Omega$         | 34    | 38    | -   | W    |

|                |                         | square wave (EIAJ); $R_L = 2 \Omega$                   | -     | 60    | -   | W    |

|                |                         | Parallel mode:                                         | [2]   |       |     |      |

|                |                         | $V_P$ = 14.4 V; THD = 10 %; $R_L$ = 2 $\Omega$         | -     | 50    | -   | W    |

|                |                         | $V_P$ = 35 V; THD = 10 %; $R_L$ = 2 $\Omega$           | -     | 250   | -   | W    |

|                |                         | $V_P$ = 25 V; THD = 1 %; $R_L$ = 1 $\Omega$            | 135   | 150   | -   | W    |

<sup>[1]</sup> In this data sheet supply voltage  $V_P$  describes  $V_{P1},\,V_{P2}$  and  $V_{PA}.$

## 5. Ordering information

Table 2. Ordering information

| Type number | Package |                                                                         |          |  |  |

|-------------|---------|-------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                             | Version  |  |  |

| TDF8599ATH  | HSOP36  | plastic, heatsink small outline package; 36 leads; low stand-off height | SOT851-2 |  |  |

<sup>[2]</sup> Output power is measured indirectly based on R<sub>DSon</sub> measurement.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

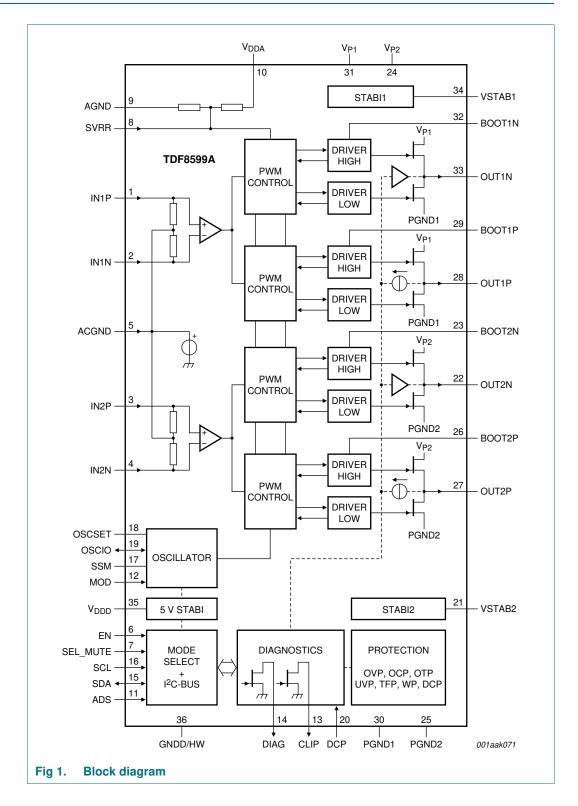

## 6. Block diagram

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

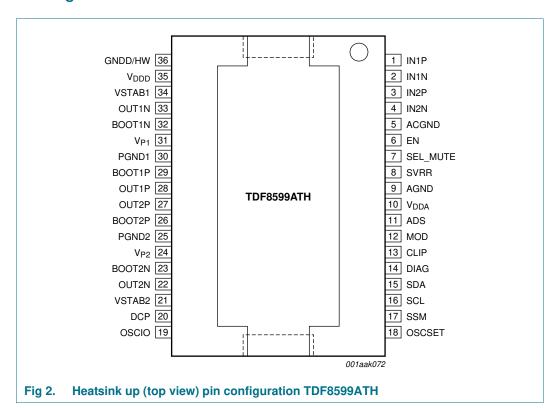

## 7. Pinning information

## 7.1 Pinning

## 7.2 Pin description

Table 3. Pin description

| Symbol    | Pin | Type[1] | Description                                                     |

|-----------|-----|---------|-----------------------------------------------------------------|

| IN1P      | 1   | I       | channel 1 positive audio input                                  |

| IN1N      | 2   | I       | channel 1 negative audio input                                  |

| IN2P      | 3   | I       | channel 2 positive audio input                                  |

| IN2N      | 4   | I       | channel 2 negative audio input                                  |

| ACGND     | 5   | I       | decoupling for input reference voltage                          |

| EN        | 6   | I       | enable input:                                                   |

|           |     |         | non-I <sup>2</sup> C-bus mode: switch between off and Mute mode |

|           |     |         | I <sup>2</sup> C-bus mode: off and Standby mode                 |

| SEL_MUTE  | 7   | I       | select mute or unmute                                           |

| SVRR      | 8   | I       | decoupling for internal half supply reference voltage           |

| AGND      | 9   | G       | analog supply ground                                            |

| $V_{DDA}$ | 10  | Р       | analog supply voltage                                           |

| ADS       | 11  | I       | non-I <sup>2</sup> C-bus mode: connected to ground              |

|           |     |         | I <sup>2</sup> C-bus mode: selection and address selection pin  |

| MOD       | 12  | I       | modulation mode, phase shift and parallel mode select           |

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Table 3.

Pin description ...continued

|                     |     | <u> </u> |                                                        |  |

|---------------------|-----|----------|--------------------------------------------------------|--|

| Symbol              | Pin | Type[1]  | Description                                            |  |

| CLIP                | 13  | 0        | clip output; open-drain                                |  |

| DIAG                | 14  | 0        | diagnostic output; open-drain                          |  |

| SDA                 | 15  | I/O      | I <sup>2</sup> C-bus data input and output             |  |

| SCL                 | 16  | I        | I <sup>2</sup> C-bus clock input                       |  |

| SSM                 | 17  |          | master setting: Spread spectrum mode frequency         |  |

|                     |     |          | slave setting: phase lock operation                    |  |

| OSCSET              | 18  |          | master/slave oscillator setting                        |  |

|                     |     |          | master only setting: set internal oscillator frequency |  |

| OSCIO               | 19  | I/O      | external oscillator slave setting: input               |  |

|                     |     |          | internal oscillator master setting: output             |  |

| DCP                 | 20  | I        | DC protection input for the filtered output voltages   |  |

| VSTAB2              | 21  |          | decoupling internal stabilizer 2 for DMOST drivers     |  |

| OUT2N               | 22  | 0        | channel 2 negative PWM output                          |  |

| BOOT2N              | 23  |          | boot 2 negative bootstrap capacitor                    |  |

| V <sub>P2</sub> [2] | 24  | Р        | channel 2 power supply voltage                         |  |

| PGND2               | 25  | G        | channel 2 power ground                                 |  |

| BOOT2P              | 26  |          | boot 2 positive bootstrap capacitor                    |  |

| OUT2P               | 27  | 0        | channel 2 positive PWM output                          |  |

| OUT1P               | 28  | 0        | channel 1 positive PWM output                          |  |

| BOOT1P              | 29  |          | boot 1 positive bootstrap capacitor                    |  |

| PGND1               | 30  | G        | channel 1 power ground                                 |  |

| V <sub>P1</sub> [2] | 31  | Р        | channel 1 power supply voltage                         |  |

| BOOT1N              | 32  |          | boot 1 negative bootstrap capacitor                    |  |

| OUT1N               | 33  | 0        | channel 1 negative PWM output                          |  |

| VSTAB1              | 34  |          | decoupling internal stabilizer 1 for DMOST drivers     |  |

| $V_{DDD}$           | 35  |          | decoupling of the internal 5 V logic supply            |  |

| GNDD/HW             | 36  | G        | ground digital supply voltage                          |  |

|                     |     |          | handle wafer connection                                |  |

|                     |     |          |                                                        |  |

<sup>[1]</sup> I = input, O = output, I/O = input/output, G = ground and P = power supply.

## 8. Functional description

#### 8.1 General

The TDF8599A is a dual full bridge (BTL) audio power amplifier using class-D technology. The audio input signal is converted into a Pulse-Width Modulated (PWM) signal using the analog input and PWM control stages. A PWM signal is applied to driver circuits for both high-side and low-side enabling the DMOS power output transistors to be driven. An external 2<sup>nd</sup> order low-pass filter converts the PWM signal into an analog audio signal across the loudspeakers.

<sup>[2]</sup> In this data sheet supply voltage  $V_P$  describes  $V_{P1}$ ,  $V_{P2}$  and  $V_{PA}$ .

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

The TDF8599A includes integrated common circuits for all channels such as the oscillator, all reference sources, mode functionality and a digital timing manager. In addition, the built-in protection includes thermal foldback, temperature, overcurrent and overvoltage (load dump).

The TDF8599A operates in either I<sup>2</sup>C-bus mode or non-I<sup>2</sup>C-bus mode. In I<sup>2</sup>C-bus mode, DC load detection, frequency hopping and extended configuration functions are provided together with enhanced diagnostic information.

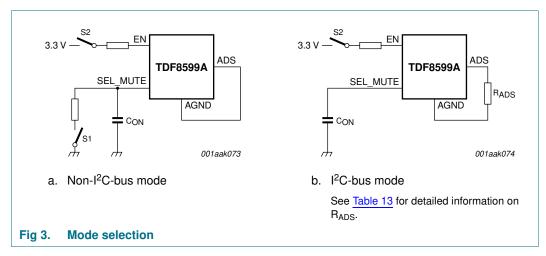

#### 8.2 Mode selection

The mode pins EN, ADS and SEL\_MUTE enable mute state, I<sup>2</sup>C-bus mode and Operating mode switching.

Pin SEL\_MUTE is used to mute and unmute the device and must be connected to an external capacitor ( $C_{ON}$ ). This capacitor generates a time constant which is used to ensure smooth fade-in and fade-out of the input signal.

The TDF8599A is enabled when pin EN is HIGH. When pin EN is LOW, the TDF8599A is off and the supply current is at its lowest value (typically 2  $\mu$ A). When off, the TDF8599A is completely deactivated and will not react to I<sup>2</sup>C-bus commands.

I<sup>2</sup>C-bus mode is selected by connecting a resistor between pins ADS and AGND. In I<sup>2</sup>C-bus mode with pin EN HIGH, the TDF8599A waits for further commands (see Table 4). I<sup>2</sup>C-bus mode is described in Section 9 on page 23.

Non-l<sup>2</sup>C-bus mode is selected by connecting pin ADS to pin AGND. In non-l<sup>2</sup>C-bus mode, the default TDF8599A state is Mute mode. The amplifiers switch idle (50 % duty cycle) and the audio signal is suppressed at the output. In addition, the capacitor ( $C_{SVRR}$ ) is charged to half the supply voltage. To enter Operating mode, pin SEL\_MUTE must be HGH with S1 open, enabling capacitor ( $C_{ON}$ ) charged by an internal pull-up (see Figure 3). In addition, pin EN must be driven HIGH.

$I^2$ C-bus mode and non- $I^2$ C-bus mode control are described in <u>Table 4 on page 7</u> and <u>Table 5 on page 7</u>. Switches S1 and S2 are shown in <u>Figure 3</u>.

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Table 4. I<sup>2</sup>C-bus mode operation

| Pin EN           | Pin SEL_MUTE | Bit IB1[D0] | Bit IB2[D0] | Mode           |

|------------------|--------------|-------------|-------------|----------------|

| HIGH (S2 closed) | HIGH         | 1           | 0           | Operating mode |

|                  | LOW          | 1           | 1           | Mute mode      |

|                  | LOW          | 0           | X[1]        | Standby mode   |

| LOW (S2 open)    | X[1]         | X[1]        | X[1]        | off (default)  |

<sup>[1]</sup> X = do not care.

Table 5. Non-I<sup>2</sup>C-bus mode operation

| Pin EN           | Pin SEL_MUTE    | Mode                |

|------------------|-----------------|---------------------|

| HIGH (S2 closed) | HIGH (S1 open)  | Operating mode      |

|                  | LOW (S1 closed) | Mute mode (default) |

| LOW (S2 open)    | X[1]            | off                 |

<sup>[1]</sup> X = do not care.

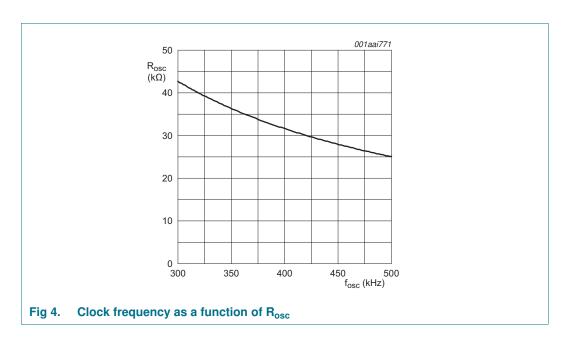

## 8.3 Pulse-width modulation frequency

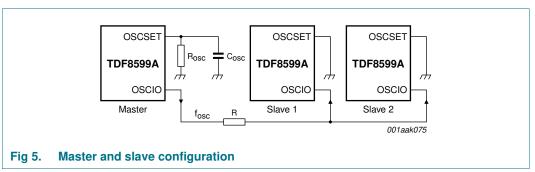

The output signal from the amplifier is a PWM signal with a clock frequency of  $f_{osc}$ . This frequency is set by connecting a resistor ( $R_{osc}$ ) between pins OSCSET and AGND. The optimal clock frequency setting is between 300 kHz and 400 kHz. Connecting a resistor with a value of 39 k $\Omega$ , for example, sets the clock frequency to 320 kHz (see Figure 5). The external capacitor ( $G_{osc}$ ) has no influence on the oscillator frequency. It does however, reduce jitter and sensitivity to disturbance. Using a  $2^{nd}$  order LC demodulation filter in the application generates an analog audio signal across the loudspeaker.

#### 8.3.1 Master and slave mode selection

In a master and slave configuration, multiple TDF8599A devices are daisy-chained together in one audio application with a single device providing the clock frequency signal for all other devices. In this situation, it is recommended that the oscillators of all devices are synchronized for optimum EMI behavior as follows:

All OSCIO pins are connected together and one TDF8599A in the application is configured as the clock-master. All other TDF8599A devices are configured as clock-slaves (see Figure 5).

- The clock-master pin OSCIO is configured as the oscillator output. When a resistor (R<sub>osc</sub>) is connected between pins OSCSET and AGND, the TDF8599A is in Master mode.

- The clock-slave pins OSCIO are configured as the oscillator inputs. When pin OSCSET is directly connected to pin AGND (see <u>Table 6</u>), the TDF8599A is in Slave mode.

Table 6. Mode setting pin OSCIO

| Mode   | Settings                                   |           |  |  |  |  |

|--------|--------------------------------------------|-----------|--|--|--|--|

|        | Pin OSCSET                                 | Pin OSCIO |  |  |  |  |

| Master | $R_{osc} > 26 \text{ k}\Omega$             | output    |  |  |  |  |

| Slave  | $R_{osc} = 0 \Omega$ ; shorted to pin AGND | input     |  |  |  |  |

TDF8599A

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

The value of the resistor R<sub>osc</sub> sets the clock frequency based on Equation 1:

$$f_{osc} = \frac{12.45 \times 10^9}{R_{osc}} [Hz] \tag{1}$$

In Master mode, Spread spectrum mode and frequency hopping can be enabled. In Slave mode, phase staggering and phase lock operation can be selected. An external clock can be used as the master-clock on pin OSCIO of the slave devices. When using an external clock, it must remain active during the shutdown sequence to ensure that all devices are switched off and able to enter the off state as described in Section 8.2 on page 6.

In Slave mode, an internal watchdog timer on pin OSCIO is triggered when the TDF8599A is switched off by pulling down pin EN. If the external clock fails, the watchdog timer forces the TDF8599A to switch off.

## 8.3.2 Spread spectrum mode (Master mode)

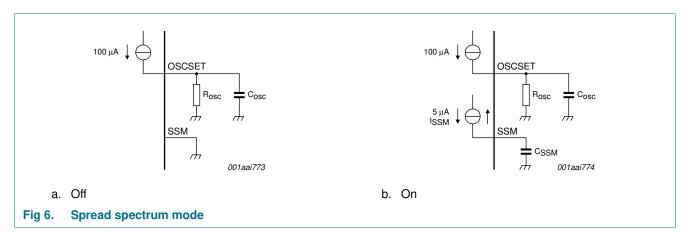

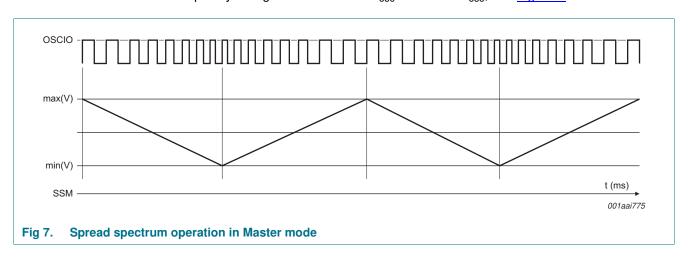

Spread spectrum mode is a technique of modulating the oscillator frequency with a slowly varying signal to broaden the switching spectrum, thereby reducing the spectral density of the EMI. Connecting a capacitor ( $C_{SSM}$ ) to pin SSM enables Spread spectrum mode (see <u>Figure 6</u>). When pin SSM is connected to pin AGND, Spread spectrum mode is disabled.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

The capacitor on pin SSM ( $C_{SSM}$ ) sets the spreading frequency when Spread spectrum mode is active. The current ( $I_{SSM}$ ) flowing in and out of pin SSM is typically 5  $\mu$ A. This gives a triangular voltage on pin SSM that sweeps around the voltage set by pin OSCSET  $\pm$  5 %. The voltage on pin SSM is used to modulate the oscillator frequency.

The spread spectrum frequency (f<sub>SSM</sub>) can be calculated using Equation 2:

$$f_{SSM} = \frac{I_{SSM}}{2 \times C_{SSM} \times V_I \times 10\%} [Hz]$$

(2)

where the voltage on pin OSCSET =  $V_1$  and is calculated as 100  $\mu A \times R_{osc}$  (V) with  $I_{SSM} = 5~\mu A.$

The frequency swings between  $0.95 \times f_{osc}$  and  $1.05 \times f_{osc}$ ; see Figure 7.

#### 8.3.3 Frequency hopping (Master mode)

Frequency hopping is a technique used to change the oscillator frequency for AM tuner compatibility. In Master mode, the resistor connected between pins OSCSET and AGND sets the oscillator frequency ( $f_{osc}$ ). In I<sup>2</sup>C-bus mode, this frequency can be varied by  $\pm$  10 %. Set bit IB1[D4] to logic 1 and bit IB1[D3] to either logic 0 (0.9 ×  $f_{osc}$ ) or logic 1 (1.1 ×  $f_{osc}$ ).

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

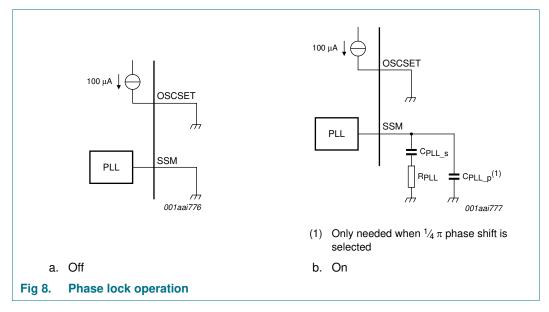

#### 8.3.4 Phase lock operation (Slave mode)

In Slave mode, Phase-Locked Loop (PLL) operation can be used to reduce the jitter effect of the external oscillator signal connected to pin OSCIO. Phase lock operation is also needed to enable phase staggering, see Section 8.4.2 on page 13. Phase lock operation is enabled when the oscillator is in Slave mode by connecting two capacitors ( $C_{PLL_s}$  and  $C_{PLL_p}$ ) and a resistor ( $R_{PLL}$ ) between pin SSM and pin AGND (see Figure 8). Connecting pin SSM to pin AGND disables phase lock operation and causes the slave to directly use the external oscillator signal. Values for  $C_{PLL_s}$ ,  $C_{PLL_p}$  and  $R_{PLL}$  depend on the desired loop bandwidth ( $R_{PLL}$ ) of the PLL.  $R_{PLL}$  is given by:  $R_{PLL} = 8.4 \times R_{PLL} \Omega$ . The corresponding values for  $R_{PLL_s}$  and  $R_{PLL_p}$  are given by Equation 3 and Equation 4:

$$C_{PLL_p} = \frac{0.032}{R_{PII} \times B_{PII}} [F] \tag{3}$$

**Remark:**  $C_{PLL\_p}$  is only needed when  $\frac{1}{4}\pi$  phase shift is selected. See <u>Section 8.4.2</u> for more detailed information.

$$C_{PLL\_s} = \frac{0.8}{R_{PLL} \times B_{PLL}} [F] \tag{4}$$

When pin OSCIO is connected to a clock-master with Spread spectrum mode enabled, the PLL loop bandwidth  $B_{PLL}$  should be 100  $\times$   $f_{SSM}$ .

Table 7 lists all oscillator modes.

Table 7. Oscillator modes

| OSCSET pin                         | OSCIO pin | SSM pin                                         | Oscillator modes           |

|------------------------------------|-----------|-------------------------------------------------|----------------------------|

| $R_{\rm osc} > 26 \text{ k}\Omega$ | output    | C <sub>SSM</sub> to pin AGND                    | master, spread spectrum    |

| $R_{\rm osc} > 26 \text{ k}\Omega$ | output    | shorted to pin AGND                             | master, no spread spectrum |

| $R_{osc} = 0 \Omega$               | input     | C <sub>PLL</sub> + R <sub>PLL</sub> to pin AGND | slave, PLL enabled         |

| $R_{osc} = 0 \Omega$               | input     | shorted to pin AGND                             | slave, PLL disabled        |

TDF8599A

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

## 8.4 Operation mode selection

Pin MOD is used to select specific operating modes. The resistor ( $R_{MOD}$ ) connected between pins MOD and AGND together with the non-I<sup>2</sup>C-bus/I<sup>2</sup>C-bus mode determine the operating mode (see <u>Table 8</u>). The mode of operation depends on whether non-I<sup>2</sup>C-bus mode or I<sup>2</sup>C-bus mode is active. This in turn is determined by the resistor value connected between pins ADS and AGND.

In non-I<sup>2</sup>C-bus mode, pin MOD is used to select:

- AD or BD modulation (see Section 8.4.1).

- $\frac{1}{2}$   $\pi$  phase shift when oscillator is used in Slave mode (see Section 8.4.2).

- Parallel mode operation (see <u>Section 8.4.3</u>).

In I<sup>2</sup>C-bus mode, pin MOD can only select Parallel mode. In addition, the modulation mode and phase shift are programmed using I<sup>2</sup>C-bus commands.

Table 8. Operation mode selection with the MOD pin

| $R_{MOD}$ ( $k\Omega$ ) | I <sup>2</sup> C-bus mode[1] | Non-I <sup>2</sup> C-bus mode <sup>[2]</sup>              |

|-------------------------|------------------------------|-----------------------------------------------------------|

| 0 (short to AGND)       | Stereo mode                  | AD modulation: no phase shift in Slave mode               |

| 4.7                     |                              | BD modulation: no phase shift in Slave mode               |

| 13                      |                              | AD modulation: $\frac{1}{2}\pi$ phase shift in Slave mode |

| 33                      | Parallel mode[3]             | BD modulation: $\frac{1}{2}\pi$ phase shift in Slave mode |

| 100                     |                              | AD modulation: no phase shift in Slave mode               |

| ∞ (open)                |                              | BD modulation: no phase shift in Slave mode               |

<sup>[1]</sup>  $R_{ADS} \ge 4.7 \text{ k}\Omega$ ; See <u>Table 13 on page 23</u>.

In  $I^2C$ -bus mode, pin MOD is latched using the  $I^2C$ -bus command IB3[D7] = 1. This avoids amplifier switching interference generating incorrect information on pin MOD.

In non-I<sup>2</sup>C-bus mode or when IB3[D7] = 0, the information on pin MOD is latched when one of the TDF8599A's outputs starts switching.

## 8.4.1 Modulation mode

In non-I<sup>2</sup>C-bus mode, pin MOD is used to select either AD or BD modulation mode (see <u>Table 8</u>). In I<sup>2</sup>C-bus mode, the modulation mode is selected using an I<sup>2</sup>C-bus command.

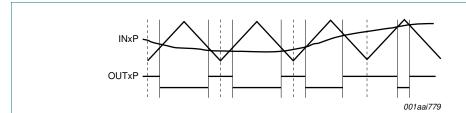

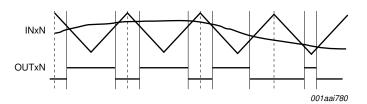

- AD modulation mode: the bridge halves switch in opposite phase.

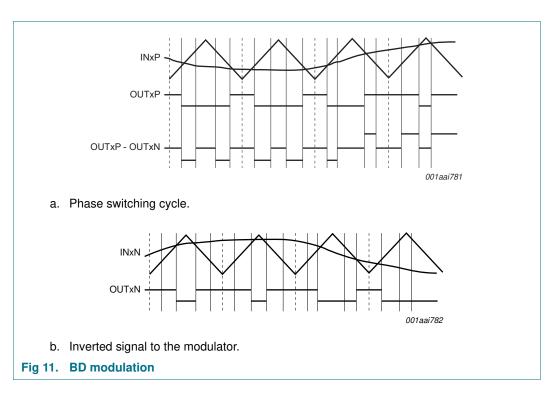

- BD modulation mode: the bridge halves switch in phase but the input signal for the modulators is inverted.

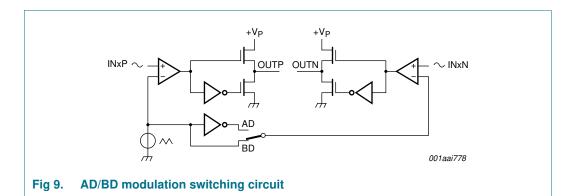

Figure 10 and Figure 11 show simplified representations of AD and BD modulation.

<sup>[2]</sup>  $R_{ADS} = 0 \Omega$ ; pin ADS is short circuited to pin AGND.

<sup>[3]</sup> See Section 8.4.3 on page 14 for more detailed information.

## l<sup>2</sup>C-bus controlled dual channel class-D power amplifier

a. Bridge half 1.

b. Bridge half 2 switched in the opposite phase to bridge half 1.

Fig 10. AD modulation

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

## 8.4.2 Phase staggering (Slave mode)

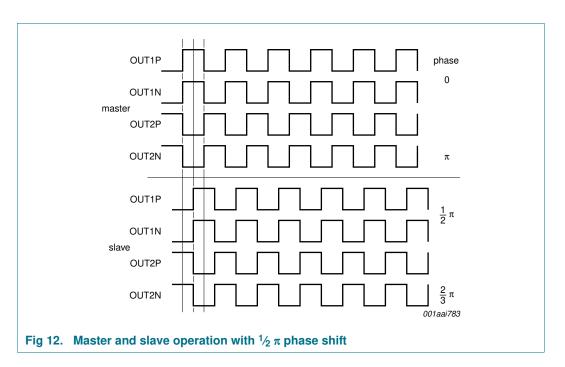

In Slave mode with phase lock operation enabled, a phase shift with respect to the incoming clock signal can be selected to distribute the switching moments over time. In non-I²C-bus mode,  $1_{\!\!/2}$   $\pi$  phase shift can be programmed using pin MOD. In I²C-bus mode, five different phase shifts ( $1_{\!\!/4}$   $\pi$ ,  $1_{\!\!/3}$   $\pi$ ,  $1_{\!\!/2}$   $\pi$ ,  $2_{\!\!/3}$   $\pi$ ,  $3_{\!\!/4}$   $\pi$ ) can be selected using the I²C-bus bits (IB3[D1:D3]). See Table 8 for selection of the phase shift in non-I²C-bus mode with pin MOD. An additional capacitor must be connected to pin SSM when  $1_{\!\!/4}$   $\pi$  phase shift is used (see Figure 8). An example of using  $1_{\!\!/2}$   $\pi$  phase shift for BD modulation is shown in Figure 12.

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

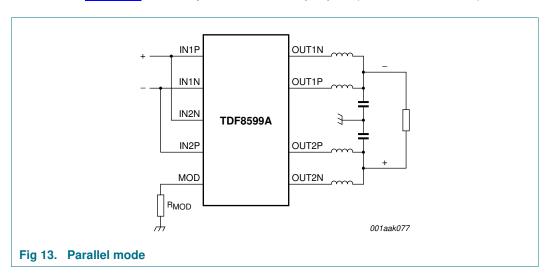

#### 8.4.3 Parallel mode

In Parallel mode; the two output stages operate in parallel to enlarge the drive capability. The inputs and outputs for Parallel mode must be connected on the Printed-Circuit Board (PCB) as shown in Figure 13. The parallel connection can be made after the output filter, as shown in Figure 13 or directly to the device output pins (OUTxP and OUTxN).

In Parallel mode, the channel 1 I<sup>2</sup>C-bus bits can be programmed using the I<sup>2</sup>C-bus.

## 8.5 Protection

The TDF8599A includes a range of built-in protection functions. How the TDF8599A manages the various possible fault conditions for each protection is described in the following sections:

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Table 9. Overview of protection types

| Reference     |

|---------------|

| Section 8.5.1 |

| Section 8.5.2 |

| Section 8.5.3 |

| Section 8.5.4 |

| Section 8.5.5 |

| Section 8.5.6 |

| Section 8.5.6 |

|               |

#### 8.5.1 Thermal foldback

Thermal Foldback Protection (TFP) is tripped when the average junction temperature exceeds the threshold level (145 °C). TFP decreases amplifier gain such that the combination of power dissipation and  $R_{th(j\text{-}a)}$  create a junction temperature around the threshold level. The device will not completely switch off but remains operational at the lower output power levels. If the average junction temperature continues to increase, a second built-in temperature protection threshold level shuts down the amplifier completely.

#### 8.5.2 Overtemperature protection

If the average junction temperature  $(T_j) > 160$  °C, OverTemperature Protection (OTP) is tripped and the power stage shuts down immediately.

#### 8.5.3 Overcurrent protection

OverCurrent Protection (OCP) is tripped when the output current exceeds the maximum output current of 8 A. OCP regulates the output voltage such that the maximum output current is limited to 8 A. The amplifier outputs keep switching and the amplifier is NOT shutdown completely. This is called current limiting.

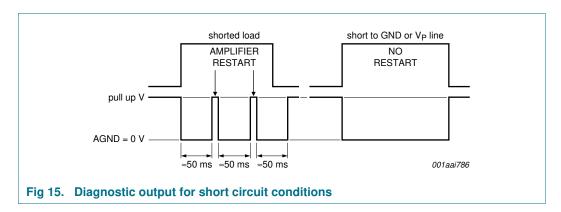

OCP also detects when the loudspeaker terminals are short circuited or one of the amplifier's demodulated outputs is short circuited to one of the supply lines. In either case, the shorted channel(s) are switched off.

The amplifier can distinguish between loudspeaker impedance drops and a low-ohmic short across the load or one of the supply lines. This impedance threshold depends on the supply voltage used. When a short is made across the load causing the impedance to drop below the threshold level, the shorted channel(s) are switched off. They try to restart every 50 ms. If the short circuit condition is still present after 50 ms, the cycle repeats. The average power dissipation will be low because of this reduced duty cycle.

When a channel is switched off due to a short circuit on one of the supply lines, Window Protection (WP) is activated. WP ensures the amplifier does not start-up after 50 ms until the supply line short circuit is removed.

#### 8.5.4 Window protection

Window Protection (WP) checks the PWM output voltage before switching from Standby mode to Mute mode (with both outputs switching) and is activated as follows:

TDF8599A **NXP Semiconductors**

## l<sup>2</sup>C-bus controlled dual channel class-D power amplifier

- · During the start-up sequence:

- When the TDF8599A is switched from standby to mute (t<sub>d(stb-mute)</sub>). When a short circuit on one of the output terminals (i.e. between V<sub>P</sub> or GND) is detected, the start-up procedure is interrupted and the TDF8599A waits for open circuit outputs. No large currents flow in the event of a short circuit to the supply lines because the check is performed before the power stages are enabled.

- During operation:

- A short to one of the supply lines trips OCP causing the amplifier channel to shutdown. After 50 ms the amplifier channel restarts and WP is activated. However, the corresponding amplifier channel will not start-up until the supply line short circuit has been removed.

#### 8.5.5 DC offset protection

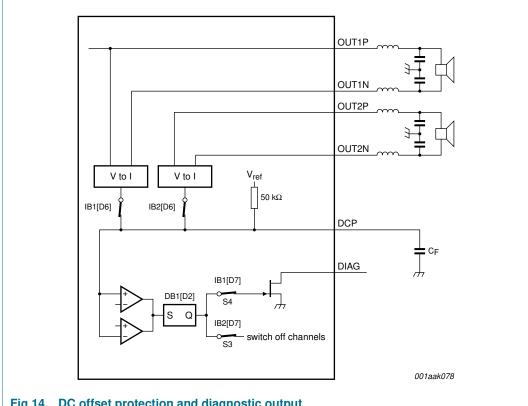

DC Protection (DCP) is activated when the DC content in the demodulated output voltage exceeds a set threshold (typically 2 V). DCP is active in both Mute mode and Operating mode. Figure 14 shows how false triggering of the DCP by low frequencies in the audio signal is prevented using the external capacitor (C<sub>F</sub>) to generate a cut-off frequency.

Fig 14. DC offset protection and diagnostic output

In I<sup>2</sup>C-bus mode, DC offsets generate a voltage shift around the bias voltage. When the voltage shift exceeds threshold values, the offset alarm bit DB1[D2] is set and if bit IB1[D7] is not set, diagnostic information is also given. Any detected offset shuts down both channels when bit IB2[D7] is not set. To restart the TDF8599A in I2C-bus mode, pin EN must be toggled or DCP disabled by connecting pin DCP to pin AGND.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

In non-I<sup>2</sup>C-bus mode, when an offset is detected, DCP always gives diagnostic information on pin DIAG and shuts down both channels.

Connecting a capacitor between pins DCP and AGND enables DC offset protection. Connecting pin DCP to pin AGND disables DCP in both I<sup>2</sup>C-bus and non-I<sup>2</sup>C-bus mode.

#### 8.5.6 Supply voltages

UnderVoltage Protection (UVP) is activated when the supply voltage drops below the UVP threshold. UVP triggers the UVP circuit causing the system to first mute and then stop switching. When the supply voltage rises above the threshold level, the system restarts.

OverVoltage Protection (OVP) is activated when the supply voltage exceeds the OVP threshold. The OVP (or load dump) circuit is activated and the power stages are shutdown.

An overview of all protection circuits and the amplifier states is given in Table 10.

#### 8.5.7 Overview of protection circuits and amplifier states

Table 10. Overview of TDF8599A protection circuits and amplifier states

| Protection circuit name | Amplifier stat    | Amplifier state  |            |  |  |

|-------------------------|-------------------|------------------|------------|--|--|

|                         | Complete shutdown | Channel shutdown | Restart[1] |  |  |

| TFP                     | N[2]              | N <sup>[2]</sup> | Y[3]       |  |  |

| OTP                     | Υ                 | N                | Y[3]       |  |  |

| OCP                     | N                 | Υ                | Y[4]       |  |  |

| WP                      | N                 | Υ                | Υ          |  |  |

| DCP                     | Υ                 | N                | N[5]       |  |  |

| UVP                     | Υ                 | N                | Y[6]       |  |  |

| OVP                     | Υ                 | N                | Υ          |  |  |

<sup>[1]</sup> When fault is removed.

#### 8.6 Diagnostic output

#### 8.6.1 Diagnostic table

The diagnostic information for  $I^2C$ -bus mode and non- $I^2C$ -bus mode is shown in <u>Table 11</u>. The instruction bitmap and data bytes are described in <u>Table 14</u> and <u>Table 15</u>.

Pins DIAG and CLIP have an open-drain output which must have an external pull-up resistor connected to an external voltage. Pins CLIP and DIAG can show both fixed and  $I^2C$ -bus selectable information.

<sup>[2]</sup> Amplifier gain depends on the junction temperature and size of the heat sink.

<sup>[3]</sup> TFP influences restart timing depending on heat sink size.

<sup>[4]</sup> Shorted load causes a restart of the channel every 50 ms.

<sup>[5]</sup> Latched protection is reset by toggling pin EN or by disabling DCP in I<sup>2</sup>C-bus mode.

<sup>[6]</sup> In I<sup>2</sup>C-bus mode deep supply voltage drops will cause a Power-On Reset (POR). The restart requires an I<sup>2</sup>C-bus command.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Pin DIAG goes LOW when a short circuit to one of the amplifier outputs occurs. The microprocessor reads the failure information using the I<sup>2</sup>C-bus. The I<sup>2</sup>C-bus bits are set for a short circuit. These bits can be reset with the I<sup>2</sup>C-bus read command.

Even after the short has been removed, the microprocessor knows what was wrong after reading the I<sup>2</sup>C-bus. Old information is read when a single I<sup>2</sup>C-bus read command is used. To read the current information, two read commands must be sent, one after another.

When selected, pin DIAG gives the current diagnostic information. Pin DIAG is released instantly when the failure is removed, independent of the I<sup>2</sup>C-bus latches.

| Diagnostic              | I <sup>2</sup> C-bus me | I <sup>2</sup> C-bus mode |          | Non-I <sup>2</sup> C-bus mode |  |

|-------------------------|-------------------------|---------------------------|----------|-------------------------------|--|

|                         | Pin DIAG                | Pin CLIP                  | Pin DIAG | Pin CLIP                      |  |

| Power-on reset          | yes                     | yes                       | yes      | yes                           |  |

| UVP or OVP              | yes                     | no                        | yes      | no                            |  |

| Clip detection          | no                      | selectable                | no       | yes                           |  |

| Temperature pre-warning | no                      | selectable                | no       | yes                           |  |

| OCP/WP                  | yes                     | no                        | yes      | no                            |  |

| DCP                     | selectable              | no                        | yes      | no                            |  |

| OTP                     | yes                     | no                        | yes      | no                            |  |

When OCP is triggered, the open-drain DIAG output is activated. The diagnostic output signal during different short circuit conditions is illustrated in Figure 15.

## 8.6.2 Load identification (I<sup>2</sup>C-bus mode only)

#### 8.6.2.1 DC load detection

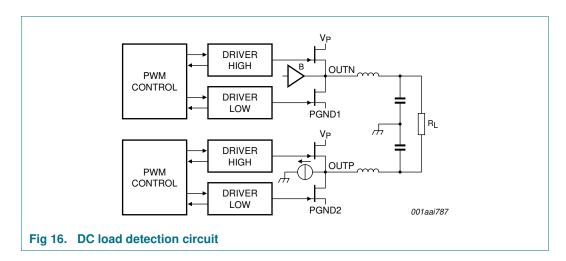

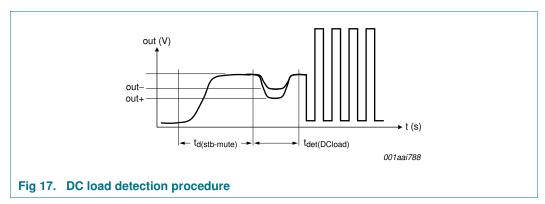

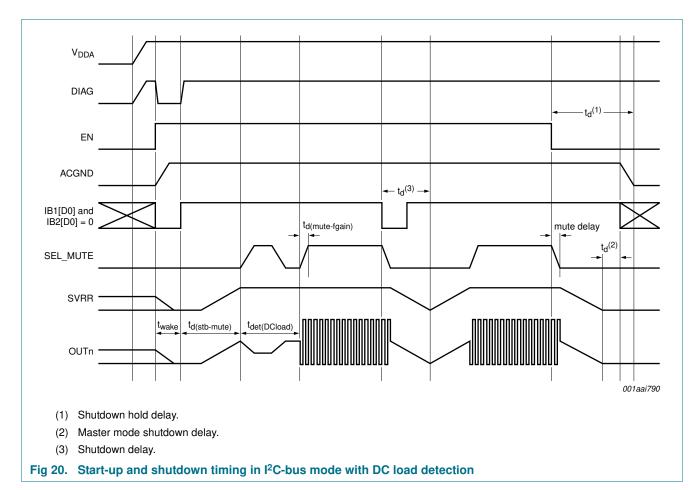

DC load detection is only available in  $I^2C$ -bus mode and is controlled using bit IB2[D2]. The default setting is logic 0 for bit IB2[D2] which disables DC load detection. DC load detection is enabled when bit IB2[D2] = 1. Load detection takes place before the class-D amplifier output stage starts switching in Mute mode and the start-up time from Standby mode to Mute mode is increased by  $t_{det(DCload)}$  (see Figure 16).

18 of 55

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

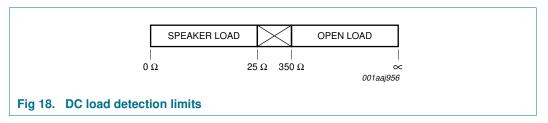

The capacitor connected to pin SEL\_MUTE (see <u>Figure 3 on page 6</u>) is used to create an inaudible current test pulse, drawn from the positive amplifier output. The diagnostic 'speaker load' (or 'open load'), based on the voltage difference between pins OUTxP and OUTxN is shown in <u>Figure 18</u>.

**Remark:** DC load detection identifies a short circuited speaker as a valid speaker load. OCP detection, using byte DB1[D3] for channel 1 and byte DB2[D3] for channel 2, performs diagnostics on shorted loads. However, the diagnostics are performed after the DC load detection cycle has finished and once the amplifier is in Operating mode.

The result of the DC load detection is stored in bits DB1[D4] and DB2[D4].

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Table 12. Interpretation of DC load detection bits

| DC load bits DB1[D4] and DB2[D4] | OCP bits DB1[D3] and DB2[D3] | Description  |

|----------------------------------|------------------------------|--------------|

| 0                                | 0                            | speaker load |

| 0                                | 1                            | shorted load |

| 1                                | 0                            | open load    |

Remark: After DC load detection has been performed, the DC load valid bit DB1[D6] must be set. The DC load data bits are only valid when bit DB1[D6] = 1. When DC load detection is interrupted by a sudden large change in supply voltage (triggered by UVP or OVP) or if the amplifier hangs up, the DC load valid bit is reset to DB1[D6] = 0. The DC load detection enable bit IB2[D2] must be reset after the DC load protection cycle to release any amplifier hang-up. Once the DC load detection cycle has finished, DC load detection can be restarted by toggling the DC load detection enable bit IB2[D2]. However, this can only be used if both amplifier channels have not been enabled with bit IB1[D1] or bit IB2[D1]. See Section 8.6.2.2 "Recommended start-up sequence with DC load detection enabled" for detailed information.

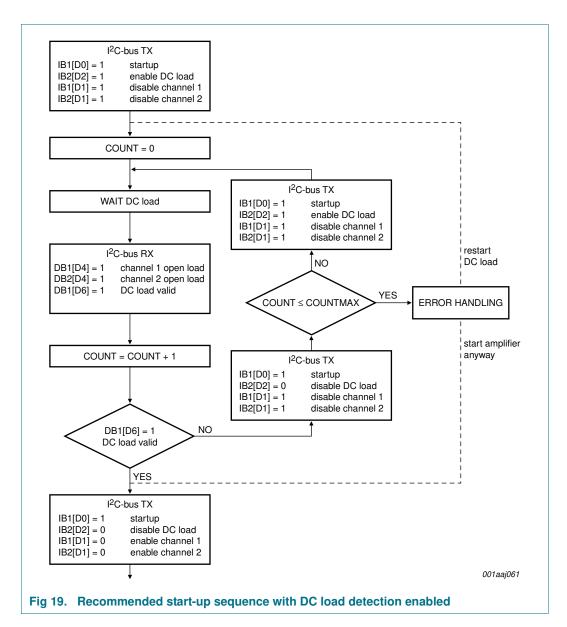

#### 8.6.2.2 Recommended start-up sequence with DC load detection enabled

The flow diagram (Figure 19) illustrates the TDF8599A's ability to perform a DC load detection without starting the amplifiers. After a DC load detection cycle finishes without setting the DC load valid bit DB1[D6], DC load detection is repeated (when bit IB2[D2] is toggled).

To limit the maximum number of DC load detection cycle loops, a counter and limit have been added. The loop exits after the predefined number of cycles (COUNTMAX), if the DC load detection cycle finishes with an invalid detection.

Depending on the application needs, the invalid DC load detection cycle can be handled as follows:

- the amplifier can be started without DC load detection

- the DC load detection loop can be executed again

#### I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

#### 8.6.2.3 AC load detection

AC load detection is only available in  $I^2C$ -bus mode and is controlled using bit IB3[D4]. The default setting for bit IB3[D4] = 0 disables AC load detection. When AC load detection is enabled (bit IB3[D4] = 1), the amplifier load current is measured and compared with a reference level. Pin CLIP is activated when this threshold is reached. Using this information, AC load detection can be performed using a predetermined input signal frequency and level. The frequency and signal level should be chosen so that the load current exceeds the programmed current threshold when the AC coupled load (tweeter) is present.

#### 8.6.2.4 CLIP detection

CLIP detection gives information for clip levels  $\geq 0.2$  %. Pin CLIP is used as the output for the clip detection circuitry on both channel 1 and channel 2. Setting either bit IB1[D5] or bit IB2[D5] to logic 0 defines which channel reports clip information on the CLIP pin.

## l<sup>2</sup>C-bus controlled dual channel class-D power amplifier

#### 8.6.3 Start-up and shutdown sequence

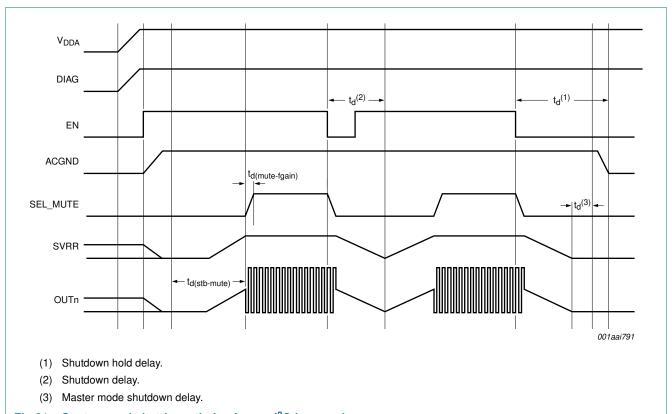

To prevent switch on or switch off 'pop noises', a capacitor ( $C_{SVRR}$ ) connected to pin SVRR is used to smooth start-up and shutdown. During start-up and shutdown, the output voltage tracks the voltage on pin SVRR. Increasing  $C_{SVRR}$  results in a longer start-up and shutdown time. Enhanced pop noise performance is achieved by muting the amplifier until the SVRR voltage reaches its final value and the outputs start switching. The capacitor value on pin SEL\_MUTE ( $C_{ON}$ ) determines the unmute and mute timing. The voltage on pin SEL\_MUTE determines the amplifier gain. Increasing  $C_{ON}$  increases the unmute and mute times. In addition, a larger  $C_{ON}$  value increases the DC load detection cycle.

When the amplifier is switched off with an  $I^2C$ -bus command or by pulling pin EN LOW, the amplifier is first muted and then capacitor ( $C_{SVRR}$ ) is discharged.

In Slave mode, the device enters the off state immediately after capacitor ( $C_{SVRR}$ ) is discharged. In Master mode, the clock is kept active by an additional delay ( $t_d^{(2)}$ ) of approximately 50 ms to allow slave devices to enter the off state.

When an external clock is connected to pin OSCIO (in Slave mode), the clock must remain active during the shutdown sequence for delay  $(t_d^{(1)})$  to ensure that the slaved TDF8599A devices are able to enter the off state.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

Fig 21. Start-up and shutdown timing in non-l<sup>2</sup>C-bus mode

# 9. I<sup>2</sup>C-bus specification

TDF8599A address with hardware address select.

Table 13. I<sup>2</sup>C-bus write address selection using pins MOD and ADS

| $R_{ADS}^{[1]}(k\Omega)$ | $R_{MOD}^{[1]}(k\Omega)$             |     |     |               |     | R/W  |                        |

|--------------------------|--------------------------------------|-----|-----|---------------|-----|------|------------------------|

|                          | Stereo mode                          |     |     | Parallel mode |     |      |                        |

|                          | 0[2]                                 | 4.7 | 13  | 33            | 100 | open |                        |

| Open                     | 58h                                  | 68h | 78h | 58h           | 68h | 78h  | 1 = Read from TDF8599A |

| 100                      | 56h                                  | 66h | 76h | 56h           | 66h | 76h  | 0 = Write to TDF8599A  |

| 33                       | 54h                                  | 64h | 74h | 54h           | 64h | 74h  |                        |

| 13                       | 52h                                  | 62h | 72h | 52h           | 62h | 72h  |                        |

| 4.7                      | 50h                                  | 60h | 70h | 50h           | 60h | 70h  |                        |

| 0[2]                     | non-l <sup>2</sup> C-bus mode select |     |     |               |     |      |                        |

<sup>[1]</sup> Required external resistor accuracy is 1 %.

In I $^2$ C-bus mode, pins MOD and ADS can be latched using the I $^2$ C-bus command IB3[D7] = 1. This avoids disturbances from amplifier outputs of other TDF8599A devices in the same application switching and generating incorrect information on the MOD and ADS pins.

<sup>[2]</sup> Short circuited to ground.

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

In non- $I^2C$  mode or when IB3[D7] = 0, the information on the MOD and ADS pins is latched when one of the TDF8599A's outputs starts switching.

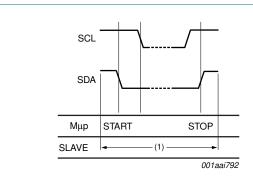

When SCL is HIGH, SDA changes to form the start or stop condition.

Fig 22. I<sup>2</sup>C-bus start and stop conditions

- (1) SDA is allowed to change.

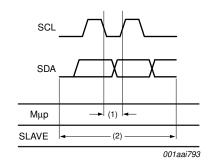

- (2) All data bits must be valid on the positive edges of SCL.

Fig 23. Data bits sent from Master microprocessor  $(M\mu p)$

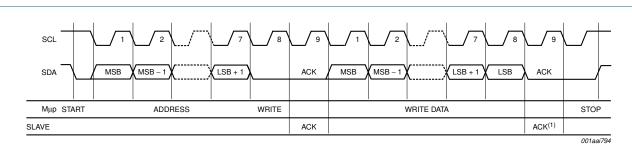

(1) To stop the transfer after the last acknowledge a stop condition must be generated.

Fig 24. I<sup>2</sup>C-bus write

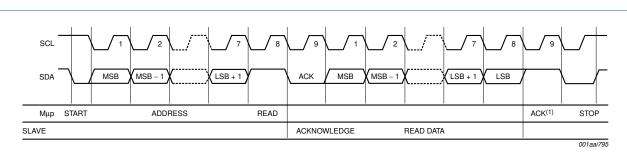

(1) To stop the transfer, the last byte must not be acknowledged (SDA is HIGH) and a stop condition must be generated.

Fig 25. I<sup>2</sup>C-bus read

## I<sup>2</sup>C-bus controlled dual channel class-D power amplifier

## 9.1 Instruction bytes

If R/W bit = 0, the TDF8599A expects three instruction bytes: IB1, IB2 and IB3. After a power-on reset, all unspecified instruction bits must be set to zero.

Table 14. Instruction byte descriptions

| Bit | Value | Description                                                  |                                      |                                                                           |  |  |  |  |

|-----|-------|--------------------------------------------------------------|--------------------------------------|---------------------------------------------------------------------------|--|--|--|--|

|     |       | Instruction byte IB1                                         | Instruction byte IB2                 | Instruction byte IB3                                                      |  |  |  |  |

| D7  | 0     | offset detection on pin DIAG                                 | offset protection on                 | latch information on pins ADS and MOD when the amplifier starts switching |  |  |  |  |

|     | 1     | no offset detection on pin DIAG                              | offset protection off                | latch information on pins ADS and MOD; see <u>Section 9 on page 23</u>    |  |  |  |  |

| D6  | 0     | channel 1 offset monitoring on                               | channel 2 offset monitoring on       | -                                                                         |  |  |  |  |

|     | 1     | channel 1 offset monitoring off                              | channel 2 offset monitoring off      | -                                                                         |  |  |  |  |

| D5  | 0     | channel 1 clip detect on pin CLIP                            | channel 2 clip detect on pin CLIP    | -                                                                         |  |  |  |  |

|     | 1     | channel 1 no clip detect on pin CLIP                         | channel 2 no clip detect on pin CLIP | -                                                                         |  |  |  |  |

| D4  | 0     | disable frequency hopping                                    | thermal pre-warning on pin CLIP      | disable AC load detection                                                 |  |  |  |  |

|     | 1     | enable frequency hopping[1]                                  | no thermal pre warning on pin CLIP   | enable AC load detection                                                  |  |  |  |  |

| D3  | 0     | oscillator frequency as set with $R_{\text{osc}} - 10 \; \%$ | temperature pre-warning at 140 °C    | oscillator phase shift bits IB3[D3] to IB3[D1][2]                         |  |  |  |  |

|     | 1     | oscillator frequency as set with R <sub>osc</sub> + 10 %     | temperature pre-warning at 120 °C    |                                                                           |  |  |  |  |

| D2  | 0     | -                                                            | DC-load detection disabled           |                                                                           |  |  |  |  |

|     | 1     | -                                                            | DC-load detection enabled            |                                                                           |  |  |  |  |

| D1  | 0     | channel 1 enabled                                            | channel 2 enabled                    |                                                                           |  |  |  |  |

|     | 1     | channel 1 disabled                                           | channel 2 disabled                   |                                                                           |  |  |  |  |

| D0  | 0     | TDF8599A in Standby mode                                     | all channels operating               | AD modulation                                                             |  |  |  |  |

|     | 1     | TDF8599A in Mute or Operating modes[3]                       | all channels muted                   | BD modulation                                                             |  |  |  |  |

<sup>[1]</sup> See Section 8.3.3 on page 9 for information on IB1[D4] and IB1[D3].

Table 15. Phase shift bit settings

| D3 | D2 | D1 | Phase |

|----|----|----|-------|

| 0  | 0  | 0  | 0     |

| 0  | 0  | 1  | 1/4 π |

| 0  | 1  | 0  | 1/3 π |

| 0  | 1  | 1  | 1/2 π |

| 1  | 0  | 0  | 2/3 π |

| 1  | 0  | 1  | 3/4 π |

<sup>[2]</sup> See Table 15 "Phase shift bit settings" for information on IB3[D3] to IB3[D1].

<sup>[3]</sup> See Table 4 for information on IB1[D0] and IB2[D0].