# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### 1. General description

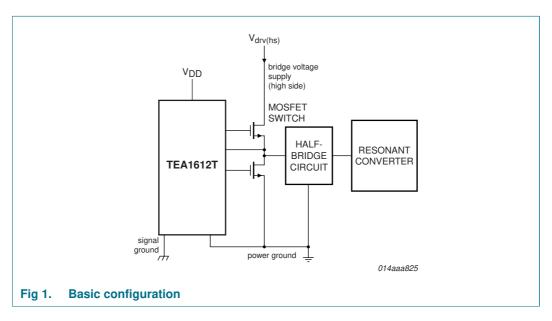

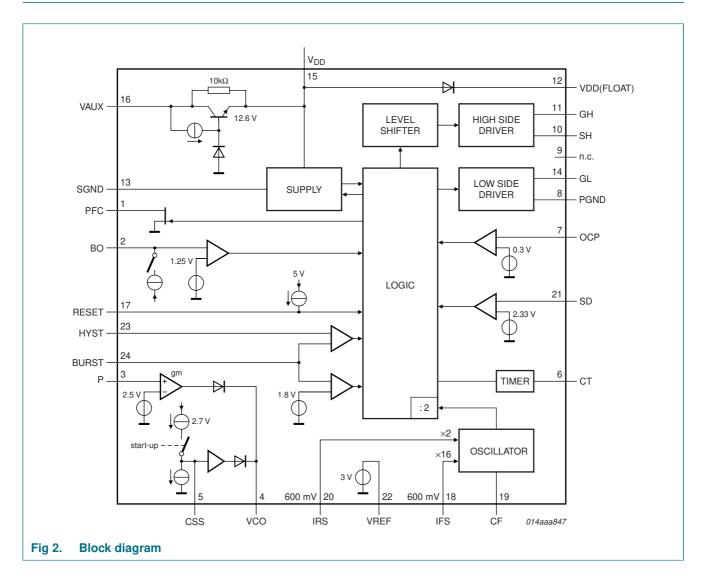

The TEA1612T is a monolithic integrated circuit implemented in a high-voltage double Diffused Metal Oxide Semiconductor (DMOS) process. The circuit is a high voltage controller for a zero-voltage switching resonant converter. The IC provides the drive function for two discrete power MOSFETs in a half-bridge configuration. It also includes a level-shift circuit, an oscillator with an accurately-programmable frequency range, a latched shut-down function, burst mode operation and a transconductance error amplifier.

The oscillator signal passes through a divide-by-two flip-flop before being fed to the output drivers in order to guarantee an accurate 50 % switching duty factor.

The circuit is very flexible and enables a broad range of applications for different mains voltages.

### 2. Features

- Adjustable burst mode operation at low loads for low standby power

- Integrated high voltage level-shift function

- Integrated high voltage bootstrap diode

- Low start-up current

- Adjustable non-overlap time

- Internal Over Temperature Protection (OTP)

- Over Current Protection (OCP) that activates a shut-down timer

- Soft start timing pin

- Brown Out (BO) detection

- Transconductance error amplifier for ultra high-ohmic regulation feedback

- Latched shut-down circuit for Over Voltage Protection (OVP)

- Adjustable minimum and maximum frequencies

- Under Voltage Lock Out (UVLO)

- Fault latch reset input

- Wide (max. 20 V) supply voltage range

- PFC-off output

### 3. Applications

- TV and monitor power supplies

- High power adapter

- PC power supplies

- High voltage power supplies

- Office equipment

### 4. Ordering information

#### Table 1.Ordering information

| Type number | Package | Package                                                    |          |  |  |

|-------------|---------|------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                | Version  |  |  |

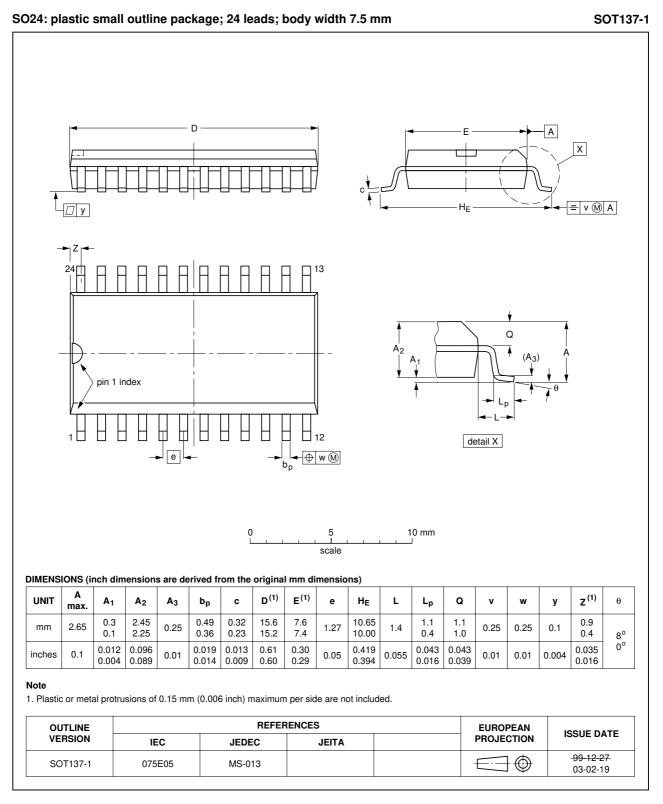

| TEA1612T    | SO24    | plastic small outline package; 24 leads; body width 7.5 mm | SOT137-1 |  |  |

## **TEA1612T**

Zero voltage switching resonant converter controller

### 5. Block diagram

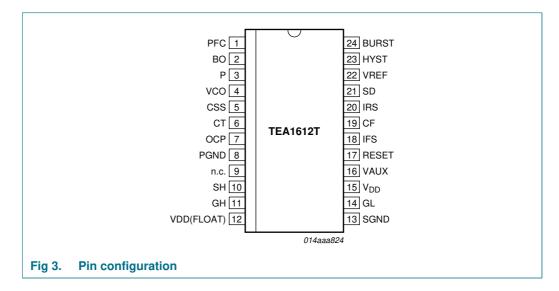

### 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

| Table 2.        | Pin description, p | proposal                            |

|-----------------|--------------------|-------------------------------------|

| Symbol          | Pin                | Description                         |

| PFC             | 1                  | PFC-control output                  |

| BO              | 2                  | brownout input                      |

| Ρ               | 3                  | error amplifier non-inverting input |

| VCO             | 4                  | error amplifier output              |

| CSS             | 5                  | soft start capacitor input          |

| CT              | 6                  | timer capacitor input               |

| OCP             | 7                  | overcurrent protection input        |

| PGND            | 8                  | power ground                        |

| n.c.            | 9                  | not connected <sup>[1]</sup>        |

| SH              | 10                 | high side switch source connection  |

| GH              | 11                 | high side switch gate connection    |

| VDD(FLOAT       | T) 12              | floating supply high side driver    |

| SGND            | 13                 | signal ground                       |

| GL              | 14                 | low side switch gate connection     |

| V <sub>DD</sub> | 15                 | supply voltage                      |

| VAUX            | 16                 | auxiliary supply voltage            |

| RESET           | 17                 | latch reset input                   |

| IFS             | 18                 | oscillator discharge current input  |

| CF              | 19                 | oscillator capacitor                |

| IRS             | 20                 | oscillator charge input current     |

| SD              | 21                 | shut-down input                     |

| Table 2. | Pin description, proposal |                                           |  |

|----------|---------------------------|-------------------------------------------|--|

| Symbol   | Pin                       | Description                               |  |

| VREF     | 22                        | reference voltage                         |  |

| HYST     | 23                        | hysteresis reference input for burst mode |  |

| BURST    | 24                        | burst comparator input                    |  |

[1] Provided as a high voltage spacer

### 7. Functional description

### 7.1 Start-up

When the applied voltage at pin  $V_{DD}$  reaches  $V_{DD(init)}$  (see Figure 4), the low side power switch is turned-on while the high side power switch remains in the non-conducting state. This start-up output state guarantees the initial charging of the bootstrap capacitor ( $C_{boot}$ ) used for the floating supply of the high side driver.

During start-up, the voltage on the frequency capacitor ( $C_f$ ) is zero and defines the start-up state. The voltage at the soft start pin (CSS) is set to 2.7 V. The CSS pin voltage is copied to the VCO pin via a buffer and switching starts at about 80 % of the maximum frequency at the moment  $V_{DD}$  reaches the start level.

The start-up state is maintained until  $V_{DD}$  reaches the start level (13.5 V), the oscillator is activated and the converter starts operating.

### 7.2 Oscillator

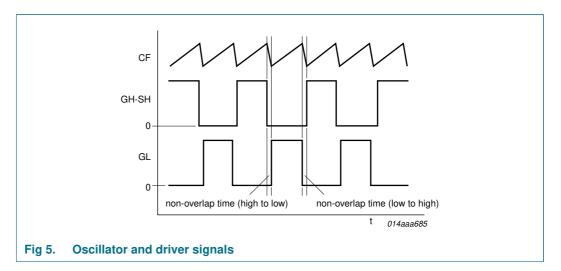

The internal oscillator is a current-controlled oscillator that generates a sawtooth output. The frequency of the sawtooth is determined by the external capacitor  $C_f$  and the currents flowing into the IFS and IRS pins.

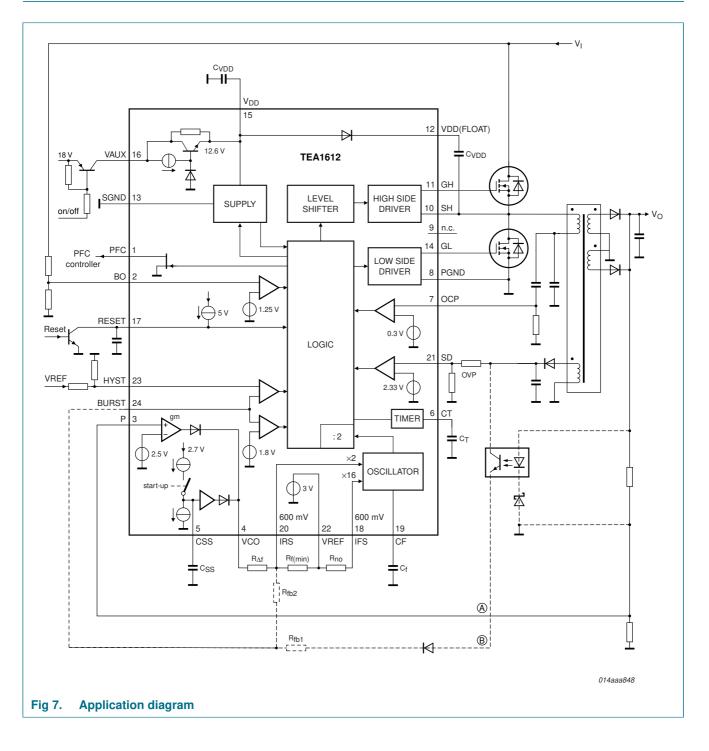

The minimum frequency and the non-overlap time are set by the capacitor C<sub>f</sub> and resistors R<sub>f(min)</sub> and R<sub>no</sub>. The maximum frequency is set by resistor R<sub> $\Delta f$ </sub> (see Figure 7). The oscillator frequency is exactly twice the bridge frequency to achieve an accurate 50 % duty factor. An overview of the oscillator and driver signals is given in Figure 5.

### 7.3 Non-overlap time resistor

The non-overlap time resistor  $R_{no}$  is connected between the 3 V reference pin VREF, and the IFS current input pin (see Figure 7). The voltage on the IFS pin is kept constant at a temperature independent value of 0.6 V. The current that flows into the IFS pin is determined by resistor's  $R_{no}$  2.4 V voltage drop divided by its value. The IFS input current equals 1/16 of the discharge current of capacitor  $C_f$  and determines the falling slope of the oscillator.

The falling slope time is used to create a non-overlap time  $(t_{no})$  between two successive switching actions of the half-bridge switches:

$$I_{IFS} = \frac{2.4V}{R_{no}}$$

$$t_{no} = \frac{C_f \times \Delta V_{Cf}}{16 \times I_{IFS}}$$

$t_{IFS} = t_{no}$

### 7.4 Minimum frequency resistor

The  $R_{f(min)}$  resistor is connected between the VREF pin (3 V reference voltage) and the IRS current input pin (held at a temperature independent voltage level of 0.6 V). The charge current of the capacitor  $C_f$  is twice the current flowing into the IRS pin.

The  $R_{f(min)}$  resistor has a voltage drop of 2.4 V and its resistance defines the minimum charge current (rising slope) of the  $C_f$  capacitor if the control current is zero. The minimum frequency is defined by this minimum charge current ( $I_{IRS1}$ ) and the discharge current:

$$I_{IRS1} = \frac{2.4V}{R_{f(min)}}$$

$$t_{IRS1} = \frac{C_f \times \Delta V_{Cf}}{2 \times I_{IRS1}}$$

$$f_{osc(min)} = \frac{1}{t_{no} + t_{IRSI}}$$

$$f_{bridge(min)} = \frac{f_{osc(min)}}{2}$$

### 7.5 Maximum frequency resistor

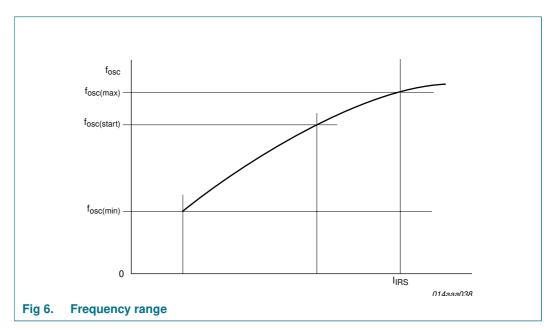

The output voltage is regulated by changing the frequency of the half-bridge converter. The maximum frequency is determined by the  $R_{\Delta f}$  resistor which is connected between the error amplifier output VCO and the oscillator current input pin IRS. The current that flows through the  $R_{\Delta f}$  resistor ( $I_{IRS2}$ ) is added to the current flowing through the  $R_{f(min)}$  resistor. As a result, the charge current  $I_{CF}$  increases and the oscillation frequency increases. As the falling slope of the oscillator is constant, the relationship between the output frequency and the charge current is not a linear function (see Figure 6 and Figure 7):

$$I_{IRS2} = \frac{V_{VCO} - 0.6}{R_{\Delta f}}$$

$t_{IRS2} = \frac{C_f \times \Delta V_{Cf}}{2 \times (I_{IRS1} + I_{IRS2})}$

The maximum output voltage of the error amplifier and the value of  $R_{\Delta f}$  determine the maximum frequency:

$$I_{IRS2(max)} = \frac{V_{VCO(max)} - 0.6}{R_{\Delta f}}$$

$$C_f \times \Delta V_{Cf}$$

$$t_{IRS(min)} = \frac{I_J + I_{IRS2}}{2 \times (I_{IRS2} + I_{IRS2(max)})}$$

$$f_{osc(max)} = \frac{1}{T_{osc}}$$

$$f_{bridge(max)} = \frac{f_{osc(max)}}{2}$$

$$T_{OSC} = t_{IRS(min)} + t_{IFS}$$

TEA1612T\_1 Product data sheet

Bridge frequency accuracy is optimum in the low frequency region. At higher frequencies both the non-overlap time and the oscillator frequency show a decay.

The frequency of the oscillator depends on the value of capacitor  $C_f$ , the peak-to-peak voltage swing  $V_{CF}$ , and the charge and discharge currents. However, at higher frequencies the accuracy decreases due to delays in the circuit.

### 7.6 Error amplifier

The error amplifier is a transconductance amplifier. Thus the output current at pin VCO is determined by the amplifier transconductance, the differential voltage on input pin P, and the internal reference voltage (2.5 V). The output current  $I_{VCO}$  is fed to the IRS input of the current-controlled oscillator.

The source capability of the error amplifier increases current in the IRS pin when the differential input voltage is positive. Therefore the minimum current is determined by resistor  $R_{f(min)}$  and the minimum frequency setting is independent of the characteristics of the error amplifier.

The error amplifier has a maximum output current of 0.5 mA for an output voltage up to 2.5 V. If the source current decreases, the oscillator frequency also decreases resulting in a higher regulated output voltage.

During start-up, the output voltage of the amplifier is connected to the soft start (CSS) pin via a buffer. This will hold the VCO pin at a constant value of  $V_{VCO(start)}$ .

### 7.7 Soft start

The CSS pin voltage is copied to the VCO pin via a buffer. This buffer only has a source capability i.e. it can only charge the VCO pin. This means that the error amplifier output can increase the VCO pin voltage above the CSS voltage level.

At start-up the soft start capacitor is charged to  $V_{VCO(start)}$  setting a start-up frequency of about 80 % of the maximum frequency. After start-up the external soft start capacitor is discharged by  $I_{start(soft)}$ . The VCO pin voltage follows the CSS voltage (discharging takes place via  $R_{\Delta f}$ ) and the frequency sweeps down. The CSS capacitor determines the frequency sweep rate.

When the circuit comes into regulation, the error amplifier output controls the VCO pin voltage and the CSS voltage sweeps down further to zero volt.

### 7.8 VAUX input

The TEA1612T can start up either via a start-up bleeder resistor (connected to the high voltage and V<sub>DD</sub>) or via the VAUX input. In the latter case the internal 10 k $\Omega$  resistor (from VAUX to V<sub>DD</sub>) initiates charging of the V<sub>DD</sub> capacitor after which the series regulator takes over. The series regulator is active up to the moment that V<sub>DD</sub> equals V<sub>DD(reg)</sub>. Further charging to V<sub>DD(startup)</sub> is done via the internal 10 k $\Omega$  resistor.

In oscillation state the start-up resistor is no longer capable of delivering the V<sub>DD</sub> supply current, so an auxiliary supply (for instance, via an auxiliary winding or a dV/dt supply) needs to take over. The VAUX input facilitates a series regulator which regulates its output voltage (=  $V_{DD}$ ) to  $V_{DD(reg)}$ .

### 7.9 Burst mode

In the application the amount of converted power can be estimated from the actual operating frequency: the higher the frequency, the lower the output power. This frequency is proportional to the feedback current to the IRS pin which is measured via a sense resistor  $R_{fb2}$  (see Figure 7). The actual feedback current equals  $1/R_{fb2} \times (V_{BURST} - V_{IRS})$ .

When the voltage at the BURST pin exceeds  $V_{ref(BURST)}$ , the TEA1612T output drivers (GL, GH) are made inactive (i.e. low). The output drivers are enabled again when the voltage at the BURST pin falls below the preset voltage at the HYST pin.

### 7.10 Shut-down

The shut-down input on pin SD has an accurate threshold level of 2.33 V. When the voltage on input SD reaches 2.33 V, the TEA1612T enters shut-down mode.

During shut-down mode,  $V_{DD}$  is clamped by an internal Zener diode at 12.0 V with 1 mA input current. This clamp prevents  $V_{DD}$  rising above the rating of 14 V due to low supply current to the TEA1612T in shut-down mode.

When the TEA1612T is in shut-down mode, it can only be activated again by lowering  $V_{DD}$  to below the  $V_{DD(rst)}$  level (typically 5.3 V) or by making the reset input active. The shut-down latch is then reset and a new start-up cycle can commence.

In shut-down mode the GL pin is high and the GH pin is low. In this way the bootstrap capacitor remains charged so that after a reset a new cycle can start well defined.

### 7.11 Latch reset input

The internal shut-down latch can be reset via the reset input. This input is active low.

### 7.12 Overcurrent protection and timer

The OCP input continuously compares the voltage on pin OCP with  $V_{ref(OCP)}$ . When the OCP pin voltage is higher than  $V_{ref(OCP)}$ , the timer capacitor CT will be charged with  $I_{ch}$  during the next full CF cycle or else the timer capacitor will be discharged with  $I_{leak}$ .

In case the CT voltage exceeds  $V_{trip(H)(CT)}$  the TEA1612T will switch to shut-down mode. The timer capacitor will be discharged with I<sub>dch</sub> until the CT voltage reaches  $V_{trip(L)(CT)}$  after which a soft start cycle is started.

### 7.13 Overtemperature protection

The TEA1612T continuously monitors its temperature. When the temperature exceeds the  $T_{otp(act)}$  level, the TEA1612T will switch to the shut-down mode.

### 7.14 Brownout protection

The brownout protection compares the actual BO pin with the V<sub>trip(bo)</sub> voltage. If the BO voltage (see Figure 7) is lower than V<sub>trip(bo)</sub>, the TEA1612T switches to start-up mode and activates an internal current source I<sub>bo(hys)</sub> to create a brownout hysteresis. When the BO pin voltage becomes larger than V<sub>trip(bo)</sub>, the TEA1612T will start-up again.

### 7.15 PFC disable function

The PFC output pin is an open-drain output. Operation of the PFC pin is internally enabled when the voltage on the BO pin is higher than  $V_{trip(bo)}$ . When the voltage is lower than  $V_{trip(bo)}$ , the PFC output is always in the open-drain state.

The PFC output is pulled low when:

- The overtemperature protection is active.

- The OCP timer has timed out.

- The TEA1612T has been set to shut-down.

- During the off-time in burst mode.

This PFC output signal can be used to switch off the power corrector in the application during Burst mode (and during protection) to further reduce standby power losses.

### 8. Limiting values

| Symbol               | Parameter                        | Conditions               |    | Min    | Max    | Unit |

|----------------------|----------------------------------|--------------------------|----|--------|--------|------|

| Supply Vo            | Itages                           |                          |    |        |        |      |

| V <sub>drv(hs)</sub> | high-side driver voltage         |                          |    | 0      | 600    | V    |

| V <sub>DD</sub>      | supply voltage                   | [                        | 1] | 0      | 14     | V    |

| V <sub>aux</sub>     | auxiliary voltage                | [                        | 1] | 0      | 20     | V    |

| Voltages o           | on pins P, SD, RESET, OCP, BO, I | PFC, BURST, HYS          | T  | and CT |        |      |

| VI                   | input voltage                    |                          |    | 0      | 5      | V    |

| Currents             |                                  |                          |    |        |        |      |

| I <sub>IFS</sub>     | current on pin IFS               |                          |    | -      | 1 ÷ 16 | mA   |

| I <sub>IRS</sub>     | current on pin IRS               |                          |    | -      | 1      | mA   |

| I <sub>VREF</sub>    | current on pin VREF              |                          |    | -      | -2     | mA   |

| Power and            | temperature                      |                          |    |        |        |      |

| P <sub>tot</sub>     | total power dissipation          | T <sub>amb</sub> < 70 °C |    | -      | 0.8    | W    |

| T <sub>amb</sub>     | ambient temperature              | operating                |    | -25    | +70    | °C   |

| T <sub>stg</sub>     | storage temperature              |                          |    | -25    | +150   | °C   |

| Handling             |                                  |                          |    |        |        |      |

| V <sub>ESD</sub>     | electrostatic discharge voltage  | [;                       | 2] | -      | 2000   | V    |

|                      |                                  | [(                       | 3] | -      | 200    | V    |

[1] It is recommended that a 100 nF capacitor be placed as close as possible to the  $V_{DD}$  pin (as indicated in Figure 7, and in the application note).

[2] Human body model class 2: equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

[3] Machine model class 2: equivalent to discharging a 200 pF capacitor through a 0.75  $\mu H$  coil and 10  $\Omega$  resistor.

### 9. Thermal characteristics

| Table 4.             | Thermal characteristics                     |             |     |      |

|----------------------|---------------------------------------------|-------------|-----|------|

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 100 | K/W  |

### **10. Characteristics**

#### Table 5. Characteristics

All voltages are referred to the ground pins which must be connected externally; positive currents flow into the IC;  $V_{DD} = 13 V$  and  $T_{amb} = 25 °C$ ; tested using the circuit shown in Figure 7, unless otherwise specified.

| Symbol                                                                 | Parameter                                                                                                                                  | Conditions                                                                                                                                                              | Min              | Тур              | Мах              | Unit           |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|----------------|

| High volta                                                             | ge pins VDD(FLOAT), GH and                                                                                                                 | SH                                                                                                                                                                      |                  |                  |                  |                |

| I <sub>leak</sub>                                                      | leakage current                                                                                                                            | $V_{DD(float)},~V_{GH}$ and $V_{SH}$ = 600 V                                                                                                                            | -                | -                | 30               | μA             |

| Supply pin                                                             | is V <sub>DD</sub> , VAUX                                                                                                                  |                                                                                                                                                                         |                  |                  |                  |                |

| V <sub>DD(init)</sub>                                                  | initial supply voltage                                                                                                                     | low side on; high side off                                                                                                                                              | -                | 4                | 5                | V              |

| V <sub>DD(startup)</sub>                                               | start-up supply voltage                                                                                                                    |                                                                                                                                                                         | 12.9             | 13.4             | 13.9             | V              |

| V <sub>DD(stop)</sub>                                                  | stop supply voltage                                                                                                                        |                                                                                                                                                                         | 9.0              | 9.4              | 9.8              | V              |

| V <sub>DD(hys)</sub>                                                   | hysteresis of supply voltage                                                                                                               |                                                                                                                                                                         | 3.8              | 4.0              | 4.2              | V              |

| V <sub>DD(reg)</sub>                                                   | regulation supply voltage                                                                                                                  | $V_{aux} = 17 V$                                                                                                                                                        | -                | 12.6             | -                | V              |

| V <sub>DD</sub>                                                        | supply voltage                                                                                                                             | $V_{aux} = 17 \text{ V}, I_{VDD} = 50 \text{ mA},$ oscillation state                                                                                                    | -                | 12.3             | -                | V              |

|                                                                        |                                                                                                                                            | clamp voltage in shut-down state;<br>low side on; high side off;<br>I <sub>DD</sub> = 1 mA                                                                              | 11.0             | 12.0             | 13.0             | V              |

| V <sub>DD(rst)</sub>                                                   | reset supply voltage                                                                                                                       |                                                                                                                                                                         | 4.5              | 5.6              | 6.3              | V              |

| I <sub>DD</sub>                                                        | supply current:                                                                                                                            | low side on; high side off;<br>$C_f = 100 \text{ pF}$ ; $I_{IFS} = 0.5 \text{ mA}$ ;<br>$I_{IRS} = 50 \mu A$ ; low side off;<br>high side off; $V_{DD} = 9 V_{1}^{(1)}$ |                  |                  |                  |                |

|                                                                        |                                                                                                                                            | start-up                                                                                                                                                                | 210              | 260              | 310              | μA             |

|                                                                        |                                                                                                                                            | operating                                                                                                                                                               | -                | 2.0              | -                | mA             |

|                                                                        |                                                                                                                                            | shut-down                                                                                                                                                               | -                | 220              | 270              | μA             |

| Reference                                                              | voltage on pin VREF                                                                                                                        |                                                                                                                                                                         |                  |                  |                  |                |

| V <sub>ref</sub>                                                       | reference voltage                                                                                                                          | $I_{ref} = 0 \text{ mA}$                                                                                                                                                | 2.9              | 3.0              | 3.1              | V              |

| I <sub>ref</sub>                                                       | reference current                                                                                                                          | source only                                                                                                                                                             | -2.0             | -                | -                | mA             |

| Zo                                                                     | output impedance                                                                                                                           | $I_{ref} = -1 \text{ mA}$                                                                                                                                               | -                | 5.0              | -                | Ω              |

| ТС                                                                     | temperature coefficient                                                                                                                    | $I_{ref}$ = 0 mA; $T_j$ = 25 °C to 150 °C                                                                                                                               | -                | -0.3             | -                | mV/ł           |

| Current co                                                             | ontrolled oscillator pins IRS, II                                                                                                          | FS, CF                                                                                                                                                                  |                  |                  |                  |                |

|                                                                        |                                                                                                                                            | I <sub>IBS</sub> = 15 μA; V <sub>CF</sub> = 2 V                                                                                                                         | 28               | 30               | 32               | μA             |

| I <sub>ch</sub> (CF)min                                                | minimum charge current on<br>pin CF                                                                                                        | $\eta_{\rm RS} = 15 \mu$ A, $v_{\rm CF} = 2 v$                                                                                                                          | 20               | 00               | 0-               | •              |

|                                                                        | -                                                                                                                                          | $I_{IRS} = 10 \ \mu A$ ; $V_{CF} = 2 \ V$<br>$I_{IRS} = 200 \ \mu A$ ; $V_{CF} = 2 \ V$                                                                                 | 340              | 380              | 420              | μΑ             |

| I <sub>ch(CF)max</sub>                                                 | pin CF<br>maximum charge current on                                                                                                        |                                                                                                                                                                         |                  |                  |                  | ·              |

| I <sub>ch(CF)max</sub>                                                 | pin CF<br>maximum charge current on<br>pin CF                                                                                              | $I_{IRS} = 200 \ \mu A; V_{CF} = 2 \ V$                                                                                                                                 | 340              | 380              | 420              | μA             |

| Ich(CF)max<br>V <sub>IRS</sub><br>Idch(CF)min                          | pin CF<br>maximum charge current on<br>pin CF<br>voltage on pin IRS<br>minimum discharge current                                           | I <sub>IRS</sub> = 200 μA; V <sub>CF</sub> = 2 V<br>I <sub>IRS</sub> = 200 μA                                                                                           | 340<br>590       | 380<br>620       | 420<br>650       | μA<br>mV       |

| Ich(CF)min<br>Ich(CF)max<br>VIRS<br>Idch(CF)min<br>Idch(CF)max<br>VIFS | pin CF<br>maximum charge current on<br>pin CF<br>voltage on pin IRS<br>minimum discharge current<br>on pin CF<br>maximum discharge current | $I_{IRS} = 200 \ \mu A; V_{CF} = 2 \ V$<br>$I_{IRS} = 200 \ \mu A$<br>$I_{IFS} = 50 \ \mu A \div 16; V_{CF} = 2 \ V$                                                    | 340<br>590<br>47 | 380<br>620<br>50 | 420<br>650<br>53 | μA<br>mV<br>μA |

#### Table 5. Characteristics ...continued

All voltages are referred to the ground pins which must be connected externally; positive currents flow into the IC;  $V_{DD} = 13 V$  and  $T_{amb} = 25 \degree C$ ; tested using the circuit shown in Figure 7, unless otherwise specified.

| Symbol                   | Parameter                                                | Conditions                                                                                                                             | Min     | Тур  | Max  | Unit  |

|--------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|------|------|-------|

| f <sub>bridge(max)</sub> | maximum bridge frequency                                 | $C_{f} = 100 \text{ pF}; I_{IFS} = 1 \text{ mA} \div 16;$                                                                              | [2] 395 | 440  | 485  | kHz   |

| .,                       |                                                          | $I_{IRS} = 200 \ \mu\text{A}; f_{bridge} = f_{OSC} \div 2$                                                                             |         | 4 07 |      |       |

| V <sub>trip(L)</sub>     | LOW-level trip voltage                                   | pin CF; DC level                                                                                                                       | -       | 1.27 | -    | V     |

| V <sub>trip(H)</sub>     | HIGH-level trip voltage                                  | pin CF; DC level                                                                                                                       | -       | 2.97 | -    | V     |

| V <sub>CF(p-p)</sub>     | peak-to-peak voltage on pin<br>CF                        | DC level                                                                                                                               | 1.6     | 1.7  | 1.8  | V     |

| t <sub>no</sub>          | non-overlap time                                         | $\label{eq:cf} \begin{array}{l} C_f = 100 \ p\text{F}; \ I_{IFS} = 0.5 \ m\text{A} \div 16; \\ I_{IRS} = 50 \ \mu\text{A} \end{array}$ | 0.58    | 0.63 | 0.68 | μs    |

| $I_{dch(osc)}/I_{IFS}$   | oscillator discharge current to current on pin IFS ratio | I <sub>IFS</sub> = 0.5 mA ÷ 16;                                                                                                        | 14.4    | 16   | 17.6 | -     |

| Output driv              | rers                                                     |                                                                                                                                        |         |      |      |       |

| I <sub>source(GH)</sub>  | source current on pin GH                                 | high side; $V_{DD(float)} = 11.2 V$ ;<br>$V_{SH} = 0 V$ ; $V_{GH} = 0 V$                                                               | -       | 300  | -    | mA    |

| I <sub>sink(GH)</sub>    | sink current on pin GH                                   | high side; $V_{DD(float)} = 11.2 V$ ;<br>$V_{SH} = 0 V$ ; $V_{GH} = 11.2 V$                                                            | -       | 480  | -    | mA    |

| Isource(GL)              | source current on pin GL                                 | low side; V <sub>GL</sub> = 0 V                                                                                                        | -       | 300  | -    | mA    |

| I <sub>sink(GL)</sub>    | sink current on pin GL                                   | low side; V <sub>GL</sub> = 13 V                                                                                                       | -       | 580  | -    | mA    |

| V <sub>OH</sub>          | HIGH-level output voltage                                | pin GH; high side;<br>$V_{DD(float)} = 11.2 V; V_{SH} = 0 V;$<br>$I_{GH} = 10 mA$                                                      | -       | 10.9 | -    | V     |

|                          |                                                          | pin GL; low side; l <sub>GL</sub> = 10 mA                                                                                              | -       | 12.6 | -    | V     |

| V <sub>OL</sub>          | LOW-level output voltage                                 | pin GH; high side;<br>V <sub>DD(float)</sub> = 11.2 V; V <sub>SH</sub> = 0 V;<br>I <sub>GH</sub> = 10 mA                               | -       | 0.17 | -    | V     |

|                          |                                                          | pin GL; low side; l <sub>GL</sub> = 10 mA                                                                                              | -       | 0.18 | -    | V     |

| V <sub>Fd(bs)</sub>      | bootstrap diode forward voltage                          | $I_{O} = 5 \text{ mA}$                                                                                                                 | 1.3     | 1.6  | 1.9  | V     |

| Shut-down                | input pin SD                                             |                                                                                                                                        |         |      |      |       |

| l <sub>l</sub>           | input current                                            | V <sub>SD</sub> = 2.33 V                                                                                                               | -       | -    | 0.5  | μA    |

| V <sub>th(SD)</sub>      | threshold voltage on pin SD                              |                                                                                                                                        | 2.26    | 2.33 | 2.40 | V     |

| Error ampli              | fier pins P, VCO                                         |                                                                                                                                        |         |      |      |       |

| I <sub>I(cm)</sub>       | common-mode input current                                | $V_{I(cm)} = 1 V$                                                                                                                      | -       | -0.1 | -0.5 | μA    |

| V <sub>I(cm)</sub>       | common-mode input voltage                                |                                                                                                                                        | -       | -    | 2.5  | V     |

| V <sub>I(offset)</sub>   | offset input voltage                                     | $V_{I(cm)} = 1 V; I_{VCO} = -10 mA$                                                                                                    | -2      | 0    | +2   | mV    |

| 9 <sub>m</sub>           | transconductance                                         | $V_{I(cm)} = 1$ V; source only                                                                                                         | -       | 330  | -    | μA/mV |

| G <sub>ol</sub>          | open-loop gain                                           | $R_L = 10 \text{ k}\Omega \text{ to GND}; V_{I(cm)} = 1 \text{ V}$                                                                     | -       | 70   | -    | dB    |

| GB                       | gain bandwidth product                                   | $R_L = 10 \text{ k}\Omega \text{ to GND}; V_{I(cm)} = 1 \text{ V}$                                                                     | -       | 5    | -    | MHz   |

| V <sub>VCO(max)</sub>    | maximum VCO voltage                                      | operating; $R_L = 10 \text{ k}\Omega$ to GND                                                                                           | 3.2     | 3.6  | 4.0  | V     |

| I <sub>VCO(max)</sub>    | maximum VCO current                                      | operating; $V_{VCO} = 1 V$                                                                                                             | -0.4    | -0.5 | -0.6 | mA    |

| V <sub>VCO(start)</sub>  | start VCO voltage                                        | $I_{VCO} = 0.3 \text{ mA}$                                                                                                             | 2.5     | 2.7  | 2.9  | V     |

#### Table 5. Characteristics ...continued

All voltages are referred to the ground pins which must be connected externally; positive currents flow into the IC;  $V_{DD} = 13 V$  and  $T_{amb} = 25 °C$ ; tested using the circuit shown in Figure 7, unless otherwise specified.

| Symbol                            | Parameter                                         | Conditions              | Min  | Тур  | Max  | Unit |

|-----------------------------------|---------------------------------------------------|-------------------------|------|------|------|------|

| Reset pin                         |                                                   |                         |      |      |      |      |

| V <sub>rst</sub>                  | reset voltage                                     |                         | 2.15 | 2.4  | 2.65 | V    |

| V <sub>rst(hys)</sub>             | hysteresis of reset voltage                       |                         | -    | 0.65 | -    | V    |

| I <sub>I(rst)</sub>               | reset input current                               |                         | -    | -    | 1    | μA   |

| CSS pin                           |                                                   |                         |      |      |      |      |

| Istart(soft)                      | soft start current                                |                         | 12   | 15   | 18   | μA   |

| CT pin                            |                                                   |                         |      |      |      |      |

| I <sub>ch</sub>                   | charge current                                    |                         | 21   | 27   | 33   | μA   |

| I <sub>dch</sub>                  | discharge current                                 |                         | 8    | 10   | 12   | μA   |

| l <sub>leak</sub>                 | leakage current                                   |                         | 0.1  | 0.3  | 1    | μA   |

| I <sub>ch</sub> /I <sub>dch</sub> | charge current to discharge<br>current ratio      |                         | 2.4  | 2.7  | 3.0  | μA   |

| V <sub>trip(H)(CT)</sub>          | HIGH-level trip voltage on<br>pin CT              |                         | 2.7  | 3    | 3.3  | V    |

| V <sub>trip(L)(CT)</sub>          | LOW-level trip voltage on pin<br>CT               |                         | 0.6  | 0.7  | 0.8  | V    |

| OCP pin                           |                                                   |                         |      |      |      |      |

| V <sub>ref(OCP)</sub>             | reference voltage on pin<br>OCP                   |                         | 280  | 305  | 330  | mV   |

| ОТР                               |                                                   |                         |      |      |      |      |

| T <sub>otp(act)</sub>             | activation overtemperature protection temperature |                         | 120  | 135  | 150  | °C   |

| BO pin                            |                                                   |                         |      |      |      |      |

| V <sub>trip(bo)</sub>             | brownout trip voltage                             |                         | 1.19 | 1.25 | 1.31 | V    |

| I <sub>bo(hys)</sub>              | hysteresis of brownout<br>current                 |                         | 14   | 16   | 18   | μA   |

| BURST pin                         |                                                   |                         |      |      |      |      |

| V <sub>ref(BURST)</sub>           | reference voltage on pin<br>BURST                 |                         | 1.75 | 1.8  | 1.85 | V    |

| PFC pin                           |                                                   |                         |      |      |      |      |

| I <sub>leak</sub>                 | leakage current                                   | $V_{PFC} = 1 V$         | -    | -    | 1    | μA   |

| V <sub>sat</sub>                  | saturation voltage                                | I <sub>PFC</sub> = 1 mA | -    | -    | 0.2  | V    |

| HYST pin                          |                                                   |                         |      |      |      |      |

| I <sub>leak</sub>                 | leakage current                                   | V <sub>HYST</sub> = 5 V | -    | -    | 1    | μA   |

[1] The supply current I<sub>DD</sub> increases with the increasing bridge frequency to drive the capacitive load of two MOSFETs. Typical MOSFETs for the TEA1612T application are 8N50 (NXP type PHX80N50E,  $Q_{G(tot)} = 55 \text{ nC}$  (typ) and these will increase the supply current at 150 kHz according to the following formula:  $\Delta I_{DD} = 2 \times Q_{G(tot)} \times f_{bridge} = 2 \times 55nC \times 150kHz = 16.5mA$

[2] The frequency of the oscillator depends on the value of capacitor  $C_f$ , the peak-to-peak voltage swing  $V_{CF}$  and the charge/discharge currents  $I_{ch(CF)}$  and  $I_{dch(CF)}$ .

## **TEA1612T**

Zero voltage switching resonant converter controller

### **11. Application information**

### **NXP Semiconductors**

## **TEA1612T**

Zero voltage switching resonant converter controller

### 12. Package outline

#### Fig 8. Package outline SOT137-1 (SO24)

### 13. Revision history

| Table 6. | Revision history |              |                    |               |            |  |

|----------|------------------|--------------|--------------------|---------------|------------|--|

| Document | : ID             | Release date | Data sheet status  | Change notice | Supersedes |  |

| TEA1612T | _1               | 20090924     | Product data sheet | -             | -          |  |

### 14. Legal information

### 14.1 Data sheet status

| Document status <sup>[1][2]</sup> | Product status <sup>[3]</sup> | Definition                                                                            |

|-----------------------------------|-------------------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet      | Development                   | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet    | Qualification                 | This document contains data from the preliminary specification.                       |

| Product [short] data sheet        | Production                    | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

### 14.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 14.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

### 14.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### **15. Contact information**

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

### **NXP Semiconductors**

## **TEA1612T**

#### Zero voltage switching resonant converter controller

### 16. Contents

| 1          | General description              | . 1 |

|------------|----------------------------------|-----|

| 2          | Features                         | . 1 |

| 3          | Applications                     | . 2 |

| 4          | Ordering information             |     |

| 5          | Block diagram                    | . 3 |

| 6          | Pinning information              | . 4 |

| 6.1        | Pinning                          |     |

| 6.2        | Pin description                  | . 4 |

| 7          | Functional description           | . 5 |

| 7.1        | Start-up                         | . 5 |

| 7.2        | Oscillator                       | -   |

| 7.3        | Non-overlap time resistor        |     |

| 7.4        | Minimum frequency resistor       |     |

| 7.5        |                                  |     |

| 7.6        | Error amplifier                  |     |

| 7.7<br>7.8 | Soft start                       |     |

| 7.0<br>7.9 | VAUX input                       |     |

| 7.10       | Shut-down.                       | -   |

| 7.11       | Latch reset input.               |     |

| 7.12       | Overcurrent protection and timer | 10  |

| 7.13       | Overtemperature protection       | 10  |

| 7.14       | Brownout protection              | 10  |

| 7.15       | PFC disable function             | 10  |

| 8          | Limiting values                  | 11  |

| 9          | Thermal characteristics.         | 11  |

| 10         | Characteristics                  | 12  |

| 11         | Application information.         | 15  |

| 12         | Package outline                  | 16  |

| 13         | Revision history                 | 17  |

| 14         | Legal information                | 18  |

| 14.1       | Data sheet status                | 18  |

| 14.2       | Definitions                      | 18  |

| 14.3       | Disclaimers                      | 18  |

| 14.4       | Trademarks                       | 18  |

| 15         | Contact information              | 18  |

| 16         | Contents                         | 19  |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

#### © NXP B.V. 2009.

#### All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 24 September 2009 Document identifier: TEA1612T\_1