Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **TEA18361LT**

## **GreenChip SMPS control IC**

Rev. 2 — 12 December 2013

**Product data sheet**

## 1. General description

The TEA18361LT is a controller IC for low-cost Switched Mode Power Supplies (SMPS). It is intended for flyback topologies. The built-in green functions provide high efficiency at all power levels.

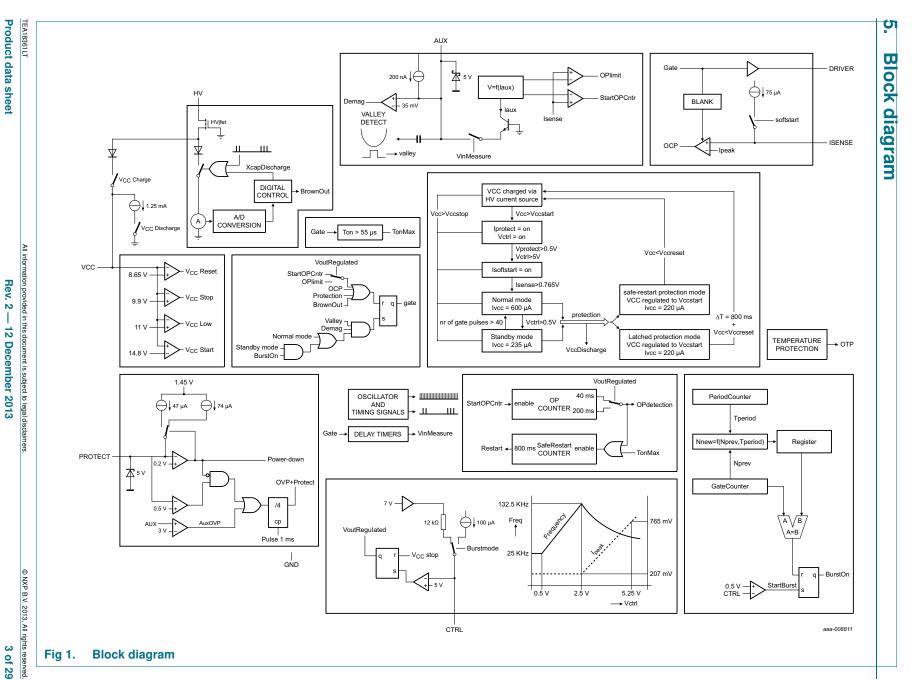

At high power levels the flyback operates in Quasi-Resonant (QR) mode. At lower power levels, the controller switches to Frequency Reduction (FR) or Discontinuous Conduction Mode (DCM) and limits the peak current to approximately 25 % of the maximum peak current. Valley switching is used in all operating modes.

At low power levels, when the flyback switching frequency drops below 25 kHz, the flyback converter switches to burst mode. A special burst mode has been integrated which reduces the opto current to a minimum level, ensuring high efficiency at low power and excellent no load power performance. As the switching frequency in this mode has a minimum value of 25 kHz while the burst frequency is below 800 Hz, the frequencies are outside the audible range. During the non-switching phase of the burst mode, the internal IC supply current is minimized for further efficiency optimization.

The TEA18361LT includes an accurate OverPower Protection (OPP). The OPP enables the controller to operate in overpower situations for a limited amount of time. If the output is shorted, the system switches to low-power mode where the output power is limited to a lower level.

The TEA18361LT is manufactured in a high-voltage Silicon-On-Insulator (SOI) process. The SOI process combines the advantages of a low-voltage process (accuracy, high-speed protection, functions, and control), while maintaining the high-voltage capabilities (high-voltage start-up, low standby power, and an integrated X-capacitor discharge function).

The TEA18361LT enables low-cost, highly efficient and reliable supplies for power requirements up to 75 W to be designed with a minimum number of external components.

All values mentioned in this data sheet are typical values, unless otherwise specified.

### 2. Features and benefits

#### 2.1 General features

- SMPS controller IC for low-cost applications

- Large supply voltage range (up to 30 V)

- Integrated high-voltage start-up

- Continuous VCC regulation during start-up and protection via the HV pin, allowing a minimum VCC capacitor value

- Reduced opto current in burst mode enabling low no load power consumption

- Operating frequencies in all operating modes are outside the audible area

- Integrated X-capacitor discharge; NXP Semiconductors patented (Patent reference: 81512184EP01 (Patent pending))

- Adjustable soft start

- Power-down mode via the PROTECT pin

#### 2.2 Green features

- Low supply current during normal operation (0.6 mA without load)

- Low supply current during non-switching state in burst mode (0.2 mA)

- Valley switching for minimum switching losses

- Frequency reduction with fixed minimum peak current to maintain high efficiency at low output power levels

#### 2.3 Protection features

- Mains voltage independent OverPower Protection (OPP)

- OverTemperature Protection (OTP)

- Integrated overpower time-out

- Integrated restart timer for system fault conditions

- Continuous mode protection using demagnetization detection

- Accurate OverVoltage Protection (OVP)

- General-purpose input for latched protection; for use with system OverTemperature Protection (OTP)

- Driver maximum on-time protection

# 3. Applications

Applications requiring efficient and cost-effective power supply solutions up to 75 W

# 4. Ordering information

Table 1. Ordering information

| Type number  | Package |                                                            |          |  |  |

|--------------|---------|------------------------------------------------------------|----------|--|--|

|              | Name    | Description                                                | Version  |  |  |

| TEA18361LT/1 | SO14    | plastic small outline package; 14 leads; body width 3.9 mm | SOT108-1 |  |  |

TEA18361LT

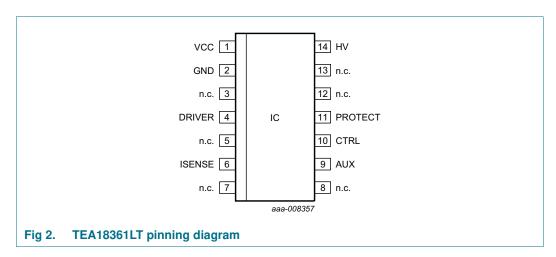

# 6. Pinning information

## 6.1 Pinning

# 6.2 Pin description

Table 2. Pin descriptions

| Pin     | Pin number | Description                                                                                      |

|---------|------------|--------------------------------------------------------------------------------------------------|

| VCC     | 1          | supply voltage                                                                                   |

| GND     | 2          | ground                                                                                           |

| n.c.    | 3          | not connected                                                                                    |

| DRIVER  | 4          | gate driver output                                                                               |

| n.c.    | 5          | not connected                                                                                    |

| ISENSE  | 6          | current sense input                                                                              |

| n.c     | 7          | not connected                                                                                    |

| n.c.    | 8          | not connected                                                                                    |

| AUX     | 9          | auxiliary winding input for demagnetization timing, valley detect, overpower correction, and OVP |

| CTRL    | 10         | control input                                                                                    |

| PROTECT | 11         | general purpose protection input; pin for power-down mode                                        |

| n.c.    | 12         | high-voltage safety spacer; not connected                                                        |

| n.c.    | 13         | high-voltage safety spacer; not connected                                                        |

| HV      | 14         | high voltage start-up; active X-capacitor discharge                                              |

## 7. Functional description

#### 7.1 General control

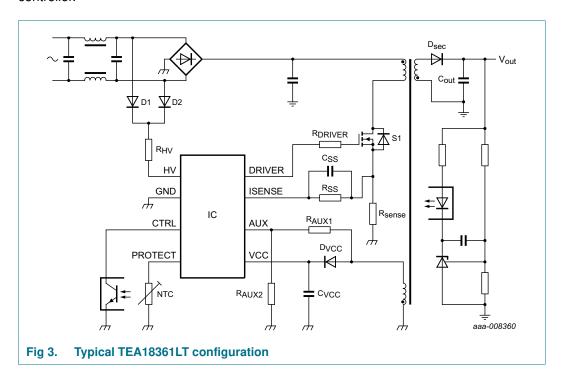

<u>Figure 3</u> shows a typical configuration of the TEA18361LT, including flyback circuit controller.

### 7.1.1 Start-up and UnderVoltage LockOut (UVLO)

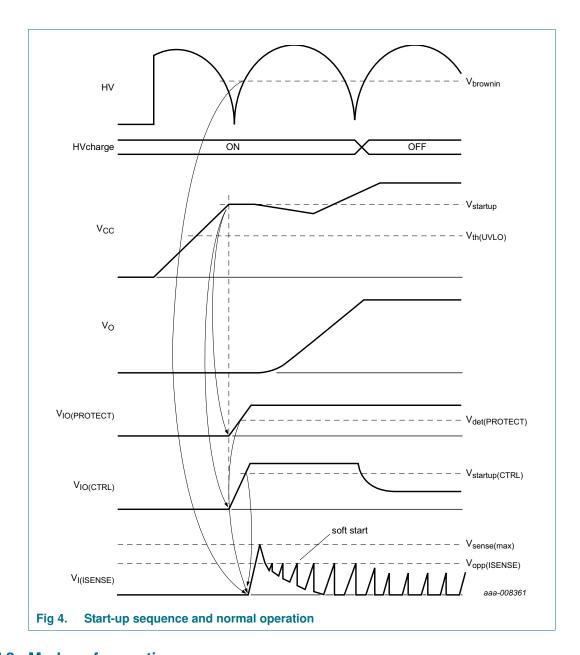

Initially, the capacitor on the VCC pin is charged from the high-voltage mains using the HV pin. As long as  $V_{CC}$  is below  $V_{startup}$ , the IC current consumption is minimized to 40  $\mu$ A.

When  $V_{CC}$  reaches the  $V_{startup}$  level, the control logic activates the internal circuitry. The IC then waits for the PROTECT pin to reach  $V_{det(PROTECT)} + V_{det(hys)PROTECT}$ , the CTRL pin to reach  $V_{startup(CTRL)}$ , and the mains voltage to increase to above the brownin level. When all these conditions are met, the soft start capacitor on the ISENSE pin ( $C_{SS}$  in Figure 3) is charged. The system starts switching. In a typical application, the supply voltage is taken over by the auxiliary winding of the transformer.

During the start-up period, the VCC pin is continuously regulated to the  $V_{startup}$  level using the HV charge current until the output voltage is at its regulation level, which is detected via the CTRL pin. In this way the VCC capacitor value can be limited. Due to the limited current capability from the HV pin and depending on the mains voltage, the voltage on pin VCC can still drop slightly during the start-up period.

## 7.2 Modes of operation

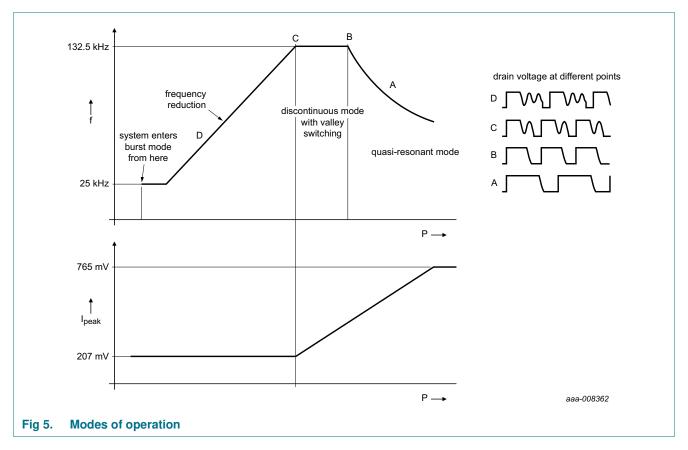

The TEA18361LT operates in quasi-resonant mode, discontinuous conduction mode or burst mode (see <u>Figure 5</u>). The auxiliary winding of the flyback transformer provides demagnetization and valley detection.

At high output power the converter operates in quasi-resonant mode. The next converter cycle starts after demagnetization of the transformer and detection of the valley. In quasi-resonant mode switching losses are minimized because the external MOSFET is switched on while the drain-source voltage is minimal.

To prevent high-frequency operation at lower loads, the quasi-resonant operation switches to Discontinuous Conduction Mode (DCM) operation with valley skipping once the frequency reaches its maximum. This frequency limit reduces the MOSFET switch-on losses and conducted EMI.

At medium power levels, the controller enters Frequency Reduction (FR) mode. A Voltage Controlled Oscillator (VCO) controls the frequency. The minimum frequency in this mode is reduced to 25 kHz. During FR mode, the primary peak current is kept at an adjustable minimum level to maintain high efficiency. Valley switching is also active in this mode.

At low power, the converter enters the burst mode. In burst mode, the minimum switching frequency is 25 kHz.

## 7.3 Supply management

All internal reference voltages are derived from a temperature compensated on-chip band gap circuit. Internal reference currents are derived from a trimmed and temperature-compensated current reference circuit.

### 7.4 Mains voltage measuring

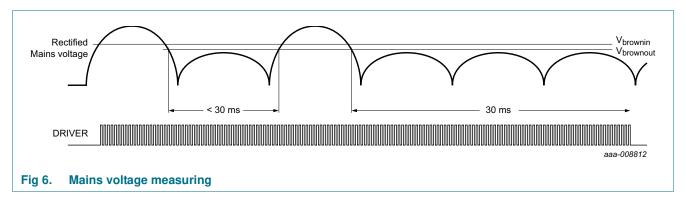

In a typical application, the mains input voltage is measured using the HV pin. Once per ms the mains voltage is measured by pulling down the HV pin to ground and measuring its current. This current then reflects the input voltage.

The system determines if the mains voltage exceeds the brownin level or it is disconnected using an analog-to-digital converter and digital control (see Figure 1).

Once the mains is above the brownin level, the system is allowed to start switching (see Figure 6).

If the mains voltage is continuously below the brownout level for a period of at least 30 ms, a brownout is detected and the system immediately stops switching. This period is required to avoid that the system stops switching due to the zero crossings of the mains or during a short mains interruption.

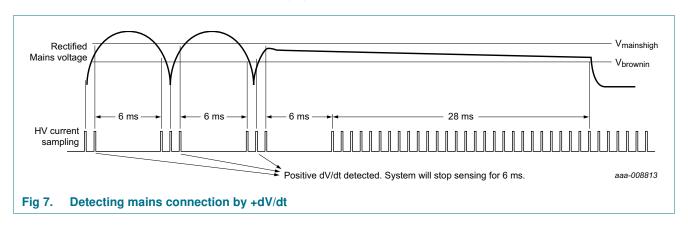

When the mains voltage is measured by pulling the HV pin to ground, the digital control calculates if there is a positive dV/dt at the mains. A positive dV/dt implies that a mains is connected.

Once a mains is detected, the measuring of the mains input voltage is stopped for a period of 6 ms to improve efficiency. In burst mode this waiting period is enlarged to 97 ms to improve efficiency.

A positive dV/dt is measured when succeeding samples cross the brownin level  $(I_{bi(HV)})$  or the mains high level  $(I_{IH(HV)})$ ; see Figure 7).

If the system does not detect a positive dV/dt for 28 ms, it assumes that the mains is disconnected. In that case the HV pin is continuously pulled to ground, discharging the external X-capacitor.

### 7.5 Auxiliary winding

The VCC pin is connected via a diode and a capacitor to the auxiliary winding to efficiently supply the control IC.

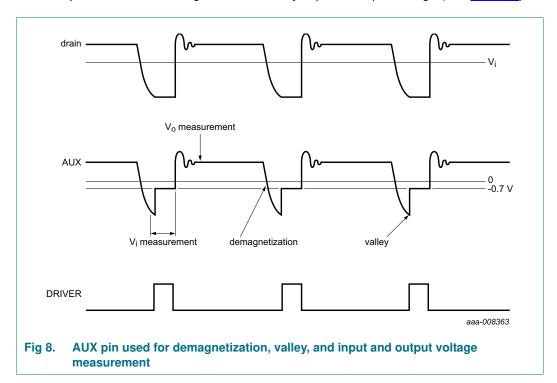

To detect demagnetization, valley, and input and output voltage, the auxiliary winding is connected to the AUX pin via a resistive divider (see <u>Figure 3</u>). Each switching cycle is divided in sections. During each section the system knows if the voltage or current out of the AUX pin reflects the demagnetization, valley, input or output voltage (see <u>Figure 8</u>).

When the external MOSFET is switched on, the voltage at the auxiliary winding reflects the input voltage. The AUX pin is clamped to -0.7 V. The output current is a measure of the input voltage. This current value is internally used for an accurate OPP.

The demagnetization, valley and output voltages are measured as a voltage on the AUX pin. In this way, the input voltage measurement and OVP can be adjusted independently.

#### 7.6 Protection

If a protection is triggered, the controller stops switching. Depending on the protection triggered and the IC version, the protection causes a restart or latches the converter to an off state (See <u>Table 3</u>).

To avoid false triggering, some protections have a built-in delay.

Table 3. Protections

| Protection              | Delay              | Action                                                  | V <sub>CC</sub> regulated |

|-------------------------|--------------------|---------------------------------------------------------|---------------------------|

| AUX open                | no                 | wait until AUX is connected                             | no                        |

| brownout                | 30 ms              | wait until<br>V <sub>mains</sub> > V <sub>brownin</sub> | yes                       |

| maximum on-time         | no                 | safe restart 800 ms                                     | yes                       |

| OTP internal            | no                 | latch                                                   | yes                       |

| OTP via the PROTECT pin | 2 ms to 4 ms       | latch                                                   | yes                       |

| OVP via the AUX pin     | 4 driver pulses[1] | latch                                                   | yes                       |

| overpower compensation  | no                 | via AUX;<br>cycle-by-cycle                              | -                         |

| overpower time-out      | 40 ms or 200 ms    | latch                                                   | yes                       |

| overpower + UVLO        | no                 | latch                                                   | yes                       |

| overcurrent protection  | blanking time      | cycle-by-cycle                                          | no                        |

| UVLO                    | no                 | Wait until V <sub>CC</sub> > V <sub>startup</sub>       | yes                       |

|                         |                    |                                                         |                           |

<sup>[1]</sup> When the voltage on the PROTECT pin is between V<sub>th(pd)PROTECT</sub> and V<sub>det(PROTECT)</sub>, the clock of the delay counter is changed from the driver pulse to 1 ms internal pulse.

When the system stops switching, the VCC pin is not supplied via the auxiliary winding anymore. Depending on the protection triggered, the VCC is regulated to  $V_{\text{startup}}$  via the HV pin (see Table 3).

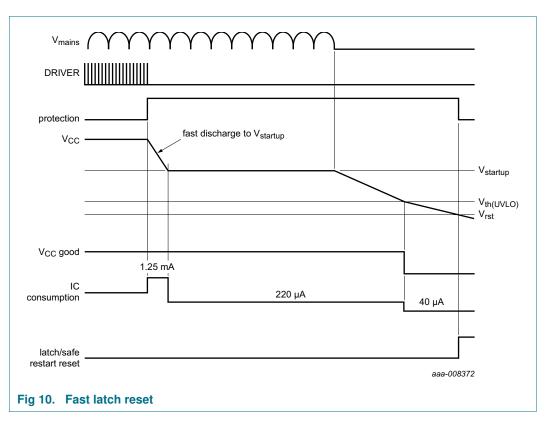

Releasing the latched protections or shortening the safe restart timer can be achieved by removing or shorting the mains voltage. This is called a fast latch reset. It is mainly used to shorten the test time in production (See Section 7.6.8).

### 7.6.1 OverPower Protection (OPP)

The overpower function is used to realize a maximum output power which is nearly constant over the full input mains.

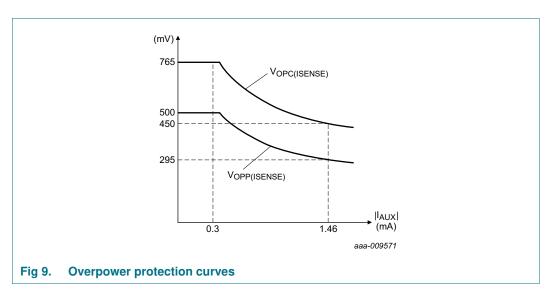

The overpower compensation circuit measures the input voltage via the AUX pin and outputs two reference voltages (see Figure 1). If the measured voltage at the ISENSE pin exceeds the highest reference voltage ( $V_{opc(ISENSE)}$ ) the DRIVER output is pulled low. If the measured ISENSE voltage exceeds the lower reference voltage ( $V_{opp(ISENSE)}$ ), the OverPower counter starts. Both reference voltages depend on the measured input voltage. In this way the system allows 150 % overpower over the rated power on a cycle-by-cycle base. 100 % overpower triggers the overpower counter of 200 ms. Figure 9 shows the overpower protection curves.

During system start-up, the maximum overpower is limited to 100 % and the maximum time-out period is lowered to 40 ms. Once the output voltage is within its regulation level (voltage on the CTRL pin is below 5 V), the maximum overpower is switched to 150 % and the maximum time-out period returns to 200 ms limiting the output power to a minimum at a shorted output. Lowering the maximum output power and shortening the overpower timer ensure that the input power of the system is limited to < 5 W at a shorted output.

Due to the limited output power, the output voltage drops if the load requires more than 150 %. As a result, the  $V_{CC}$  voltage drops as well and UVLO can be triggered. To retain the same response in an overpower situation (whether UVLO is triggered or not) the system enters the protection mode (latch or safe restart) when overpower + UVLO is detected. The system entering the protection mode does not depend on the value of the OP counter.

## 7.6.2 OverVoltage Protection (OVP)

An accurate output OVP is implemented by measuring the voltage at the AUX pin during the secondary stroke. As the auxiliary winding voltage is a well-defined replica of the output voltage, the OVP level can be adjusted by the external resistor divider ratio  $R_{AUX2} / (R_{AUX1} + R_{AUX2})$ .

An internal counter of 4 gate pulses prevents false OVP detection which can occur during ESD or lightning events.

### 7.6.3 Protection input (PROTECT pin)

The PROTECT pin is a general purpose input pin. It can be used to switch off the converter (latched protection). The converter is stopped when the voltage on this pin is pulled below  $V_{\text{det}(PROTECT)}$  (0.5 V).

The PROTECT pin can be used to create an OTP function by connecting a Negative Temperature Coefficient (NTC) resistor to this pin. A voltage on the PROTECT pin lower than 0.5 V detects overtemperature. The PROTECT current (maximum 74  $\mu$ A) flowing through the external NTC resistor creates the voltage. The PROTECT voltage is clamped

to maximum 1.45 V. At room temperature the resistance value of the NTC resistor is much higher than at high temperature. Due to the clamp, the current out of the PROTECT pin is 1.45 V divided by the resistance, which is significantly lower than 74  $\mu$ A.

A filter capacitor can be connected to this pin.

To avoid false triggering, an internal filter of 2 ms to 4 ms is applied.

The PROTECT pin can also be a power-down mode pin (see Section 7.10).

#### 7.6.4 OverTemperature Protection (OTP)

Integrated OTP ensures that the IC stops switching if the junction temperature exceeds the thermal temperature shutdown limit. OTP is a latched protection.

#### 7.6.5 Maximum on-time

The controller limits the on-time of the external MOSFET to 55  $\mu s$ . When the on-time is longer, the IC stops switching and enters safe restart mode.

#### 7.6.6 Safe restart

If a protection is triggered and the system enters the safe restart mode, the system restarts after 800 ms. Because the system is not switching, the VCC pin is supplied from the mains via the HV pin.

After the 800 ms, the control IC measures the mains voltage. if the mains voltage exceeds the brownin level, the control IC activates the PROTECT pin current source and the internal voltage sources connected to the CTRL pin. Once the voltages on these pins reach a minimum level, the soft start capacitor on the ISENSE pin is charged and the system starts switching again.

The  $V_{CC}$  is continuously regulated to the  $V_{startup}$  level until the output voltage is within the regulation level again.

#### 7.6.7 Latched protection

If a protection is triggered and the system enters the latched protection mode, the  $V_{CC}$  is continuously regulated to the  $V_{startup}$  level via the HV current source. As long as the AC voltage remains, the system does not switch.

Removing the mains for a short time is the only possibility to restart the system.

#### 7.6.8 Fast latch reset

Fast latch reset is a simple and fast method to reset the system when it is in latched protection mode or safe restart mode. This function is used during production testing.

When the latched protection mode or safe restart mode is triggered, the voltage on pin VCC is fast discharged by an internal current source ( $I_{CC(dch)}$ ); see <u>Figure 10</u>). The fast discharge avoids an additional waiting period if the VCC voltage is high. When shorting the mains, the waiting period is only the time of the discharge from  $V_{startup}$  to  $V_{rst}$ .

Using a 10  $\mu$ F VCC capacitor, the fast latch reset time is below 0.6 s. If the mains is not shorted but removed, a discharged of the X-cap can cause an additional waiting time.

### 7.7 Burst mode operation (CTRL pin)

The controller enters the burst mode when a low output power causes the voltage on the CTRL pin to drop below 0.5 V.

During normal operation, the primary opto current can be calculated with Equation 1:

$$I_{opto} = \frac{(7 \ V - V_{IO(CTRL)})}{12 \ k\Omega} \tag{1}$$

This implies that without any additional measure, the maximum primary opto current in burst mode is:

$$I_{opto} = \frac{(7 \ V - 0 \ V)}{12 \ k\Omega} = 583 \ \mu A \tag{2}$$

Depending on the optocoupler used , the secondary opto current is even higher.

To achieve minimum no load input power, the internal voltage (7 V) is regulated to a value that causes the primary opto current value to be 100  $\mu$ A when the system is in burst mode. The secondary opto current is then automatically also within this lower range. If the IC detects that the opto current is lower than 80  $\mu$ A, the internal voltage is increased faster to achieve a small output voltage undershoot at a positive load step. Once the system enters normal operation mode, the internal voltage is slowly increased to 7 V again.

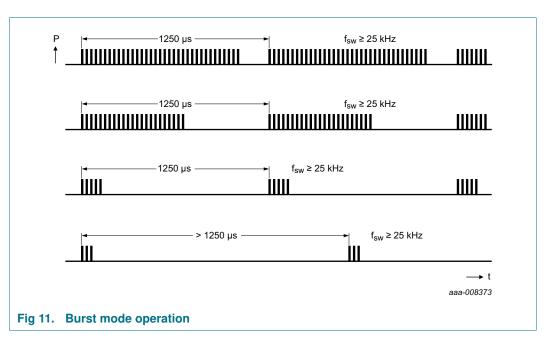

To avoid audible noise, a special digital burst mode is implemented. The minimum switching frequency in this mode is 25 kHz. The burst mode repetition rate has a target frequency of 800 Hz (1250 µs; see Figure 11).

The amount of pulses at each burst period is defined by the requested output power. At higher output power, the amount of switching pulses increases. At low load, it decreases.

The digital circuit defines the amount of burst cycles so that the burst frequency is below the audible range (800 Hz) and the switching frequency exceeds the audible range (25 kHz). Any audible noise is avoided.

The minimum amount of switching cycles is set to 3 to ensure good efficiency at very low loads. To regulate the output power at a very low load, the system increases the burst period (< 800 Hz). The increased burst period is still outside the audible range.

To further improve the no load input power and efficiency at low loads, the current consumption of the IC is lowered to 235  $\mu$ A during the non-switching period in the burst mode.

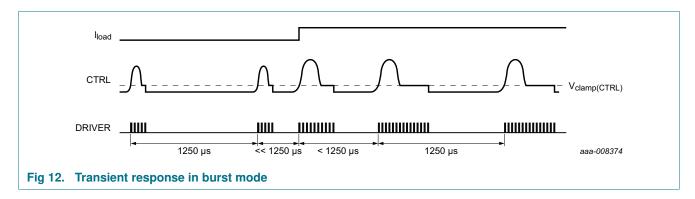

To achieve a good transient response in burst mode, the system starts switching immediately at an increased output load, allowing a shorter burst period. Eventually, it regulates to the required burst period by increasing the amount of driver pulses (see Figure 12).

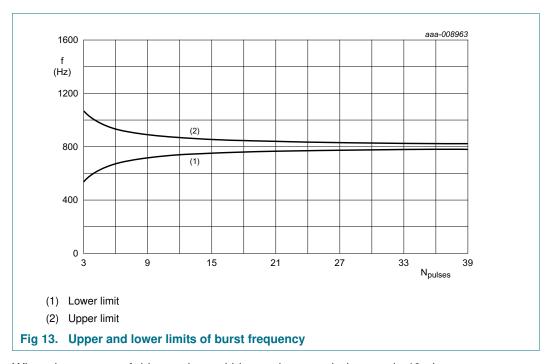

Due to the discrete number of switching cycles, the new calculated number of pulses must be 0.5 higher or lower than the existing number before one switching cycle is added or taken away. For the IC to increase or decrease the amount of switching cycles, a certain deviation from the target burst repetition frequency (800 Hz) is required because of the internal algorithm. This deviation becomes smaller when the amount of switching cycles increases. Figure 13 shows the upper and lower limits of the burst repetition frequency as a function of the number of pulses.

When the amount of driver pulses within one burst period exceeds 40, the system switches to normal mode again.

During the burst period, the voltage on the CTRL pin is clamped to the minimum  $V_{\text{clamp}(\text{CTRL})}$ . The current out of the CTRL pin is measured. If the current exceeds  $I_{\text{stop}(\text{CTRL})}$ , the burst period is terminated regardless of digital control. This feature ensures a small overshoot at the output voltage when the load in burst mode suddenly reduces.

At the end of each burst period, the CTRL pin is pulled to the ground level for 12.5  $\mu$ s, unless the current flowing from pin CTRL < 87  $\mu$ A, which usually occurs at a positive load step.

## 7.8 Soft start-up (ISENSE pin)

To prevent audible noise during start-up or a restart condition, a soft start feature is implemented. Before the converter starts, the soft start capacitor  $C_{SS}$  on the ISENSE pin is charged. When the converter starts switching, the primary peak current slowly increases as the soft start capacitor discharges through the soft start resistor  $R_{SS}$  (see Figure 3).

The soft start time constant is set by the external soft start capacitor and the parallel resistor values.

### 7.9 Driver (DRIVER pin)

The driver circuit to the gate of the power MOSFET has a current sourcing capability of 300 mA and a current sink capability of 750 mA. These capabilities allow a fast turn-on and turn-off of the power MOSFET for efficient operation.

The maximum driver output is limited to 10.5 V. The DRIVER output pin can be connected to the gate of a MOSFET directly or via a resistor.

#### 7.10 Power-down mode

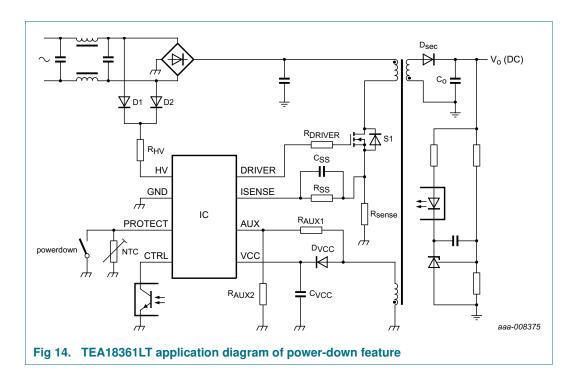

To achieve extremely low no-load standby power, the IC can be forced to power-down mode using an external signal on the PROTECT pin (see Figure 14).

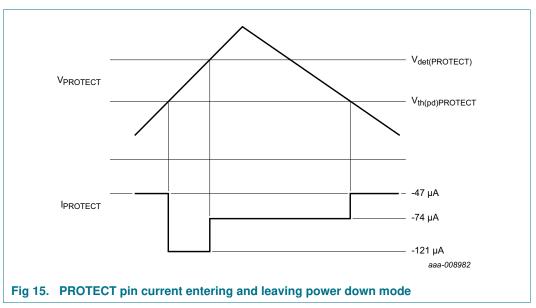

When the voltage on the PROTECT pin is pulled below  $V_{th(pd)PROTECT}$ , the system enters the power-down mode. The voltage on the CTRL pin is lowered to 0 V. The IC automatically runs in burst mode with the voltage on pin VCC regulated at the  $V_{restart}$  level. The primary and secondary opto current is saved. The current out of the PROTECT pin is reduced from 74  $\mu$ A to 47  $\mu$ A to save current consumption (See Figure 15).

To avoid that the latched protection is accidentally triggered when the system enters or comes out of the power-down mode, the latched protection is blocked when the voltage on the PROTECT pin is lower than  $V_{th(pd)PROTECT}$ .

# 8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol                   | Parameter                              | Conditions                |     | Min        | Max   | Unit |

|--------------------------|----------------------------------------|---------------------------|-----|------------|-------|------|

| Voltages                 |                                        |                           |     |            |       |      |

| $V_{IO(HV)}$             | input/output voltage on pin<br>HV      |                           |     | -0.4       | +700  | V    |

| V <sub>CC</sub>          | supply voltage                         | continuous                |     | -0.4       | +30   | V    |

|                          |                                        | t < 100 ms                |     | -          | +35   | V    |

| $V_{IO(CTRL)}$           | input/output voltage on pin CTRL       |                           |     | -0.4       | +12   | V    |

| V <sub>I(ISENSE)</sub>   | input voltage on pin<br>ISENSE         |                           |     | -0.4       | +12   | V    |

| V <sub>IO(PROTECT)</sub> | input/output voltage on pin<br>PROTECT | current limited           |     | -0.4       | +5    | V    |

| $V_{IO(AUX)}$            | input/output voltage on pin<br>AUX     | current limited           |     | <b>-5</b>  | +5    | V    |

| V <sub>O(DRIVER)</sub>   | output voltage on pin<br>DRIVER        |                           |     | -0.4       | +12   | V    |

| Currents                 |                                        |                           |     |            |       |      |

| I <sub>IO(AUX)</sub>     | input/output current on pin<br>AUX     |                           |     | -1.5       | +1    | mA   |

| I <sub>IO(HV)</sub>      | input/output current on pin<br>HV      |                           |     | <b>–1</b>  | +5    | mA   |

| I <sub>IO(CTRL)</sub>    | input/output current on pin CTRL       |                           |     | -3         | 0     | mA   |

| I <sub>IO(PROTECT)</sub> | input/output current on pin PROTECT    |                           |     | -1         | +1    | mA   |

| I <sub>O(DRIVER)</sub>   | output current on pin<br>DRIVER        | δ < 10 %                  |     | -0.4       | +1    | Α    |

| General                  |                                        |                           |     |            |       |      |

| P <sub>tot</sub>         | total power dissipation                | $T_{amb} < 75  ^{\circ}C$ |     | -          | 1     | W    |

| $T_{stg}$                | storage temperature                    |                           |     | <b>-55</b> | +150  | °C   |

| T <sub>j</sub>           | junction temperature                   |                           |     | -40        | +150  | °C   |

| ESD                      |                                        |                           |     |            |       |      |

| V <sub>ESD</sub>         | electrostatic discharge                | class 1                   |     |            |       |      |

|                          | voltage                                | human body<br>model       | [1] |            |       |      |

|                          |                                        | pin HV                    |     | -1000      | +1000 | V    |

|                          |                                        | all other pins            |     | -2000      | +2000 | V    |

|                          |                                        | charged device<br>model   | [2] | -500       | +500  | V    |

<sup>[1]</sup> Equivalent to discharge a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

<sup>[2]</sup> Equivalent to discharge a 200 pF capacitor through a 0.75  $\mu H$  coil and 10  $\Omega$ .

## 9. Thermal characteristics

Table 5. Thermal characteristics

| Symbol        | Parameter                                   | Conditions                       | Тур  | Unit |

|---------------|---------------------------------------------|----------------------------------|------|------|

| $R_{th(j-a)}$ | thermal resistance from junction to ambient | in free air;<br>JEDEC test board | 73   | K/W  |

| $R_{th(j-c)}$ | thermal resistance from junction to case    | in free air;<br>JEDEC test board | 33.1 | K/W  |

## 10. Characteristics

Table 6. Characteristics

| Symbol                       | Parameter                              | Conditions                                                    | Min   | Тур   | Max   | Unit |

|------------------------------|----------------------------------------|---------------------------------------------------------------|-------|-------|-------|------|

| Start-up curre               | ent source (HV pin)                    |                                                               |       |       |       |      |

| I <sub>startup(HV)</sub>     | start-up current on pin                | V <sub>HV</sub> > 10 V                                        | 0.8   | 1.1   | 1.4   | mA   |

|                              | HV                                     | V <sub>CC</sub> > V <sub>startup</sub> ;<br>HV not sampling   | -     | -     | 1     | μΑ   |

| V <sub>clamp</sub>           | clamp voltage                          | I <sub>HV</sub> < 2 mA                                        | -     | -     | 680   | V    |

| Supply voltag                | e management (VCC pin)                 |                                                               |       |       |       |      |

| V <sub>startup</sub>         | start-up voltage                       |                                                               | 13.4  | 14.9  | 16.4  | V    |

| V <sub>restart</sub>         | restart voltage                        | burst mode                                                    | 9.9   | 11    | 12.1  | V    |

| $V_{\text{th}(\text{UVLO})}$ | undervoltage lockout threshold voltage |                                                               | 9     | 9.9   | 10.8  | V    |

| V <sub>rst</sub>             | reset voltage                          |                                                               | 7.75  | 8.65  | 9.55  | V    |

| I <sub>CC(startup)</sub>     | start-up supply current                | $V_{HV} = 0 V$                                                | -     | 40    | -     | μА   |

|                              |                                        | $V_{HV} > 10 \text{ V}$                                       | -1.35 | -1.05 | -0.75 | mA   |

| I <sub>CC(oper)</sub>        | operating supply current               | driver unloaded;<br>excluding opto current                    | 500   | 600   | 700   | μΑ   |

| I <sub>CC(burst)</sub>       | burst mode supply current              | non-switching;<br>excluding opto current                      | 200   | 235   | 270   | μΑ   |

| I <sub>CC(prot)</sub>        | protection supply current              |                                                               | 185   | 220   | 255   | μА   |

| I <sub>CC(dch)</sub>         | discharge supply current               | latched protection;<br>V <sub>CC</sub> > V <sub>startup</sub> | 0.9   | 1.25  | 1.6   | mA   |

| Mains detect                 | (HV pin)                               |                                                               |       |       |       |      |

| $t_{p(HV)}$                  | pulse duration on pin HV               | measuring mains voltage                                       | 18    | 20    | 22    | μS   |

| f <sub>meas(HV)</sub>        | measurement frequency on pin HV        | measuring mains voltage                                       | 0.9   | 1.0   | 1.1   | kHz  |

| $t_{d(norm)\text{HV}}$       | normal mode delay time on pin HV       | measuring mains voltage                                       | 5     | 6     | 7     | ms   |

| $t_{d(burst)HV}$             | burst mode delay time on pin HV        | measuring mains voltage                                       | 87    | 97    | 107   | ms   |

| $I_{bo(HV)}$                 | brownout current on pin HV             |                                                               | 552   | 587   | 622   | μΑ   |

Table 6.

Characteristics ...continued

| Symbol                     | Parameter                                | Conditions                                                                | Min    | Тур          | Max    | Uni |

|----------------------------|------------------------------------------|---------------------------------------------------------------------------|--------|--------------|--------|-----|

| I <sub>bi(HV)</sub>        | brownin current on pin<br>HV             |                                                                           | 623    | 663          | 703    | μΑ  |

| l <sub>bo(hys)</sub> HV    | hysteresis of brownout current on pin HV |                                                                           | -      | 76           | -      | μΑ  |

| IH(HV)                     | HIGH-level input current on pin HV       |                                                                           | 1186   | 1262         | 1338   | μΑ  |

| I <sub>IL(HV)</sub>        | LOW-level input current on pin HV        |                                                                           | 1118   | 1190         | 1262   | μΑ  |

| HL(hys)HV                  | HIGH to LOW hysteresis current on pin HV |                                                                           | -      | 72           | -      | μΑ  |

| Clamp(HV)                  | clamp current on pin HV                  | during measurement time                                                   | -      | -            | 1.7    | mA  |

| V <sub>meas(HV)</sub>      | measurement voltage on pin HV            |                                                                           | -      | 2.6          | -      | V   |

| t <sub>d(dch)</sub>        | discharge delay time                     | X capacitor discharge; pin HV                                             | -      | 28           | -      | ms  |

| t <sub>d(det)bo</sub>      | brownout detection delay time            |                                                                           | -      | 30           | -      | ms  |

| Peak current c             | ontrol (pin CTRL)                        |                                                                           |        |              |        |     |

| $V_{IO(CTRL)}$             | input/output voltage on pin CTRL         | minimum flyback peak current                                              | 2.3    | 2.5          | 2.7    | V   |

|                            |                                          | maximum flyback<br>current                                                | 4.9    | 5.25         | 5.6    | V   |

| $R_{int(CTRL)}$            | internal resistance on pin<br>CTRL       |                                                                           | 10     | 12           | 14     | kΩ  |

| I <sub>IO(CTRL)</sub>      | input/output current on pin CTRL         | normal mode                                                               |        |              |        |     |

|                            |                                          | $V_{CTRL} = 1.5 V$                                                        | -0.58  | -0.48        | -0.38  | mA  |

|                            |                                          | $V_{CTRL} = 3.5 V$                                                        | -0.385 | -0.315       | -0.245 | mA  |

| V <sub>startup(CTRL)</sub> | start-up voltage on pin<br>CTRL          |                                                                           | 4.7    | 5            | 5.3    | V   |

| Burst mode (p              | in CTRL)                                 |                                                                           |        |              |        |     |

| $V_{th(burst)}$            | burst mode threshold voltage             |                                                                           | 0.42   | 0.5          | 0.58   | V   |

| T <sub>burst</sub>         | burst mode period                        |                                                                           | -      | 1250         | -      | μS  |

| sw(min)                    | minimum switching frequency              | burst mode                                                                | 23     | 25           | 27     | kHz |

| regd(CTRL)                 | regulated current on pin CTRL            | burst mode                                                                | -115   | -100         | -85    | μΑ  |

| V <sub>clamp(CTRL)</sub>   | clamp voltage on pin<br>CTRL             | burst mode;<br>system switching                                           | 0.44   | 0.5          | 0.56   | V   |

| I <sub>stop(CTRL)</sub>    | stop current on pin CTRL                 | burst mode;<br>system switching;<br>including regulated<br>output current | -820   | - <b>750</b> | -680   | μΑ  |

Table 6.

Characteristics ...continued

| Symbol                              | Parameter                                  | Conditions                                                                                                                                   | Min   | Тур                     | Max   | Unit |

|-------------------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------|-------|------|

| t <sub>pd(CTRL)</sub>               | pull-down time on pin<br>CTRL              |                                                                                                                                              | 10    | 12.5                    | 15    | μS   |

| det(CTRL)                           | detection current on pin                   | positive load step                                                                                                                           | 65    | 80                      | 95    | μΑ   |

|                                     | CTRL                                       | disable pulling down the CTRL pin                                                                                                            | 77    | 87                      | 97    | μΑ   |

| Oscillator                          |                                            |                                                                                                                                              |       |                         |       |      |

| f <sub>sw(max)</sub>                | maximum switching frequency                |                                                                                                                                              | 125   | 132.5                   | 140   | kHz  |

| sw(min)                             | minimum switching frequency                |                                                                                                                                              | 23    | 25                      | 27    | kHz  |

| V <sub>start(red)f</sub>            | frequency reduction start voltage          | pin CTRL                                                                                                                                     | 2.3   | 2.5                     | 2.7   | V    |

| Current sense (                     | pin ISENSE)                                |                                                                                                                                              |       |                         |       |      |

| V <sub>sense(max)</sub>             | maximum sense voltage                      | $\begin{array}{l} \Delta V/\Delta t = 0 \ V/s; \\ I_{AUX} = 0 \ \mu A; \\ V_{CTRL} = 5.5 \ V \end{array}$                                    | 700   | 765                     | 830   | mV   |

|                                     |                                            | frequency reduction<br>mode; $\Delta V/\Delta t = 0$ mV/ $\mu$ s;<br>$I_{AUX} = 0$ $\mu$ A;                                                  | 190   | 207                     | 225   | mV   |

|                                     |                                            | V <sub>CTRL</sub> = 1.0 V                                                                                                                    |       | 100                     |       |      |

| tPD(sense)                          | sense propagation delay                    | from the ISENSE pin reaching V <sub>sense(max)</sub> to driver off; V <sub>ISENSE</sub> pulse-stepping 100 mV around V <sub>sense(max)</sub> | -     | 120                     | -     | ns   |

| t <sub>leb</sub>                    | leading edge blanking time                 | • Selise(max)                                                                                                                                | 275   | 325                     | 375   | ns   |

| Soft start (pin I                   | SENSE)                                     |                                                                                                                                              |       |                         |       |      |

| start(soft)                         | soft start current                         |                                                                                                                                              | -85   | -75                     | -65   | μΑ   |

| V <sub>start(soft)</sub>            | soft start voltage                         | enable voltage                                                                                                                               | -     | V <sub>sense(max)</sub> | -     | V    |

| R <sub>start(soft)</sub>            | soft start resistance                      |                                                                                                                                              | 12    | -                       | -     | kΩ   |

|                                     | on and valley control (pin A               | UX)                                                                                                                                          |       |                         |       |      |

| V <sub>det(demag)</sub>             | demagnetization detection voltage          |                                                                                                                                              | 20    | 35                      | 50    | mV   |

| prot(AUX)                           | protection current on pin AUX              |                                                                                                                                              | -     | -200                    | -     | nA   |

| blank(det)demag                     | demagnetization detection blanking time    |                                                                                                                                              | 1.8   | 2.2                     | 2.6   | μS   |

| $(\Delta V/\Delta t)_{\text{vrec}}$ | valley recognition                         | positive $\Delta V/\Delta t$                                                                                                                 | 0.25  | 0.37                    | 0.49  | V/µs |

|                                     | voltage change with time                   | negative $\Delta V/\Delta t$                                                                                                                 | -2.35 | -1.9                    | -1.45 | V/μs |

| d(vrec-swon)                        | valley recognition to switch-on delay time |                                                                                                                                              | -     | 120                     | -     | ns   |

| V <sub>clamp(AUX)</sub>             | clamp voltage on pin                       | I <sub>AUX</sub> = 1 mA                                                                                                                      | 4.4   | 4.8                     | 5.2   | ٧    |

Table 6.

Characteristics ...continued

| Symbol                         | Parameter                                         | Conditions                                    | Min  | Тур  | Max   | Unit |

|--------------------------------|---------------------------------------------------|-----------------------------------------------|------|------|-------|------|

| t <sub>sup(xfmr_ring)</sub>    | transformer ringing                               |                                               | 1.9  | 2.3  | 2.7   | μS   |

|                                | suppression time                                  |                                               |      |      |       |      |

| Maximum on-tim                 | e (pin DRIVER)                                    |                                               |      |      |       |      |

| t <sub>on(max)</sub>           | maximum on-time                                   |                                               | 45   | 55   | 65    | μS   |

| Driver (pin DRIVE              | ER)                                               |                                               |      |      |       |      |

| I <sub>source</sub> (DRIVER)   | source current on pin<br>DRIVER                   | V <sub>DRIVER</sub> = 2 V                     | -    | -0.3 | -0.25 | Α    |

| I <sub>sink(DRIVER)</sub>      | sink current on pin                               | $V_{DRIVER} = 2 V$                            | 0.25 | 0.3  | -     | Α    |

|                                | DRIVER                                            | $V_{DRIVER} = 10 V$                           | 0.6  | 0.75 | -     | Α    |

| V <sub>O(DRIVER)max</sub>      | maximum output voltage on pin DRIVER              |                                               | 9    | 10.5 | 12    | V    |

| Overpower comp                 | pensation (pin ISENSE and                         | d pin AUX)                                    |      |      |       |      |

| $V_{clamp(AUX)}$               | clamp voltage on pin<br>AUX                       | primary stroke;<br>I <sub>AUX</sub> = -0.3 mA | -0.8 | -0.7 | -0.6  | V    |

| t <sub>d(clamp)</sub> AUX      | clamp delay time on pin<br>AUX                    | after rising edge of pin<br>DRIVER            | 580  | 665  | 750   | ns   |

|                                |                                                   | after falling edge of pin<br>DRIVER           | 1.8  | 2.2  | 2.6   | μS   |

| V <sub>opc(ISENSE)</sub>       | overpower                                         | $I_{AUX} = -0.3 \text{ mA}$                   | 700  | 765  | 830   | mV   |

| ,                              | compensation voltage on pin ISENSE                | $I_{AUX} = -1.46 \text{ mA}$                  | 400  | 450  | 500   | mV   |

| $V_{opp(ISENSE)}$              | overpower protection                              | counter trigger level                         |      |      |       |      |

|                                | voltage on pin ISENSE                             | $I_{AUX} = -0.3 \text{ mA}$                   | 450  | 500  | 550   | mV   |

|                                |                                                   | $I_{AUX} = -1.46 \text{ mA}$                  | 265  | 295  | 325   | mV   |

| d(opp)                         | overpower protection delay time                   | start-up mode;<br>V <sub>CTRL</sub> > 5 V     | 36   | 40   | 44    | ms   |

|                                |                                                   | normal mode                                   | 180  | 200  | 220   | ms   |

| t <sub>d(restart)</sub>        | restart delay time                                |                                               | 720  | 800  | 820   | ms   |

| External protecti              | on (pin PROTECT)                                  |                                               |      |      |       |      |

| $V_{det(PROTECT)}$             | detection voltage on pin PROTECT                  |                                               | 0.47 | 0.5  | 0.53  | V    |

| V <sub>hys(det)(PROTECT)</sub> | hysteresis of detection voltage on pin PROTECT    |                                               | -    | 50   | -     | mV   |

| I <sub>O(PROTECT)</sub>        | output current on pin                             | normal mode                                   | -79  | -74  | -69   | μΑ   |

| •                              | PROTECT                                           | power-down mode                               | -55  | -47  | -40   | μΑ   |

| V <sub>clamp(PROTECT)</sub>    | clamp voltage on pin<br>PROTECT                   |                                               | 1.25 | 1.45 | 1.65  | V    |

| Power-down mod                 | de (pin PROTECT)                                  |                                               |      |      |       |      |

| V <sub>th(pd)</sub> PROTECT    | power-down threshold<br>voltage on pin<br>PROTECT |                                               | 0.18 | 0.2  | 0.22  | V    |

|                                |                                                   |                                               |      |      |       |      |

Table 6.

Characteristics ...continued

| Symbol                | Parameter                                 | Conditions              | Min  | Тур | Max  | Unit |

|-----------------------|-------------------------------------------|-------------------------|------|-----|------|------|

| Overvoltage p         | protection (pin AUX)                      |                         |      |     |      |      |

| $V_{\text{ovp}(AUX)}$ | overvoltage protection voltage on pin AUX |                         | 2.88 | 3   | 3.12 | V    |

| t <sub>det(ovp)</sub> | overvoltage protection detection time     | in the secondary stroke | 1.9  | 2.3 | 2.7  | μS   |

| Temperature           | protection                                |                         |      |     |      |      |

| $T_{pl(IC)}$          | IC protection level temperature           |                         | 130  | 140 | 150  | °C   |

# 11. Application information

A power supply with TEA18361LT is a flyback converter operating in QR mode or DCM (See Figure 3).

Capacitor  $C_{VCC}$  buffers the IC supply voltage. The IC supply voltage is powered from the mains via D1, D2,  $R_{HV}$  during start-up. It is powered via the auxiliary winding during normal operation.  $R_{HV}$  defines the current into the HV pin for brownout detection and mains detection.

Sense resistor  $R_{\text{sense}}$  converts the current through MOSFET S1 into a voltage on pin ISENSE. The value of  $R_{\text{sense}}$  defines the maximum primary peak current through MOSFET S1. Resistor  $R_{SS}$  and capacitor  $C_{SS}$  define the soft start time.

Resistor  $R_{DRIVER}$  is required to limit the current spikes to pin DRIVER because of parasitic inductance of the current sense resistor  $R_{sense}$ .  $R_{DRIVER}$  also dampens possible oscillation of MOSFET S1. Adding a bead on the gate pin of MOSFET S1 can be required to prevent local oscillations of the MOSFET.

The PROTECT pin can be connected to a Negative Temperature Coefficient (NTC) resistor. The protection is activated when the resistor drops below a value of  $V_{det(PROTECT)}$  /  $I_{O(PROTECT)}$  = 6.7 k $\Omega$ . Shorting the PROTECT pin to ground by an external switch or optocoupler can activate the power-down mode.

The resistor  $R_{AUX2}$  determines the compensation for input voltage variation. The ratio of  $R_{AUX1}$  and  $R_{AUX2}$  determines the overvoltage protection at the AUX pin.

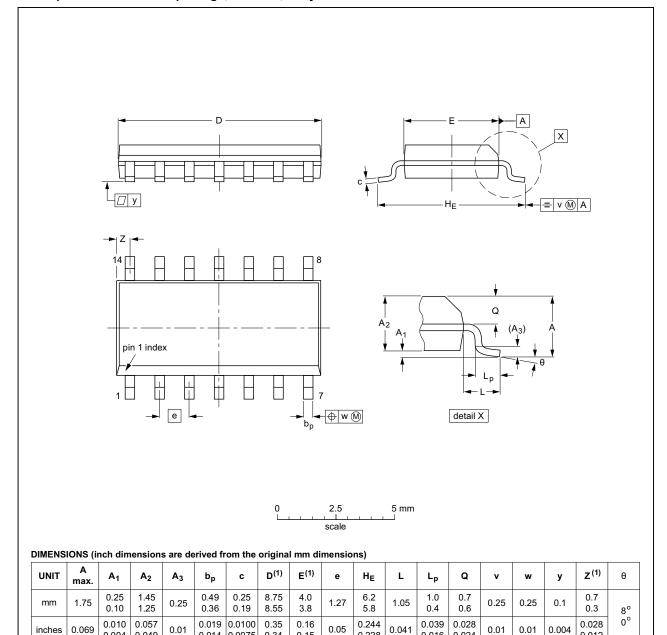

# 12. Package outline

### SO14: plastic small outline package; 14 leads; body width 3.9 mm

SOT108-1

# Note

1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

0.014 0.0075

0.34

0.15

| OUTLINE  |        | REFER  | ENCES | EUROPEAN |            | ISSUE DATE                      |

|----------|--------|--------|-------|----------|------------|---------------------------------|

| VERSION  | IEC    | JEDEC  | JEITA |          | PROJECTION | 155UE DATE                      |

| SOT108-1 | 076E06 | MS-012 |       |          |            | <del>99-12-27</del><br>03-02-19 |

0.228

0.016

0.024

Fig 16. Package outline SOT108-1 (SO14)

0.004

0.049

TEA18361LT