# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### VIDEO CELLULAR MATRIX

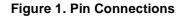

- 6 Video Inputs 8 Video Outputs

- 2 Internal Selectable YC Adders

- 15MHz Bandwidth @ -3dB

- Selectable 0.5/6.5dB Gain FOR EACH Output

- High Impedance Switch for each Output (3state operation)

- Programmable Clamp Mode on each Input (sync bottom or average value)

- -60dB Crosstalk @ 5MHz

- 4 Sub-address Capability

- I<sup>2</sup>C Bus Control

#### DESCRIPTION

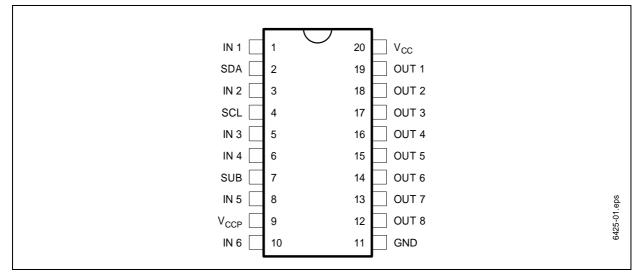

This device is intended for switching between video and chroma signals such as CVBS, SVHS, baseband CVBS, MAC. Each input clamp mode, each output gain, all switching are controlled through the  $I^2C$  bus. The 8 outputs can be set separately in high impedance state, to enable parallel DC connection of several devices (up to 4).

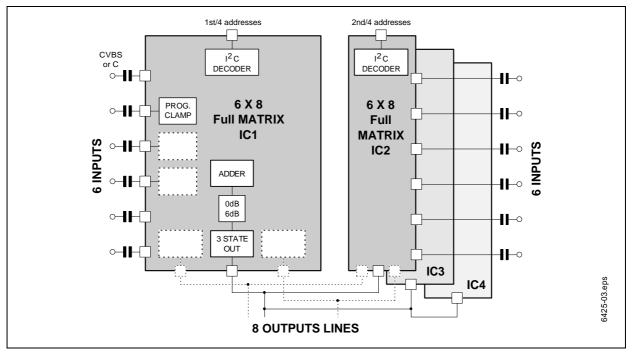

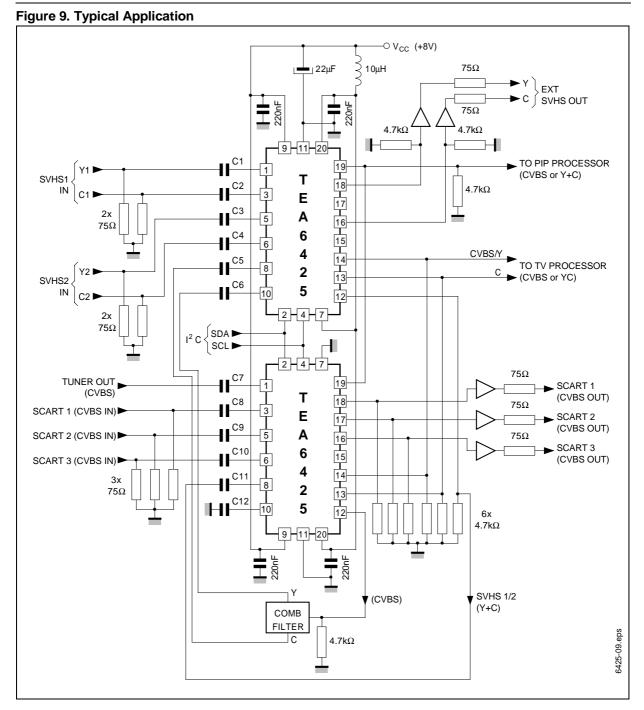

#### Figure 2. Block Diagram

Figure 3. Cellular Matrix Connections

2/10

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol            | Parameter                     | Value              | Unit |

|-------------------|-------------------------------|--------------------|------|

| V <sub>CC</sub>   | Supply Voltage                | 12                 | V    |

| VI                | Voltage at Pin i to GND       | 0, V <sub>CC</sub> | V    |

| T <sub>oper</sub> | Operating Ambient Temperature | 0, + 70            | °C   |

| T <sub>stg</sub>  | Storage Temperature           | -20, + 150         | °C   |

#### THERMAL DATA

| Symbol                | Parameter                           | Value | Unit |      |

|-----------------------|-------------------------------------|-------|------|------|

| R <sub>th</sub> (j-a) | Junction-ambient Thermal Resistance | Min.  | 80   | °C/W |

**ELECTRICAL CHARACTERISTICS** ( $V_{CC} = 8V$ ,  $T_{amb} = 25^{oC}$ ,  $V_{IN} = 1V$ , Gain = 6.5dB,  $C_{load} = 20pF$ ,  $R_{load} = 4.7k\Omega$ ; Gain condition, clamp and 3-state are controlled by I<sup>2C</sup> bus, unless otherwise specified)

| Symbol             | Parameter Test Conditions                 |                                                                    | Min. | Тур.          | Max. | Unit            |

|--------------------|-------------------------------------------|--------------------------------------------------------------------|------|---------------|------|-----------------|

| SUPPLY             |                                           |                                                                    | •    | •             |      |                 |

| V <sub>CC</sub>    | Supply Voltage                            |                                                                    | 7.2  | 8             | 8.8  | V               |

| I <sub>CC</sub>    | Supply Current                            |                                                                    |      | 45            | 60   | mA              |

| RR                 | Supply Voltage Rejection                  | f = 1kHz                                                           | 40   | 46            |      | dB              |

| VIDEO INP          | UTS (clamping at bottom sync level        | )                                                                  | •    | •             |      |                 |

| V <sub>IN</sub>    | Max. Signal Amplitude                     | Clamp Active                                                       | 2    |               |      | V <sub>PP</sub> |

| V <sub>clamp</sub> | Clamp Level                               | Clamp Active                                                       | 1.7  | 2             | 2.3  | V               |

| V <sub>DC</sub>    | Input DC Level                            | Clamp Inactive                                                     | 2.7  | 3             | 3.3  | V               |

| I <sub>IN</sub>    | Leakage Current                           | 1 input connected to 1 output                                      |      | 2             | 5    | μA              |

| I <sub>clamp</sub> | Clamp Current                             | V <sub>clamp</sub> - 200mV                                         |      | 0.9           | 3    | mA              |

| VIDEO OU           | TPUTS                                     | • •                                                                | •    | •             |      |                 |

| R <sub>OUT</sub>   | Output Resistance                         |                                                                    |      | 15            | 50   | W               |

| Z <sub>HI</sub>    | Output "off" Impedance                    | no load                                                            | 50   |               |      | kΩ              |

| C <sub>HI</sub>    | C <sub>OUT</sub> in 3-state               | no load                                                            |      | 3             |      | pF              |

| G1                 | Voltage Gain                              | f = 100kHz                                                         | 0    | 0.5           | 1    | dB              |

| G2                 | Voltage Gain                              | f = 100kHz                                                         | 6    | 6.5           | 7    | dB              |

| V <sub>sync</sub>  | Top Level Sync (Y or CVBS)                | G = 6.5dB, Clamp Active                                            | 1    | 1.25          | 2    | V               |

|                    | Output Mean Level (chroma)                | G = 0.5dB, Clamp Inactive                                          | 2    | 2.4           | 3    | V               |

| V <sub>bias</sub>  | Output Mean Lever (Chroma)                | G = 6.5dB, Clamp Inactive                                          | 3    | 3.4           | 4    | V               |

|                    | Isolation "off" State                     | f = 5MHz                                                           | 60   |               |      | dB              |

|                    | Crosstalk Attenuation between<br>Channels | f = 5MHz                                                           | 50   | 60            |      | dB              |

| В                  | Bandwidth                                 | $C_{load} = 20pF, G = 6.5dB$<br>at ± 0.5dB<br>at ± 1dB<br>at - 3dB |      | 5<br>10<br>21 |      | MHz             |

#### FUNCTIONAL DESCRIPTION

This device is controlled via the  $I^2C$  bus. 4 addresses can be selected by a 4-level detector on Pin 7, thus enabling parallel connection of 4 devices.

Via the I<sup>2</sup>C bus :

- The input signals can be clamped at their negative peak (top sync).

- The gain factor of the outputs can be selected between 0.5 and 6.5dB.

- Each of the 6 inputs can be connected to the 8 outputs.

- Each output can individually be set in a high impedance state.

Two internal SVHS mixers will add the selected Y and C inputs. Two dedicated outputs will have the option to select this added signal also.

#### I<sup>2</sup>C BUS CHARACTERISTICS

| Cumbal                | Desemptor                                                   | Test Conditions         | Stan  | dard Mode             | Fa    | Unit                  |      |

|-----------------------|-------------------------------------------------------------|-------------------------|-------|-----------------------|-------|-----------------------|------|

| Symbol                | Parameter                                                   | Test Conditions         | Min.  | Max.                  | Min.  | Max.                  | Unit |

| SCL                   |                                                             |                         |       |                       |       |                       |      |

| V <sub>IL</sub>       | Low Level Input Voltage                                     |                         | - 0.3 | + 1.5                 | - 0.3 | + 1.5                 | V    |

| V <sub>IH</sub>       | High Level Input Voltage                                    |                         | 3.0   | V <sub>CC</sub> + 0.5 | 3.0   | V <sub>CC</sub> + 0.5 | V    |

| Ι <sub>LI</sub>       | Input Leakage Current                                       | $V_{I} = 0$ to $V_{DD}$ | - 10  | + 10                  | - 10  | + 10                  | μA   |

| f <sub>SCL</sub>      | Clock Frequency                                             |                         | 0     | 100                   | 0     | 400                   | kHz  |

| t <sub>R</sub>        | Input Rise Time                                             | 1.5V to 3V              |       | 1000                  |       | 300                   | ns   |

| t <sub>F</sub>        | Input Fall Time                                             | 1.5V to 3V              |       | 300                   |       | 300                   | ns   |

| CI                    | Input Capacitance                                           |                         |       | 10                    |       | 10                    | pF   |

| SDA                   | •                                                           | •                       | -     |                       | •     |                       |      |

| V <sub>IL</sub>       | Low Level Input Voltage                                     |                         | - 0.3 | + 1.5                 | - 0.3 | + 1.5                 | V    |

| V <sub>IH</sub>       | High Level Input Voltage                                    |                         | 3.0   | V <sub>CC</sub> + 0.5 | 3.0   | V <sub>CC</sub> + 0.5 | V    |

| Ι <sub>LI</sub>       | Input Leakage Current                                       | $V_{I} = 0$ to $V_{DD}$ | - 10  | + 10                  | - 10  | + 10                  | μA   |

| CI                    | Input Capacitance                                           |                         |       | 10                    |       | 10                    | pF   |

| t <sub>R</sub>        | Input Rise Time                                             | 1.5V to 3V              |       | 1000                  |       | 300                   | ns   |

| t <sub>F</sub>        | Input Fall Time                                             | 1.5V to 3V              |       | 300                   |       | 300                   | ns   |

| V <sub>OL</sub>       | Low Level Output Voltage                                    | I <sub>OL</sub> = 3mA   |       | 0.4                   |       | 0.4                   | V    |

| t <sub>F</sub>        | Output Fall Time                                            | 3V to 1.5V              |       | 250                   |       | 250                   | ns   |

| CL                    | Load Capacitance                                            |                         |       | 400                   |       | 400                   | pF   |

| TIMING                |                                                             |                         |       |                       |       |                       |      |

| t <sub>LOW</sub>      | Clock Low Period                                            |                         | 4.7   |                       | 1.3   |                       | μs   |

| t <sub>HIGH</sub>     | Clock High Period                                           |                         | 4.0   |                       | 0.6   |                       | μs   |

| t <sub>SU</sub> , DAT | Data Set-up Time                                            |                         | 250   |                       | 100   |                       | ns   |

| t <sub>HD</sub> , DAT | Data Hold Time                                              |                         | 0     | 340                   | 0     | 340                   | ns   |

|                       | Set-up Time from Clock High to Stop                         |                         | 4.0   |                       | 0.6   |                       | μs   |

| t <sub>BUF</sub>      | Start Set-up Time following a Stop                          |                         | 4.7   |                       | 1.3   |                       | μs   |

| t <sub>HD</sub> , STA | Start Hold Time                                             |                         | 4.0   |                       | 0.6   |                       | μs   |

| t <sub>SU</sub> , STA | Start Set-up Time following Clock Low-to<br>High Transition |                         | 4.7   |                       | 0.6   |                       | μs   |

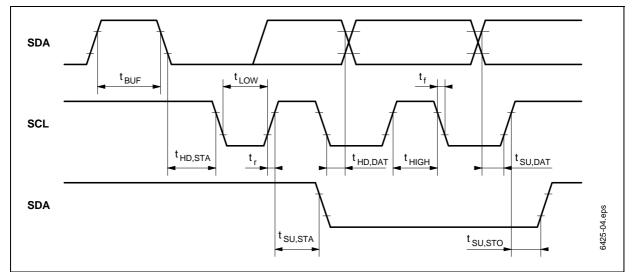

#### Figure 4. I<sup>2</sup>C Bus Timing

#### I<sup>2</sup>C BUS SELECTION

#### I<sup>2</sup>C Bus Slave Address

| Address | A6 | A5 | A4 | A3 | A2 | A1  | A0 | R/W |

|---------|----|----|----|----|----|-----|----|-----|

| Value   | 1  | 0  | 0  | 1  | 0  | A 1 | A0 | 0   |

#### |<sup>2</sup>C Sub-Address

| Symbol | Parameter          | Cond | litions         | Pin 7 Voltage (Typ) | Unit            |

|--------|--------------------|------|-----------------|---------------------|-----------------|

| Vsub   | Slave address HEXA |      | ddress<br>note) |                     |                 |

|        |                    | A1   | A0              |                     |                 |

| 1      | 90                 | 0    | 0               | GND                 | V               |

| 2      | 96                 | 1    | 1               | V <sub>CC</sub>     | V               |

| 3      | 94                 | 1    | 0               | 1/3                 | V <sub>CC</sub> |

| 4      | 92                 | 0    | 1               | 2/3                 | V <sub>CC</sub> |

**Note:** The first 3 levels are defined by connecting the sub-address pin to the appropriate level. Sub-address 4 will be selected when this pin is left open.

#### 1st Data Byte

|        | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Selected |

|--------|----|----|----|----|----|----|----|----|----------|

|        | a2 | a1 | a0 | *  | *  | *  | *  | 1  | Output   |

|        | 0  | 0  | 0  | *  | *  | *  | *  | 0  | OUT1     |

|        | 0  | 0  | 1  | *  | *  | *  | *  | 0  | OUT2     |

|        | 0  | 1  | 0  | *  | *  | *  | *  | 0  | OUT3     |

| Output | 0  | 1  | 1  | *  | *  | *  | *  | 0  | OUT4     |

| Select | 1  | 0  | 0  | *  | *  | *  | *  | 0  | OUT5     |

|        | 1  | 0  | 1  | *  | *  | *  | *  | 0  | OUT6     |

|        | 1  | 1  | 0  | *  | *  | *  | *  | 0  | OUT7     |

|        | 1  | 1  | 1  | *  | *  | *  | *  | 0  | OUT8     |

#### 2nd Data Byte

|           | b7 | b6 | b5 | b4 | b3 | b2 | b1 | b0 | Selected      |

|-----------|----|----|----|----|----|----|----|----|---------------|

| İ         | a2 | a1 | a0 | *  | *  | *  | *  | I  | Output        |

|           | 0  | 0  | 0  | *  | *  | *  | *  | 1  | IN1           |

|           | 0  | 0  | 1  | *  | *  | *  | *  | 1  | IN2           |

| Input     | 0  | 1  | 0  | *  | *  | *  | *  | 1  | IN3           |

| Select    | 0  | 1  | 1  | *  | *  | *  | *  | 1  | IN4           |

|           | 1  | 0  | 0  | *  | *  | *  | *  | 1  | IN5           |

|           | 1  | 0  | 1  | *  | *  | *  | *  | 1  | IN6           |

| Claura    | *  | *  | *  | 0  | *  | *  | *  | 1  | Free          |

| Clamp     | *  | *  | *  | 1  | *  | *  | *  | 1  | Clamped       |

| Qain      | *  | *  | *  | *  | 0  | *  | *  | 1  | 0.5dB         |

| Gain      | *  | *  | *  | *  | 1  | *  | *  | 1  | 6.5dB         |

| Misson    | *  | *  | *  | *  | *  | 0  | *  | 1  | Disabled      |

| Mixer     | *  | *  | *  | *  | *  | 1  | *  | 1  | Enabled       |

| Tri atata | *  | *  | *  | *  | *  | *  | 0  | 1  | Low impedance |

| Tri-state | *  | *  | *  | *  | *  | *  | 1  | 1  | Tri-state     |

#### **Power-on-Reset**

When active: outputs in 3-state, inputs are clamped

| Symbol | Parameter      | Test Conditions       | Min. | Тур. | Max. | Unit |

|--------|----------------|-----------------------|------|------|------|------|

|        | Start of Reset | Incr. V <sub>CC</sub> |      |      | 2.5  | V    |

| Reset  |                | Decr. V <sub>CC</sub> |      |      | 4.2  | V    |

|        | End of Reset   | Incr. V <sub>CC</sub> | 4.5  |      | 7.2  | V    |

#### **PIN CONFIGURATIONS**

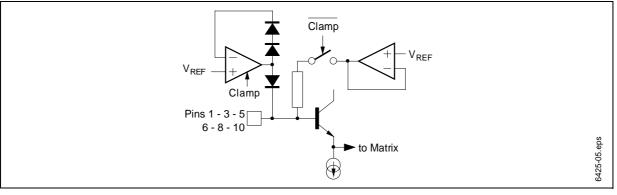

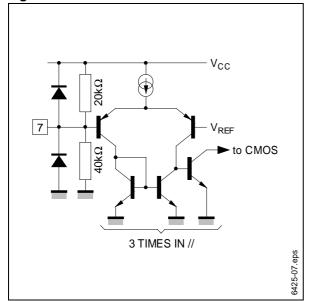

#### Figure 5. Video IN

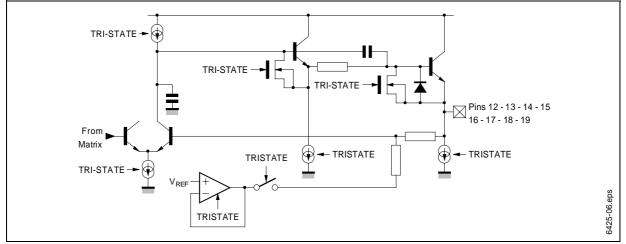

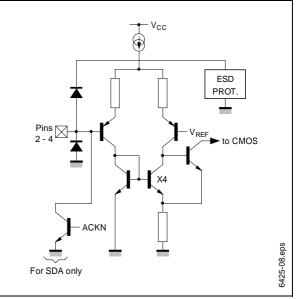

#### Figure 6. Video OUT

Figure 8. Bus Inputs

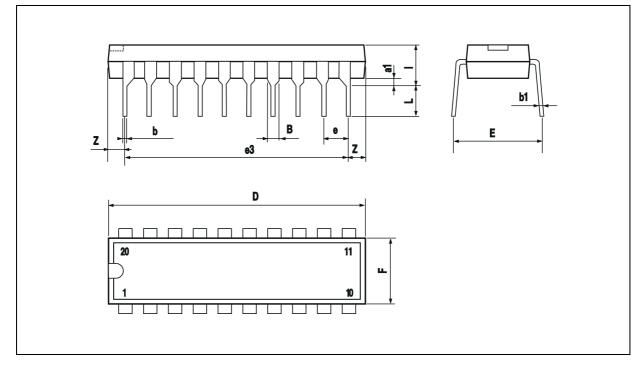

#### PACKAGE MECHANICAL DATA

20 PINS - PLASTIC DIP

#### Figure 10. 20-Pin Package

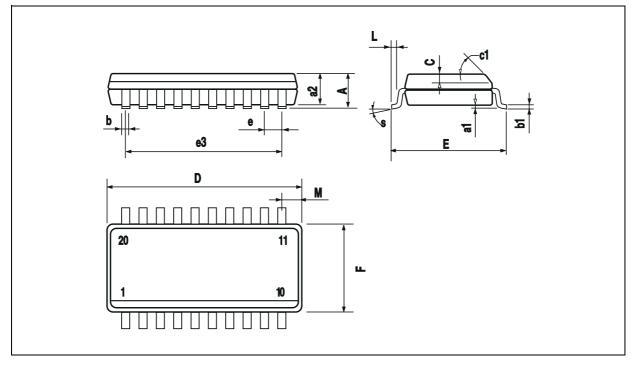

#### PACKAGE MECHANICAL DATA (Cont'd) 20 PINS - PLASTIC MICROPACKAGE

#### Figure 11. 20-Pin Package

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics

©2003 STMicroelectronics - All Rights Reserved.

Purchase of I<sup>2</sup>C Components by STMicroelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

STMicroelectronics Group of Companies

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

**لرک**ا