Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **TFA9891**

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

Rev. 1 — 21 December 2016

Product short data sheet

### 1. General description

The TFA9891 is a high efficiency class-D audio amplifier with a sophisticated speaker boost and protection algorithm. It can deliver 7.2 W peak output power to an 8  $\Omega$  speaker, at a supply voltage of 3.6 V. The internal boost converter raises the supply voltage to 9.5 V, providing ample headroom for major improvements in sound quality.

A safe working environment is provided for the speaker under all operating conditions. The TFA9891 maximizes acoustic output while ensuring that the diaphragm displacement and voice coil temperature do not exceed their rated limits. This function is based on a speaker box model that operates in all loudspeaker environments (e.g. free air, closed box or vented box). Furthermore, advanced signal processing ensures that the quality of the audio signal is never degraded by unwanted clipping or distortion in the amplifier or speaker. An integrated Dynamic Range Compressor (DRC) allows the speaker to operate at the highest possible power rating without suffering physical damage.

Unlike competing solutions, the adaptive sound maximizer algorithm uses feedback to calculate both the temperature and the excursion. It allows the TFA9891 to adapt to changes in the acoustic environment.

Internal intelligent DC-to-DC conversion boosts the supply rail to provide additional headroom and power output. The supply voltage is only raised when necessary. It maximizes the output power of the class-D audio amplifier while limiting quiescent power consumption.

The TFA9891 also incorporates advanced battery protection. By limiting the supply current when the battery voltage is low, it prevents the audio system from drawing excessive load currents from the battery. Drawing excessive load currents from the battery could cause a system undervoltage. The advanced processor minimizes the impact of a falling battery voltage on the audio quality, by preventing distortion as the battery discharges.

The device features low RF susceptibility because it has a digital input interface that is insensitive to clock jitter. The second order closed loop architecture used in a class-D audio amplifier provides excellent audio performance and high supply voltage ripple rejection. The audio input interface is I<sup>2</sup>S and the control settings are communicated via an I<sup>2</sup>C-bus interface.

The device also provides the speaker with robust protection against ESD damage. In a typical application, no additional components are required to withstand a 15 kV discharge on the speaker.

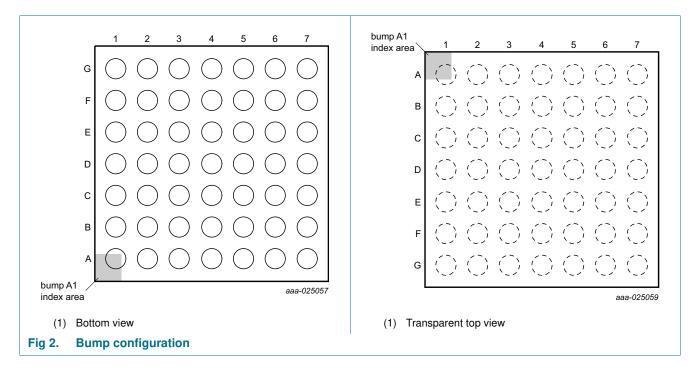

The TFA9891 is available in a 49-bump WLCSP (Wafer Level Chip-Size Package) with a 400  $\mu$ m pitch.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 2. Features and benefits

- Sophisticated speaker-boost and protection algorithm that maximizes speaker performance while protecting the speaker:

- Fully embedded software, no additional license fee or porting required

- ◆ Total integrated solution that includes DSP, amplifier, DC-to-DC, sensing and more

- Adaptive excursion control which guarantees that the speaker membrane excursion never exceeds its rated limit

- Multiband Dynamic Range Compressor (DRC) allows independent control of up to three frequency bands

- Audio enhancement

- Real-time temperature protection direct measurement ensures that voice coil temperature never exceeds its rated limit

- Environmentally aware automatically adapts speaker parameters to acoustic and thermal changes including compensation for speaker box leakage

- Output power: 3.6 W (RMS) into 8  $\Omega$  at 3.6 V supply voltage (THD = 1 %)

- Clip avoidance DSP algorithm prevents clipping even with sagging supply voltage

- Bandwidth extension option to increase low frequency response

- Compatible with standard acoustic echo canceler (s)

- High efficiency and low-power dissipation

- Wide supply voltage range (fully operational from 2.7 V to 5.5 V)

- Two I<sup>2</sup>S inputs to support two audio sources or one Pulse Density Modulation (PDM) input

- A third I<sup>2</sup>S input dedicated to inter-chip communications

- I<sup>2</sup>C-bus control interface (400 kHz)

- Speaker current and voltage monitoring (via the I<sup>2</sup>S-bus or PDM output) for Acoustic Echo Cancellation (AEC) at the host

- Fully short-circuit proof across the load and to the supply lines

- Sample frequencies from 8 kHz to 48 kHz supported in I<sup>2</sup>S mode and 16 kHz to 48 kHz in PDM mode

- 3-bit clock/word select ratios supported (32x, 48x, and 64x) in I<sup>2</sup>S mode

- Bit clock speed from 2.048 MHz up to 6.144 MHz in PDM mode

- Option to route I<sup>2</sup>S input directly to I<sup>2</sup>S output allowing a second I<sup>2</sup>S output slave device to be used in combination with TFA9891

- TDM interface supported (with limited functionality)

- Volume control

- Low RF susceptibility

- Input clock jitter insensitive interface

- Thermally protected

- 15 kV system-level ESD protection without external components

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

## 3. Applications

- Mobile phones, Tablets

- Portable Navigation Devices (PND)

- Notebooks/netbooks

- MP3 players and portable media players

- Small audio systems

### 4. Quick reference data

Table 1. Quick reference data

| Symbol              | Parameter              | Conditions                                                                                                                                                                              | Min  | Тур | Max  | Unit |

|---------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| $V_{BAT}$           | battery supply voltage | on pin VBAT                                                                                                                                                                             | 2.7  | -   | 5.5  | ٧    |

| $V_{DDD}$           | digital supply voltage | on pin VDDD                                                                                                                                                                             | 1.65 | 1.8 | 1.95 | V    |

| Іват                | battery supply current | on pin VBAT and in DC-to-DC converter coil; operating modes with load; DC-to-DC converter in adaptive boost mode (no output signal, V <sub>BAT</sub> = 3.6 V, V <sub>DDD</sub> = 1.8 V) | -    | 4   | -    | mA   |

|                     |                        | power-down mode                                                                                                                                                                         | -    | 1   | -    | μΑ   |

| I <sub>DDD</sub>    | digital supply current | on pin VDDD; operating modes; speaker boost protection activated                                                                                                                        | -    | 20  | -    | mA   |

|                     |                        | on pin VDDD; operating modes;<br>CoolFlux DSP bypassed                                                                                                                                  | -    | 7   | -    | mA   |

|                     |                        | on pin VDDD; power-down mode;<br>BCK1 = WS1 = DATAI1 = BCK2 =<br>WS2 = DATAI2 = DATAI3 = 0 V                                                                                            | -    | 10  |      | μΑ   |

| P <sub>o(RMS)</sub> | RMS output power       | THD+N = 1 %; CLIP = 0                                                                                                                                                                   |      |     |      |      |

|                     |                        | $R_L = 8 \Omega$ ; $f_s = 48 \text{ kHz}$                                                                                                                                               | -    | 3.6 | -    | W    |

|                     |                        | $R_L = 8 \Omega$ ; $f_s = 32 \text{ kHz}$                                                                                                                                               | -    | 3.7 | -    | W    |

## 5. Ordering information

Table 2. Ordering information

| Type number TFA9891UK | Package |                                                                                                       |         |  |  |  |  |  |

|-----------------------|---------|-------------------------------------------------------------------------------------------------------|---------|--|--|--|--|--|

|                       | Name    | Description                                                                                           | Version |  |  |  |  |  |

| TFA9891UK             | WLCSP49 | wafer level chip-scale package; 49 bumps; $3.43\times 2.98\times 0.56$ mm (backside coating included) | TFA9891 |  |  |  |  |  |

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

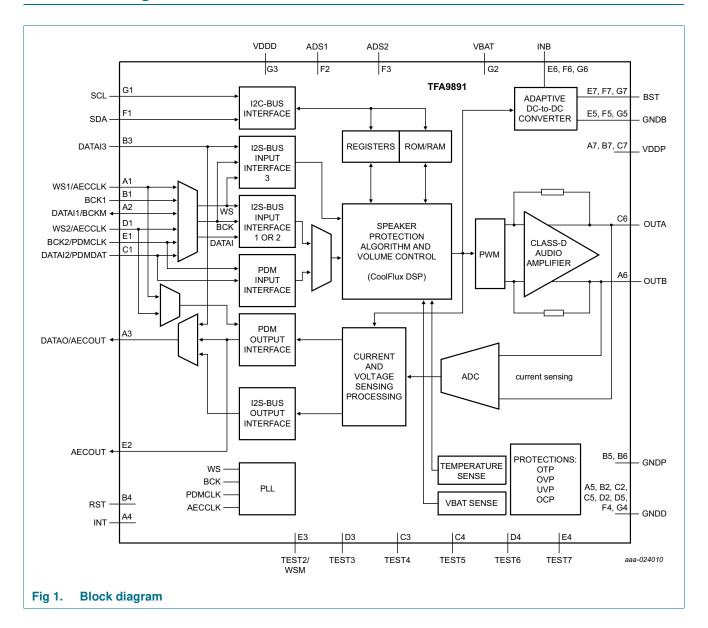

### 6. Block diagram

**NXP Semiconductors**

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

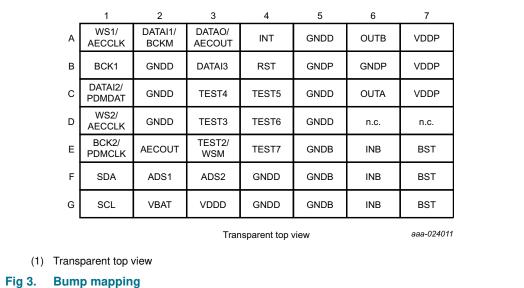

## **Pinning information**

### 7.1 Pinning

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

## 7.2 Pin description

Table 3. Pin description

| Symbol        | Pin        | Туре | Description                                                                                                                                                                |

|---------------|------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WS1/AECCLK    | A1         |      | -                                                                                                                                                                          |

| WSI/AECCLK    | AI         | I    | I <sup>2</sup> S mode: Digital audio word select input 1 for I <sup>2</sup> S interface 1 PDM mode: PDM input clock used for AEC reference output (in mono)                |

| DATAI1/BCKM   | A2         | I/O  | I <sup>2</sup> S mode: Digital audio data input 1 for I <sup>2</sup> S interface 1<br>PDM mode: Master I <sup>2</sup> S audio bit clock output for stereo gain<br>exchange |

| DATAO/AECOUT  | A3         | Ο    | I <sup>2</sup> S mode: Digital audio data output PDM mode mono: AEC PDM output PDM mode stereo: Gain exchange between 2x devices                                           |

| INT           | A4         | 0    | interrupt output                                                                                                                                                           |

| GNDD          | <b>A</b> 5 | Р    | digital ground                                                                                                                                                             |

| OUTB          | A6         | 0    | inverting output                                                                                                                                                           |

| VDDP          | A7         | Р    | power supply voltage                                                                                                                                                       |

| BCK1          | B1         | I    | digital audio bit clock input 1 for I <sup>2</sup> S interface 1                                                                                                           |

| GNDD          | B2         | Р    | digital ground                                                                                                                                                             |

| DATAI3        | ВЗ         | I    | digital audio data input 3 for I <sup>2</sup> S interface 3                                                                                                                |

| RST           | B4         | I    | reset input                                                                                                                                                                |

| GNDP          | B5         | Р    | power ground                                                                                                                                                               |

| GNDP          | B6         | Р    | power ground                                                                                                                                                               |

| VDDP          | B7         | Р    | power supply voltage                                                                                                                                                       |

| DATAI2/PDMDAT | C1         | I    | I <sup>2</sup> S mode: Digital audio data input 2 for I <sup>2</sup> S interface 2                                                                                         |

|               |            |      | PDM mode: PDM audio data stream input                                                                                                                                      |

| GNDD          | C2         | Р    | digital ground                                                                                                                                                             |

| TEST4         | C3         | 0    | test signal input 4; for test purposes only, connect to PCB ground                                                                                                         |

| TEST5         | C4         | 0    | test signal input 5; for test purposes only, connect to PCB ground                                                                                                         |

| GNDD          | C5         | Р    | digital ground                                                                                                                                                             |

| OUTA          | C6         | 0    | non-inverting output                                                                                                                                                       |

| VDDP          | C7         | Р    | power supply voltage                                                                                                                                                       |

| WS2/AECCLK    | D1         | I    | I <sup>2</sup> S mode: Digital audio word select input 2 for I <sup>2</sup> S interface 2<br>PDM mode: PDM input clock used for AEC reference output<br>(in stereo)        |

| GNDD          | D2         | Р    | digital ground                                                                                                                                                             |

| TEST3         | D3         | 0    | test signal input 3; for test purposes only, connect to PCB ground                                                                                                         |

| TEST6         | D4         | 0    | test signal input 6; for test purposes only, connect to PCB ground                                                                                                         |

| GNDD          | D5         | Р    | digital ground                                                                                                                                                             |

| n.c.          | D6         | -    | not connected[1]                                                                                                                                                           |

| n.c.          | D7         | -    | not connected <sup>[1]</sup>                                                                                                                                               |

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

Table 3.

Pin description ...continued

| Symbol      | Pin | Туре | Description                                                                                          |

|-------------|-----|------|------------------------------------------------------------------------------------------------------|

| BCK2/PDMCLK | E1  | I    | I <sup>2</sup> S mode: Digital audio bit clock input 2 for I <sup>2</sup> S interface 2              |

|             |     |      | PDM mode: PDM clock input for audio data stream                                                      |

| AECOUT      | E2  | 0    | PDM stereo: AEC PDM output                                                                           |

|             |     |      | I <sup>2</sup> S mode or PDM mono mode: Pin is tristated internally; must be tied to GNDD externally |

| TEST2/WSM   | E3  | 0    | I <sup>2</sup> S mode: Test signal input 2; connect to PCB ground                                    |

|             |     |      | PDM mode: Master audio word select output for stereo gain exchange between 2x devices                |

| TEST7       | E4  | 0    | test signal input 7; for test purposes only, connect to PCB ground                                   |

| GNDB        | E5  | Р    | boosted ground                                                                                       |

| INB         | E6  | Р    | DC-to-DC boost converter input                                                                       |

| BST         | E7  | 0    | boosted supply voltage output                                                                        |

| SDA         | F1  | I/O  | I <sup>2</sup> C-bus data input/output                                                               |

| ADS1        | F2  | I    | address select input 1                                                                               |

| ADS2        | F3  | I    | address select input 2                                                                               |

| GNDD        | F4  | Р    | digital ground                                                                                       |

| GNDB        | F5  | Р    | boosted ground                                                                                       |

| INB         | F6  | Р    | DC-to-DC boost converter input                                                                       |

| BST         | F7  | 0    | boosted supply voltage output                                                                        |

| SCL         | G1  | I    | I <sup>2</sup> C-bus clock input                                                                     |

| VBAT        | G2  | Р    | battery supply voltage sense input                                                                   |

| VDDD        | G3  | Р    | digital supply voltage                                                                               |

| GNDD        | G4  | Р    | digital ground                                                                                       |

| GNDB        | G5  | Р    | boosted ground                                                                                       |

| INB         | G6  | Р    | DC-to-DC boost converter input                                                                       |

| BST         | G7  | 0    | boosted supply voltage output                                                                        |

<sup>[1]</sup> Can be used to simplify routing to pin OUTA (see  $\underline{\text{Table 3}}$ ).

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 8. Functional description

The TFA9891 is a highly efficient mono Bridge Tied Load (BTL) class-D audio amplifier with a sophisticated SpeakerBoost protection algorithm. <u>Figure 1</u> is a block diagram of the TFA9891.

In I2S mode, TFA9891 contains three I<sup>2</sup>S data inputs and one I<sup>2</sup>S data output. Two of the I<sup>2</sup>S inputs, DATAI1 and DATAI2, can be selected as the audio input stream. The third I<sup>2</sup>S input, DATAI3, is provided to support stereo applications. The selected WS/BCK signal is used to internally clock DATAI3 (at the output of the MUX controlled by ISEL; see Figure 1).

A 'pass-through' option allows one of the  $I^2S$  input interfaces to be connected directly to the  $I^2S$  output. It allows  $I^2S$  output slave device such as codec connected in parallel with TFA9891 to be routed directly to the audio host via  $I^2S$  output.

In PDM mode, the TFA9891 features one PDM input interface for audio stream and one PDM output interface to provide AEC voltage or current reference. It also has one I<sup>2</sup>S input (DATAI3) and one I<sup>2</sup>S output interface (DATAO). In this mode, the I<sup>2</sup>S input/output interfaces are dedicated to communication between two devices for gain and synchronization on stereo platforms.

Regardless of active mode (I<sup>2</sup>S or PDM), the I<sup>2</sup>S output signal on DATAO can be configured to transmit DSP output signal, amplifier output current information, DATAI3 left or right signal information (bypass) or amplifier gain information. The gain information can be used to facilitate communication between two devices in stereo applications.

A SpeakerBoost protection algorithm, running on a CoolFlux Digital Signal Processor (DSP) core maximizes the acoustical output of the speaker. The algorithm also limits membrane excursion and voice coil temperature to a safe level. The mechanical protection implemented guarantees that the speaker membrane excursion never exceeds its rated limit, to accuracy of 10 %. Thermal protection guarantees that the voice coil temperature never exceeds its rated limit, to accuracy of  $\pm 10$  °C. Furthermore, advanced signal processing ensures that the audio quality remains acceptable always.

The protection algorithm implements an adaptive loudspeaker model that is used to predict the extent of membrane excursion. The model is continuously updated to ensure that the protection scheme remains effective even when speaker parameter values change or the acoustic enclosure is modified.

Output sound pressure levels are boosted within given mechanical, thermal and quality limits. An optional bandwidth extension mode extends the low frequency response up to a predefined limit before maximizing the output level. This mode is suitable for listening to high-quality music in quiet environments.

The frequency response of the TFA9891 can be modified via ten fully programmable cascaded second-order biquad filters. The first two biquads are processed with 48-bit double precision; biquads 3 to 8 are processed with 24-bit single precision.

At low battery voltage levels, the gain is automatically reduced to limit battery current. The SpeakerBoost protection algorithm or the host application (external) controls the output volume. In the latter case, the boost features of the SpeakerBoost protection algorithm must be disabled to avoid neutralizing external volume control.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

The SpeakerBoost protection algorithm output is converted into two pulse width modulated (PWM) signals which are injected into the class-D audio amplifier. The 3-level PWM scheme supports filterless speaker drive.

An adaptive DC-to-DC converter boosts the battery supply voltage in line with the output of the SpeakerBoost protection algorithm. It switches to follower mode ( $V_{bst} = V_{BAT}$ ; no boost) when the audio output voltage is lower than the battery voltage.

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

# 9. Internal circuitry

Table 4. Internal circuitry

| Pin                           | Symbol                                            | Equivalent circuit                                                            |

|-------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------|

| C1, C4, D1, D3, E1, F2,<br>F3 | DATAI2, TEST5, WS2,<br>TEST3, BCK2, ADS1,<br>ADS2 | C1, C4, D1,<br>D3, E1, F2,<br>F3  ESD  GNDD (E4) 010aaa788                    |

| A1, A2, A4, B1, B3, E3,<br>G1 | WS1, DATAI1, INT,<br>BCK1, DATAI3, TEST2,<br>SCL, | A1, A2, B1<br>B3, E3, G1<br>ESD<br>ESD<br>GNDD (E4)<br>GNDP (B7)<br>010aaa789 |

| C3                            | TEST4                                             | C3 ————————————————————————————————————                                       |

| F1                            | SDA                                               | F1 ESD GNDD (E4) 010aaa791                                                    |

| A3, E2                        | DATAO, AECOUT                                     | A3 ————————————————————————————————————                                       |

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

Table 4.

Internal circuitry ...continued

| Pin                                                      | Symbol           | Equivalent circuit                                                                     |

|----------------------------------------------------------|------------------|----------------------------------------------------------------------------------------|

| A6, C6                                                   | OUTB, OUTA       | V <sub>DDP</sub> (B6)  A6, C6  GNDP (B7)  010aaa787                                    |

| E6, F6, G6                                               | i.c.             | SENSE (E6)  E6, F6, G6  GNDB (D7)  010aaa793                                           |

| A5, B2, B5, B6, C2, C5,<br>D2, D5, E5, F4, F5, G4,<br>G5 | GNDP, GNDB, GNDD | GNDD (A5, B2, C2, D2, D5, E2, F4, G4)  GNDP (B5, B6, C5)  GNDB (E5, F5, G5)  010aaa794 |

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 10. I<sup>2</sup>C-bus interface and register settings

The TFA9891 supports the 400 kHz I<sup>2</sup>C-bus microcontroller interface mode standard. The I<sup>2</sup>C-bus is used to control the TFA9891 and to transmit and receive data. The TFA9891 can only operate in I<sup>2</sup>C slave mode, as a slave receiver or as a slave transmitter.

### 10.1 TFA9891 addressing

The TFA9891 is accessed via an 8-bit code; see <u>Table 5</u>. Bits 1 to 7 contain the device address. Bit 0 (R/W) indicates whether a read (1) or a write (0) operation has been requested. Four separate addresses are supported for stereo applications. Address selection is via pins ADS1 and ADS2. The levels on pins ADS1 and ADS2 determine the values of bits 1 and 2, respectively, of the device address, as detailed in <u>Table 5</u>. The generic address is independent of pins ADS1 and ADS2.

Table 5. Address selection via pins ADS1 and ADS2

| ADS2 pin voltage (V) | ADS1 pin voltage (V) | Address                    | Function       |

|----------------------|----------------------|----------------------------|----------------|

| 0                    | 0                    | 01101000                   | for write mode |

|                      |                      | 01101001                   | for read mode  |

| 0                    | $V_{DDD}$            | 01101010                   | for write mode |

|                      |                      | 01101011                   | for read mode  |

| $V_{DDD}$            | 0                    | 01101100                   | for write mode |

|                      |                      | 01101101                   | for read mode  |

| $V_{DDD}$            | $V_{DDD}$            | 01101110                   | for write mode |

|                      |                      | 01101111                   | for read mode  |

| don't care           | don't care           | 00011100 (generic address) | for write mode |

| don't care           | don't care           | 00011101 (generic address) | for read mode  |

### 10.2 I<sup>2</sup>C-bus write cycle

The sequence of events that is followed when writing data to the I<sup>2</sup>C-bus registers of TFA9891 is specified in <u>Table 6</u>. 1 byte is transmitted at a time. Each register stores 2 bytes of data. Data is always written in byte pairs. Data transfer is always MSB first.

The write cycle sequence using SDA is as follows:

- The microcontroller asserts a start condition (S).

- The microcontroller transmits the 7-bit device address of the TFA9891, followed by the R/W bit set to 0.

- The TFA9891 asserts an acknowledge (A).

- The microcontroller transmits the 8-bit TFA9891 register address to which the first data byte is written.

- The TFA9891 asserts an acknowledge.

- The microcontroller transmits the first byte (the most significant byte).

- The TFA9891 asserts an acknowledge.

- The microcontroller transmits the second byte (the least significant byte).

- The TFA9891 asserts an acknowledge.

#### 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

• The microcontroller can either assert the stop condition (P) or continue transmitting data by sending another pair of data bytes, repeating the sequence from step 6. In the latter case, the targeted register address has been auto-incremented by the TFA9891.

Table 6. I<sup>2</sup>C-bus write cycle

| Start | TFA9891<br>address                 | R/W | ACK[1] | TFA9891 first register address | ACK[1] | MSB | ACK[1] | LSB | _ | More<br>data | Stop |

|-------|------------------------------------|-----|--------|--------------------------------|--------|-----|--------|-----|---|--------------|------|

| S     | 01101A <sub>2</sub> A <sub>1</sub> | 0   | Α      | ADDR                           | Α      | MS1 | Α      | LS1 | Α | <>           | Р    |

<sup>[1]</sup> ACK stands for acknowledge.

### 10.3 I<sup>2</sup>C-bus read cycle

The sequence of events that is followed when reading data from the I<sup>2</sup>C-bus registers of TFA9891 is specified in <u>Table 7</u>. 1 byte is transmitted at a time. Each of the registers stores 2 bytes of data. Data is always written in byte pairs. Data transfer is always MSB first.

The read cycle sequence using SDA is as follows:

- The microcontroller asserts a start condition (S)

- The microcontroller transmits the 7-bit device address of the TFA9891, followed by the R/W bit set to 0

- The TFA9891 asserts an acknowledge (A)

- The microcontroller transmits the 8 bit TFA9891 register address from which the first data byte is read

- The TFA9891 asserts an acknowledge

- The microcontroller asserts a repeated start (Sr)

- The microcontroller retransmits the device address followed by the R/W bit set to 1

- The TFA9891 asserts an acknowledge

- The TFA9891 transmits the first byte (the MSB)

- The microcontroller asserts an acknowledge

- The TFA9891 transmits the second byte (the LSB)

- The microcontroller asserts either an acknowledge or a negative acknowledge (NA)

- If the microcontroller asserts an acknowledge, TFA9891auto increments the target register address and steps 9 to 12 are repeated

- If the microcontroller asserts a negative acknowledge, the TFA9891 frees the I<sup>2</sup>C-bus and the microcontroller generates a stop condition (P)

Table 7. I<sup>2</sup>C-bus read cycle

| Start | TFA9891<br>address                 | R/W |   | First<br>register<br>addres<br>s | ACK |    | TFA9891<br>address                 | R/<br>W | ACK | MSB | ACK | LSB |   | More<br>data | ACK | Stop |

|-------|------------------------------------|-----|---|----------------------------------|-----|----|------------------------------------|---------|-----|-----|-----|-----|---|--------------|-----|------|

| S     | 01101A <sub>2</sub> A <sub>1</sub> | 0   | Α | ADDR                             | Α   | Sr | 11011A <sub>2</sub> A <sub>1</sub> | 1       | Α   | MS1 | Α   | LS1 | Α | <>           | NA  | Р    |

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

# 11. Limiting values

### Table 8. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                       | Conditions                              | Min  | Max   | Unit |

|------------------|---------------------------------|-----------------------------------------|------|-------|------|

| $V_{BAT}$        | battery supply voltage          | on pin VBAT                             | -0.3 | +5.5  | V    |

| V <sub>bst</sub> | boost voltage                   | on pin BST                              | -0.3 | +11   | V    |

| $V_{INB}$        | voltage on pin INB              | on pin INB                              | -0.3 | +11   | V    |

| $V_{DDP}$        | power supply voltage            | on pin VDDP                             | -0.3 | +11   | V    |

| $V_{DDD}$        | digital supply voltage          | on pin VDDD                             | -0.3 | +1.95 | V    |

| Tj               | junction temperature            |                                         | -    | +150  | °C   |

| T <sub>stg</sub> | storage temperature             |                                         | -55  | +150  | °C   |

| T <sub>amb</sub> | ambient temperature             |                                         | -40  | +85   | °C   |

| V <sub>ESD</sub> | electrostatic discharge voltage | according to Human Body Model (HBM)     | -2   | +2    | kV   |

|                  |                                 | according to Charged Device Model (CDM) | -500 | +500  | V    |

| Amplifier of     | output                          |                                         |      |       | •    |

| Vo               | output voltage                  | on pin OUTA and pin OUTB                | -0.3 | +11   | V    |

### 12. Thermal characteristics

#### Table 9. Thermal characteristics

| Symbol               | Parameter                                   | Conditions                   | Тур | Max | Unit |

|----------------------|---------------------------------------------|------------------------------|-----|-----|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | four layer application board | 40  | 60  | K/W  |

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 13. Characteristics

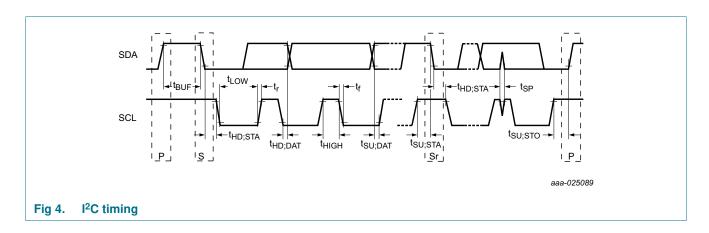

### 13.1 I<sup>2</sup>C timing characteristics

Table 10. I<sup>2</sup>C-bus interface characteristics; see Figure 4

All parameters are guaranteed for  $V_{BAT}=3.6~V;~V_{DDD}=1.8~V;~V_{DDP}=V_{bst}=9.5~V,~adaptive~boost~mode;~L_{BST}=1~\mu H^{[1]};~R_L=8~\Omega^{[1]};~L_L=40~\mu H^{[1]};~f_i=1~kHz;~f_s=48~kHz;~T_{amb}=25~^{\circ}C;~default~settings,~unless~otherwise~specified.$

| Symbol              | Parameter                                                         | Conditions          |     | Min                     | Тур | Max | Unit |

|---------------------|-------------------------------------------------------------------|---------------------|-----|-------------------------|-----|-----|------|

| f <sub>SCL</sub>    | SCL clock frequency                                               |                     |     | -                       | -   | 400 | kHz  |

| t <sub>LOW</sub>    | LOW period of the SCL clock                                       |                     |     | 1.3                     | -   | -   | μS   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                      |                     |     | 0.6                     | -   | -   | μS   |

| t <sub>r</sub>      | rise time                                                         | SDA and SCL signals | [2] | 20 + 0.1 C <sub>b</sub> | -   | -   | ns   |

| t <sub>f</sub>      | fall time                                                         | SDA and SCL signals | [2] | 20 + 0.1 C <sub>b</sub> | -   | -   | ns   |

| t <sub>HD;STA</sub> | hold time (repeated) START condition                              |                     | [3] | 0.6                     | -   | -   | μS   |

| t <sub>SU;STA</sub> | set-up time for a repeated START condition                        |                     |     | 0.6                     | -   | -   | μS   |

| t <sub>SU;STO</sub> | set-up time for STOP condition                                    |                     |     | 0.6                     | -   | -   | μS   |

| t <sub>BUF</sub>    | bus free time between a STOP and START condition                  |                     |     | 1.3                     | -   | -   | μS   |

| t <sub>SU;DAT</sub> | data set-up time                                                  |                     |     | 100                     | -   | -   | ns   |

| t <sub>HD;DAT</sub> | data hold time                                                    |                     |     | 0                       | -   | -   | μS   |

| t <sub>SP</sub>     | pulse width of spikes that must be suppressed by the input filter |                     |     | 0                       | -   | 50  | ns   |

| C <sub>b</sub>      | capacitive load for each bus line                                 |                     |     | -                       | -   | 400 | pF   |

- [1]  $L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance.

- [2] C<sub>b</sub> is the total capacitance of one bus line in pF. The maximum capacitive load for each bus line is 400 pF.

- [3] After this period, the first clock pulse is generated.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 13.2 I<sup>2</sup>S timing characteristics

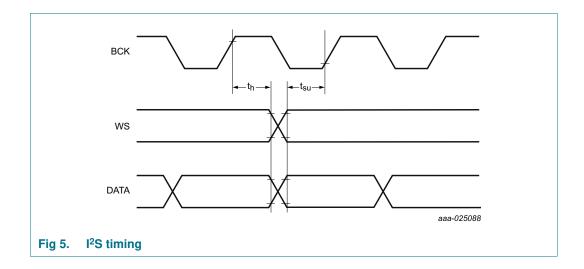

### Table 11. I<sup>2</sup>S bus interface characteristics; see Figure 5

All parameters are guaranteed for  $V_{BAT}=3.6~V;~V_{DDD}=1.8~V;~V_{DDP}=V_{bst}=9.5~V,~adaptive~boost~mode;~L_{BST}=1~\mu H_{L}^{[1]};~R_{L}=8~\Omega_{L}^{[1]};~L_{L}=40~\mu H_{L}^{[1]};~f_{i}=1~kHz;~f_{S}=48~kHz;~T_{amb}=25~^{\circ}C;~default~settings,~unless~otherwise~specified.$

| Symbol           | Parameter          | Conditions            |     | Min                     | Тур | Max             | Unit |

|------------------|--------------------|-----------------------|-----|-------------------------|-----|-----------------|------|

| fs               | sampling frequency | on pin WS             | [2] | 8                       | -   | 48              | kHz  |

| f <sub>clk</sub> | clock frequency    | on pin BCK            | [2] | $32\times f_{\text{s}}$ | -   | $64 \times f_s$ | Hz   |

| t <sub>su</sub>  | set-up time        | WS edge to BCK HIGH   | [3] | 10                      | -   | -               | ns   |

|                  |                    | DATA edge to BCK HIGH |     | 10                      | -   | -               | ns   |

| t <sub>h</sub>   | hold time          | BCK HIGH to WS edge   | [3] | 10                      | -   | -               | ns   |

|                  |                    | BCK HIGH to DATA edge |     | 10                      | -   | -               | ns   |

- [1]  $L_{BST}$  = boost converter inductance;  $R_L$  = load resistance;  $L_L$  = load inductance.

- [2] The I<sup>2</sup>S bit clock input (BCK) is used as a clock input for the DSP, as well as for the amplifier and the DC-to-DC converter. Both BCK and WS signals should be present for the clock to operate correctly.

- [3] This parameter is not tested during production; design guarantees the value and is checked during product validation.

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

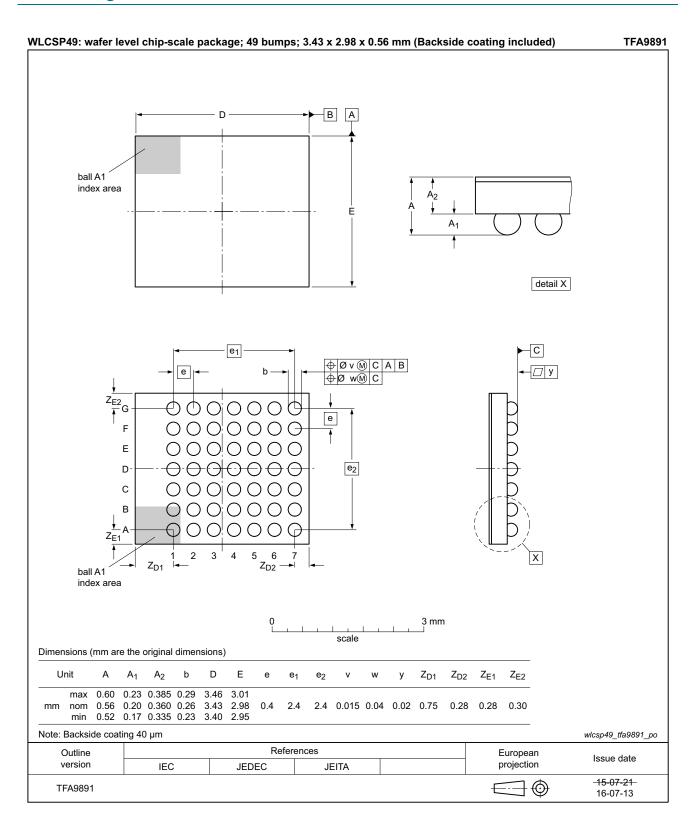

### 14. Package outline

Fig 6. Package outline TFA9891 (WLCSP49)

A9891 All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 15. Soldering of WLCSP packages

### 15.1 Introduction to soldering WLCSP packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering WLCSP (Wafer Level Chip-Size Packages) can be found in application note AN10439 "Wafer Level Chip Scale Package" and in application note AN10365 "Surface mount reflow soldering description".

Wave soldering is not suitable for this package.

All NXP WLCSP packages are lead-free.

### 15.2 Board mounting

Board mounting of a WLCSP requires several steps:

- 1. Solder paste printing on the PCB

- 2. Component placement with a pick and place machine

- 3. The reflow soldering itself

### 15.3 Reflow soldering

Key characteristics in reflow soldering are:

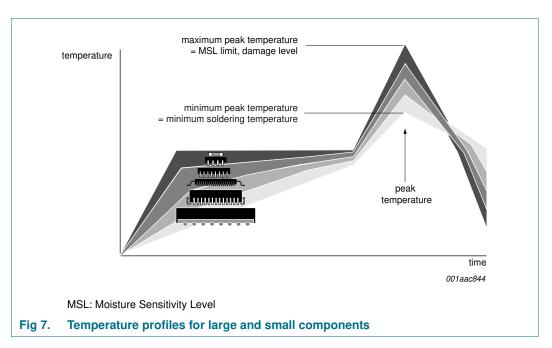

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 7</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues, such as smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature), and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic) while being low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 12.

Table 12. Lead-free process (from J-STD-020D)

| Package thickness (mm) | Package reflow temperature (°C) |             |        |  |  |

|------------------------|---------------------------------|-------------|--------|--|--|

|                        | Volume (mm³)                    |             |        |  |  |

|                        | < 350                           | 350 to 2000 | > 2000 |  |  |

| < 1.6                  | 260                             | 260         | 260    |  |  |

| 1.6 to 2.5             | 260                             | 250         | 245    |  |  |

| > 2.5                  | 250                             | 245         | 245    |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 7.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

For further information on temperature profiles, refer to application note *AN10365* "Surface mount reflow soldering description".

#### 15.3.1 Stand off

The stand off between the substrate and the chip is determined by:

- · The amount of printed solder on the substrate

- The size of the solder land on the substrate

- The bump height on the chip

The higher the stand off, the better the stresses are released due to TEC (Thermal Expansion Coefficient) differences between substrate and chip.

### 15.3.2 Quality of solder joint

A flip-chip joint is considered to be a good joint when the entire solder land has been wetted by the solder from the bump. The surface of the joint should be smooth and the shape symmetrical. The soldered joints on a chip should be uniform. Voids in the bumps after reflow can occur during the reflow process in bumps with high ratio of bump diameter to bump height, i.e. low bumps with large diameter. No failures have been found to be related to these voids. Solder joint inspection after reflow can be done with X-ray to monitor defects such as bridging, open circuits and voids.

#### 15.3.3 Rework

In general, rework is not recommended. By rework we mean the process of removing the chip from the substrate and replacing it with a new chip. If a chip is removed from the substrate, most solder balls of the chip will be damaged. In that case it is recommended not to re-use the chip again.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

Device removal can be done when the substrate is heated until it is certain that all solder joints are molten. The chip can then be carefully removed from the substrate without damaging the tracks and solder lands on the substrate. Removing the device must be done using plastic tweezers, because metal tweezers can damage the silicon. The surface of the substrate should be carefully cleaned and all solder and flux residues and/or underfill removed. When a new chip is placed on the substrate, use the flux process instead of solder on the solder lands. Apply flux on the bumps at the chip side as well as on the solder pads on the substrate. Place and align the new chip while viewing with a microscope. To reflow the solder, use the solder profile shown in application note *AN10365 "Surface mount reflow soldering description"*.

#### 15.3.4 Cleaning

Cleaning can be done after reflow soldering.

### 16. Abbreviations

Table 13. Abbreviations

| Acronym | Description                       |  |

|---------|-----------------------------------|--|

| AEC     | Acoustic Echo Cancellation        |  |

| API     | Application Programming Interface |  |

| DRC     | Dynamic Range Compressor          |  |

| PLL     | Phased Locked Loop                |  |

| PND     | Portable Navigation Devices       |  |

| OSR     | Over Sampling Ration              |  |

| RPC     | Remote Procedure Call             |  |

| WLCSP   | Wafer Level Chip-Size Package     |  |

9.5 V boosted audio system with adaptive sound maximizer and speaker protection

# 17. Revision history

### Table 14. Revision history

| Document ID     | Release date | Data sheet status        | Change notice | Supersedes |

|-----------------|--------------|--------------------------|---------------|------------|

| TFA9891_SDS v.1 | 20161221     | Product short data sheet | -             | -          |

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 18. Legal information

#### 18.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 18.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

#### 18.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

TFA9891

All information provided in this document is subject to legal disclaimers.

© NXP Semiconductors N.V. 2016. All rights reserved.

# 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from competent authorities.

**Quick reference data** — The Quick reference data is an extract of the product data given in the Limiting values and Characteristics sections of this document, and as such is not complete, exhaustive or legally binding.

Non-automotive qualified products — Unless this data sheet expressly states that this specific NXP Semiconductors product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NXP Semiconductors accepts no liability for inclusion and/or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NXP Semiconductors' warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond

NXP Semiconductors' specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NXP Semiconductors for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NXP Semiconductors' standard warranty and NXP Semiconductors' product specifications.

**Translations** — A non-English (translated) version of a document is for reference only. The English version shall prevail in case of any discrepancy between the translated and English versions.

#### 18.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

I2C-bus — logo is a trademark of NXP B.V.

CoolFlux — is a trademark of NXP B.V.

CoolFlux DSP — is a trademark of NXP B.V.

### 19. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

**TFA9891 NXP Semiconductors**

### 9.5 V boosted audio system with adaptive sound maximizer and speaker protection

### 20. Contents

| 1                 | General description                                        |

|-------------------|------------------------------------------------------------|

| 2                 | Features and benefits 2                                    |

| 3                 | Applications                                               |

| 4                 | Quick reference data                                       |

| 5                 | Ordering information 3                                     |

| 6                 | Block diagram 4                                            |

| 7                 | Pinning information 5                                      |

| 7.1               | Pinning                                                    |

| 7.2               | Pin description 6                                          |

| 8                 | Functional description 8                                   |

| 9                 | Internal circuitry                                         |

| 10                | $I^2$ C-bus interface and register settings 12             |

| 10.1              | TFA9891 addressing                                         |

| 10.2              | I <sup>2</sup> C-bus write cycle                           |

| 10.3              | I <sup>2</sup> C-bus read cycle                            |

| 11                | Limiting values                                            |

| 12                | Thermal characteristics                                    |

| 13                | Characteristics                                            |

| 13.1              | I <sup>2</sup> C timing characteristics                    |

| 13.2              | I <sup>2</sup> S timing characteristics                    |

| 14                | Package outline                                            |

| 15                | Soldering of WLCSP packages                                |

| 15.1<br>15.2      | Introduction to soldering WLCSP packages 18 Board mounting |

| 15.2              | Reflow soldering                                           |

| 15.3.1            | Stand off                                                  |

| 15.3.2            | Quality of solder joint                                    |

| 15.3.3            | Rework                                                     |

| 15.3.4            | Cleaning                                                   |

| 16                | Abbreviations                                              |

| 17                | Revision history                                           |

| 18                | Legal information                                          |

| 18.1              | Data sheet status                                          |

| 18.2              | Definitions                                                |

| 18.3<br>18.4      | Disclaimers                                                |

| 18.4<br><b>19</b> |                                                            |

| . •               | Contact information                                        |

| 20                | Contents                                                   |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

© NXP Semiconductors N.V. 2016.

All rights reserved.

For more information, please visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 21 December 2016 Document identifier: TFA9891