Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

# 8 GBIT (1G $\times$ 8 BIT) CMOS NAND E<sup>2</sup>PROM

#### **DESCRIPTION**

The TH58NVG3S0HTA00 is a single 3.3V 8 Gbit (9,126,805,504 bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E²PROM) organized as (4096 + 256) bytes  $\times$  64 pages  $\times$  4096blocks. The device has two 4352-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 4352-byte increments. The Erase operation is implemented in a single block unit (256 Kbytes + 16 Kbytes: 4352 bytes  $\times$  64 pages).

The TH58NVG3S0HTA00 is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for command inputs. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density non-volatile memory data storage.

#### **FEATURES**

Organization

x8

Memory cell array  $4352 \times 128K \times 8 \times 2$

$\begin{array}{ll} \text{Register} & 4352 \times 8 \\ \text{Page size} & 4352 \text{ bytes} \\ \text{Block size} & (256\text{K} + 16\text{K}) \text{ bytes} \end{array}$

Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Page Copy, Multi Page Program, Multi Block Erase, Multi Page Copy, Multi Page Read

Mode control

Serial input/output Command control

Number of valid blocks

Min 4016 blocks Max 4096 blocks

Power supply

$V_{CC} = 2.7V$  to 3.6V

• Access time

Cell array to register 25 µs max

Serial Read Cycle 25 ns min (CL=50pF)

• Program/Erase time

Auto Page Program 300 µs/page typ. Auto Block Erase 2.5 ms/block typ.

Operating current

Read (25 ns cycle) 30 mA max. Program (avg.) 30 mA max Erase (avg.) 30 mA max Standby 100 µA max

Package

TSOP I 48-P-1220-0.50 (Weight: 0.54 g typ.)

• 8 bit ECC for each 512Byte is required.

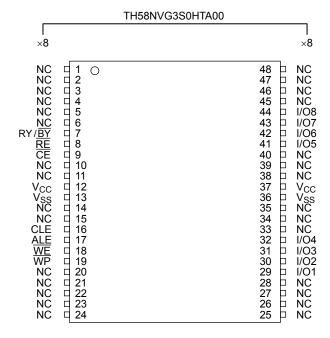

### **PIN ASSIGNMENT (TOP VIEW)**

# **PIN NAMES**

| I/O1 to I/O8    | I/O port             |

|-----------------|----------------------|

| CE              | Chip enable          |

| WE              | Write enable         |

| RE              | Read enable          |

| CLE             | Command latch enable |

| ALE             | Address latch enable |

| WP              | Write protect        |

| RY/BY           | Ready/Busy           |

| $V_{CC}$        | Power supply         |

| V <sub>SS</sub> | Ground               |

| NC              | No Connection        |

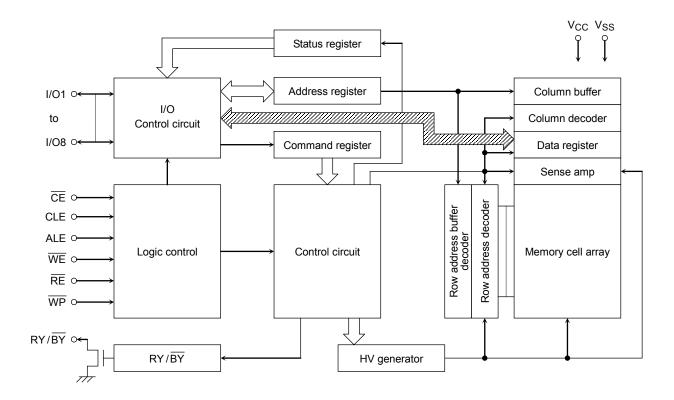

#### **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | RATING                       | VALUE                                               | UNIT |

|---------------------|------------------------------|-----------------------------------------------------|------|

| V <sub>CC</sub>     | Power Supply Voltage         | -0.6 to 4.6                                         | V    |

| VIN                 | Input Voltage                | -0.6 to 4.6                                         | V    |

| V <sub>I/O</sub>    | Input /Output Voltage        | $-0.6 \text{ to V}_{CC} + 0.3  (\le 4.6 \text{ V})$ | V    |

| P <sub>D</sub>      | Power Dissipation            | 0.3                                                 | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                                                 | °C   |

| T <sub>STG</sub>    | Storage Temperature          | –55 to 150                                          | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | 0 to 70                                             | °C   |

# **CAPACITANCE** \*(Ta = 25°C, f = 1 MHz)

| SYMB0L           | PARAMETER | CONDITION              | MIN | MAX | UNIT |

|------------------|-----------|------------------------|-----|-----|------|

| C <sub>IN</sub>  | Input     | $V_{IN} = 0 V$         | _   | 20  | pF   |

| C <sub>OUT</sub> | Output    | V <sub>OUT</sub> = 0 V |     | 20  | pF   |

<sup>\*</sup> This parameter is periodically sampled and is not tested for every device.

### **VALID BLOCKS**

| SYMBOL          | PARAMETER              | MIN  | TYP. | MAX  | UNIT   |

|-----------------|------------------------|------|------|------|--------|

| N <sub>VB</sub> | Number of Valid Blocks | 4016 | _    | 4096 | Blocks |

NOTE: The device occasionally contains unusable blocks. Refer to Application Note (13) toward the end of this document.

The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over lifetime

The number of valid blocks is on the basis of single plane operations, and this may be decreased with two plane operations.

#### RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL          | PARAMETER                | MIN       | TYP. | MAX                   | UNIT |

|-----------------|--------------------------|-----------|------|-----------------------|------|

| V <sub>CC</sub> | Power Supply Voltage     | 2.7       | _    | 3.6                   | ٧    |

| V <sub>IH</sub> | High Level input Voltage | Vcc x 0.8 | _    | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low Level Input Voltage  | -0.3*     | _    | Vcc x 0.2             | V    |

<sup>\* -2</sup> V (pulse width lower than 20 ns)

### DC CHARACTERISTICS (Ta = 0 to 70°C, V<sub>CC</sub> = 2.7 to 3.6V)

| SYMBOL                     | PARAMETER                   | CONDITION                                                                    | MIN       | TYP. | MAX | UNIT |

|----------------------------|-----------------------------|------------------------------------------------------------------------------|-----------|------|-----|------|

| I <sub>IL</sub>            | Input Leakage Current       | $V_{IN} = 0 V \text{ to } V_{CC}$                                            | _         | _    | ±20 | μА   |

| I <sub>LO</sub>            | Output Leakage Current      | V <sub>OUT</sub> = 0 V to V <sub>CC</sub>                                    | _         | _    | ±20 | μА   |

| I <sub>CCO1</sub>          | Serial Read Current         | $\overline{CE} = V_{IL}$ , $I_{OUT} = 0$ mA, tcycle = 25 ns                  |           |      | 30  | mA   |

| I <sub>CCO2</sub>          | Programming Current         | _                                                                            | _         |      | 30  | mA   |

| I <sub>CCO3</sub>          | Erasing Current             | _                                                                            | _         |      | 30  | mA   |

| Iccs                       | Standby Current             | $\overline{CE} = V_{CC} - 0.2 \text{ V}, \overline{WP} = 0 \text{ V/V}_{CC}$ |           |      | 100 | μА   |

| V <sub>OH</sub>            | High Level Output Voltage   | I <sub>OH</sub> = -0.1 mA                                                    | Vcc - 0.2 | _    | _   | ٧    |

| V <sub>OL</sub>            | Low Level Output Voltage    | I <sub>OL</sub> = 0.1 mA                                                     |           | _    | 0.2 | ٧    |

| I <sub>OL</sub><br>(RY/BY) | Output current of RY/BY pin | V <sub>OL</sub> = 0.2 V                                                      | _         | 4    | _   | mA   |

# <u>AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS</u> (Ta = 0 to $70^{\circ}$ C, $V_{CC}$ = 2.7 to 3.6V)

| SYMBOL               | PARAMETER                                             | MIN | MAX        | UNIT |

|----------------------|-------------------------------------------------------|-----|------------|------|

| t <sub>CLS</sub>     | CLE Setup Time                                        | 12  | _          | ns   |

| t <sub>CLH</sub>     | CLE Hold Time                                         | 5   | _          | ns   |

| t <sub>CS</sub>      | CE Setup Time                                         | 20  | _          | ns   |

| t <sub>CH</sub>      | CE Hold Time                                          | 5   | _          | ns   |

| t <sub>WP</sub>      | Write Pulse Width                                     | 12  | _          | ns   |

| t <sub>ALS</sub>     | ALE Setup Time                                        | 12  | _          | ns   |

| t <sub>ALH</sub>     | ALE Hold Time                                         | 5   | _          | ns   |

| t <sub>DS</sub>      | Data Setup Time                                       | 12  | _          | ns   |

| t <sub>DH</sub>      | Data Hold Time                                        | 5   | _          | ns   |

| t <sub>WC</sub>      | Write Cycle Time                                      | 25  | _          | ns   |

| t <sub>WH</sub>      | WE High Hold Time                                     | 10  | _          | ns   |

| t <sub>WW</sub>      | WP High to WE Low                                     | 100 | _          | ns   |

| t <sub>RR</sub>      | Ready to RE Falling Edge                              | 20  | _          | ns   |

| t <sub>RW</sub>      | Ready to WE Falling Edge                              | 20  | _          | ns   |

| t <sub>RP</sub>      | Read Pulse Width                                      | 12  | _          | ns   |

| t <sub>RC</sub>      | Read Cycle Time                                       | 25  | _          | ns   |

| t <sub>REA</sub>     | RE Access Time                                        | _   | 20         | ns   |

| tCEA                 | CE Access Time                                        | _   | 25         | ns   |

| t <sub>CLR</sub>     | CLE Low to RE Low                                     | 10  | _          | ns   |

| t <sub>AR</sub>      | ALE Low to RE Low                                     | 10  | _          | ns   |

| t <sub>RHOH</sub>    | RE High to Output Hold Time                           | 25  | _          | ns   |

| t <sub>RLOH</sub>    | RE Low to Output Hold Time                            | 5   | _          | ns   |

| t <sub>RHZ</sub>     | RE High to Output High Impedance                      | _   | 60         | ns   |

| t <sub>CHZ</sub>     | CE High to Output High Impedance                      | _   | 20         | ns   |

| t <sub>CSD</sub>     | CE High to ALE or CLE Don't Care                      | 0   | _          | ns   |

| t <sub>REH</sub>     | RE High Hold Time                                     | 10  | _          | ns   |

| t <sub>IR</sub>      | Output-High-impedance-to- RE Falling Edge             | 0   | _          | ns   |

| t <sub>RHW</sub>     | RE High to WE Low                                     | 30  | _          | ns   |

| t <sub>WHC</sub>     | WE High to CE Low                                     | 30  | _          | ns   |

| t <sub>WHR</sub>     | WE High to RE Low                                     | 60  | _          | ns   |

| t <sub>R</sub>       | Memory Cell Array to Starting Address                 | _   | 25         | μS   |

| t <sub>DCBSYR1</sub> | Data Cache Busy in Read Cache (following 31h and 3Fh) | _   | 25         | μs   |

| t <sub>DCBSYR2</sub> | Data Cache Busy in Page Copy (following 3Ah)          | _   | 30         | μs   |

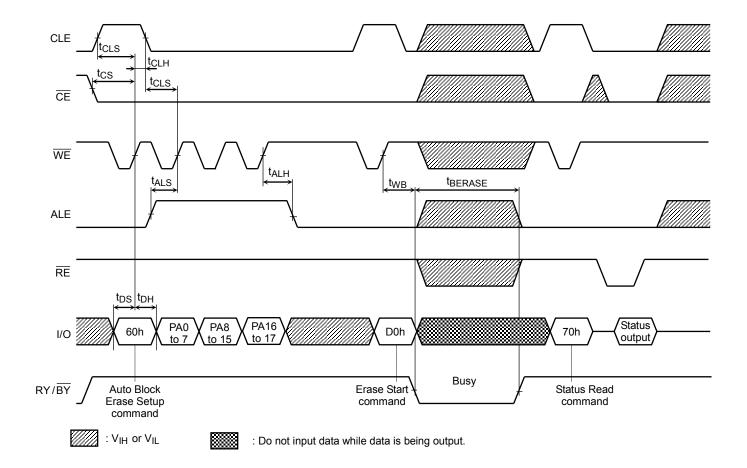

| t <sub>WB</sub>      | WE High to Busy                                       | _   | 100        | ns   |

| t <sub>RST</sub>     | Device Reset Time (Ready/Read/Program/Erase)          | _   | 5/5/10/500 | μS   |

<sup>\*1:</sup> tCLS and tALS can not be shorter than tWP

<sup>\*2:</sup> tCS should be longer than tWP + 8ns.

#### **AC TEST CONDITIONS**

| PARAMETER                      | CONDITION                      |  |

|--------------------------------|--------------------------------|--|

| PARAIVIETER                    | V <sub>CC</sub> : 2.7 to 3.6V  |  |

| Input level                    | V <sub>CC</sub> – 0.2 V, 0.2 V |  |

| Input pulse rise and fall time | 3 ns                           |  |

| Input comparison level         | Vcc / 2                        |  |

| Output data comparison level   | Vcc / 2                        |  |

| Output load                    | C <sub>L</sub> (50 pF) + 1 TTL |  |

Note: Busy to ready time depends on the pull-up resistor tied to the  $RY/\overline{BY}$  pin. (Refer to Application Note (9) toward the end of this document.)

#### PROGRAMMING AND ERASING CHARACTERISTICS

$(Ta = 0 \text{ to } 70^{\circ}C, V_{CC} = 2.7 \text{ to } 3.6V)$

| SYMBOL               | PARAMETER                                           | MIN | TYP. | MAX | UNIT | NOTES |

|----------------------|-----------------------------------------------------|-----|------|-----|------|-------|

| t <sub>PROG</sub>    | Average Programming Time                            | _   | 300  | 700 | μѕ   |       |

| t <sub>DCBSYW1</sub> | Data Cache Busy Time in Write Cache (following 11h) | _   | _    | 10  | μS   |       |

| t <sub>DCBSYW2</sub> | Data Cache Busy Time in Write Cache (following 15h) |     |      | 700 | μS   | (2)   |

| N                    | Number of Partial Program Cycles in the Same Page   | _   | _    | 4   |      | (1)   |

| t <sub>BERASE</sub>  | Block Erasing Time                                  |     | 2.5  | 5   | ms   |       |

<sup>(1)</sup> Refer to Application Note (12) toward the end of this document.

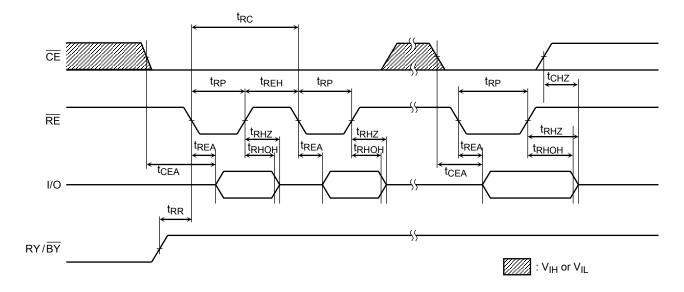

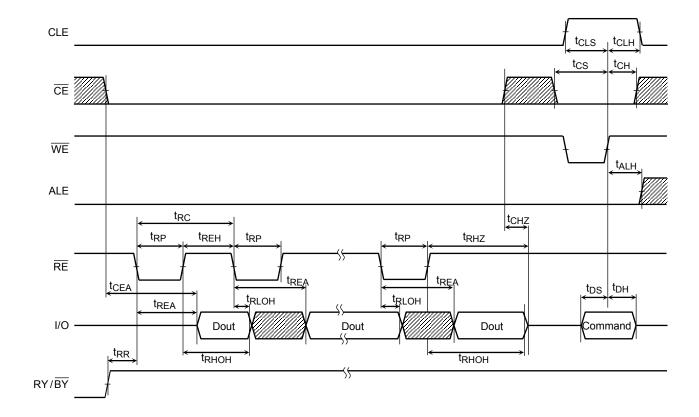

#### **Data Output**

When tREH is long, output buffers are disabled by /RE=High, and the hold time of data output depend on tRHOH (25ns MIN). On this condition, waveforms look like normal serial read mode.

When tREH is short, output buffers are not disabled by /RE=High, and the hold time of data output depend on tRLOH (5ns MIN). On this condition, output buffers are disabled by the rising edge of CLE,ALE,/CE or falling edge of /WE, and waveforms look like Extended Data Output Mode.

<sup>(2)</sup> t<sub>DCBSYW2</sub> depends on the timing between internal programming time and data in time.

# **TIMING DIAGRAMS**

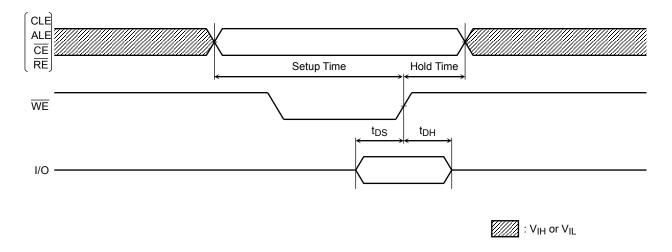

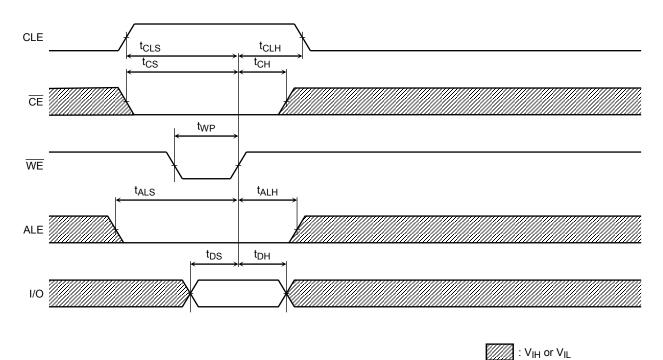

#### Latch Timing Diagram for Command/Address/Data

# Command Input Cycle Timing Diagram

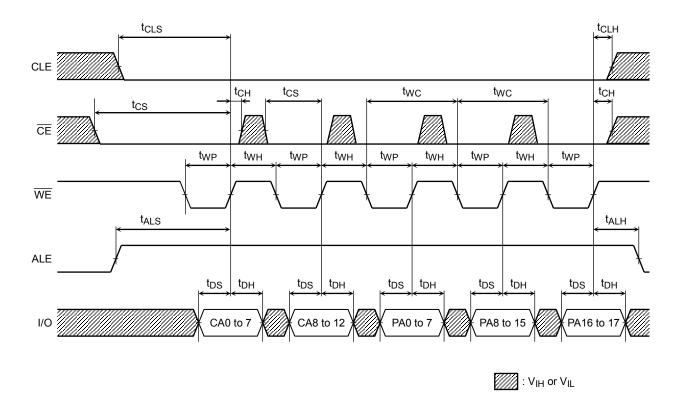

### Address Input Cycle Timing Diagram

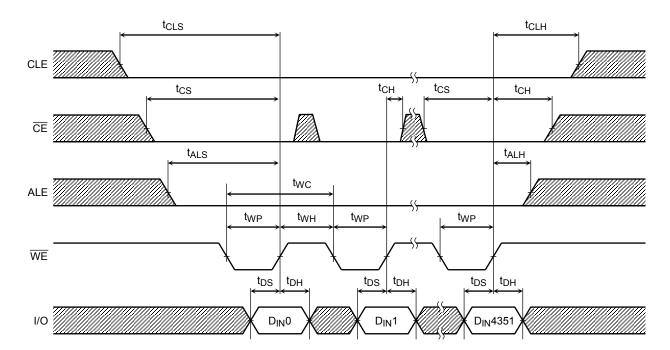

#### **Data Input Cycle Timing Diagram**

#### Serial Read Cycle Timing Diagram

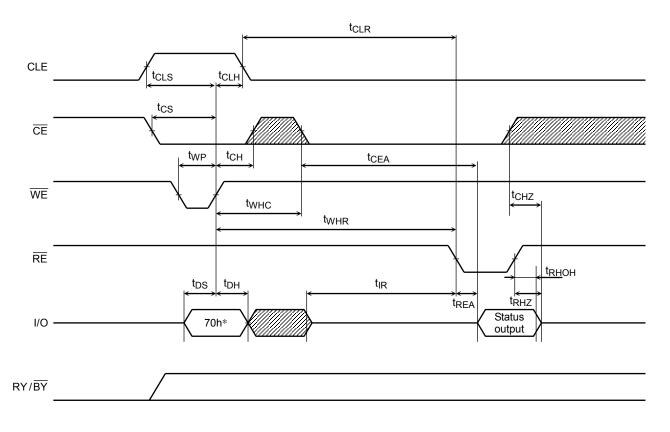

# Status Read Cycle Timing Diagram

<sup>\*: 70</sup>h represents the hexadecimal number

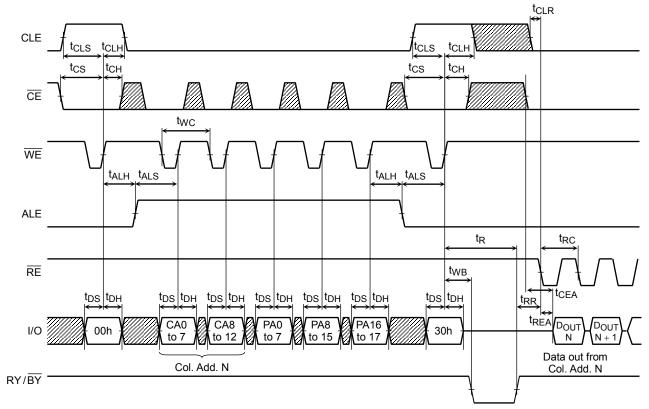

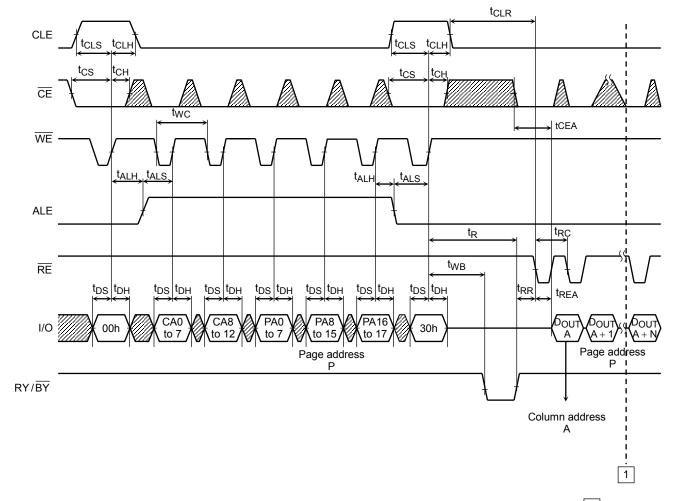

#### Read Cycle Timing Diagram

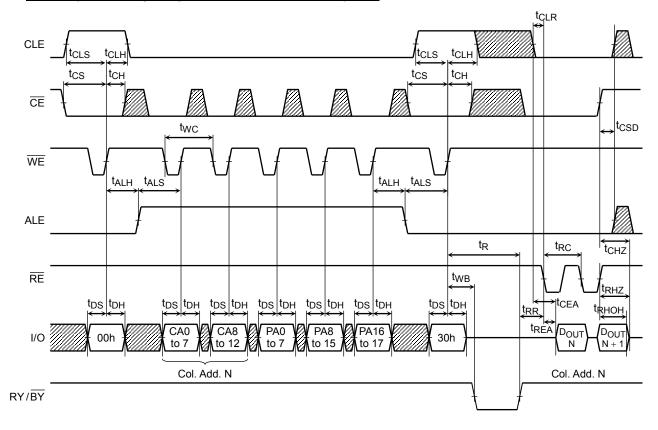

#### Read Cycle Timing Diagram: When Interrupted by CE

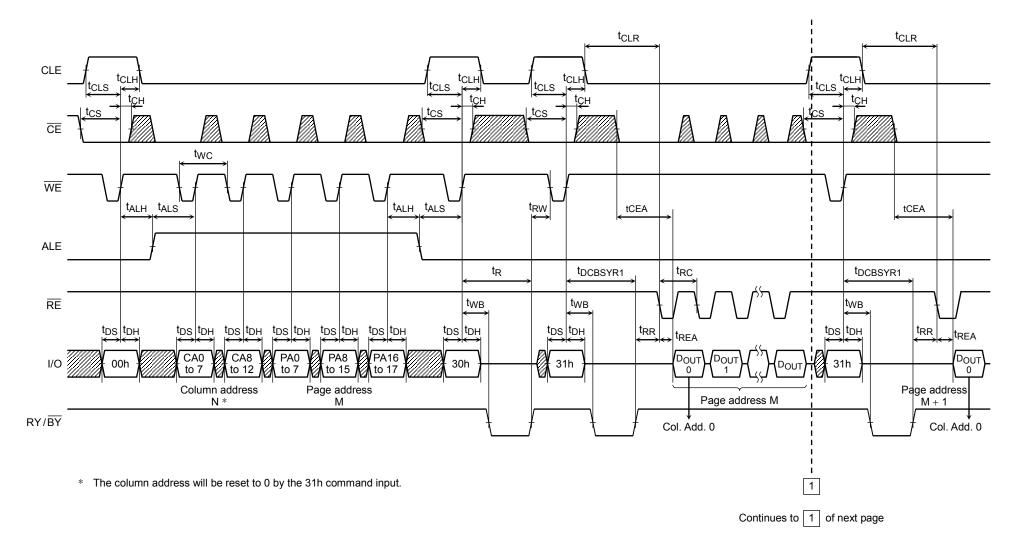

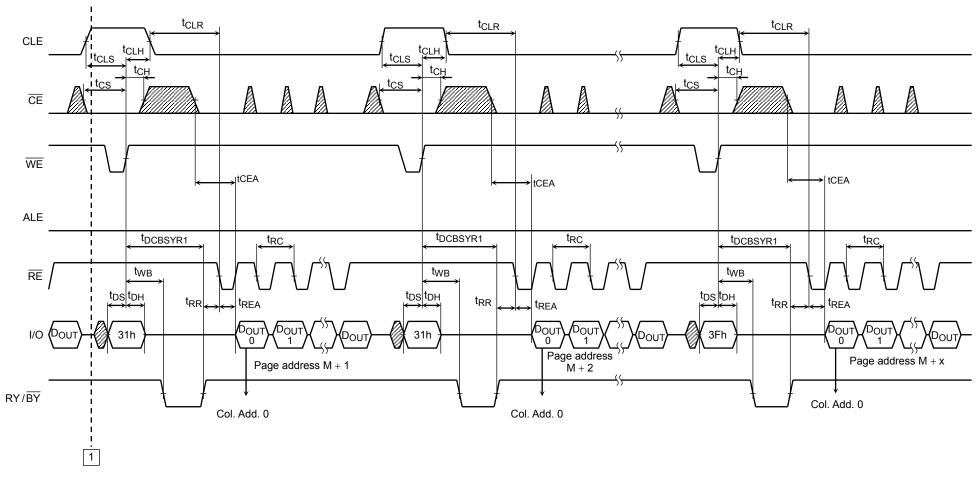

#### Read Cycle with Data Cache Timing Diagram (1/2)

11 2013-09-20C

#### Read Cycle with Data Cache Timing Diagram (2/2)

Continues from 1 of previous page

Make sure to terminate the operation with 3Fh command.

12 2013-09-20C

# Column Address Change in Read Cycle Timing Diagram (1/2)

Continues to 1 of next page

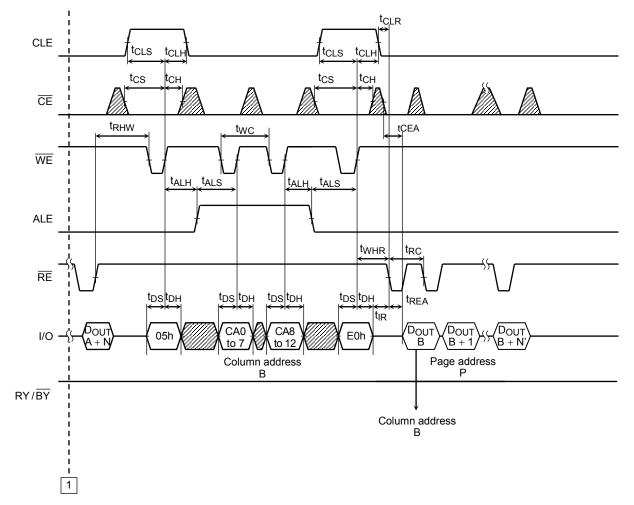

# Column Address Change in Read Cycle Timing Diagram (2/2)

Continues from 1 of previous page

#### **Data Output Timing Diagram**

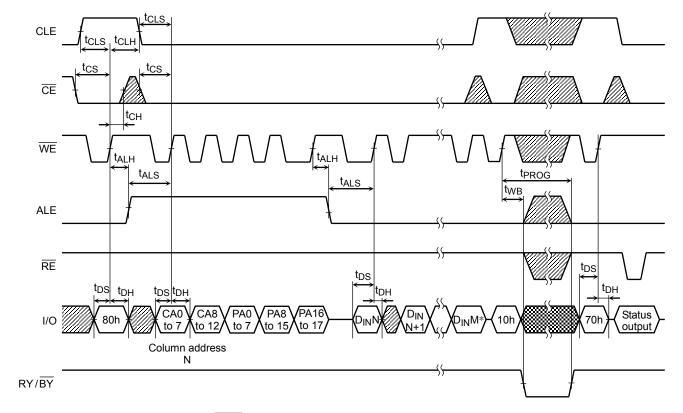

#### **Auto-Program Operation Timing Diagram**

: Do not input data while data is being output.

: V<sub>IH</sub> or V<sub>IL</sub>

\*) M: up to 4351 (byte input data for  $\times 8$  device).

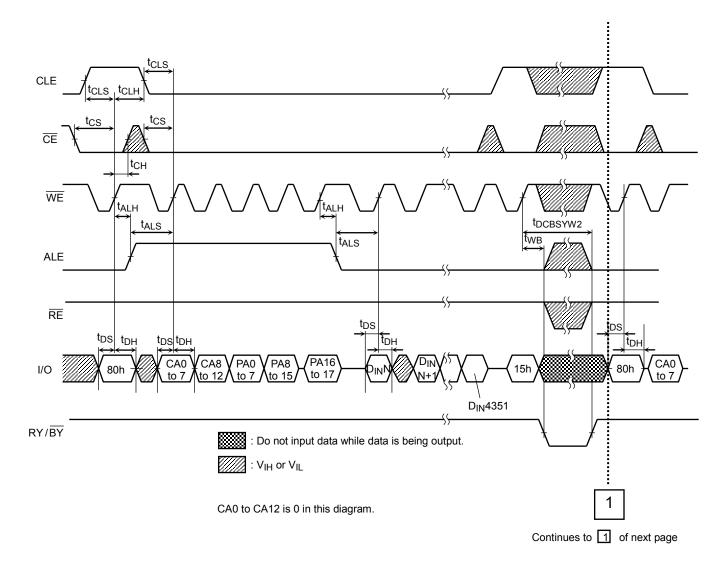

# Auto-Program Operation with Data Cache Timing Diagram (1/3)

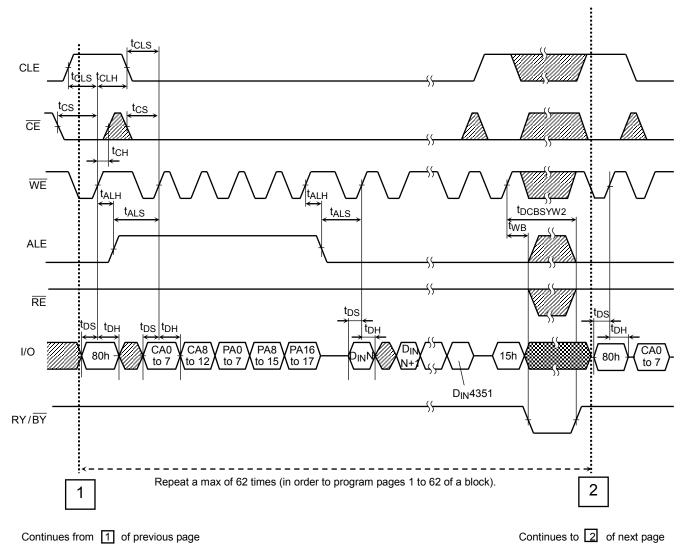

# Auto-Program Operation with Data Cache Timing Diagram (2/3)

Continues to 2 of next page

: Do not input data while data is being output.

:  $V_{IH}$  or  $V_{IL}$

Continues from 2 of previous page

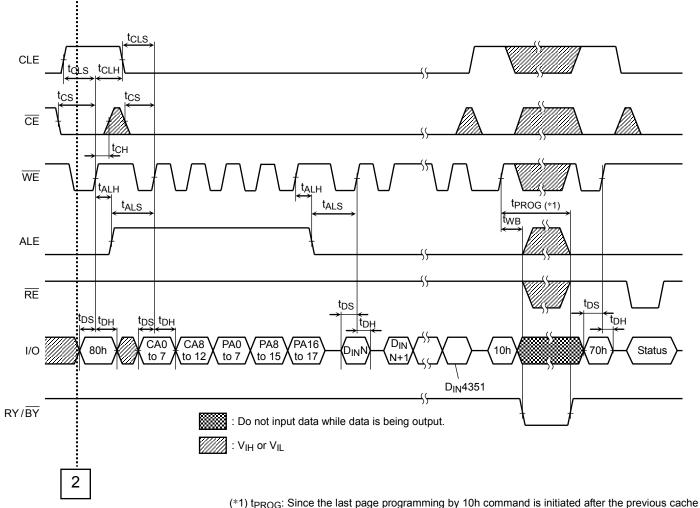

#### Auto-Program Operation with Data Cache Timing Diagram (3/3)

program, the t<sub>PROG</sub> during cache programming is given by the following equation.

$t_{PROG} = t_{PROG}$  of the last page +  $t_{PROG}$  of the previous page - A A = (command input cycle + address input cycle + data input cycle time of the last page)

If "A" exceeds the t<sub>PROG</sub> of previous page, t<sub>PROG</sub> of the last page is t<sub>PROG</sub> max.

(Note) Make sure to terminate the operation with 80h-10h- command sequence.

If the operation is terminated by 80h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

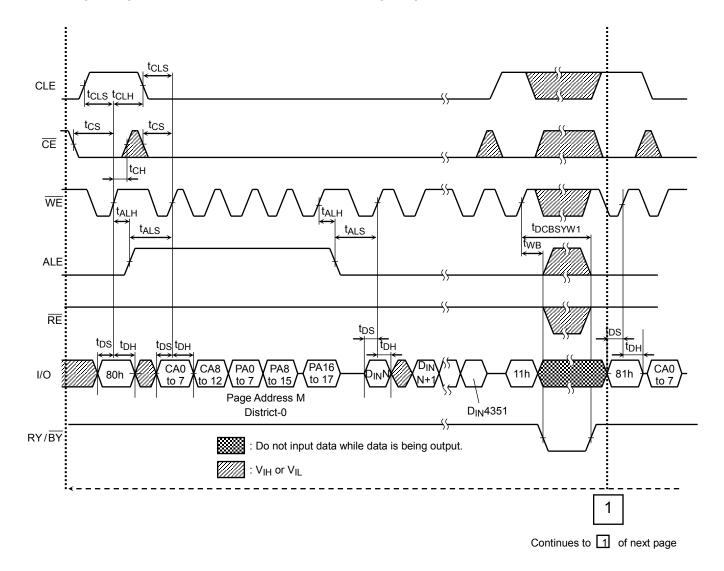

# Multi-Page Program Operation with Data Cache Timing Diagram (1/4)

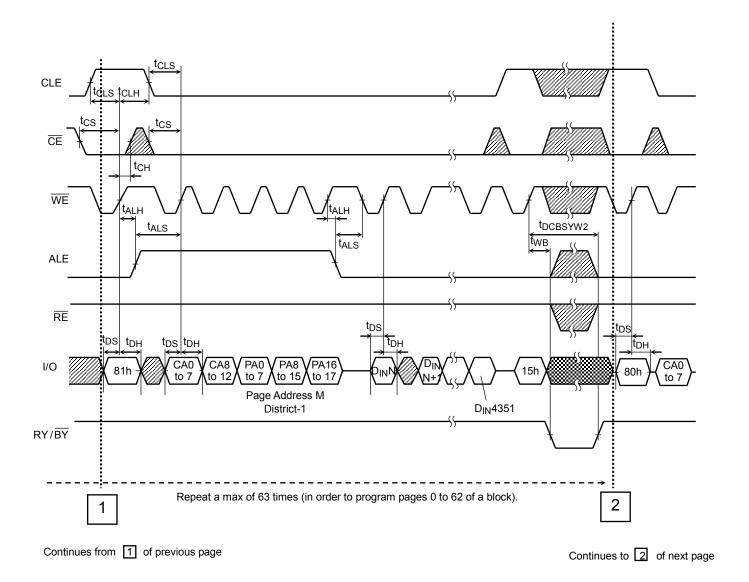

# Multi-Page Program Operation with Data Cache Timing Diagram (2/4)

**TOSHIBA**

: Do not input data while data is being output.

: V<sub>IH</sub> or V<sub>IL</sub>

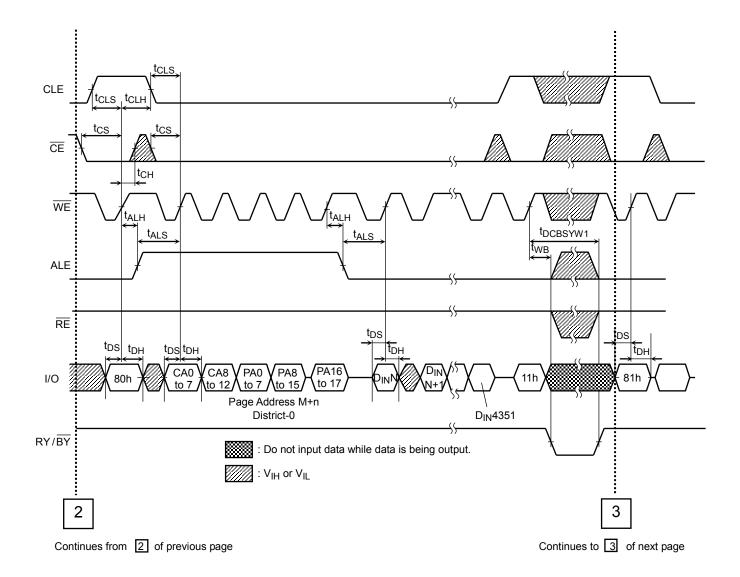

# Multi-Page Program Operation with Data Cache Timing Diagram (3/4)

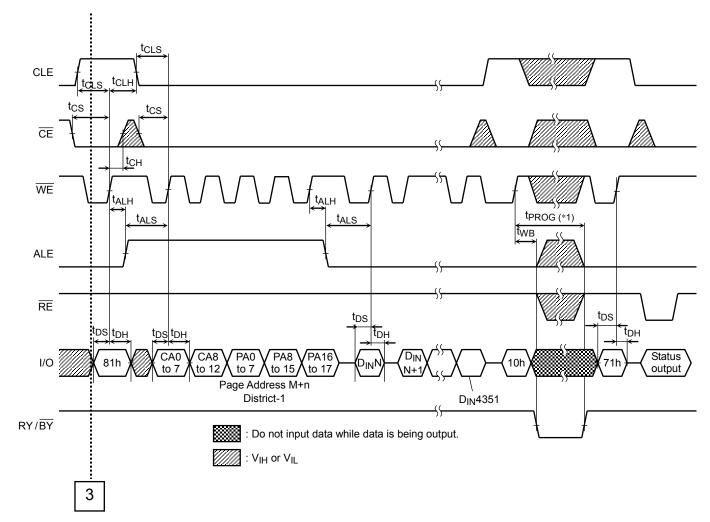

#### Multi-Page Program Operation with Data Cache Timing Diagram (4/4)

Continues from 3 of previous page

(\*1)  $t_{PROG}$ : Since the last page programming by 10h command is initiated after the previous cache program, the  $t_{PROG}$  during cache programming is given by the following equation.

$t_{PROG} = t_{PROG}$  of the last page  $+ t_{PROG}$  of the previous page - AA = (command input cycle + address input cycle + data input cycle time of the last page)

If "A" exceeds the t<sub>PROG</sub> of previous page, t<sub>PROG</sub> of the last page is t<sub>PROG</sub> max.

(Note) Make sure to terminate the operation with 81h-10h- command sequence.

If the operation is terminated by 81h-15h command sequence, monitor I/O 6 (Ready / Busy) by issuing Status Read command (70h) and make sure the previous page program operation is completed. If the page program operation is completed issue FFh reset before next operation.

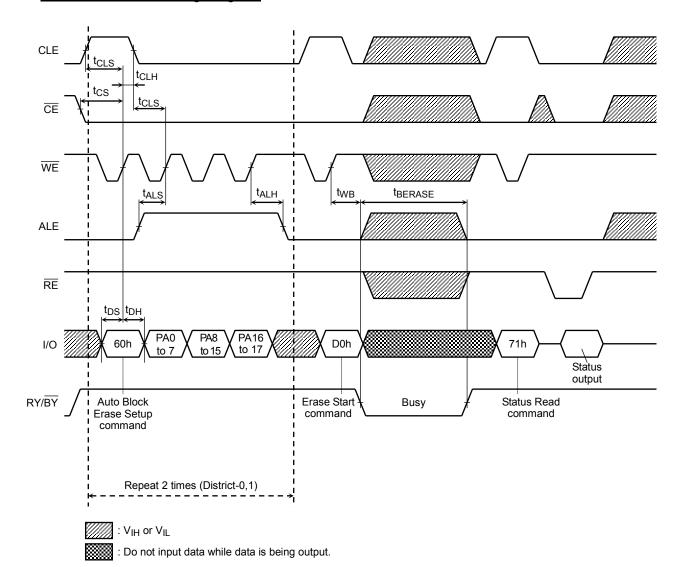

#### Auto Block Erase Timing Diagram

# Multi Block Erase Timing Diagram