Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# To Our Customers

Continuing it's rich tradition of partnering with high quality Japanese semiconductor suppliers, CEL is now partnering with THine from May of 2015 onwards.

## THC63LVDR84C

24bit Color LVDS Receiver (Rising Edge Strobe Output)

### **General Description**

The THC63LVDR84C receiver supports wide temperature range as -40 to +85°C, and wide frequency range as 8 to 112MHz.

The THC63LVDR84C converts the four LVDS data streams back into 24bits of LVCMOS data with Rising edge clock. At a transmit clock frequency of 112MHz, 24bits of RGB data and 4bits of timing and control data (HSYNC, VSYNC, DE, etc.) are transmitted at an effective rate of 3.1Gbps.

### **Application**

- · Medium and Small Size Panel

- · Security Camera

- · Multi Function Printer

- ·Machine Vision (Frame Grabber Board)

- · Medical Equipment Monitor

#### **Features**

- •1:7 LVDS to LVCMOS Deserializer

- •Operating Temperature Range: -40 to +85°C

- ·No Special Start-up Sequence Required

- Spread Spectrum Clocking Tolerant up to 100kHz Frequency Modulation and +/-2.5% Deviations

- •Pixel Clock Range: 8 to 112MHz

- · 56pin TSSOP Package

- ·Power Down Mode

- ·Rising Edge Strobe Output

- •EU RoHS Compliant

#### Recommended LVDS Transmitter ICs

- ·THC63LVDM83D

- ·THC63LVDM87

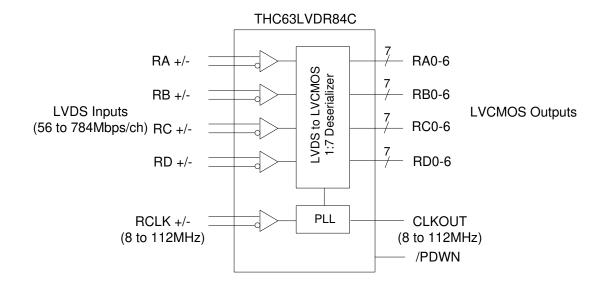

### **Block Diagram**

Figure 1. Block Diagram

1

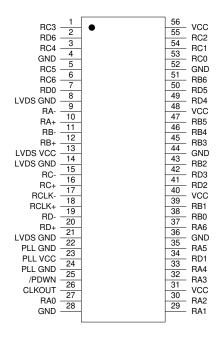

### Pin Diagram

Figure 2. Pin Diagram

#### Pin Description

| r III Descripti                                  | <u>UII</u>                                                                                                     |           |        |                                                                        |

|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----------|--------|------------------------------------------------------------------------|

| Pin Name                                         | Pin #                                                                                                          | Direction | Type   | Description                                                            |

| RA+, RA-                                         | 10, 9                                                                                                          |           |        |                                                                        |

| RB+, RB-                                         | 12, 11                                                                                                         |           |        | LVDS Data Inputs                                                       |

| RC+, RC-                                         | 16, 15                                                                                                         |           |        | LVD3 Data inputs                                                       |

| RD+, RD-                                         | 20, 19                                                                                                         |           |        |                                                                        |

| RCLK+,<br>RCLK-                                  | 18, 17                                                                                                         | Input     | LVDS   | LVDS Clock Inputs                                                      |

| RA0 ~ RA6<br>RB0 ~ RB6<br>RC0 ~ RC6<br>RD0 ~ RD6 | 27, 29, 30, 32, 33, 35, 37<br>38, 39, 43, 45, 46, 47, 51<br>53, 54, 55, 1, 3, 5, 6<br>7, 34, 41, 42, 49, 50, 2 | Output    | LVOMOO | Pixel Data Outputs                                                     |

| CLKOUT                                           | 26                                                                                                             |           | LVCMOS | Pixel Clock Output                                                     |

| /PDWN                                            | 25                                                                                                             | Input     |        | H : Normal Operation L : Power Down (All outputs are pulled to ground) |

| VCC                                              | 31, 40, 48, 56                                                                                                 |           |        | Power Supply Pins for LVCMOS outputs and digital circuitry             |

| GND                                              | 4, 28, 36, 44, 52                                                                                              |           | Davier | Ground Pins for LVCMOS outputs and digital circuitry                   |

| LVDS VCC                                         | 13                                                                                                             | ] -       | Power  | Power Supply Pins for LVDS inputs                                      |

| LVDS GND                                         | 8, 14, 21                                                                                                      |           |        | Ground Pins for LVDS inputs                                            |

| PLL VCC                                          | 23                                                                                                             |           |        | Power Supply Pins for PLL circuitry                                    |

| PLL GND                                          | 22, 24                                                                                                         |           |        | Ground Pins for PLL circuitry                                          |

Table 1. Pin Description

Absolute Maximum Ratings

| Parameter                               | Min  | Max       | Unit |

|-----------------------------------------|------|-----------|------|

| Supply Voltage (VCC, LVDS VCC, PLL VCC) | -0.3 | +4.0      | V    |

| LVCMOS Input Voltage                    | -0.3 | VCC + 0.3 | V    |

| LVCMOS Output Voltage                   | -0.3 | VCC + 0.3 | V    |

| LVDS Input Pin                          | -0.3 | VCC + 0.3 | V    |

| Junction Temperature                    | -    | +125      | °C   |

| Storage Temperature                     | -55  | +150      | °C   |

| Reflow Peak Temperature                 | -    | +260      | °C   |

| Reflow Peak Temperature Time            | -    | 10        | sec  |

| Maximum Power Dissipation @+25°C        | -    | 1.9       | W    |

**Table 2. Absolute Maximum Ratings**

**Recommended Operating Conditions**

| Symbol | Parameter                                  | Min | Тур | Max | Unit |

|--------|--------------------------------------------|-----|-----|-----|------|

| VCC33  | All Supply Voltage(VCC, LVDS VCC, PLL VCC) | 3.0 | -   | 3.6 | V    |

| Ta     | Operating Ambient Temperature              | -40 | +25 | +85 | °C   |

| PCLK   | RCLK and CLKOUT Clock Frequency            | 8   | -   | 112 | MHz  |

**Table 3. Recommended Operating Conditions**

<sup>&</sup>quot;Absolute Maximum Ratings" are those values beyond which the safety of the device can not be guaranteed. They are not meant to imply that the device should be operated at these limits. The tables of "Electrical Characteristics Table4, 5, 6, 7" specify conditions for device operation. "Absolute Maximum Rating" value also includes behavior of overshooting and undershooting.

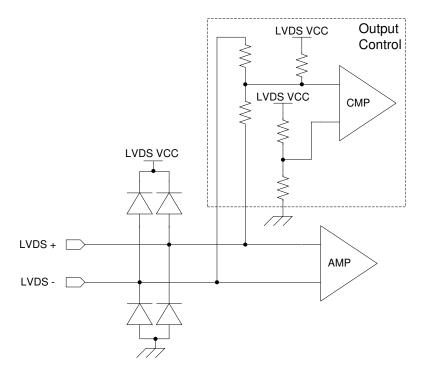

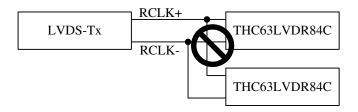

### Equivalent LVDS Input Schematic Diagram

Figure 3. LVDS Input Schematic Diagram

### Output Control

| /PDWN | RCLK +/- Input | LVCMOS Output        |

|-------|----------------|----------------------|

| Н     | Valid Clock    | Active Clock & Data  |

| Н     | Invalid Clock  | Unfixed Clock & Data |

| Н     | Open or Hi-z   | All Low              |

| I     | Don't Care     | All Low              |

**Table 4. LVCMOS Output Data Control**

### **Power Consumption**

Over recommended operating supply and temperature range unless otherwise specified

|                                   |                                  | 1 6 11 5 1                         | 0    |     | 1    |

|-----------------------------------|----------------------------------|------------------------------------|------|-----|------|

| Symbol                            | Parameter                        | Conditions                         | Typ* | Max | Unit |

| LVDS Receiver Operating Current V |                                  | CL=8pF, PCLK=65MHz,<br>VCC33=3.3V  | 55   | 70  | mA   |

| IRCCG                             | Gray Scale Pattern 16 (Fig.4)    | CL=8pF, PCLK=112MHz,<br>VCC33=3.3V | 90   | 110 | mA   |

|                                   | LVDS Receiver Operating Current  | CL=8pF, PCLK=65MHz,<br>VCC33=3.3V  | 90   | 110 | mA   |

| IRCCW                             | Worst Case Pattern(Fig.5)        | CL=8pF, PCLK=112MHz,<br>VCC33=3.3V | 130  | 160 | mA   |

| I <sub>RCCS</sub>                 | LVDS Receiver Power Down Current | /PDWN=L                            | -    | 500 | μΑ   |

<sup>\*</sup>Typ values are at the conditions of Ta = +25°C

**Table 5. Power Consumption**

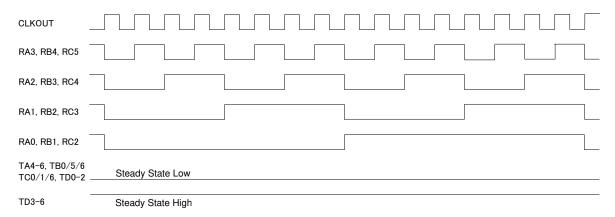

### 16 Grayscale Pattern

Figure 4. 16 Grayscale Pattern

### **Worst Case Pattern**

Figure 5. Worst Case Pattern

### **Electrical Characteristics**

### **LVDS Receiver DC Specifications**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol          | Parameter                            | Conditions                                  | Min  | Typ* | Max | Unit |

|-----------------|--------------------------------------|---------------------------------------------|------|------|-----|------|

| $V_{TH}$        | Differential Input High<br>Threshold | - RL=100Ω. VIC=+1.2V                        | -    | -    | 100 | mV   |

| V <sub>TL</sub> | Differential Input Low<br>Threshold  | RL=100Ω, VIC=+1.2V                          | -100 | -    | -   | mV   |

| I <sub>IN</sub> | Input Current                        | V <sub>IN</sub> =+2.4 / 0V<br>LVDS VCC=3.6V | -    | -    | ±30 | μА   |

**Table 6. LVDS Receiver DC Specifications**

### **LVCMOS DC Specifications**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol          | Parameter                 | Conditions                                                    | Min | Тур | Max | Unit |

|-----------------|---------------------------|---------------------------------------------------------------|-----|-----|-----|------|

| V <sub>IH</sub> | High Level Input Voltage  | -                                                             | 2.0 | -   | VCC | V    |

| $V_{IL}$        | Low Level Input Voltage   | -                                                             | GND | 1   | 0.8 | V    |

| V <sub>OH</sub> | High Level Output Voltage | I <sub>OH</sub> =-4mA (Data)<br>I <sub>OH</sub> =-8mA (Clock) | 2.4 | -   | -   | V    |

| V <sub>OL</sub> | Low Level Output Voltage  | I <sub>OL</sub> =4mA (Data)<br>I <sub>OL</sub> =8mA (Clock)   | -   | -   | 0.4 | V    |

| I <sub>IN</sub> | Input Current             | $GND \leq V_{IN} \leq VCC$                                    | -   | -   | ±10 | μА   |

**Table 7. LVCMOS DC Specifications**

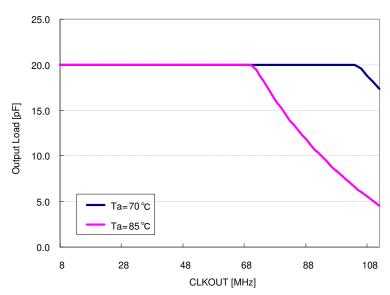

### **LVCMOS Output Load Limitation**

The output load is limited so that the junction temperature does not exceed 125°C.

Figure 6. LVCMOS Output Load Limitation

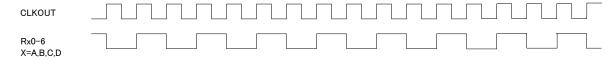

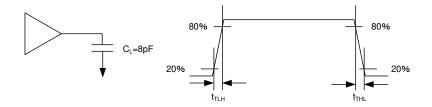

### **Switching Characteristics**

Over recommended operating supply and temperature range unless otherwise specified

| Symbol            | Parameter                          |             | Min                   | Typ*                | Max                   | Unit |

|-------------------|------------------------------------|-------------|-----------------------|---------------------|-----------------------|------|

| t <sub>RCP</sub>  | RCLK and CLKOUT Transition         | Time        | 8.92                  | Т                   | 125                   | ns   |

| t <sub>RCH</sub>  | LVCMOS CLKOUT High Time            |             | -                     | T/2                 | -                     | ns   |

| t <sub>RCL</sub>  | LVCMOS CLKOUT Low Time             |             | -                     | T/2                 | -                     | ns   |

| t <sub>RCD</sub>  | RCLK IN to CLKOUT Delay            |             | -                     | $(3/14+3) \times T$ | -                     | ns   |

| t <sub>RS</sub>   | LVCMOS Data Setup to CLKOUT        |             | 0.35×T-0.3            | -                   | -                     | ns   |

| t <sub>RH</sub>   | LVCMOS Data Hold from CLKOUT       |             | 0.45×T - 1.6          | ı                   | ı                     | ns   |

| t <sub>TLH</sub>  | LVCMOS Low to High Transition Time |             | -                     | 0.7                 | 1.0                   | ns   |

| t <sub>THL</sub>  | LVCMOS High to Low Transition Time |             | -                     | 0.7                 | 1.0                   | ns   |

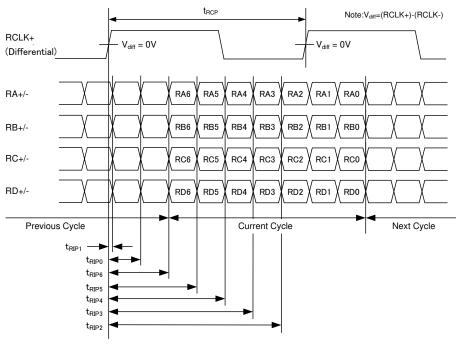

| tou               | LVDS Receiver Skew Margin          | PCLK=65MHz  | -0.55                 | -                   | 0.55                  | ne   |

| tsk               | LVD3 Neceiver Skew Margin          | PCLK=112MHz | -0.25                 | -                   | 0.25                  | ns   |

| t <sub>RIP1</sub> | LVDS Input Data Position0          |             | - t <sub>SK</sub>     | 0.0                 | + t <sub>SK</sub>     | ns   |

| t <sub>RIP0</sub> | LVDS Input Data Position1          |             | T/7- t <sub>SK</sub>  | T/7                 | $T/7+t_{SK}$          | ns   |

| t <sub>RIP6</sub> | LVDS Input Data Position2          |             | 2T/7- t <sub>SK</sub> | 2T/7                | 2T/7+ t <sub>SK</sub> | ns   |

| t <sub>RIP5</sub> | LVDS Input Data Position3          |             | 3T/7- t <sub>SK</sub> | 3T/7                | 3T/7+ t <sub>SK</sub> | ns   |

| t <sub>RIP4</sub> | LVDS Input Data Position4          |             | 4T/7- t <sub>SK</sub> | 4T/7                | 4T/7+ t <sub>SK</sub> | ns   |

| t <sub>RIP3</sub> | LVDS Input Data Position5          |             | 5T/7- t <sub>SK</sub> | 5T/7                | 5T/7+ t <sub>SK</sub> | ns   |

| t <sub>RIP2</sub> | LVDS Input Data Position6          |             | 6T/7- t <sub>SK</sub> | 6T/7                | 6T/7+ t <sub>SK</sub> | ns   |

| t <sub>RPLL</sub> | Phase Lock Loop Set                |             | -                     | -                   | 10.0                  | ms   |

<sup>\*</sup>Typ values are at the conditions of VCC33=3.3V and  $Ta = +25^{\circ}C$

Table 8. LVCMOS & LVDS Receiver AC Specifications

### **AC Timing Diagrams**

### **LVDS** Input

**Figure 7. LVDS Input Data Position**

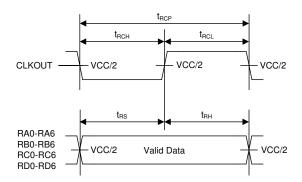

### **LVCMOS Output**

Figure 8. LVCMOS Output Load and Transition Time

Figure 9. LVCMOS Output Setup and Hold Time

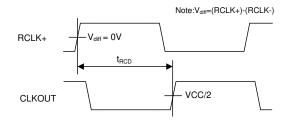

### **Input to Output Delay**

Figure 10.Input Clock to Output Clock Delay Time

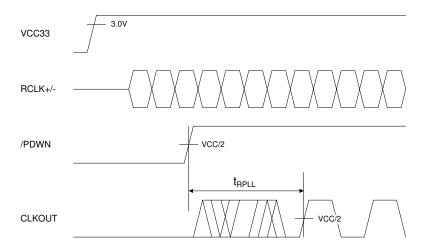

### **Phase Lock Loop Set Time**

Figure 11. PLL Lock Loop Set Time

### Application note

### Display Data Mapping Example

| Transmitter | VESA        | format      | JEIDA       | format      | Receiver |

|-------------|-------------|-------------|-------------|-------------|----------|

| Pin         | 6bit(18bpp) | 8bit(24bpp) | 6bit(18bpp) | 8bit(24bpp) | Pin      |

| TA0         | R0          | R0          | R2          | R2          | RA0      |

| TA1         | R1          | R1          | R3          | R3          | RA1      |

| TA2         | R2          | R2          | R4          | R4          | RA2      |

| TA3         | R3          | R3          | R5          | R5          | RA3      |

| TA4         | R4          | R4          | R6          | R6          | RA4      |

| TA5         | R5          | R5          | R7          | R7          | RA5      |

| TA6         | G0          | G0          | G2          | G2          | RA6      |

| TB0         | G1          | G1          | G3          | G3          | RB0      |

| TB1         | G2          | G2          | G4          | G4          | RB1      |

| TB2         | G3          | G3          | G5          | G5          | RB2      |

| TB3         | G4          | G4          | G6          | G6          | RB3      |

| TB4         | G5          | G5          | G7          | G7          | RB4      |

| TB5         | B0          | B0          | B2          | B2          | RB5      |

| TB6         | B1          | B1          | B3          | B3          | RB6      |

| TC0         | B2          | B2          | B4          | B4          | RC0      |

| TC1         | B3          | B3          | B5          | B5          | RC1      |

| TC2         | B4          | B4          | B6          | B6          | RC2      |

| TC3         | B5          | B5          | B7          | B7          | RC3      |

| TC4         | Hsync       | Hsync       | Hsync       | Hsync       | RC4      |

| TC5         | Vsync       | Vsync       | Vsync       | Vsync       | RC5      |

| TC6         | DE          | DE          | DE          | DE          | RC6      |

| TD0         | -           | R6          | -           | R0          | RD0      |

| TD1         | -           | R7          | -           | R1          | RD1      |

| TD2         | -           | G6          | -           | G0          | RD2      |

| TD3         | -           | G7          | -           | G1          | RD3      |

| TD4         | -           | B6          | -           | B0          | RD4      |

| TD5         | -           | B7          | -           | B1          | RD5      |

| TD6         | - TO 1      | N/A         | -           | N/A         | RD6      |

Note: Use TA to TC channels and open TD channel for 6bit application.

Table 9. Data Mapping for VESA & JEIDA RGB Color format

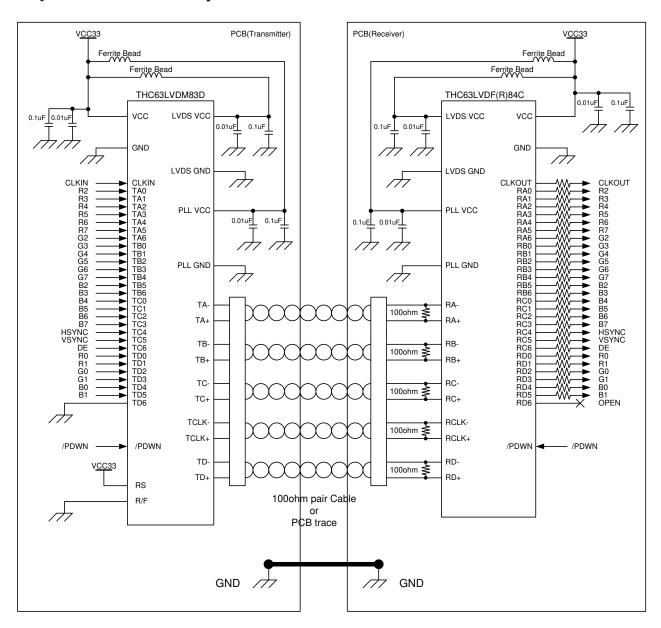

### **System Connection Example**

Figure 12. Connection Example with JEIDA Format

#### Notes

#### 1) Cable Connection and Disconnection

Do not connect and disconnect the LVDS cable, when the power is supplied to the system.

#### 2) GND Connection

Connect each GND of the PCB which LVDS-Tx and THC63LVDR84C on it. It is better for EMI reduction to place GND cable as close to LVDS cable as possible.

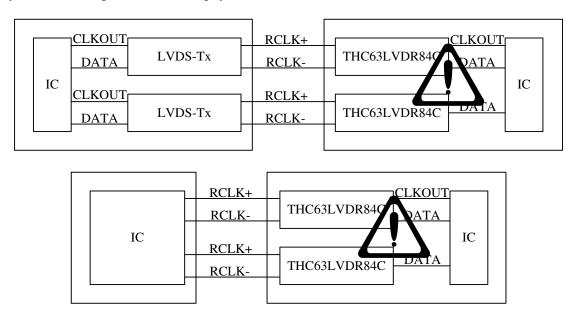

### 3) Multi Drop Connection

Multi drop connection is not recommended.

Figure 13. Multi Drop Connection

#### 4) Asynchronous use

Asynchronous using such as following systems is not recommended.

Figure 14. Asynchronous Use

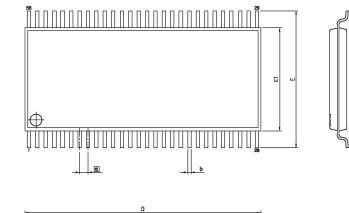

### **Package**

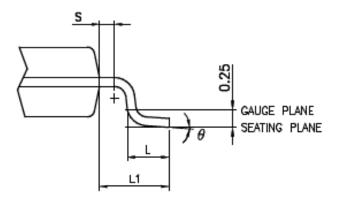

#### SYMBOLS MIN. 1.20 0.05 A1 A2 1.00 1,05 0.80 0.17 0.27 0.20 13.90 6.00 14.00 6.10 14.10 6.20 E1 8.10 BSC 0.50 BSC 1.00 REF 0.60 е

NOTES: 1.JEDEC OUTLINE : MO-153 EE REV.F

0.20

- 1.AEDEC OUTLINE: MO-153 EE REV.F

Z.DIMENSION O'P DOES NOT INCLUDE MOLD FLASH,

PROTRUSIONS OR CATE BURRS, MOLD FLASH, PROTRUSIONS

OR CATE BURRS SHALL NOT EXCEED 0.15 PER SIDE.

3.DIMENSION 'E1' DOES NOT INCLUDE INTERLEAD FLASH OR

PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL

NOT EXCEED 0.25 PER SIDE.

- NOT EXCELSE U.23 PER SIDE.

\*\*A-DIMENSION 'b', DOES NOT INCLUDE DAMBAR PROTRUSION.

\*\*ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 MM

TOTAL IN EXCESS OF THE 'b' DIMENSION AT MAXIMUM

MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE

LOWER RADIUS OF THE FOOT. MINIMUM SPACE BETWEEN

PROTRUSION AND ADJACENT LEAD IS 0.07 MM.

\*\*DIMENSIONS 'D' AND 'E1' TO BE DETERMINED AT DATUM

PLANE B.\*\*

Figure 15. Package Diagram

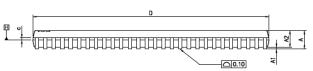

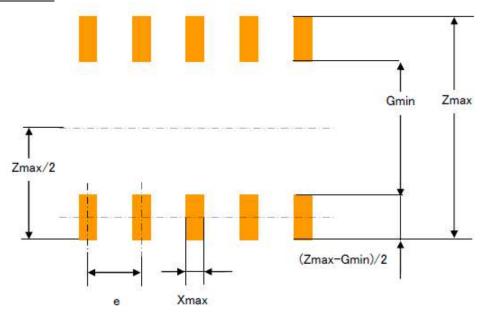

#### Reference Land Pattern

| Symbol | Calculation method | Units | Calculation Result |        |        |

|--------|--------------------|-------|--------------------|--------|--------|

|        |                    | Units | Level1             | Level2 | Level3 |

| Zmax   | Lmax+ 2JT          | mm    | 9.40               | 9.00   | 8.60   |

| Gmin   | Smin -2JH          | mm    | 5.40               | 5.70   | 6.00   |

| Xmax   | Wmax +2JS          | mm    | 0.47               | 0.370  | 0.27   |

| -      | (Zamx-Gmin)/2      | mm    | 2.00               | 1.65   | 1.30   |

<sup>\*</sup> We calculate the value based on Reflow Soldering Method.

(Printed Manufacturing Tolerance and Mounted Tolerance = 0mm)

Figure 16. Reference of Land Pattern

The recommendation mounting method of THine device is reflow soldering. The reference pattern is using the calculation result on condition of reflow soldering.

#### Notes

This land pattern design is a calculated value based on JEITA ET-7501.

Please take into consideration in an actual substrate design about enough the ease of mounting, the intensity of connection, the density of mounting, and the solder paste used, etc... The optimal land pattern size changes with these parameters. Please use the value shown by the land pattern as reference data.

#### **Notices and Requests**

- 1. The product specifications described in this material are subject to change without prior notice.

- 2. The circuit diagrams described in this material are examples of the application which may not always apply to the customer's design. We are not responsible for possible errors and omissions in this material. Please note if errors or omissions should be found in this material, we may not be able to correct them immediately.

- 3. This material contains our copyright, know-how or other proprietary. Copying or disclosing to third parties the contents of this material without our prior permission is prohibited.

- 4. Note that if infringement of any third party's industrial ownership should occur by using this product, we will be exempted from the responsibility unless it directly relates to the production process or functions of the product.

#### 5. Product Application

- 5.1 Application of this product is intended for and limited to the following applications: audio-video device, office automation device, communication device, consumer electronics, smartphone, feature phone, and amusement machine device. This product must not be used for applications that require extremely high-reliability/safety such as aerospace device, traffic device, transportation device, nuclear power control device, combustion chamber device, medical device related to critical care, or any kind of safety device.

- 5.2 This product is not intended to be used as an automotive part, unless the product is specified as a product conforming to the demands and specifications of ISO/TS16949 ("the Specified Product") in this data sheet. Thine Electronics, Inc. ("Thine") accepts no liability whatsoever for any product other than the Specified Product for it not conforming to the aforementioned demands and specifications.

- 5.3 THine accepts liability for demands and specifications of the Specified Product only to the extent that the user and THine have been previously and explicitly agreed to each other.

- 6. Despite our utmost efforts to improve the quality and reliability of the product, faults will occur with a certain small probability, which is inevitable to a semi-conductor product. Therefore, you are encouraged to have sufficiently redundant or error preventive design applied to the use of the product so as not to have our product cause any social or public damage.

- 7. Please note that this product is not designed to be radiation-proof.

- 8. Testing and other quality control techniques are used to this product to the extent THine deems necessary to support warranty for performance of this product. Except where mandated by applicable law or deemed necessary by THine based on the user's request, testing of all functions and performance of the product is not necessarily performed.

- 9. Customers are asked, if required, to judge by themselves if this product falls under the category of strategic goods under the Foreign Exchange and Foreign Trade Control Law.

- 10. The product or peripheral parts may be damaged by a surge in voltage over the absolute maximum ratings or malfunction, if pins of the product are shorted by such as foreign substance. The damages may cause a smoking and ignition. Therefore, you are encouraged to implement safety measures by adding protection devices, such as fuses.

## THine Electronics, Inc.

sales@thine.co.ip