# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 1. General description

The TJA1083 FlexRay node transceiver is compliant with the FlexRay Electrical Physical Layer specification V3.0.1 (see <u>Ref. 1</u>). In order to meet JASPAR the equirements, it implements the 'Increased voltage amplitude transmitter' functional class. It is primarily intended for communication systems operating at between 2.5 Mbit/s and 10 Mbit/s, and provides an advanced interface between the protocol controller and the physical bus in a FlexRay network. The TJA1083 offers an optimized solution for Electronic Control Unit (ECU) applications that do not need enhanced power management and are typically switched by the ignition or activated by a dedicated wake-up line.

The TJA1083 provides a differential transmit capability to the network and a differential receive capability to the FlexRay controller. It offers excellent ElectroMagnetic Compatibility (EMC) performance as well as high ElectroStatic Discharge (ESD) protection.

The TJA1083 actively monitors system performance using dedicated error and status information (readable by any microcontroller), as well as internal voltage and temperature monitoring.

# 2. Features and benefits

# 2.1 Optimized for time triggered communication systems

- Compliant with Electrical Physical Layer specification V3.0.1

- Meets JASPAR requirements as described in the 'Bus driver increased voltage amplitude transmitter' functional class

- Automotive product qualification in accordance with AEC-Q100

- Data transfer rates from 2.5 Mbit/s to 10 Mbit/s

- Supports 60 ns minimum bit time at 400 mV differential input voltage

- Very low ElectroMagnetic Emission (EME) to support unshielded cable

- Differential receiver with high common-mode range for excellent ElectroMagnetic Immunity (EMI)

- Auto I/O level adaptation to host controller supply voltage V<sub>IO</sub>

- Can be used in 14 V, 24 V and 48 V powered systems

- Instant transmitter shut-down interface (BGE pin)

# 2.2 Low-power management

- Very low current consumption in Standby mode

- Remote wake-up via a wake-up pattern or dedicated FlexRay data frames on the bus lines

# 2.3 Diagnosis and robustness

- Enhanced supply voltage monitoring for V<sub>CC</sub> and V<sub>IO</sub>

- Two error diagnosis modes:

- ◆ Status register readout via the Serial Peripheral Interface (SPI)

- Simple error indication via pin ERRN

- Overtemperature detection

- Short-circuit detection on bus lines

- Power-on flag

- Clamping diagnosis for pins TXEN and BGE

- Bus pins protected against ±6 kV ESD pulses according to IEC61000-4-2 and ±8 kV according to HBM

- Bus pins protected against transients in automotive environment (according to ISO 7637 class C)

- Bus pins short-circuit proof to battery voltage (14 V, 24 V and 48 V) and ground

- Maximum differential voltage between pins BP or BM and any other pin of  $\pm 60 \text{ V}$

- Bus lines remain passive when the transceiver is not powered

- No reverse currents from the digital input pins to V<sub>IO</sub> or V<sub>CC</sub> when the transceiver is not powered

# 2.4 Functional classes according to FlexRay Electrical Physical Layer specification V3.0.1

- Bus driver increased voltage amplitude transmitter

- Bus driver bus guardian control interface

- Bus driver logic level adaptation

- Bus driver remote wake-up

# 3. Ordering information

#### Table 1.Ordering information

| Type number | Package |                                                                        |          |  |  |

|-------------|---------|------------------------------------------------------------------------|----------|--|--|

|             | Name    | Description                                                            | Version  |  |  |

| TJA1083TT   | TSSOP14 | plastic thin shrink small outline package; 14 leads; body width 4.4 mm | SOT402-1 |  |  |

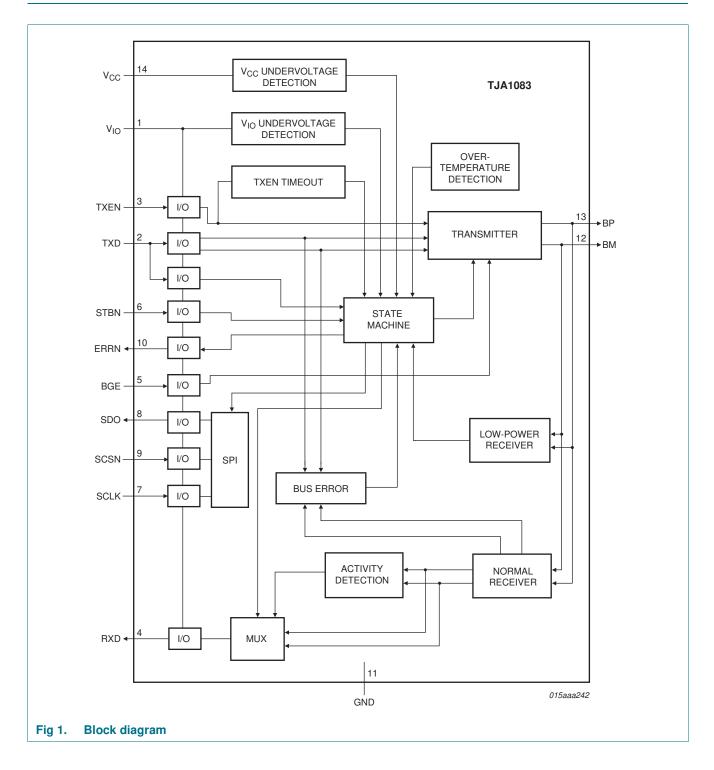

# 4. Block diagram

TJA1083 Product data sheet

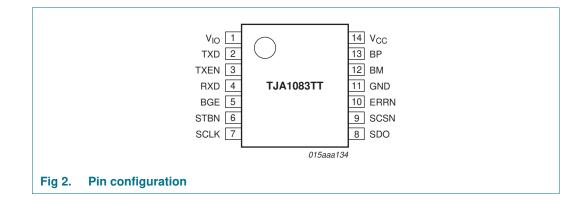

# 5. Pinning information

# 5.1 Pinning

# 5.2 Pin description

# Table 2. Pin description

| Symbol          | Pin | Туре | Description                                                                     |

|-----------------|-----|------|---------------------------------------------------------------------------------|

| V <sub>IO</sub> | 1   | Р    | supply voltage for $V_{\text{IO}}$ voltage level adaptation                     |

| TXD             | 2   | I    | transmit data input; internal pull-down                                         |

| TXEN            | 3   | I    | transmitter enable input; when HIGH transmitter disabled; internal pull-up      |

| RXD             | 4   | 0    | receive data output                                                             |

| BGE             | 5   | Ι    | bus guardian enable input; when LOW transmitter disabled; internal pull-down    |

| STBN            | 6   | I    | mode control input; transceiver in Normal mode when HIGH;<br>internal pull-down |

| SCLK            | 7   | I    | SPI clock signal; internal pull-up                                              |

| SDO             | 8   | 0    | SPI data output                                                                 |

| SCSN            | 9   | I    | SPI chip select input; internal pull-up/pull-down                               |

| ERRN            | 10  | 0    | error diagnosis output and wake-up indication                                   |

| GND             | 11  | Ρ    | ground                                                                          |

| BM              | 12  | I/O  | bus line minus                                                                  |

| BP              | 13  | I/O  | bus line plus                                                                   |

| V <sub>CC</sub> | 14  | Р    | supply voltage (+5 V)                                                           |

|                 |     |      |                                                                                 |

# 6. Functional description

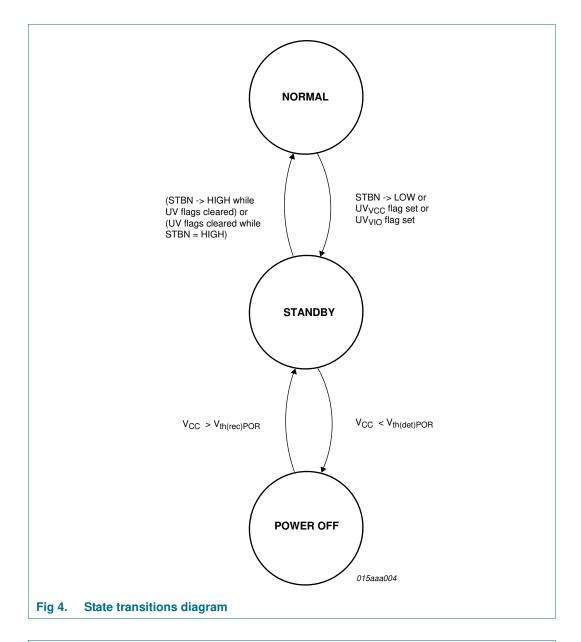

# 6.1 Power modes

The TJA1083 features three power modes: Normal, Standby and Power-off. Normal and Standby modes can be selected via the STBN input (HIGH for Normal mode) once the transceiver has been powered up. See <u>Table 3</u> for a detailed description of pin signaling in the three power modes.

| IUAIUUU | TJ | <b>A1</b> | 083 |

|---------|----|-----------|-----|

|---------|----|-----------|-----|

| Mode      | STRN | UV at                | UV                    | ERRN                               | 1                                    | RXD                                             |                                      | SDO                                        | Biasing             | UV-det   | Trans-    | Low-                     |

|-----------|------|----------------------|-----------------------|------------------------------------|--------------------------------------|-------------------------------------------------|--------------------------------------|--------------------------------------------|---------------------|----------|-----------|--------------------------|

| Mode      | STBN | V <sub>IO</sub>      | at<br>V <sub>CC</sub> |                                    | HIGH                                 | LOW                                             | HIGH                                 | 300                                        | BP, BM              | UV-det   | mitter    | power<br>receiver        |

| Normal    | HIGH | no                   | no                    | error<br>flag<br>set               | error<br>flag<br>reset               | bus<br>DATA<br>_0                               | bus<br>DATA_1<br>or idle             | high-<br>impedance<br>(in simple           | V <sub>CC</sub> / 2 |          | d enabled | enabled <mark>[1]</mark> |

| Standby   | LOW  | no                   | no                    | wake<br>flag<br>set                | wake<br>flag<br>reset                | wake<br>flag<br>set                             | wake<br>flag<br>reset                | error<br>indication<br>mode) or<br>enabled | GND                 |          | disabled  | enabled <mark>[2]</mark> |

|           | LOW  | no                   | yes <mark>[3]</mark>  | wake<br>flag<br>set <sup>[4]</sup> | wake<br>flag<br>reset <sup>[4]</sup> | wake<br>flag<br>set <mark><sup>[4]</sup></mark> | wake<br>flag<br>reset <sup>[4]</sup> | (in SPI<br>mode)                           |                     |          |           | disabled                 |

|           | HIGH | no                   | yes <mark>[3]</mark>  | error<br>flag<br>set               | error<br>flag<br>reset               | wake<br>flag<br>set <mark><sup>[4]</sup></mark> | wake<br>flag<br>reset <sup>[4]</sup> |                                            |                     |          |           |                          |

|           | Х    | yes <mark>[5]</mark> | no                    | LOW                                |                                      | LOW                                             |                                      | high-                                      |                     |          |           | enabled <mark>[2]</mark> |

|           | Х    | yes <mark>[5]</mark> | yes <mark>[3]</mark>  | LOW                                |                                      | LOW                                             |                                      | impedance                                  |                     |          |           | disabled                 |

| Power-off | Х    | χ <u>[5]</u>         | yes                   | high-<br>imped                     | lance                                | HIGH                                            |                                      |                                            | GND <sup>[6]</sup>  | disabled |           | disabled                 |

#### Table 3. Pin signaling in the different power modes

[1] The wake flag is set if a valid wake-up event is detected while switching to Standby mode.

[2] The wake flag is set if a valid wake-up event is detected.

$[3] \quad V_{uvd(VCC)} > V_{CC} > V_{th(det)POR}.$

[4] Pins ERRN and RXD reflect the state of the wake flag prior to the  $V_{CC}$  undervoltage event.

[5] The internal signals at pins STBN, BGE and TXD are set LOW; the internal signals at pins TXEN, SCLK and SCSN are set HIGH.

[6] Except when  $V_{CC} = 0$ ; in this case BP and BM are floating.

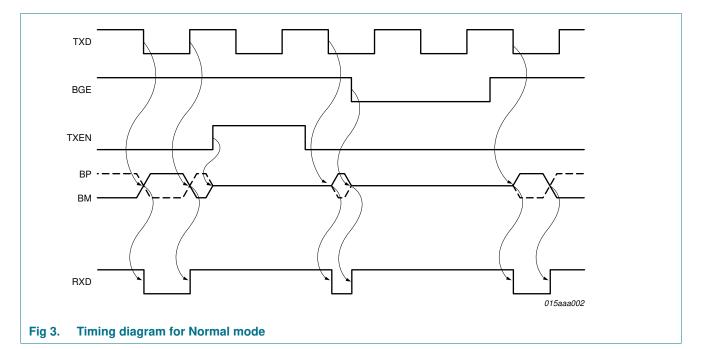

# 6.1.1 Normal mode

In Normal mode, the transceiver transmits and receives data via the bus lines BP and BM. The transmitter and the normal receiver are enabled, along with the undervoltage detection function. The timing diagram for Normal mode is illustrated in Figure 3.

<u>Table 4</u> describes the behavior of the transmitter in Normal mode, when the temperature flag (TEMP HIGH) is not set and with no time-out on pin TXEN. Transmitter behavior is illustrated in Figure 13.

| BGE | TXEN | TXD | Bus state | Transmitter                                                                                          |

|-----|------|-----|-----------|------------------------------------------------------------------------------------------------------|

| L   | Х    | Х   | idle      | transmitter is disabled                                                                              |

| Х   | Н    | Х   | idle      | transmitter is disabled                                                                              |

| Η   | L    | Η   | DATA_1    | transmitter is enabled; the bus lines are actively driven;<br>BP is driven HIGH and BM is driven LOW |

| Η   | L    | L   | DATA_0    | transmitter is enabled; the bus lines are actively driven;<br>BP is driven LOW and BM is driven HIGH |

#### Table 4. Transmitter operation in Normal mode

The transmitter is activated during the first LOW level on pin TXD while pin BGE is HIGH and pin TXEN is LOW.

In Normal mode, the normal receiver output is connected directly to pin RXD (see <u>Table 5</u>). Receiver behavior is illustrated in <u>Figure 14</u>.

| Bus state | RXD |

|-----------|-----|

| DATA_0    | L   |

| DATA_1    | Н   |

| idle      | Н   |

When  $V_{IO}$  and  $V_{CC}$  are within their operating ranges, pin ERRN indicates the status of the error flag. See <u>Section 6.8</u> for a detailed description of error signaling in Normal mode.

TJA1083 Product data sheet

# 6.1.1.1 Bus activity and idle detection

In Normal mode, bus activity and bus idle are detected as follows:

- Bus activity is detected when the absolute differential voltage on the bus lines is higher than |V<sub>i(dif)det(act)</sub>| for t<sub>det(act)(bus)</sub>:

- If the differential voltage on the bus lines is lower than V<sub>IL(dif)</sub> after bus activity has been detected, pin RXD switches LOW.

- If the differential voltage on the bus lines is higher than V<sub>IH(dif)</sub> after bus activity has been detected, pin RXD remains HIGH.

- Bus idle is detected when the absolute differential voltage on the bus lines is lower than |V<sub>i(dif)det(act)</sub>| for t<sub>det(idle)(bus)</sub>. This results in pin RXD being switched HIGH or staying HIGH.

# 6.1.2 Standby mode

Standby mode is a low-power mode featuring very low current consumption. In Standby mode, the transceiver is unable to transmit or receive data since both the transmitter and the normal receiver are switched off. The low-power receiver is activated to monitor the bus for wake-up activity, provided an undervoltage has not been detected on pin  $V_{CC}$ .

The low-power receiver is deactivated if an undervoltage is detected on pin  $V_{CC}$  - with the result that the wake flag is not set if a wake-up pattern or dedicated data frame is received.

Pins ERRN and RXD indicate the status of the wake flag when  $V_{IO}$  and  $V_{CC}$  are within their operating ranges. See <u>Table 3</u> for a description of pins ERRN and RXD when an undervoltage is detected on pin  $V_{IO}$  or pin  $V_{CC}$ .

The status register cannot be read via the SPI interface if an undervoltage is detected on pin  $V_{\text{IO}}.$

The BGE input has no effect in Standby mode.

### 6.1.3 Power-off mode

The transmitter and the two receivers (normal and low-power) are deactivated in Power-off mode. As a result, the wake flag is not set if a wake-up pattern or dedicated data frame is received. If the voltage at V<sub>CC</sub> rises above V<sub>th(rec)POR</sub>, the transceiver switches to Standby mode and the digital section is reset. If V<sub>CC</sub> subsequently drops below V<sub>th(det)POR</sub>, the transceiver reverts to Power-off mode (see <u>Section 6.2</u>).

The status register cannot be read via the SPI interface in Power-off mode.

### 6.1.4 State transitions

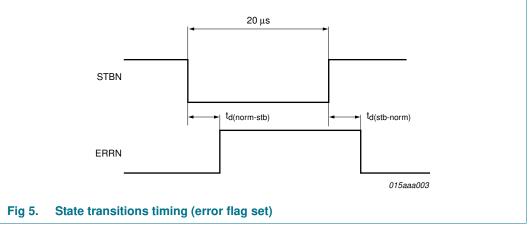

Figure 4 shows the TJA1083 state transition diagram. The timing diagram for the ERRN indication signal during transitions between Normal and Standby modes, when the error flag is set and the wake flag is not set, is illustrated in Figure 5 and described in Table 6.

**TJA1083**

FlexRay node transceiver

All information provided in this document is subject to legal disclaimers.

TJA1083

| Transition           | UVV <sub>IO</sub><br>flag <mark>[1]</mark> | UVV <sub>CC</sub><br>flag <mark><sup>[1]</sup></mark> | wake flag <sup>[1]</sup> | PWON flag <sup>[1]</sup> | STBN            | VCC level                                               |

|----------------------|--------------------------------------------|-------------------------------------------------------|--------------------------|--------------------------|-----------------|---------------------------------------------------------|

| Normal to Standby    | cleared                                    | cleared                                               | cleared                  | cleared                  | $\rightarrow$ L | $V_{CC} > V_{uvd(VCC)}$                                 |

|                      | $\rightarrow$ set                          | cleared                                               | cleared                  | cleared                  | Н               | $V_{CC} > V_{uvd(VCC)}$                                 |

|                      | cleared                                    | $\rightarrow$ set                                     | cleared                  | cleared                  | Н               | $V_{uvd(VCC)} > V_{CC} > V_{th(det)POR}$                |

| Standby to Normal    | cleared                                    | cleared                                               | $1 \rightarrow cleared$  | $2 \rightarrow cleared$  | $\rightarrow$ H | $V_{CC} > V_{uvd(VCC)}$                                 |

|                      | $\rightarrow$ cleared                      | cleared                                               | $1 \rightarrow cleared$  | $2 \rightarrow cleared$  | Н               | $V_{CC} > V_{uvd(VCC)}$                                 |

|                      | cleared                                    | $\rightarrow$ cleared                                 | $1 \rightarrow cleared$  | $2 \rightarrow cleared$  | Н               | $V_{uvd(VCC)} > V_{CC} > V_{th(det)POR}$                |

| Standby to Power-off | Х                                          | set                                                   | Х                        | Х                        | Х               | $\rightarrow$ V <sub>CC</sub> < V <sub>th(det)POR</sub> |

| Power-off to Standby | Х                                          | set                                                   | Х                        | $1 \rightarrow set$      | Х               | $\rightarrow V_{CC} > V_{th(rec)POR}$                   |

#### Table 6. State transitions

ation that initi anding 1 in dia ak - +6----

[1] See Table 7 for set and reset conditions of all flags.

# 6.2 Power-up and power-down behavior

# 6.2.1 Power-up

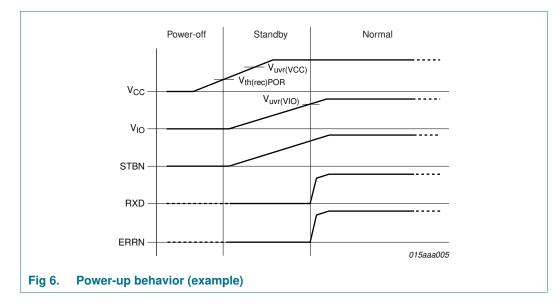

The TJA1083 has two supply pins:  $V_{CC}$  (+5 V) and  $V_{IO}$  (for the voltage level adaptation). The ramp up of the different power supplies can vary, depending on the state or value of a number of signals and parameters. The power-up behavior of the TJA1083 is not affected by the sequence in which power is supplied to these pins or by the voltage ramp up.

As an example, Figure 6 shows one possible power supply ramp-up scenario. The digital section of the TJA1083 is supplied by V<sub>CC</sub>. The voltage on pin V<sub>CC</sub> ramps up before the voltage on pin  $V_{IO}$ . As long as the voltage on  $V_{CC}$  remains below the power-on reset recovery threshold, V<sub>th(rec)POR</sub>, the internal state machine is inactive and the transceiver is totally passive, remaining in Power-off mode. As soon as the voltage rises above the  $V_{th(rec)POR}$  threshold, the internal state machine starts running, setting the PWON flag and switching the TJA1083 to Standby mode. This initializes the  $V_{CC}$  and  $V_{IO}$  under-voltage flags to the set state (since both  $V_{CC}$  and  $V_{IO}$  are actually in undervoltage state just after power-on).

Once both  $V_{IO}$  and  $V_{CC}$  have reached their operating ranges, the under-voltage flags are reset. The operating mode is then determined by the level on STBN (the TJA1083 switches to Normal mode if STBN is HIGH and remains in Standby mode if STBN is LOW), provided  $V_{IO}$  and  $V_{CC}$  are above their respective undervoltage recovery levels  $(V_{uvr(VIO)} \text{ and } V_{uvr(VCC)}).$

# 6.2.2 Power-down

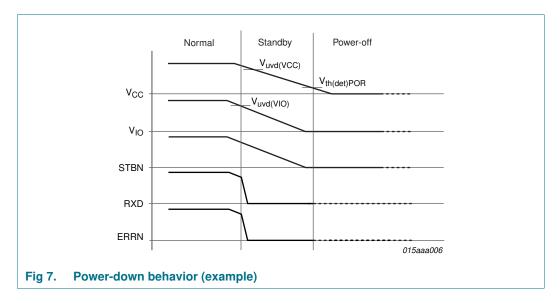

The behavior of the TJA1083 during power-down is illustrated in Figure 7.

TJA1083 Product data sheet

# 6.3 Remote wake-up

# 6.3.1 Bus wake-up via wake-up pattern

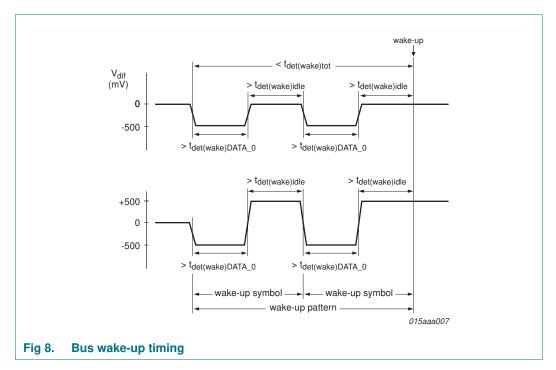

A valid remote wake-up event occurs when a wake-up pattern is received. A wake-up pattern consists of at least two consecutive wake-up symbols. A wake-up symbol comprises a DATA\_0 phase lasting longer than  $t_{det(wake)DATA_0}$  followed by an idle phase lasting longer than  $t_{det(wake)idle}$ , provided both wake-up symbols occur within a time span of  $t_{det(wake)tot}$  (see Figure 8). The transceiver also wakes up if DATA\_1 phases are substituted for the idle phases.

See <u>Ref. 1</u> for more details of the wake-up mechanism.

# 6.3.2 Bus wake-up via dedicated FlexRay data frame

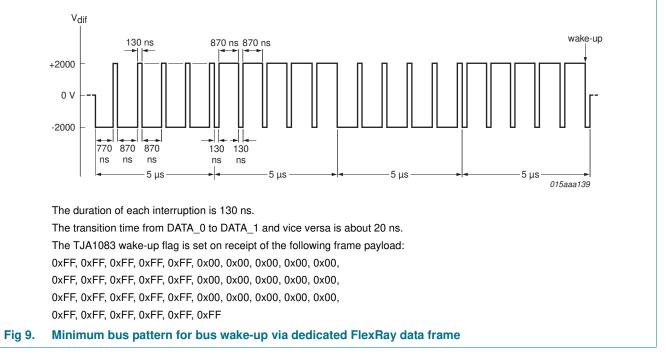

The TJA1083 wake flag is set when a dedicated data frame emulating a valid wake-up pattern, as shown in Figure 9, is received.

The DATA\_0 and DATA\_1 phases of the emulated wake-up symbol are interrupted by the Byte Start Sequence (BSS) preceding each byte in the data frame. With a data rate of 10 Mbit/s, the interruption has a maximum duration of 130 ns and does not prevent the transceiver from recognizing the wake-up pattern in the payload.

For longer interruptions at lower data rates (5 Mbit/s and 2.5 Mbit/s), the wake-up pattern should be used (see <u>Section 6.3.1</u>).

The wake flag is not set if an invalid wake-up pattern is received. See <u>Ref. 1</u> for more details on invalid wake-up patterns.

# 6.4 Bus error detection

The TJA1083 detects the following bus errors during transmission:

- Short-circuit BP to BM at the ECU connector or on the bus

- Short-circuit BP to GND at the ECU connector or on the bus

- · Short-circuit BM to GND at the ECU connector or on the bus

- Short-circuit BP to  $V_{CC}$  at the ECU connector or on the bus

- Short-circuit BM to V<sub>CC</sub> at the ECU connector or on the bus

The bus error flag is not set when a wake-up pattern or a FlexRay Collision Avoidance Symbol (CAS) is being transmitted or received.

# 6.5 Fail silent behavior

Three mechanisms guarantee the 'fail silent' behavior of the TJA1083:

- The TXEN clamped flag is set if pin TXEN goes LOW for longer than t<sub>detCL(TXEN)</sub> in Normal mode; the transmitter is disabled.

- The BGE clamped flag is set if pin BGE goes HIGH for longer than t<sub>detCL(BGE)</sub> in Normal mode; no action is taken.

- If a loss-of-ground occurs at the transceiver, resulting in the TJA1083 switching to Power-off mode, no current flows out of the digital input pins (TXD, TXEN, BGE, STBN, SCLK, SCSN); see <u>Table 3</u> for details of the behavior of the bus pins.

# 6.6 TJA1083 flags

The TJA1083 has 11 status/error flags. These are described in Table 7.

| Flag name              | Flag type      | Flag description                                                         | Set condition                                                      | Reset condition <sup>[1]</sup>                                                                                              | Consequence of<br>flag set                                                                      |

|------------------------|----------------|--------------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| bus wake               | status<br>flag | indicates if a wake-up event has occurred                                | wake-up event on bus<br>in Standby mode <sup>[2]</sup>             | transition to Normal mode                                                                                                   | $\begin{array}{l} RXD \rightarrow LOW;\\ ERRN \rightarrow LOW \ \underline{^{[3]}} \end{array}$ |

| Normal<br>mode         | status<br>flag | indicates if the transceiver is in Normal mode                           | entering Normal mode                                               | leaving Normal mode                                                                                                         | -                                                                                               |

| transmitter<br>enabled | status<br>flag | indicates the transmitter status                                         | transmitter enabled <sup>[4]</sup>                                 | transmitter disabled                                                                                                        | -                                                                                               |

| BGE<br>clamped         | status<br>flag | indicates if pin BGE is<br>clamped                                       | BGE HIGH for longer<br>than t <sub>detCL(BGE)</sub> <sup>[5]</sup> | BGE LOW <sup>[5]</sup>                                                                                                      | -                                                                                               |

| PWON                   | status<br>flag | indicates when the digital section is initialized                        | $V_{CC} > V_{th(rec)POR}$                                          | transition to Normal mode                                                                                                   | -                                                                                               |

| bus error              | error flag     | indicates if a bus error has been detected                               | bus error detected <sup>[5]</sup>                                  | no bus error detected or<br>positive edge on<br>TXEN <sup>[5]</sup>                                                         | ERRN → LOW [6]                                                                                  |

| TEMP<br>HIGH           | error flag     | indicates if the max.<br>junction temperature has<br>been reached        | $T_{vj} > T_{j(dis)(high)}^{[5]}$                                  | $\begin{array}{l} \text{TXEN} = \text{HIGH while} \\ \text{T}_{vj} < \text{T}_{j(dis)(high)}^{[\underline{5}]} \end{array}$ | ERRN $\rightarrow$ LOW <sup>[6]</sup> ; transmitter disabled                                    |

| TXEN<br>clamped        | error flag     | indicates if pin TXEN is clamped                                         | TXEN LOW for longer than t <sub>detCL(TXEN)</sub> [5]              | TXEN = HIGH <sup>[5]</sup>                                                                                                  | ERRN $\rightarrow$ LOW [6];<br>transmitter disabled                                             |

| UVV <sub>CC</sub>      | error flag     | indicates if there is an undervoltage at pin $V_{\mbox{\scriptsize CC}}$ | $V_{CC} < V_{uvd(VCC)}$ for longer than $t_{det(uv)(VCC)}$         | $V_{CC} > V_{uvr(VCC)}$ for longer than $t_{rec(uv)(VCC)}$                                                                  | ERRN $\rightarrow$ LOW [6];<br>entering Standby<br>mode                                         |

| UVV <sub>IO</sub>      | error flag     | indicates if there is an undervoltage at pin $V_{\text{IO}}$             | $V_{IO} < V_{uvd(VIO)}$ for longer than $t_{det(uv)(VIO)}$         | $\label{eq:VIO} \begin{split} V_{IO} &> V_{uvr(VIO)} \text{ for longer} \\ than \ t_{rec(uv)(VIO)} \end{split}$             | ERRN $\rightarrow$ LOW [6];<br>entering Standby<br>mode                                         |

| SPI error              | error flag     | indicates if an SPI error has occurred                                   | SPI error detected <sup>[8]</sup>                                  | falling edge on SCSN                                                                                                        | ERRN $\rightarrow$ LOW [7];<br>SDO goes to a high<br>impedance state                            |

# Table 7. TJA1083 flags and set/reset conditions

[1] All flags, except for the PWON flag, are reset after a power-on reset.

[2] If an undervoltage has not been detected on pin  $V_{CC}$ .

[3] If STBN = LOW.

[4] If BGE = HIGH, the Normal mode flag is set, the TEMP HIGH flag is not set and the TXEN clamped flag is not set.

- [5] Flag can only be set or reset in Normal mode or on leaving Normal mode.

- [6] If STBN = HIGH.

- [7] If STBN = HIGH in SPI mode

- [8] The SPI error flag is set when:

a) more than 16 falling edges occur on pin SCLK while pin SCSN = LOW

b) less than 16 falling edges occur on pin SCLK while pin SCSN = LOW.

# 6.7 TJA1083 status register

The TJA1083 contains a 16-bit status register, of which bits S0 to S4 reflect the state of the status flags, bits S5 to S10 reflect the state of the error flags and bit S15 is a parity bit. All flags can be individually read out on pin SDO via a 16-bit SPI interface when the transceiver is configured in SPI mode. The status register bits are described in <u>Table 8</u>.

# **TJA1083**

#### FlexRay node transceiver

| Table 0.      | IJA 1005 Status Te  | yistei                                |                                                                      |

|---------------|---------------------|---------------------------------------|----------------------------------------------------------------------|

| Status<br>bit | Flag name           | Set condition                         | Reset condition                                                      |

| S0            | bus wake            | bus wake flag set                     | bus wake flag cleared                                                |

| S1            | Normal mode         | Normal mode flag set                  | Normal mode flag cleared                                             |

| S2            | transmitter enabled | transmitter enabled flag set          | transmitter enabled flag cleared                                     |

| S3            | BGE clamped         | BGE clamped flag set                  | BGE clamped flag cleared                                             |

| S4            | PWON                | PWON flag set                         | PWON flag cleared and successful readout <sup>[1]</sup>              |

| S5            | bus error           | bus error flag set                    | bus error flag cleared and successful readout <sup>[1]</sup>         |

| S6            | TEMP HIGH           | TEMP HIGH flag set                    | TEMP HIGH flag cleared and successful readout <sup>[1]</sup>         |

| S7            | TXEN clamped        | TXEN clamped flag set                 | TXEN clamped flag cleared and successful readout <sup>[1]</sup>      |

| S8            | UVV <sub>CC</sub>   | $\mathrm{UVV}_{\mathrm{CC}}$ flag set | UVV <sub>CC</sub> flag cleared and successful readout <sup>[1]</sup> |

| S9            | UVV <sub>IO</sub>   | UVV <sub>IO</sub> flag set            | $UVV_{IO}$ flag cleared and successful readout $[\![1]\!]$           |

| S10           | SPI error           | SPI error flag set                    | SPI error flag cleared and successful readout <sup>[1]</sup>         |

| S11           | reserved            | always LOW                            |                                                                      |

| S12           | reserved            | always HIGH                           |                                                                      |

| S13           | reserved            | always LOW                            |                                                                      |

| S14           | reserved            | always HIGH                           |                                                                      |

| S15           | parity bit          | odd parity of status bits             | even parity of status bits                                           |

|               |                     |                                       |                                                                      |

#### Table 8. TJA1083 status register

[1] Also cleared during Power-off.

# 6.8 Error signaling

The TJA1083 provides two modes for error indication:

- Simple error indication mode

- SPI mode (default mode)

SPI mode is active on power-up.

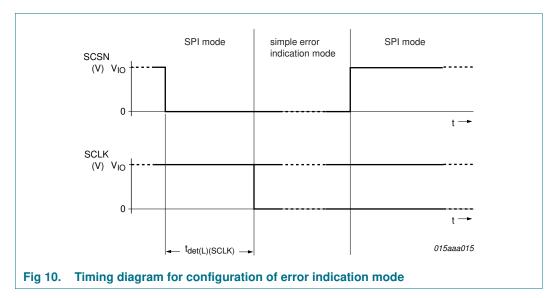

To switch to simple error indication mode, SCSN must be held LOW (connected to GND) and SCLK held HIGH (connected to V<sub>IO</sub>) for longer than  $t_{det(L)(SCLK)}$  (provided a V<sub>IO</sub> undervoltage has not occurred). When the TJA1083 is in simple error indication mode, a rising edge on SCSN initiates a transition to SPI mode (again provided a V<sub>IO</sub> undervoltage has not occurred); see Figure 10.

If a  $V_{IO}$  undervoltage condition is detected, it is not possible to switch between SPI mode and simple error indication mode.

# 6.8.1 SPI mode

The error flag information in the status register is latched in SPI mode. This means that the status bit is reset once the status register has been completely read (provided the corresponding error flag has been reset). If an error condition is detected in Normal mode, pin ERRN goes LOW (provided one of the error bits, S5 to S10, is set). Pin ERRN goes HIGH again once all the error bits have been reset.

# 6.8.2 Simple error indication mode

If an error condition is detected in Normal mode, pin ERRN goes LOW once the relevant error flag has been set. Pin ERRN stays stable for at least  $t_{ERRNL(min)}$  and goes HIGH again when all error conditions have been cleared and all flags have been reset. Error flags are not latched. It is not possible to read-out the status bits in this mode.

# 6.9 SPI interface

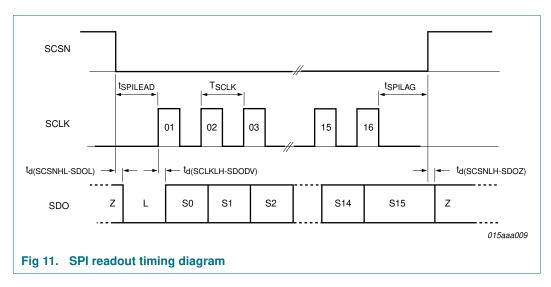

The TJA1083 includes a 16-bit SPI interface to enable a host to read the status register when the transceiver is in SPI mode (see <u>Section 6.8</u>).

While pin SCSN is HIGH, the SDO output is in a high-impedance state. To begin a status register readout, the host must force pin SCSN LOW. This action causes the SDO pin to output a LOW level by default. The data on pin SDO is then shifted out on the rising edge of the clock signal on pin SCLK.

The status bits shifted out on pin SDO are active HIGH. The status bits are refreshed and pin SDO returned to a high-impedance state once the status register has been read successfully (after exactly 16 clock cycles) and SCSN has been forced HIGH again. Clock signals on SCLK are ignored while SCSN is HIGH. The timing diagram for the SPI readout is illustrated in Figure 11.

The SLCK period ranges from 500 ns to 100  $\mu$ s (10 kbit/s to 2 Mbit/s).

TJA1083

If SCSN remains LOW for longer than 16 clock cycles, it is recognized as an SPI error. When this happens, the SPI error flag is set and pin SDO goes to a high-impedance state until the next falling edge on pin SCSN.

An SPI error is also assumed if fewer than 16 clock cycles are received while SCSN is LOW. If this happens, the SPI error flag is set.

All status bits are refreshed once the status register has been successfully read.

When the transceiver is in simple error indication mode the SDO output is in a high-impedance state and pin SCSN is in pull-down mode. In SPI mode pin SCSN is in pull-up mode.

SPI readout is not possible when the transceiver has detected an undervoltage on  $V_{IO}$ .

# 7. Limiting values

#### Table 9. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are referenced to GND.

| Symbol            | Parameter                      | Conditions                                      | Min  | Max            | Unit |

|-------------------|--------------------------------|-------------------------------------------------|------|----------------|------|

| V <sub>CC</sub>   | supply voltage                 | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>IO</sub>   | supply voltage on pin $V_{IO}$ | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>ERRN</sub> | voltage on pin ERRN            | no time limit                                   | -0.3 | $V_{IO} + 0.3$ | V    |

| V <sub>RXD</sub>  | voltage on pin RXD             | no time limit                                   | -0.3 | $V_{IO} + 0.3$ | V    |

| V <sub>SDO</sub>  | voltage on pin SDO             | no time limit                                   | -0.3 | $V_{IO} + 0.3$ | V    |

| V <sub>TXEN</sub> | voltage on pin TXEN            | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>TXD</sub>  | voltage on pin TXD             | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>STBN</sub> | voltage on pin STBN            | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>SCSN</sub> | voltage on pin SCSN            | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>SCLK</sub> | voltage on pin SCLK            | no time limit                                   | -0.3 | +5.5           | V    |

| V <sub>BGE</sub>  | voltage on pin BGE             | no time limit                                   | -0.3 | +5.5           | V    |

| $V_{BP}$          | voltage on pin BP              | no time limit (with respect to pins BM and GND) | -60  | +60            | V    |

All information provided in this document is subject to legal disclaimers.

TJA1083

#### Table 9. Limiting values ...continued

In accordance with the Absolute Maximum Rating System (IEC 60134). All voltages are referenced to GND.

| Symbol               | Parameter                       | Conditions                                      | Min                  | Max   | Unit |

|----------------------|---------------------------------|-------------------------------------------------|----------------------|-------|------|

| V <sub>BM</sub>      | voltage on pin BM               | no time limit (with respect to pins BP and GND) | -60                  | +60   | V    |

| I <sub>I(ERRN)</sub> | input current on pin ERRN       | no time limit; $V_{IO} = 0 V$                   | -10                  | 10    | mA   |

| I <sub>I(RXD)</sub>  | input current on pin RXD        | no time limit; $V_{IO} = 0 V$                   | -10                  | 10    | mA   |

| I <sub>I(SDO)</sub>  | input current on pin SDO        | no time limit; $V_{IO} = 0 V$                   | -10                  | 10    | mA   |

| V <sub>trt</sub> tra | transient voltage               | on pins BM and BP                               | <u>[1]</u> –100      | -     | V    |

|                      |                                 |                                                 | [2] _                | 75    | V    |

|                      |                                 |                                                 | <u>[3]</u> –150      | -     | V    |

|                      |                                 |                                                 | [4]                  | 100   | V    |

| T <sub>stg</sub>     | storage temperature             |                                                 | -55                  | +150  | °C   |

| T <sub>vj</sub>      | virtual junction temperature    |                                                 | <u>[5]</u> –40       | +150  | °C   |

| T <sub>amb</sub>     | ambient temperature             |                                                 | -40                  | +125  | °C   |

| V <sub>ESD</sub>     | electrostatic discharge voltage | IEC61000-4-2 on pins BP and BM to ground        | <u>6</u> –6.0        | +6.0  | kV   |

|                      |                                 | HBM on pins BP and BM to ground                 | <u>[7]</u> −8.0      | +8.0  | kV   |

|                      |                                 | HBM on any other pin                            | <u>[7]</u> −4.0      | +4.0  | kV   |

|                      |                                 | MM on all pins                                  | <u>8</u> –200        | +200  | V    |

|                      |                                 | CDM on all pins                                 | <mark>9</mark> –1000 | +1000 | V    |

[1] According to ISO7637, test pulse 1, class C; verified by an external test house.

[2] According to ISO7637, test pulse 2a, class C; verified by an external test house.

[3] According to ISO7637, test pulse 3a, class C; verified by an external test house.

[4] According to ISO7637, test pulse 3b, class C; verified by an external test house.

[5] In accordance with IEC 60747-1. An alternative definition of  $T_{vj}$  is:  $T_{vj} = T_{amb} + P \times R_{th(j-a)}$ , where  $R_{th(j-a)}$  is a fixed value used in the calculation of  $T_{vj}$ . The rating for  $T_{vj}$  limits the allowable combinations of power dissipation (P) and ambient temperature ( $T_{amb}$ ).

[6] IEC61000-4-2: C = 150 pF; R = 330 Ω; verified by an external test house; the test results were equal to or better than ±6 kV (unaided).

[7] HBM: C = 100 pF; R =  $1.5 \text{ k}\Omega$ .

[8] MM: C = 200 pF; L = 0.75  $\mu$ H; R = 10  $\Omega$ .

[9] CDM: R = 1 Ω.

# 8. Thermal characteristics

### Table 10.Thermal characteristics

| Symbol               | Parameter                                   | Conditions  | Тур | Unit |

|----------------------|---------------------------------------------|-------------|-----|------|

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient | in free air | 130 | K/W  |

# 9. Static characteristics

# Table 11. Static characteristics

All parameters are guaranteed for  $V_{CC}$  = 4.45 V to 5.25 V;  $V_{IO}$  = 2.55 V to 5.25 V;  $T_{vj}$  = -40 °C to +150 °C;  $R_{bus}$  = 40  $\Omega$  to 55  $\Omega$  and  $C_{bus}$  = 100 pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                   | Parameter                                                 | Conditions                                                                       | Min                | Тур | Max                | Unit           |

|--------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|--------------------|-----|--------------------|----------------|

| Pin V <sub>CC</sub>      |                                                           |                                                                                  |                    |     |                    |                |

| I <sub>CC</sub>          | supply current                                            | Standby mode with no undervoltage; $T_{vj} \leq 85~^\circ C$                     | -                  | 20  | 30                 | μA             |

|                          |                                                           | Standby mode with no undervoltage; $T_{\nu j} \leq 150~^\circ C$                 | -                  | 20  | 40                 | μA             |

|                          |                                                           | Power-off mode; $T_{vj} \leq 85~^{\circ}C$                                       | -                  | -   | 30                 | μA             |

|                          |                                                           | Power-off mode; $T_{vj} \leq 150~^{\circ}\text{C}$                               | -                  | -   | 40                 | μA             |

|                          |                                                           | Normal mode;<br>V <sub>BGE</sub> = 0 V or V <sub>TXEN</sub> = V <sub>IO</sub>    | -                  | 11  | 22                 | mA             |

|                          |                                                           | Normal mode; $V_{BGE} = V_{IO}$ ;<br>$V_{TXEN} = 0 V$                            | -                  | 40  | 60                 | mA             |

|                          |                                                           | Normal mode; $V_{BGE} = V_{IO}$ ;<br>$V_{TXEN} = 0$ ; V; $R_{bus} > 10 M\Omega$  | -                  | 25  | 40                 | mA             |

| V <sub>uvd(VCC)</sub>    | undervoltage detection voltage on pin $V_{\text{CC}}$     |                                                                                  | 4.45               | -   | 4.729              | V              |

| V <sub>uvr(VCC)</sub>    | undervoltage recovery voltage on pin V <sub>CC</sub>      |                                                                                  | 4.47               | -   | 4.749              | V              |

| $V_{uvhys(VCC)}$         | undervoltage hysteresis voltage on pin $V_{CC}$           |                                                                                  | 20                 | -   | 290                | mV             |

| V <sub>th(det)</sub> POR | power-on reset<br>detection threshold<br>voltage          |                                                                                  | 3.75               | -   | 4.15               | V              |

| V <sub>th(rec)</sub> POR | power-on reset recovery threshold voltage                 |                                                                                  | 3.85               | -   | 4.25               | V              |

| V <sub>hys(POR)</sub>    | power-on reset<br>hysteresis voltage                      |                                                                                  | 100                | -   | 500                | mV             |

| Pin V <sub>IO</sub>      |                                                           |                                                                                  |                    |     |                    |                |

| l <sub>IO</sub>          | supply current on pin<br>V <sub>IO</sub>                  | Normal mode; $V_{TXEN} = V_{IO}$ ; $V_{BGE} = V_{IO}$ ; $R_{RXD} > 10 \ M\Omega$ | -                  | -   | 1000               | μA             |

|                          |                                                           | Normal mode; $V_{TXEN} = 0 V$ ;<br>$V_{BGE} = V_{IO}$ ; $R_{RXD} > 10 M\Omega$   | -                  | -   | 1000               | μA             |

|                          |                                                           | Standby mode with no undervoltage                                                | -                  | 2.2 | 7                  | μA             |

|                          |                                                           | Power-off mode; $V_{IO} = 5 V$                                                   | -                  | 3   | 7                  | μA             |

| V <sub>uvd(VIO)</sub>    | undervoltage detection<br>voltage on pin V <sub>IO</sub>  |                                                                                  | 2.55               | -   | 2.774              | V              |

| V <sub>uvr(VIO)</sub>    | undervoltage recovery<br>voltage on pin V <sub>IO</sub>   |                                                                                  | 2.575              | -   | 2.799              | V              |

| V <sub>uvhys(VIO)</sub>  | undervoltage hysteresis<br>voltage on pin V <sub>IO</sub> |                                                                                  | 25                 | -   | 240                | mV             |

| Pin SCSN                 |                                                           |                                                                                  |                    |     |                    |                |

| V <sub>IH</sub>          | HIGH-level input voltage                                  |                                                                                  | 0.7V <sub>IO</sub> | -   | 5.5                | V              |

| FJA1083                  |                                                           | All information provided in this document is subject to legal disclaimers.       |                    | C   | NXP B.V. 2012. All | rights reserve |

| Product data s           | heet                                                      | Rev. 1 — 10 October 2012                                                         |                    |     |                    | 18 of 4        |

# Table 11. Static characteristics ...continued

All parameters are guaranteed for  $V_{CC}$  = 4.45 V to 5.25 V;  $V_{IO}$  = 2.55 V to 5.25 V;  $T_{vj}$  = -40 °C to +150 °C;  $R_{bus}$  = 40  $\Omega$  to 55  $\Omega$  and  $C_{bus}$  = 100 pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol          | Parameter                | Conditions                                                                         | Min                | Тур | Max                | Unit |

|-----------------|--------------------------|------------------------------------------------------------------------------------|--------------------|-----|--------------------|------|

| V <sub>IL</sub> | LOW-level input voltage  |                                                                                    | -0.3               | -   | 0.3V <sub>IO</sub> | V    |

| I <sub>IH</sub> | HIGH-level input current | Simple error indication mode; $V_{SCSN} = 0.7 V_{IO}$                              | 3                  | -   | 15                 | μA   |

| I <sub>IL</sub> | LOW-level input current  | SPI mode; $V_{SCSN} = 0.3 V_{IO}$                                                  | -15                | -   | -3                 | μA   |

| l <sub>r</sub>  | reverse current          | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{SCSN} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$ | -5                 | 0   | +5                 | μA   |

| Pin SCLK        |                          |                                                                                    |                    |     |                    |      |

| V <sub>IH</sub> | HIGH-level input voltage |                                                                                    | 0.7V <sub>IO</sub> | -   | 5.5                | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                                                                                    | -0.3               | -   | $0.3V_{IO}$        | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_{SCLK} = V_{IO}$                                                                | -1                 | 0   | +1                 | μA   |

| IIL             | LOW-level input current  | $V_{SCLK} = 0.3 V_{IO}$                                                            | -15                | -   | -3                 | μA   |

| l <sub>r</sub>  | reverse current          | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{SCLK} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$ | -5                 | 0   | +5                 | μA   |

| Pin STBN        |                          |                                                                                    |                    |     |                    |      |

| V <sub>IH</sub> | HIGH-level input voltage |                                                                                    | 0.7V <sub>IO</sub> | -   | 5.5                | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                                                                                    | -0.3               | -   | $0.3V_{IO}$        | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_{STBN} = 0.7 V_{IO}$                                                            | 3                  | -   | 15                 | μA   |

| IIL             | LOW-level input current  | V <sub>STBN</sub> = 0 V                                                            | -1                 | 0   | +1                 | μA   |

| l <sub>r</sub>  | reverse current          | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{STBN} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$ | -5                 | 0   | +5                 | μA   |

| Pin TXEN        |                          |                                                                                    |                    |     |                    |      |

| V <sub>IH</sub> | HIGH-level input voltage |                                                                                    | 0.7V <sub>IO</sub> | -   | 5.5                | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                                                                                    | -0.3               | -   | $0.3V_{IO}$        | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_{TXEN} = V_{IO}$                                                                | -1                 | 0   | +1                 | μA   |

| I <sub>IL</sub> | LOW-level input current  | $V_{TXEN} = 0.3 V_{IO}$                                                            | -300               | -   | -50                | μA   |

| l <sub>r</sub>  | reverse current          | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{TXEN} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$ | -5                 | 0   | +5                 | μA   |

| Pin BGE         |                          |                                                                                    |                    |     |                    |      |

| V <sub>IH</sub> | HIGH-level input voltage |                                                                                    | 0.7V <sub>IO</sub> | -   | 5.5                | V    |

| V <sub>IL</sub> | LOW-level input voltage  |                                                                                    | -0.3               | -   | $0.3V_{IO}$        | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_{BGE} = 0.6 V_{IO}$                                                             | 3                  | -   | 15                 | μA   |

| IIL             | LOW-level input current  | $V_{BGE} = 0 V$                                                                    | -1                 | 0   | +1                 | μA   |

| l <sub>r</sub>  | reverse current          | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{BGE} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$  | -5                 | 0   | +5                 | μA   |

| Pin TXD         |                          |                                                                                    |                    |     |                    |      |

| V <sub>IH</sub> | HIGH-level input voltage | Normal mode                                                                        | 0.6V <sub>IO</sub> | -   | 5.5                | V    |

| V <sub>IL</sub> | LOW-level input voltage  | Normal mode                                                                        | -0.3               | -   | $0.4V_{IO}$        | V    |

| I <sub>IH</sub> | HIGH-level input current | $V_{TXD} = 0.6 V_{IO}$                                                             | 3                  | -   | 15                 | μA   |

| IIL             | LOW-level input current  | $V_{\text{TVD}} = 0 V$                                                             | -1                 | 0   | +1                 | μA   |

TJA1083

# Table 11. Static characteristics ...continued

All parameters are guaranteed for  $V_{CC}$  = 4.45 V to 5.25 V;  $V_{IO}$  = 2.55 V to 5.25 V;  $T_{vj}$  = -40 °C to +150 °C;  $R_{bus}$  = 40  $\Omega$  to 55  $\Omega$  and  $C_{bus}$  = 100 pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol          | Parameter                    | Conditions                                                                        | Min          | Тур | Max             | Unit |

|-----------------|------------------------------|-----------------------------------------------------------------------------------|--------------|-----|-----------------|------|

| l <sub>r</sub>  | reverse current              | Power-off mode; to $V_{CC}/V_{IO}$ ;<br>$V_{TXD} = 5 V$ ; $V_{CC} = V_{IO} = 0 V$ | -5           | 0   | +5              | μA   |

| Ci              | input capacitance            | with respect to all other pins at ground; V <sub>TXD</sub> = 100 mV; f = 5 MHz    | [1] -        | -   | 10              | pF   |

| Pin RXD         |                              |                                                                                   |              |     |                 |      |

| V <sub>OH</sub> | HIGH-level output voltage    | $I_{OH(RXD)} = -1.5 \text{ mA}$                                                   | $V_{IO}-0.4$ | -   | V <sub>IO</sub> | V    |

| V <sub>OL</sub> | LOW-level output<br>voltage  | $I_{OL(RXD)} = 1.5 \text{ mA}$                                                    | -            | -   | 0.4             | V    |

| I <sub>OH</sub> | HIGH-level output<br>current | $V_{RXD} = V_{IO} - 0.4 \text{ V}; V_{IO} = V_{CC}$                               | -15          | -   | -1.5            | mA   |

| I <sub>OL</sub> | LOW-level output<br>current  | $V_{RXD} = 0.4 V$                                                                 | 1.5          | -   | 15              | mA   |

| Vo              | output voltage               | when undervoltage on $V_{IO}$ ; $R_L = 100 \text{ k}\Omega$ to GND                | -            | -   | 500             | mV   |

|                 |                              | Power-off mode;<br>$R_L = 100 \text{ k}\Omega \text{ to } V_{IO}$                 | $V_{IO}-500$ | -   | $V_{IO}$        | mV   |

| Pin ERRN        |                              |                                                                                   |              |     |                 |      |

| V <sub>OH</sub> | HIGH-level output voltage    | $I_{OH(ERRN)} = -100 \ \mu A$                                                     | $V_{IO}-0.4$ | -   | V <sub>IO</sub> | V    |

| V <sub>OL</sub> | LOW-level output voltage     | $I_{OL(ERRN)} = 200 \ \mu A$                                                      | -            | -   | 0.4             | V    |

| I <sub>ОН</sub> | HIGH-level output<br>current | $V_{ERRN} = V_{IO} - 0.4 \text{ V}; V_{IO} = V_{CC}$                              | -1500        | -   | -100            | μA   |

| I <sub>OL</sub> | LOW-level output<br>current  | V <sub>ERRN</sub> = 0.4 V                                                         | 200          | -   | 1700            | μA   |

| IL              | leakage current              | Power-off mode; $V_{ERRN} \leq V_{IO}$                                            | -5           | -   | +5              | μA   |

| Vo              | output voltage               | when undervoltage on $V_{IO}$ ;<br>$R_L = 100 \text{ k}\Omega \text{ to GND}$     | -            | -   | 500             | mV   |

|                 |                              | Power-off mode;<br>$R_L = 100 \text{ k}\Omega \text{ to GND}$                     | -            | -   | 500             | mV   |

| Pin SDO         |                              |                                                                                   |              |     |                 |      |

| V <sub>OH</sub> | HIGH-level output<br>voltage | $I_{OH(SDO)} = -0.5 \text{ mA}$                                                   | $V_{IO}-0.4$ | -   | V <sub>IO</sub> | V    |

| V <sub>OL</sub> | LOW-level output voltage     | $I_{OL(SDO)} = 0.8 \text{ mA}$                                                    | -            | -   | 0.4             | V    |

| I <sub>OH</sub> | HIGH-level output<br>current | $V_{SDO} = V_{IO} - 0.4 \ V$                                                      | -8           | -3  | -0.5            | mA   |

| I <sub>OL</sub> | LOW-level output<br>current  | $V_{SDO} = 0.4 V$                                                                 | 0.8          | 3   | 9               | mA   |

| IL              | leakage current              | high-impedance state;<br>0 V < V <sub>SDO</sub> < V <sub>IO</sub>                 | -5           | -   | +5              | μA   |

# Table 11. Static characteristics ...continued

All parameters are guaranteed for  $V_{CC}$  = 4.45 V to 5.25 V;  $V_{IO}$  = 2.55 V to 5.25 V;  $T_{vj}$  = -40 °C to +150 °C;  $R_{bus}$  = 40  $\Omega$  to 55  $\Omega$  and  $C_{bus}$  = 100 pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                      | Parameter                                                                    | Conditions                                                                                                                  |               | Min         | Тур         | Max                 | Unit |

|-----------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|-------------|-------------|---------------------|------|

| Vo                          | output voltage                                                               | when undervoltage on V <sub>IO</sub> ; V <sub>CC</sub> > 4.75 V; R <sub>L</sub> = 100 k $\Omega$ to GND                     |               | -500        | -           | +500                | mV   |

|                             |                                                                              | Power-off mode;<br>$R_L = 100 \text{ k}\Omega \text{ to GND}$                                                               |               | -           | -           | 500                 | mV   |

| Pins BP and                 | BM                                                                           |                                                                                                                             |               |             |             |                     |      |

| V <sub>o(idle)(BP)</sub>    | idle output voltage on                                                       | Normal mode; $V_{TXEN} = V_{IO}$                                                                                            |               | $0.4V_{CC}$ | $0.5V_{CC}$ | $0.6V_{CC}$         | V    |

|                             | pin BP                                                                       | Standby mode with no undervoltage on pin $V_{CC}$                                                                           |               | -0.1        | 0           | +0.1                | V    |

| V <sub>o(idle)(BM)</sub>    | idle output voltage on                                                       | Normal mode; $V_{TXEN} = V_{IO}$                                                                                            |               | $0.4V_{CC}$ | $0.5V_{CC}$ | $0.6V_{CC}$         | V    |

|                             | pin BM                                                                       | Standby mode with no undervoltage on pin $V_{\text{CC}}$                                                                    |               | -0.1        | 0           | +0.1                | V    |

| I <sub>o(idle)</sub> BP     | idle output current on<br>pin BP                                             | Normal and Standby modes with no undervoltage; –60 V $\leq$ V_{BP} $\leq$ +60 V                                             |               | -7.5        | -           | +7.5                | mA   |

| I <sub>o(idle)</sub> BM     | idle output current on<br>pin BM                                             | Normal and Standby modes with no undervoltage; –60 V $\leq$ V_{BM} $\leq$ +60 V                                             |               | -7.5        | -           | +7.5                | mA   |

| V <sub>o(idle)(dif)</sub>   | differential idle output<br>voltage                                          | Normal mode                                                                                                                 |               | -25         | 0           | +25                 | mV   |

|                             | differential HIGH-level                                                      | $4.75~V \leq V_{CC} \leq 5.25~V$                                                                                            |               | 900         | -           | 2000                | mV   |

|                             | output voltage                                                               | $4.45~V \leq V_{CC} \leq 5.25~V$                                                                                            |               | 700         | -           | 2000                | mV   |

| V <sub>OL(dif)</sub>        | differential LOW-level<br>output voltage                                     | $4.75~V \leq V_{CC} \leq 5.25~V$                                                                                            |               | -2000       | -           | -900                | mV   |

|                             | output voltage                                                               | $4.45~V \leq V_{CC} \leq 5.25~V$                                                                                            |               | -2000       |             | -700                | mV   |

| V <sub>IH(dif)</sub>        | differential HIGH-level<br>input voltage                                     | Normal mode; –10 V $\leq V_{cm} \leq$ +15 V                                                                                 | [2]           | 150         | 225         | 300                 | mV   |

| V <sub>IL(dif)</sub>        | differential LOW-level                                                       | Normal mode; -10 V $\leq$ V_{cm} $\leq$ +15 V                                                                               | [2]           |             | -225        | -150                | mV   |

|                             | input voltage                                                                | Standby mode with no undervoltage on pin $V_{CC};$ –10 V $\leq V_{cm} \leq$ +15 V                                           | <u>[2]</u>    | -400        | -225        | -100                | mV   |

| $ \Delta V_{i(dif)(H-L)} $  | differential input volt.<br>diff. betw. HIGH- and<br>LOW-levels (abs. value) | $V_{cm} = 2.5 V$                                                                                                            | [2]           | -           | -           | 30                  | mV   |

| V <sub>i(dif)det(act)</sub> | activity detection<br>differential input voltage<br>(absolute value)         |                                                                                                                             |               | 150         | 225         | 300                 | mV   |

| I <sub>O(sc)</sub>          | short-circuit output<br>current (absolute value)                             | on pin BP; –5 V $\leq$ V <sub>BP</sub> $\leq$ +60 V; R <sub>sc</sub> $\leq$ 1 $\Omega;$ t <sub>sc</sub> $\geq$ 1500 $\mu s$ | <u>[4][6]</u> | -           | -           | 72                  | mA   |

|                             |                                                                              | on pin BP; –5 V $\leq$ V_{BP} $\leq$ +27 V; $R_{sc}$ $\leq$ 1 $\Omega;$ $t_{sc}$ $\geq$ 1500 $\mu s$                        | <u>[4][6]</u> | -           | -           | 60                  | mA   |

|                             |                                                                              | on pin BM; –5 V $\leq$ V <sub>BM</sub> $\leq$ +60 V;<br>$R_{sc}$ $\leq$ 1 $\Omega;$ $t_{sc}$ $\geq$ 1500 $\mu s$            | <u>[4][6]</u> | -           | -           | 72                  | mA   |

|                             |                                                                              | on pin BM; –5 V $\leq$ V <sub>BM</sub> $\leq$ +27 V;<br>$R_{sc}$ $\leq$ 1 $\Omega;$ $t_{sc}$ $\geq$ 1500 $\mu s$            | <u>[4][6]</u> | -           | -           | 60                  | mA   |

|                             |                                                                              | on pins BP and BM; V_{BP} = V <sub>BM</sub> ; $R_{sc} \le 1 \ \Omega$ ; $t_{sc} \ge 1500 \ \mu s$                           | <u>[5][6]</u> | -           | -           | 60                  | mA   |

| R <sub>i(BP)</sub>          | input resistance on pin<br>BP                                                | $R_{bus} = \infty \Omega$                                                                                                   |               | 10          | 20          | 40                  | kΩ   |

| JA1083                      |                                                                              | All information provided in this document is subject to legal disclain                                                      |               |             | @ N1        | (P B.V. 2012. All r |      |

#### Table 11. Static characteristics ... continued

All parameters are guaranteed for  $V_{CC}$  = 4.45 V to 5.25 V;  $V_{IO}$  = 2.55 V to 5.25 V;  $T_{vj}$  = -40 °C to +150 °C;  $R_{bus}$  = 40  $\Omega$  to 55  $\Omega$  and  $C_{bus}$  = 100 pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                        | Parameter                                                      | Conditions                                                                                                  |            | Min                | Тур         | Max                 | Unit |

|-------------------------------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------|--------------------|-------------|---------------------|------|

| R <sub>i(BM)</sub>            | input resistance on pin<br>BM                                  | $R_{bus} = \infty \ \Omega$                                                                                 |            | 10                 | 20          | 40                  | kΩ   |

| $R_{i(dif)(BP-BM)}$           | differential input<br>resistance between pin<br>BP and pin BM  | $R_{bus} = \infty \Omega$                                                                                   |            | 20                 | 40          | 80                  | kΩ   |

| I <sub>LI(BP)</sub>           | input leakage current on pin BP                                | Power-off mode; $V_{CC}$ = $V_{IO}$ = 0 V; 0 V $\leq$ $V_{BP}$ $\leq$ 5 V                                   |            | -5                 | 0           | +5                  | μA   |

|                               |                                                                | loss of ground; $V_{BP} = V_{BM} = 0$ V; all other pins connected to 16 V via 0 $\Omega$                    | <u>[1]</u> | -1600              | -           | +1600               | μA   |

| I <sub>LI(BM)</sub>           | input leakage current on pin BM                                | Power-off mode; $V_{CC}$ = $V_{IO}$ = 0 V; 0 V $\leq$ $V_{BM} \leq$ 5 V                                     |            | -5                 | 0           | +5                  | μA   |

|                               |                                                                | loss of ground; $V_{BP} = V_{BM} = 0$ V; all other pins connected to 16 V via 0 $\Omega$                    | [1]        | -1600              | -           | +1600               | μA   |

| V <sub>cm(bus)(DATA_0)</sub>  | DATA_0 bus<br>common-mode voltage                              | Normal mode                                                                                                 |            | 0.4V <sub>CC</sub> | $0.5V_{CC}$ | 0.65V <sub>CC</sub> | V    |

| V <sub>cm(bus)</sub> (DATA_1) | DATA_1 bus<br>common-mode voltage                              | Normal mode                                                                                                 |            | $0.4V_{CC}$        | $0.5V_{CC}$ | 0.65V <sub>CC</sub> | V    |

| $\Delta V_{cm(bus)}$          | bus common-mode<br>voltage difference                          | Normal mode; DATA_1 – DATA_0                                                                                |            | -25                | 0           | +25                 | mV   |

| C <sub>i(BP)</sub>            | input capacitance on pin<br>BP                                 | with respect to all other pins at ground; $V_{BP}$ = 100 mV; f = 5 MHz                                      | <u>[1]</u> | -                  | -           | 15                  | pF   |

| C <sub>i(BM)</sub>            | input capacitance on pin<br>BM                                 | with respect to all other pins at ground; $V_{BM}$ = 100 mV; f = 5 MHz                                      | <u>[1]</u> | -                  | -           | 15                  | pF   |

| C <sub>i(dif)(BP-BM)</sub>    | differential input<br>capacitance between<br>pin BP and pin BM | with respect to all other pins at ground; $V_{BP} = 100 \text{ mV}$ ; $V_{BM} = 100 \text{ mV}$ ; f = 5 MHz | [1]        | -                  | -           | 5                   | pF   |

| Z <sub>o(eq)TX</sub>          | transmitter equivalent output impedance                        | Normal mode; $C_{bus}$ = 100 pF;<br>$R_{bus}$ = 40 $\Omega$ or 100 $\Omega$                                 | <u>[3]</u> | 10                 | -           | 600                 | Ω    |

| Temperature p                 | rotection                                                      |                                                                                                             |            |                    |             |                     |      |

| $T_{j(dis)(high)}$            | high disable junction temperature                              |                                                                                                             |            | 180                | -           | 200                 | °C   |

[1] Guaranteed by design.

[2] V<sub>cm</sub> is the BP/BM common mode voltage.

$\begin{array}{ll} [3] & Z_{o(TX)(eq)} = 50 \; \Omega \times (V_{bus(100)} - V_{bus(40)})/(2.5 \times V_{bus(40)} - V_{bus(100)}), \mbox{ where:} \\ & V_{bus(100)} = \mbox{the differential output voltage on a load of 100 } \Omega \mbox{ and 100 } pF \mbox{ in parallel.} \\ & V_{bus(40)} = \mbox{the differential output voltage on a load of 40 } \Omega \mbox{ and100 } pF \mbox{ in parallel, when driving a DATA_1.} \end{array}$

[4] R<sub>sc</sub> is the short-circuit resistance; voltage difference between bus pins BP and BM is 60 V max.

[5]  $R_{sc}$  is the short-circuit resistance between BP and BM.

[6] t<sub>sc</sub> is the minimum duration of the short-circuit

# **10. Dynamic characteristics**

# Table 12. Dynamic characteristics

All parameters are guaranteed for  $V_{CC} = 4.45$  V to 5.25 V;  $V_{IO} = 2.55$  V to 5.25 V;  $T_{vj} = -40$  °C to +150 °C;  $R_{bus} = 40 \Omega$  and  $C_{bus} = 100$  pF unless otherwise specified. All voltages are defined with respect to ground; positive currents flow into the IC.

| Symbol                        | Parameter                                               | Conditions                                                                                      |               | Min | Тур | Max   | Unit |

|-------------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------|-----|-----|-------|------|

| Pins BP and B                 | Μ                                                       |                                                                                                 |               |     |     |       |      |