# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## TLD5501-2QV

#### Dual SYNC Buck Controller with SPI Interface Infineon<sup>®</sup> LITIX<sup>™</sup> Power Flex

| Package    | PG-VQFN-48-31 |

|------------|---------------|

| Marking    | TLD55012QV    |

| Sales Name | TLD5501-2QV   |

## 1 Overview

#### Features

- Dual-Channel synchronous DC/DC Controller for HIGH POWER LED drivers

- Wide LED forward voltage Range (2 V up to 50 V)

- Wide VIN Range (IC 4.5 V to 40 V, Power 4.5 V to 55 V)

- Switching Frequency Range from 200 kHz to 700 kHz

- SPI for diagnostics and control

- Maximum Efficiency in every condition (up to 96%)

- Constant Current (LED) and Constant Voltage Regulation

- Limp Home Function (Fail Safe Mode)

- EMC optimized device: Features an auto Spread Spectrum

- LED current sense with dedicated monitor Output

- Advanced protection features for device and load

- Enhanced Dimming features: Analog and PWM dimming

- LED current accuracy +/- 3%

- Available in a small thermally enhanced PG-VQFN-48-31 package

- Automotive AEC Qualified

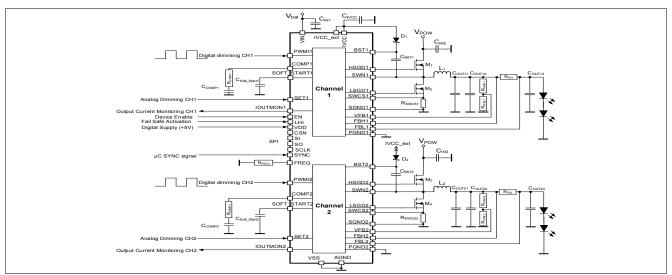

Figure 1 Application Drawing - TLD5501-2QV as current regulator

#### Overview

#### Description

The TLD5501-2QV is a synchronous DUAL Channel DC/DC buck controller with built in protection features and SPI interface. This concept is beneficial for driving high power LEDs with maximum system efficiency and minimum number of external components. The TLD5501-2QV offers both analog and digital (PWM) dimming. The switching frequency is adjustable in the range of 200 kHz to 700 kHz. It can be synchronized to an external clock source. A built in programable Spread Spectrum switching frequency modulation and the forced continuous current regulation mode improve the overall EMC behavior. Furthermore the current mode regulation scheme provides a stable regulation loop maintained by small external compensation components. The adjustable soft start feature limits the current peak as well as voltage overshoot at start-up. The TLD5501-2QV is suitable for use in the harsh automotive environment.

#### Table 1 Product Summary

| Power Stage input voltage range                                                             | V <sub>POW</sub>       | 4.5 V 55 V      |  |

|---------------------------------------------------------------------------------------------|------------------------|-----------------|--|

| Device Input supply voltage range                                                           | V <sub>VIN</sub>       | 4.5 V 40 V      |  |

| Maximum output voltage (depending by the application conditions)                            | V <sub>OUT(max)</sub>  | 50 V            |  |

| Switching Frequency range                                                                   | f <sub>sw</sub>        | 200 kHz 700 kHz |  |

| Typical NMOS driver on-state resistance at<br><i>T</i> <sub>j</sub> = 25°C (Gate Pull Up)   | R <sub>DS(ON_PU)</sub> | 2.3 Ω           |  |

| Typical NMOS driver on-state resistance at<br><i>T</i> <sub>j</sub> = 25°C (Gate Pull Down) | R <sub>DS(ON_PD)</sub> | 1.2 Ω           |  |

| SPI clock frequency                                                                         | f <sub>SCLK(MAX)</sub> | 5 MHz           |  |

#### **Protective Functions**

- Over load protection of external MOSFETs

- Shorted load, output overvoltage and overcurrent protection

- Input undervoltage protection

- Thermal shutdown of device with autorestart behavior

- Electrostatic discharge protection (ESD)

#### **Diagnostic Functions**

- Latched diagnostic information via SPI

- Open load detection in ON-state

- Device Overtemperature shutdown and Temperature Prewarning

- Smart monitoring and advanced functions provide I<sub>LED</sub> information

#### **Limp Home Function**

• Limp Home activation via LHI pin

#### Applications

- Especially designed for driving high power LEDs in automotive applications

- Automotive Exterior Lighting: full LED headlamp assemblies (Low Beam, High Beam, Matrix Beam, Pixel Light)

- General purpose current/voltage controlled DC/DC buck LED driver

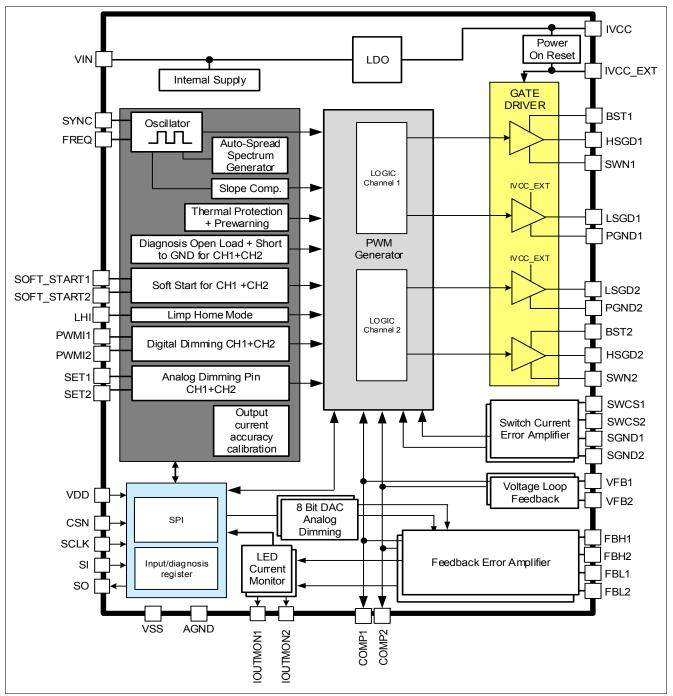

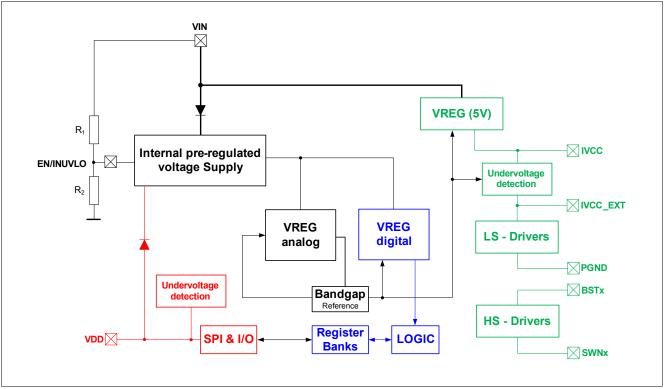

#### Block Diagram

## 2 Block Diagram

Pin Configuration

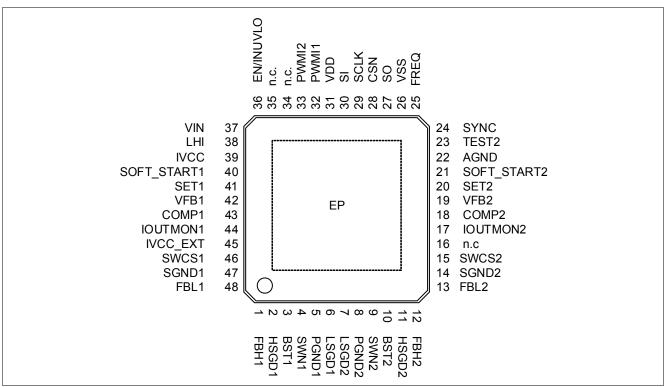

## 3 Pin Configuration

## 3.1 Pin Assignment

Figure 3 Pin Configuration - TLD5501-2QV

**Pin Configuration**

## 3.2 Pin Definitions and Functions

| Pin            | Symbol       | l/ <sup>1)</sup><br>O | Function                                                                                                                                                                                                             |

|----------------|--------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power          | Supply       |                       |                                                                                                                                                                                                                      |

| 16 , 34<br>,35 | n.c.         | -                     | Not connected, tie to AGND on the Layout;                                                                                                                                                                            |

| 37             | VIN          | -                     | <b>Power Supply Voltage;</b><br>Supply for internal biasing.                                                                                                                                                         |

| 31             | VDD          | -                     | <b>Digital GPIO Supply Voltage;</b><br>Connect to reverse voltage protected 5 V or 3.3 V supply.                                                                                                                     |

| 45             | IVCC_EXT     | I PD                  | <b>External LDO input;</b><br>Input to alternatively supply internal Gate Drivers via an external LDO.<br>Connect to IVCC pin to use internal LDO to supply gate drivers. Must not<br>be left open.                  |

| 5,8            | PGND1, 2     | -                     | <b>Power Ground;</b><br>Ground for power potential. Connect externally close to the chip.                                                                                                                            |

| 26             | VSS          | -                     | Digital GPIO Ground;<br>Ground for GPIO pins.                                                                                                                                                                        |

| 22             | AGND         | -                     | Analog Ground;<br>Ground Reference                                                                                                                                                                                   |

| -              | EP           | -                     | <b>Exposed Pad;</b><br>Connect to external heatspreading Cu area (e.g. inner GND layer of multilayer PCB with thermal vias).                                                                                         |

| Gate D         | river Stages |                       |                                                                                                                                                                                                                      |

| 2              | HSGD1        | 0                     | <b>Highside Gate Driver Output 1;</b><br>Drives the top n-channel MOSFET with a voltage equal to $V_{IVCC\_EXT}$ superimposed on the switch node voltage SWN1. Connect to gate of external switching MOSFET.         |

| 11             | HSGD2        | 0                     | <b>Highside Gate Driver Output 2;</b><br>Drives the top n-channel MOSFET with a voltage equal to $V_{\text{IVCC}_{EXT}}$ superimposed on the switch node voltage SWN2. Connect to gate of external switching MOSFET. |

| 6              | LSGD1        | 0                     | <b>Lowside Gate Driver Output 1;</b><br>Drives the lowside n-channel MOSFET between GND and <i>V</i> <sub>IVCC_EXT</sub> .<br>Connect to gate of external switching MOSFET.                                          |

| 7              | LSGD2        | 0                     | <b>Lowside Gate Driver Output 2;</b><br>Drives the lowside n-channel MOSFET between GND and V <sub>IVCC_EXT</sub> .<br>Connect to gate of external switching MOSFET.                                                 |

| 4              | SWN1         | IO                    | Switch Node 1;                                                                                                                                                                                                       |

| 9              | SWN2         | IO                    | Switch Node 2;                                                                                                                                                                                                       |

| 39             | IVCC         | 0                     | <b>Internal LDO output;</b><br>Used for internal biasing and gate driver supply. Bypass with external capacitor close to the pin. Pin must not be left open.                                                         |

## **Pin Configuration**

| Pin   | Symbol        | l/<br>O | 1) | Function                                                                                                                                                                                                                       |

|-------|---------------|---------|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input | s and Outputs |         |    |                                                                                                                                                                                                                                |

| 38    | LHI           | I       | PD | <b>Limp Home Input Pin;</b><br>Used to enter in Limp Home state during Fail Safe condition.                                                                                                                                    |

| 23    | TEST2         | -       |    | <b>Test Pin;</b><br>Used for Infineon end of line test, connect to GND in application.                                                                                                                                         |

| 36    | EN/INUVLO     | I       | PD | <b>Enable/Input Under Voltage Lock Out;</b><br>Used to put the device in a low current consumption mode, with<br>additional capability to fix an undervoltage threshold via external<br>components. Pin must not be left open. |

| 25    | FREQ          | I       |    | Frequency Select Input;<br>Connect external resistor to GND to set frequency.                                                                                                                                                  |

| 24    | SYNC          | Ι       | PD | <b>Synchronization Input;</b><br>Apply external clock signal for synchronization.                                                                                                                                              |

| 32    | PWMI1         | 1       | PD |                                                                                                                                                                                                                                |

| 33    | PWMI2         | 1       | PD | Control Input CH2; Digital input 5 V or 3.3 V.                                                                                                                                                                                 |

| 1     | FBH1          | I       |    | Output current Feedback Positive for CH1;<br>Non inverting Input (+) CH1.                                                                                                                                                      |

| 12    | FBH2          | I       |    | Output current Feedback Positive for CH2;<br>Non inverting Input (+) CH2.                                                                                                                                                      |

| 48    | FBL1          | I       |    | Output current Feedback Negative for CH1;<br>Inverting Input (-) CH1.                                                                                                                                                          |

| 13    | FBL2          | I       |    | Output current Feedback Negative for CH2;<br>Inverting Input (-) CH2.                                                                                                                                                          |

| 3     | BST1          | IO      |    | <b>Bootstrap capacitor;</b><br>Used for internal biasing and to drive the Highside Switch HSGD1.<br>Bypass to SWN1 with external capacitor close to the pin. Pin must not be<br>left open.                                     |

| 10    | BST2          | 10      |    | <b>Bootstrap capacitor;</b><br>Used for internal biasing and to drive the Highside Switch HSGD2.<br>Bypass to SWN2 with external capacitor close to the pin. Pin must not be<br>left open.                                     |

| 46    | SWCS1         | I       |    | <b>Current Sense Input for CH1;</b><br>Inductor current sense CH1 - Non Inverting Input (+).                                                                                                                                   |

| 15    | SWCS2         | I       |    | <b>Current Sense Input for CH2;</b><br>Inductor current sense CH2 - Non Inverting Input (+).                                                                                                                                   |

| 47    | SGND1         | I       |    | <b>Current Sense Ground for CH1;</b><br>Inductor current sense CH1 - Inverting Input (-).<br>Route as Differential net with SWCS1 on the Layout.                                                                               |

| 14    | SGND2         | I       |    | <b>Current Sense Ground for CH2;</b><br>Inductor current sense CH2 - Inverting Input (-).<br>Route as Differential net with SWCS2 on the Layout.                                                                               |

#### **Pin Configuration**

| Pin | Symbol      | l/<br>O | 1) | Function                                                                                                                                         |

|-----|-------------|---------|----|--------------------------------------------------------------------------------------------------------------------------------------------------|

| 43  | COMP1       | 0       |    | <b>Compensation Network Pin for CH1;</b><br>Connect R and C network to pin for stability phase margin adjustment<br>for CH1.                     |

| 18  | COMP2       | 0       |    | <b>Compensation Network Pin for CH2;</b><br>Connect R and C network to pin for stability phase margin adjustment<br>for CH2.                     |

| 40  | SOFT_START1 | 0       |    | <b>Softstart configuration Pin for CH1;</b><br>Connect a capacitor <i>C</i> <sub>SOFT_START1</sub> to GND to fix a soft start ramp default time. |

| 21  | SOFT_START2 | 0       |    | <b>Softstart configuration Pin for CH2;</b><br>Connect a capacitor C <sub>SOFT_START2</sub> to GND to fix a soft start ramp default time.        |

| 42  | VFB1        | I       |    | <b>Voltage Feedback Pin for CH1;</b><br>VFB is intended to set output protection functions for CH1.                                              |

| 19  | VFB2        | I       |    | <b>Voltage Feedback Pin for CH2;</b><br>VFB is intended to set output protection functions for CH2.                                              |

| 41  | SET1        | I       |    | Analog current sense adjustment Pin for CH1;                                                                                                     |

| 20  | SET2        | I       |    | Analog current sense adjustment Pin for CH2;                                                                                                     |

| 44  | IOUTMON1    | 0       | PD | <b>Output current monitor output 1;</b><br>Monitor pin that produces a linear function of $I_{OUT}$ as a voltage.                                |

| 17  | IOUTMON2    | 0       | PD | <b>Output current monitor output 2;</b><br>Monitor pin that produces a linear function of <i>I</i> <sub>OUT</sub> as a voltage.                  |

| SPI | I           |         |    |                                                                                                                                                  |

| 30  | SI          | I       | PD | Serial data in; Digital input 5 V or 3.3 V.                                                                                                      |

| 29  | SCLK        | I       | PD | <b>Serial clock;</b> Digital input 5 V or 3.3 V.                                                                                                 |

| 28  | CSN         | Ι       | PU | <b>SPI chip select;</b> Digital input 5 V or 3.3 V. Active LOW.                                                                                  |

| 27  | SO          | 0       |    | <b>Serial data out;</b> Digital output, referenced to $V_{DD}$ .                                                                                 |

|     |             |         |    |                                                                                                                                                  |

O: Output, I: Input, PD: pull-down circuit integrated, PU: pull-up circuit integrated

**General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

## Table 2 Absolute Maximum Ratings<sup>1)</sup>

#### T<sub>J</sub> = -40°C to +150°C; all voltages with respect to AGND, (unless otherwise specified)

| Parameter                               | Symbol                        | Values |      |      | Unit | Note or               | Number   |

|-----------------------------------------|-------------------------------|--------|------|------|------|-----------------------|----------|

|                                         |                               | Min.   | Тур. | Max. |      | <b>Test Condition</b> |          |

| Supply Voltages                         | 1                             |        |      |      |      | 1                     | I        |

| VIN                                     | V <sub>VIN</sub>              | -0.3   | -    | 60   | V    | -                     | P_4.1.1  |

| Supply Input                            |                               |        |      |      |      |                       |          |

| VDD                                     | V <sub>VDD</sub>              | -0.3   | -    | 6    | V    | -                     | P_4.1.2  |

| Digital supply voltage                  |                               |        |      |      |      |                       |          |

| IVCC                                    | V <sub>IVCC</sub>             | -0.3   | -    | 6    | V    | -                     | P_4.1.3  |

| Internal Linear Voltage Regulator       |                               |        |      |      |      |                       |          |

| Output voltage                          |                               |        |      |      |      |                       |          |

| IVCC_EXT                                | $V_{\rm IVCC\_EXT}$           | -0.3   | -    | 6    | V    | -                     | P_4.1.4  |

| External Linear Voltage Regulator Input |                               |        |      |      |      |                       |          |

| voltage<br>Gate Driver Stages           |                               |        |      |      |      |                       |          |

| LSGD1,2 - PGND1,2                       | 17                            | -0.3   |      | 5.5  | V    |                       |          |

| Lowside Gatedriver voltage              | V <sub>LSGD1,2</sub> -        | -0.3   | -    | 5.5  | v    | _                     | P_4.1.54 |

| HSGD1,2 - SWN1,2                        | PGND1,2                       | -0.3   | _    | 5.5  | V    |                       | P_4.1.55 |

| Highside Gatedriver voltage             | V <sub>HSGD1,2</sub> -        | -0.5   |      | 5.5  | v    | _                     | r_4.1.55 |

| SWN1, SWN2                              | SWN1,2<br>V <sub>SWN1,2</sub> | -1     | _    | 60   | V    | _                     | P_4.1.6  |

| switching node voltage                  | • SWN1, 2                     | -      |      | 00   |      |                       | 1 _ 1110 |

| (BST1-SWN1), (BST2-SWN2)                | V <sub>BST1,2</sub> -         | -0.3   | _    | 6    | V    | _                     | P_4.1.7  |

| Boostrap voltage                        | SWN1,2                        |        |      | -    |      |                       |          |

| BST1, BST2                              | V <sub>BST1,2</sub>           | -0.3   | _    | 65   | V    | _                     | P_4.1.8  |

| Boostrap voltage related to GND         | 0311,2                        |        |      |      |      |                       |          |

| SWCS1,2                                 | V <sub>SWCS1,2</sub>          | -0.3   | _    | 0.3  | V    | -                     | P_4.1.42 |

| Switch Current Sense Input voltages     | ,                             |        |      |      |      |                       |          |

| SGND1,2                                 | V <sub>SGND1,2</sub>          | -0.3   | -    | 0.3  | V    | -                     | P_4.1.43 |

| Switch Current Sense GND voltages       | ,                             |        |      |      |      |                       |          |

| SWCS1,2-SGND1,2                         | V <sub>SWCS1,2</sub> -        | -0.5   | -    | 0.5  | V    | -                     | P_4.1.44 |

| Switch Current Sense differential       | SGND1,2                       |        |      |      |      |                       |          |

| voltages                                |                               |        |      |      |      |                       |          |

| PGND1,2                                 | V <sub>PGND1,2</sub>          | -0.3   | -    | 0.3  | V    | -                     | P_4.1.28 |

| Power GND voltage                       |                               |        |      |      |      |                       |          |

| High voltage Pins                       |                               |        |      |      |      |                       |          |

| FBH1,2; FBL1,2                          | $V_{\rm FBH1,2;}$             | -0.3   | -    | 60   | V    | -                     | P_4.1.45 |

| Feedback Error Amplifier voltages       | FBL1,2                        |        |      |      |      |                       |          |

#### **General Product Characteristics**

## Table 2 Absolute Maximum Ratings<sup>1</sup> (cont'd)

## T<sub>J</sub> = -40°C to +150°C; all voltages with respect to AGND, (unless otherwise specified)

| Parameter                                                          | Symbol                          | Values |      |      | Unit | Note or               | Number   |

|--------------------------------------------------------------------|---------------------------------|--------|------|------|------|-----------------------|----------|

|                                                                    |                                 | Min.   | Тур. | Max. |      | <b>Test Condition</b> |          |

| FBH1,2-FBL1,2<br>Feedback Error Amplifier differential<br>voltages | V <sub>FBH1,2</sub> -<br>FBL1,2 | -0.5   | -    | 0.5  | V    | -                     | P_4.1.47 |

| EN/INUVLO<br>Device enable/input undervoltage<br>lockout           | V <sub>EN/INUVLO</sub>          | -0.3   | -    | 60   | V    | -                     | P_4.1.16 |

| Digital (I/O) Pins                                                 |                                 |        |      |      |      |                       |          |

| PWMI1,2<br>Digital Input voltages                                  | V <sub>PWMI1,2</sub>            | -0.3   | -    | 5.5  | V    | _                     | P_4.1.49 |

| CSN<br>Voltage at Chip Select pin                                  | V <sub>CSN</sub>                | -0.3   | -    | 5.5  | V    | -                     | P_4.1.18 |

| SCLK<br>Voltage at Serial Clock pin                                | V <sub>SCLK</sub>               | -0.3   | -    | 5.5  | V    | -                     | P_4.1.19 |

| SI<br>Voltage at Serial Input pin                                  | V <sub>SI</sub>                 | -0.3   | -    | 5.5  | V    | -                     | P_4.1.20 |

| SO<br>Voltage at Serial Output pin                                 | V <sub>so</sub>                 | -0.3   | -    | 5.5  | V    | -                     | P_4.1.21 |

| SYNC<br>Synchronization Input voltage                              | V <sub>SYNC</sub>               | -0.3   | -    | 5.5  | V    | -                     | P_4.1.22 |

| LHI<br>Limp Home Input Voltage                                     | V <sub>LHI</sub>                | -0.3   | -    | 5.5  | V    | -                     | P_4.1.58 |

| LHI<br>Limp Home Input Current                                     | I <sub>LHI</sub>                | -5     | -    | -    | mA   | -                     | P_4.1.60 |

| Analog Pins                                                        | ł                               | 1      | 1    |      | 1    |                       |          |

| VFB1,2<br>Loop Input voltages                                      | V <sub>VFB1,2</sub>             | -0.3   | -    | 5.5  | V    | -                     | P_4.1.50 |

| SET1,2<br>Analog dimming Input voltage                             | V <sub>SET1,2</sub>             | -0.3   | -    | 5.5  | V    | -                     | P_4.1.56 |

| COMP1,2<br>Compensation Input voltages                             | V <sub>COMP1,2</sub>            | -0.3   | -    | 3.6  | V    | -                     | P_4.1.52 |

| SOFT_START1,2<br>Softstart Voltages                                | V <sub>SOFT_STAR</sub>          | -0.3   | -    | 3.6  | V    | -                     | P_4.1.53 |

| FREQ<br>Voltage at frequency selection pin                         | V <sub>FREQ</sub>               | -0.3   | -    | 3.6  | V    | -                     | P_4.1.32 |

| IOUTMON1,2<br>Voltages at output monitor pins                      | V <sub>IOUTMON1</sub> ,         | -0.3   | -    | 5.5  | V    | -                     | P_4.1.59 |

| Temperatures                                                       | I                               | 1      | I    |      | I    | 1                     | I        |

| Junction Temperature                                               | T <sub>i</sub>                  | -40    | -    | 150  | °C   | -                     | P_4.1.35 |

| Storage Temperature                                                | T <sub>stg</sub>                | -55    | -    | 150  | °C   | -                     | P_4.1.36 |

| ESD Susceptibility                                                 |                                 | 1      | 1    | 1    | 1    | 1                     | I        |

#### **General Product Characteristics**

#### Table 2Absolute Maximum Ratings<sup>1)</sup> (cont'd)

#### T<sub>J</sub> = -40°C to +150°C; all voltages with respect to AGND, (unless otherwise specified)

| Parameter                             | Symbol                 |      | Value | s    | Unit | Note or               | Number   |

|---------------------------------------|------------------------|------|-------|------|------|-----------------------|----------|

|                                       |                        | Min. | Тур.  | Max. |      | <b>Test Condition</b> |          |

| ESD Resistivity of all Pins           | V <sub>ESD,HBM</sub>   | -2   | -     | 2    | kV   | HBM <sup>2)</sup>     | P_4.1.37 |

| ESD Resistivity to GND                | V <sub>ESD,CDM</sub>   | -500 | -     | 500  | V    | CDM <sup>3)</sup>     | P_4.1.38 |

| ESD Resistivity of corner Pins to GND | V <sub>ESD,CDM_c</sub> | -750 | -     | 750  | V    | CDM <sup>3)</sup>     | P_4.1.39 |

|                                       | orner                  |      |       |      |      |                       |          |

1) Not subject to production test, specified by design.

2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 kΩ, 100 pF)

3) ESD susceptibility, Charged Device Model "CDM" ESDA STM5.3.1 or ANSI/ESD S.5.3.1

*Note:* Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Integrated protection functions are designed to prevent IC destruction under fault conditions described in the datasheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

#### Table 3Functional Range

| Parameter                               | Symbo            | Values |      |      | Unit | Note or        | Number  |

|-----------------------------------------|------------------|--------|------|------|------|----------------|---------|

|                                         | ι                | Min.   | Тур. | Max. |      | Test Condition |         |

| Device Extended Supply Voltage<br>Range | V <sub>VIN</sub> | 4.5    | -    | 40   | V    | 1)             | P_4.2.1 |

| Device Nominal Supply Voltage<br>Range  | V <sub>VIN</sub> | 8      | -    | 36   | V    | -              | P_4.2.2 |

| Power Stage Voltage Range               | V <sub>POW</sub> | 4.5    | -    | 55   | V    | 1)             | P_4.2.5 |

| Digital Supply Voltage                  | V <sub>DD</sub>  | 3      | -    | 5.5  | V    | -              | P_4.2.3 |

| Junction Temperature                    | T <sub>i</sub>   | -40    | -    | 150  | °C   | -              | P_4.2.4 |

1) Not subject to production test, specified by design.

#### 4.3 Thermal Resistance

*Note:* This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

*Note:* Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### **General Product Characteristics**

#### Table 4

| Parameter           | Symbol            | Values |      |      | Unit | Note or               | Numbe   |

|---------------------|-------------------|--------|------|------|------|-----------------------|---------|

|                     |                   | Min.   | Тур. | Max. |      | <b>Test Condition</b> | r       |

| Junction to Case    | R <sub>thJC</sub> | -      | 0.9  | -    | K/W  | 1) 2)                 | P_4.3.1 |

| Junction to Ambient | R <sub>thJA</sub> | -      | 25   | -    | K/W  | <sup>3)</sup> 2s2p    | P_4.3.2 |

1) Not subject to production test, specified by design.

2) Specified *R*<sub>thJC</sub> value is simulated at natural convection on a cold plate setup (all pins and the exposed pad are fixed to ambient temperature). Ta = 25°C; The IC is dissipating 1 W.

3) Specified R<sub>thJA</sub> value is according to JEDEC 2s2p (JESD 51-7) + (JESD 51-5) and JEDEC 1s0p (JESD 51-3) + heatsink area at natural convection on FR4 board; The device was simulated on a 76.2 x 114.3 x 1.5 mm board. The 2s2p board has 2 outer copper layers (2 x 70 μm Cu) and 2 inner copper layers (2 x 35 μm Cu). A thermal via (diameter = 0.3 mm and 25 μm plating) array was applied under the exposed pad and connected the first outer layer (top) to the first inner layer and second outer layer (bottom) of the JEDEC PCB. Ta = 25°C; The IC is dissipating 1 W.

#### **Power Supply**

## 5 Power Supply

The TLD5501-2QV is supplied by the following pins:

- VIN (main supply voltage)

- VDD (digital supply voltage)

- IVCC\_EXT (supply for internal gate driver stages)

The VIN supply, in combination with the VDD supply, provides internal supply voltages for the analog and digital blocks. In situations where VIN voltage drops below VDD voltage, an increased current consumption may be observed at the VDD pin.

The SPI and IO interfaces are supplied by the VDD pin.

IVCC\_EXT is the supply for the low side driver stages. This supply is used also to charge, through external Schottky diodes, the bootstrap capacitors which provide supply voltages to the high side driver stages. If no external voltage is available this pin must be shorted to IVCC, which is the output of an internal 5 V LDO.

The supply pins VIN, VDD and IVCC\_EXT have undervoltage detections.

Undervoltage on VDD supply voltage prevents the activation of the gate driver stages and any SPI communication (the SPI registers are reset). Undervoltage on IVCC\_EXT or IVCC voltages forces a deactivation of the driver stages, thus stopping the switching activity, but has no effect on the SPI register settings.

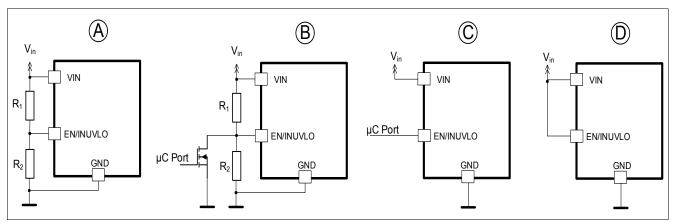

Moreover the double function pin EN/INUVLO can be used as an input undervoltage protection by placing a resistor divider from VIN to GND .

If EN/INUVLO undervoltage is detected, it will turn-off the IVCC voltage regulator, stop switching, stop communications and reset all the registers.

**Figure 4** shows a basic concept drawing of the supply domains and interactions among pins VIN, VDD and IVCC/IVCC\_EXT.

Figure 4 Power Supply Concept Drawing

#### **Power Supply**

#### Usage of EN/INUVLO pin in different applications

The pin EN/INUVLO is a double function pin and can be used to put the device into a low current consumption mode. An undervoltage threshold is fixed by placing an external resistor divider (A) in order to avoid low voltage operating conditions. This pin can be driven by a  $\mu$ C-port as shown in (B) (C).

Figure 5 Usage of EN/INUVLO pin in different applications

#### **Power Supply**

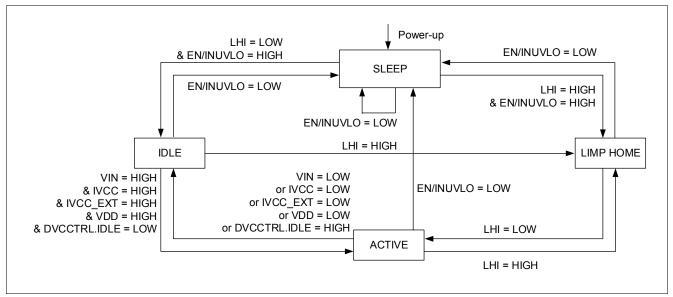

#### 5.1 Different Power States

TLD5501-2QV has the following power states:

- SLEEP state

- IDLE state

- LIMP HOME state

- ACTIVE state

The transition between the power states is determined according to these variables after a filter time of max. 3 clock cycles:

- VIN level

- EN/INUVLO level

- IVCC level

- IVCC\_EXT level

- VDD level

- LHI level

- DVCCTRL.IDLE bit state

The state diagram including the possible transitions is shown in Figure 6.

The Power-up condition is entered when the supply voltage  $V_{VIN}$  exceed its minimum supply voltage threshold  $V_{VIN(ON)}$ .

#### SLEEP

When the device is powered it enters the SLEEP state, all outputs are OFF and the SPI registers are reset, independently from the supply voltages at the pins VIN, VDD, IVCC, and IVCC\_EXT. The current consumption is low. Refer to parameters:  $I_{VDD(SLEEP)}$ , and  $I_{VIN(SLEEP)}$ .

The transition from SLEEP to ACTIVE state requires a specified time:  $t_{ACTIVE}$ .

#### IDLE

In IDLE state, the current consumption of the device can reach the limits given by parameter  $I_{VDD}$  (P\_5.3.4). The internal voltage regulator is working. Not all diagnosis functions are available (refer to **Chapter 10** for additional informations). In this state there is no switching activity, independently from the supply voltages  $V_{IN}$ ,  $V_{DD}$ , IVCC and IVCC\_EXT. When  $V_{DD}$  is available, the SPI registers are working and SPI communication is possible.

#### Limp Home

The Limp Home state is beneficial to fulfill system safety requirements and provides the possibility to maintain a defined current/voltage level on the output via a backup control circuitry. The backup control circuitry turns on required loads during a malfunction of the  $\mu$ C. For detailed info, refer to **Chapter 8**.

When Limp Home state is entered, SPI registers are reset to their default values. In order to regulate the output current/voltage, it is necessary that  $V_{\rm IN}$  and IVCC\_EXT are present and above their undervoltage threshold. If also VDD is above its undervoltage threshold, SPI communication is possible but only in read mode.

#### ACTIVE

In active state the device will start switching activity to provide power at the output only when PWMI1,2 = HIGH or LOOPCTRL\_CH1, 2. PWM\_1, 2 = HIGH. To start the Highside gate drivers HSGD1,2 the voltage level  $V_{BST1,2}$  -  $V_{SWN1,2}$  needs to be above the threshold  $V_{BST1,2}$  -  $V_{SWN1,2}$ \_UVth. In order to recharge the bootstrap capacitor, sporadic switching activity could also be observed when PWMI1,2 = LOW and LOOPCTRL\_CH1,2.PWM\_1,2 =

#### Power Supply

LOW. In ACTIVE state the device current consumption via  $V_{IN}$  and  $V_{DD}$  is dependent on the external MOSFET used and the switching frequency  $f_{SW}$ .

Figure 6 Simplified State Diagram

## 5.2 Different Possibilities to RESET the device

There are several reset triggers implemented in the device.

After any kind of reset, the Transmission Error Flag (TER) is set to HIGH.

#### Under Voltage Reset:

EN/INUVLO: When EN/INUVLO is below  $V_{\text{EN/INUVLOth}}$  (P\_5.3.7), the SPI interface is not working and all the registers are reset to their default values. In addition, the device enters SLEEP mode and the current consumption is minimized.

VDD: When  $V_{VDD}$  is below  $V_{VDD(UV)}$  (P\_5.3.6), the SPI interface is not working and all the registers are reset to their default values.

#### Reset via SPI command:

There is a command (DVCCTRL.SWRST = HIGH) available to RESET all writeable registers to their default values. Note that the result coming from the Calibration routine, which is readable by the SPI when LOOPCTRL\_CH1, 2.ENCAL\_CH1, 2 = HIGH, is not reset by the SWRST.

#### Reset via Limp Home:

When Limp Home state is detected the registers are reset to the default values.

#### **Power Supply**

## 5.3 Electrical Characteristics

## Table 5EC Power Supply

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm I}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                                        | Symbol                          | ymbol |      | Values |    | Note or                                                                                                                                                                                         | Number   |

|--------------------------------------------------|---------------------------------|-------|------|--------|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                  |                                 | Min.  | Тур. | Max.   |    | Test Condition                                                                                                                                                                                  |          |

| Power Supply V <sub>IN</sub>                     |                                 |       | ·    | ·      | ·  |                                                                                                                                                                                                 |          |

| Input Voltage Startup                            | V <sub>VIN(ON)</sub>            | -     | -    | 4.7    | V  | $V_{IN}$ increasing;<br>$V_{EN/INUVLO}$ = HIGH;<br>$V_{DD}$ = 5 V;<br>IVCC = IVCC_EXT =<br>10 mA;                                                                                               | P_5.3.1  |

| Input Undervoltage switch OFF                    | V <sub>VIN(OFF)</sub>           | -     | -    | 4.5    | V  | $V_{IN}$ decreasing;<br>$V_{EN/INUVLO}$ = HIGH;<br>$V_{DD}$ = 5 V;<br>IVCC = IVCC_EXT =<br>10 mA;                                                                                               | P_5.3.14 |

| Device operating current                         | I <sub>VIN(ACTIVE)</sub>        | -     | 6.2  | 9      | mA | <sup>1)</sup> ACTIVE mode;<br>V <sub>PWMI1,2</sub> =0V;                                                                                                                                         | P_5.3.2  |

| <i>V</i> <sub>IN</sub> Sleep mode supply current | I <sub>VIN(SLEEP)</sub>         | -     | -    | 1.5    | μΑ | $V_{EN/INUVLO} = 0 V;$<br>$V_{CSN} = V_{DD} = 5 V;$<br>$V_{IN} = 13.5 V;$<br>$V_{IVCC} = V_{IVCC\_EXT} = 0 V;$                                                                                  | P_5.3.3  |

| Digital Power Supply V <sub>DD</sub>             |                                 |       |      |        |    |                                                                                                                                                                                                 |          |

| Digital supply current                           | I <sub>VDD</sub>                | -     | -    | 0.5    | mA | $V_{IN} = 13.5 V;$<br>$f_{SCLK} = 0 Hz;$<br>$V_{PWMI1,2} = 0 V;$<br>$V_{EN} = V_{CSN} = V_{DD} = 5 V;$                                                                                          | P_5.3.4  |

| Digital Supply Sleep mode<br>current             | I <sub>VDD(SLEEP)</sub>         | _     | -    | 1.5    | μA | $V_{\text{EN/INUVLO}} = 0 \text{ V};$<br>$V_{\text{CSN}} = V_{\text{DD}} = 5 \text{ V};$<br>$V_{\text{IN}} = 13.5 \text{ V};$<br>$V_{\text{IVCC}} = V_{\text{IVCC}\_\text{EXT}} = 0 \text{ V};$ | P_5.3.5  |

| Undervoltage shutdown<br>threshold voltage       | V <sub>VDD(UV)</sub>            | 1     | -    | 3      | V  | $V_{CSN} = V_{DD};$<br>$V_{SI} = V_{SCLK} = 0 V;$<br>SO from LOW to HIGH<br>impedance;                                                                                                          | P_5.3.6  |

| <b>EN/INUVLO Pin characteristics</b>             | ;                               |       |      |        |    |                                                                                                                                                                                                 |          |

| Input Undervoltage falling<br>Threshold          | V <sub>EN/INUVLOth</sub>        | 1.6   | 1.75 | 1.9    | V  | -                                                                                                                                                                                               | P_5.3.7  |

| EN/INUVLO Rising Hysteresis                      | V <sub>EN/INUVLO(hy</sub>       | -     | 90   | -      | mV | 1)                                                                                                                                                                                              | P_5.3.8  |

| EN/INUVLO input Current LOW                      | I <sub>EN/INUVLO(LO</sub><br>w) | 0.45  | 0.89 | 1.34   | μA | $V_{\rm EN/INUVLO} = 0.8  \rm V;$                                                                                                                                                               | P_5.3.9  |

#### **Power Supply**

#### Table 5EC Power Supply (cont'd)

$V_{\rm IN}$  = 8 V to 36 V,  $T_{\rm J}$  = -40°C to +150°C, all voltages with respect to AGND; (unless otherwise specified)

| Parameter                    | Symbol                           |      | Value | s    | Unit | Note or<br>Test Condition                                                                                                | Number   |

|------------------------------|----------------------------------|------|-------|------|------|--------------------------------------------------------------------------------------------------------------------------|----------|

|                              |                                  | Min. | Тур.  | Max. |      |                                                                                                                          |          |

| EN/INUVLO input Current HIGH | I <sub>EN/INUVLO(HI</sub><br>GH) | 1.1  | 2.2   | 3.3  | μA   | $V_{\rm EN/INUVLO} = 2 V;$                                                                                               | P_5.3.10 |

| LHI Pin characteristics      | GH                               |      |       |      |      |                                                                                                                          |          |

| LOW level                    | $V_{\rm LHI(L)}$                 | 0    | -     | 0.8  | V    | -                                                                                                                        | P_5.3.16 |

| HIGH level                   | V <sub>LHI(H)</sub>              | 2.0  | -     | 5.5  | V    | -                                                                                                                        | P_5.3.17 |

| L-Input pull-down current    | I <sub>LHI(L)</sub>              | 6    | 12    | 18   | μA   | $V_{\rm LHI} = 0.8 \rm V;$                                                                                               | P_5.3.18 |

| H-Input pull-down current    | I <sub>LHI(H)</sub>              | 15   | 30    | 45   | μA   | V <sub>LHI</sub> = 2.0 V;                                                                                                | P_5.3.19 |

| Timings                      |                                  |      |       |      | L.   |                                                                                                                          |          |

| SLEEP mode to ACTIVE time    | t <sub>ACTIVE</sub>              | -    | -     | 0.7  | ms   | 1)<br>$V_{IVCC} = V_{IVCC\_EXT};$<br>$C_{IVCC} = 10 \mu\text{F};$<br>$V_{IN} = 13.5 \text{V};$<br>$V_{DD} = 5 \text{V};$ | P_5.3.11 |

1) Not subject to production test, specified by design.

#### **Regulator Description**

## 6 Regulator Description

The TLD5501-2QV includes all of the functions necessary to provide constant current to the output as usually required to drive LEDs. A voltage mode regulation can also be implemented (Refer to **Chapter 6.5**).

In deep buck applications, due to duty cycle limitations ( $D_{\text{BUCK}_{MIN}}$ ) the device will enter pulse skipping mode in order to keep regulating the average output current, the ouptut ripple may increase.

The minimum duty cycle is dependent by the  $f_{sw}$ .

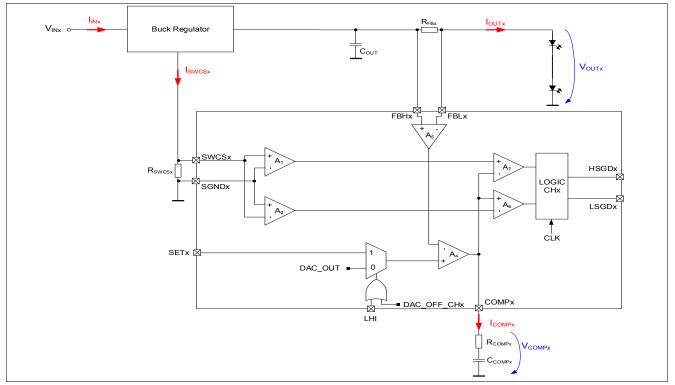

## 6.1 Regulator Diagram Description

An analog current control loop (A5, A4 with complessive gain = *IFBx*<sub>gm</sub>) connected to the sensing pins FBL1,2, FBH1,2 regulates the output current.

The regulator function is implemented by a pulse width modulated (PWM) current mode controller. The error in the output current loop is used to determine the appropriate duty cycle to get a constant output current.

An external compensation network ( $R_{COMP}$ ,  $C_{COMP}$ ) is used to adjust the control loop to various application boundary conditions.

The inductor current for the current mode loop is sensed by the  $R_{SWCS}$  resistor.

$R_{\text{swcs}}$  is used also to limit the maximum external switches / inductor current.

If the Voltage across  $R_{SWCS}$  exceeds its overcurrent threshold ( $V_{SWCS1,2\_buck}$ ) the device reduces the duty cycle in order to bring the switches current below the imposed limit.

The current mode controller has a built-in slope compensation as well to prevent sub-harmonic oscillations.

The control loop logic block (LOGIC\_CHx) provides a PWM signal to two internal gate drivers. The gate drivers (HSGD1,2 and LSGD1,2) are used to drive external MOSFETs. Once the soft start expires a forced CCM regulation mode is performed.

The control loop block diagram displayed in **Figure 7** shows a typical constant current application. The voltage across  $R_{FB}$  sets the output current.

The output current is fixed via the SPI parameter (LEDCURRADIM\_CH1, 2.ADIMVAL\_CH1, 2 =  $11110000_B$  = default at 100%) plus an offset trimming (LEDCURRCAL\_CH1, 2.CALIBVAL\_CH1, 2 =  $0000_B$  = default in the middle of the range). Refer to Chapter 8.1 for more details.

#### **Regulator Description**

Figure 7 Regulator Block Diagram (similar for both Channels) - TLD5501-2QV

#### **Regulator Description**

## 6.2 Adjustable Soft Start Ramp

The soft start routine limits the current through the inductor and the external MOSFET switches during initialization to minimize potential overshoots at the output.

The soft start routine is applied:

- At first turn on (first PWM rise after EN = High)

- After Output Short to GND detection

- After channel stop via low analog dimming value (see Chapter 8 for details)

The soft start rising edge gradually increases the current of the inductor ( $L_{OUT}$ ) over  $t_{SOFT\_START1,2}$  by clamping the COMP1,2 voltage. The soft start ramp is defined by a capacitor placed at the SOFT\_START1,2 pin.

Selection of the SOFT\_START1,2 capacitor ( $C_{SOFT_START1,2}$ ) can be done according to the approximate formula described in **Equation (6.1)**:

$$t_{SOFT\_START\,1,2} = \frac{0.9V}{I_{SOFT\_START\,1,2(PU)}} \cdot C_{SOFT\_START\,1,2}$$

(6.1)

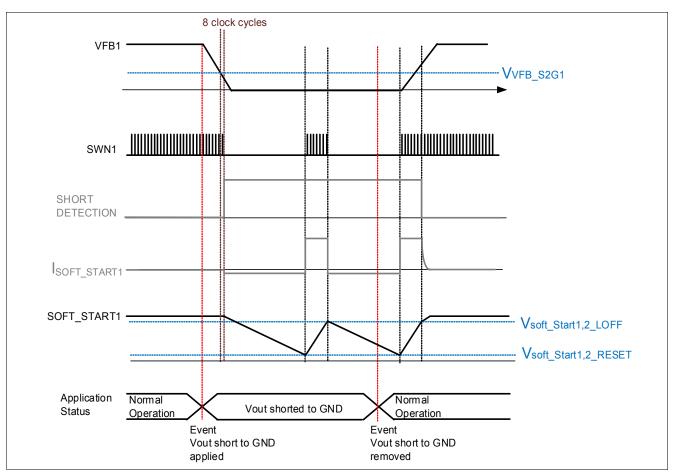

The SOFT START1,2 pins are also used to implement a fault mask and wait-before-retry time, on rising and falling edge respectively, see **Figure 8** and chapter **Chapter 10.2** for details.

If a short on the output is detected, a pull-down current source  $I_{SOFT\_START1,2\_PD}$  (P\_6.4.59) is activated. This current brings down the  $V_{SOFT\_START1,2}$  until  $V_{SOFT\_START1,2\_RESET}$  (P\_6.4.61) is reached, then the pull-up current source  $I_{SOFT\_START1,2\_PU}$  (P\_6.4.58) turns on again. If the fault condition hasn't been removed until  $V_{SOFT\_START1,2\_LOFF}$  (P\_6.4.60) is reached, the pull-down current source turns back on again, initiating a new cycle. This will continue until the fault is removed.

Figure 8 Soft Start timing diagram on a short to ground detected by the VFB1 pin

#### **Regulator Description**

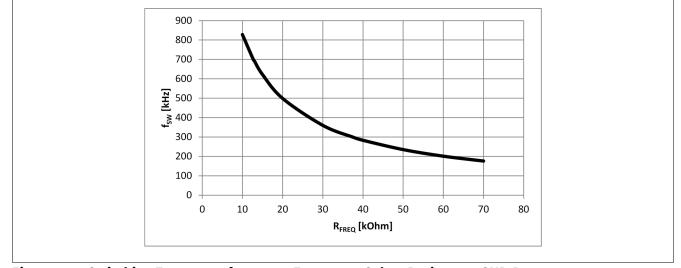

## 6.3 Switching Frequency setup

The switching frequency can be set from 200 kHz to 700 kHz by an external resistor connected from the FREQ pin to GND or by supplying a sync signal as specified in chapter **Chapter 11.2**. Select the switching frequency with an external resistor according to the graph in **Figure 9** or the following approximate formulas.

$$f_{SW}[kHz] = 5375^* (R_{FREQ}[k\Omega])^{-0.8}$$

(6.2)

$$R_{FREG}[k\Omega] = 46023^{*} (f_{SW}[kHz])^{-1.25}$$

(6.3)

Figure 9 Switching Frequency  $f_{SW}$  versus Frequency Select Resistor to GND  $R_{FREO}$

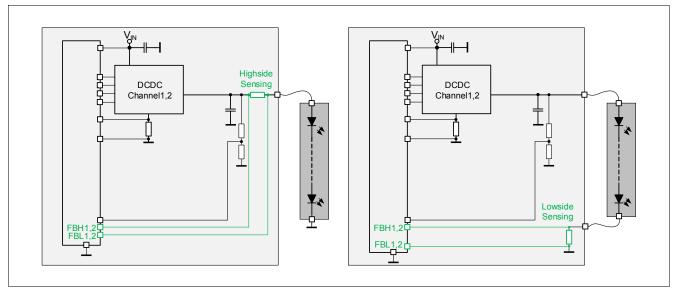

## 6.4 Flexible current sense

The flexible current sense implementation enables highside and lowside current sensing.

The Figure 10 displays the application examples for the highside and lowside current sense concept.

Figure 10 Highside and lowside current sensing - TLD5501-2QV

#### **Regulator Description**

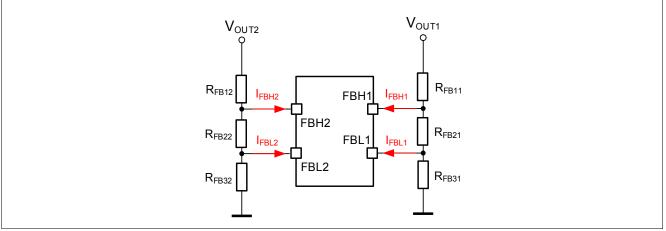

## 6.5 Programming Output Voltage (Constant Voltage Regulation)

For a voltage regulator, the output voltage can be set by selecting the values  $R_{FBx1}$ ,  $R_{FBx2}$  and  $R_{FBx3}$  according to the following **Equation (6.4)**:

$$V_{OUT1,2} = \left(I_{FBH1,2} + \frac{V_{FBH1,2-FBI1,2}}{R_{FB21,2}}\right) \cdot R_{FB1,2} + \left(\frac{V_{FBH1,2-FBI1,2}}{R_{FB21,2}} - I_{FBI1,2}\right) \cdot R_{FB31,2} + V_{FBH1,2-FBI1,2}$$

(6.4)

After the output voltage is fixed via the resistor divider, the value can be changed via the Analog Dimming bits ADIMVAL CH1, 2.

If Analog dimming is performed, due to the variations on the  $I_{FBL}$  ( $I_{FBL1,2\_HSS}$  (P\_6.4.52) and  $I_{FBL1,2\_LSS}$  (P\_6.4.54)) current on the entire voltage spanning, a non linearity on the output voltage may be observed. To minimize this effect RFBx resistors should be properly dimensioned.

Figure 11 Programming Output Voltage (Constant Voltage Regulation)

### **Regulator Description**

## 6.6 Electrical Characteristics

#### Table 6 EC Regulator

$V_{IN}$  = 8 V to 36 V,  $T_{J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                                                       | Symbol                               | Values |      |       | Unit | Note or                                                                                        | Number        |

|-----------------------------------------------------------------|--------------------------------------|--------|------|-------|------|------------------------------------------------------------------------------------------------|---------------|

|                                                                 |                                      | Min.   | Тур. | Max.  |      | Test Condition                                                                                 |               |

| Regulator:                                                      | •                                    |        |      | ,     |      |                                                                                                | •             |

| V <sub>(FBH1,2-FBL1,2)</sub> thresholds                         | V <sub>(FBH1,2</sub> -<br>FBL1,2)    | 145.5  | 150  | 154.5 | mV   | ADIM.ADIMVAL_C<br>H1,2=11110000 <sub>B</sub> ;                                                 | P_6.4.43      |

| V <sub>(FBH1,2-FBL1,2)</sub> thresholds @<br>analog dimming 10% | V <sub>(FBH1,2</sub> -<br>FBL1,2)_10 | 12     | 15   | 18    | mV   | ADIM.ADIMVAL_C<br>H1, 2 = 00011000 <sub>B</sub> ;<br>Calibration<br>Procedure not<br>performed | P_6.4.47      |

| FBH1,2 Bias currents @<br>highside sensing setup                | I <sub>FBH1,2_HSS</sub>              | 65     | 100  | 156   | μA   | $V_{FBL1,2} = 7 V;$<br>$V_{FBH1,2 - FBL1,2} =$<br>150 mV;                                      | P_6.4.51      |

| FBL1,2 Bias currents @ highside<br>sensing setup                | I <sub>FBL1,2_HSS</sub>              | 17     | 30   | 45    | μA   | $V_{FBL1,2} = 7 V;$<br>$V_{FBH1,2 - FBL1,2} =$<br>150 mV;                                      | P_6.4.52      |

| FBH1,2 Bias currents @ lowside<br>sensing setup                 | I <sub>FBH1,2_LSS</sub>              | -7.5   | -4   | -2.5  | μA   | $V_{FBL1,2} = 0 V;$<br>$V_{FBH1,2 - FBL1,2} =$<br>150 mV;                                      | P_6.4.53      |

| FBL1,2 Bias currents @ lowside<br>sensing setup                 | I <sub>FBL1,2_LSS</sub>              | -45    | -30  | -20   | μA   | $V_{FBL1,2} = 0 V;$<br>$V_{FBH1,2 - FBL1,2} =$<br>150 mV;                                      | P_6.4.54      |

| FBH-FBL High Side sensing<br>entry threshold                    | V <sub>FBH_HSS_in</sub>              | 1.9    | 2    | 2.1   | V    | <sup>1)</sup> V <sub>FBH1,2</sub> increasing;                                                  | P_6.9.1       |

| FBH-FBL High Side sensing exit<br>threshold                     | V <sub>FBH_HSS_d</sub>               | 1.65   | 1.75 | 1.85  | V    | <sup>1)</sup> V <sub>FBH1,2</sub> decreasing;                                                  | P_6.9.2       |

| OUT Current sense Amplifier g <sub>m</sub>                      | IFBx <sub>gm</sub>                   | -      | 890  | -     | μS   | 1)                                                                                             | P_6.4.10      |

| Output Monitor Voltages                                         | V <sub>IOUTMON1,</sub>               | 1.33   | 1.4  | 1.47  | V    | V <sub>FBH1,2 - FBL1,2</sub> =<br>150 mV;                                                      | P_6.5.1       |

| Minimum BUCK Duty Cycle                                         | D <sub>BUCK_MIN</sub>                | -      | 4    | 5.5   | %    | ${}^{1)}f_{sw} = 300 \text{ kHZ};$                                                             | P_6.8.2       |

| Maximum BUCK Duty Cycle                                         | D <sub>BUCK_MAX</sub>                | 90.5   | 92   | 94    | %    | $^{1)}f_{sw} = 300 \text{ kHZ};$                                                               | P_6.5.2       |

| Switch Peak Over Current<br>Thresholds - BUCK                   | V <sub>SWCS1,2_bu</sub>              | -60    | -50  | -40   | mV   | 1)                                                                                             | P_10.8.2<br>5 |

| Soft Start                                                      |                                      |        |      |       |      |                                                                                                |               |

| Soft Start1,2 pull up currents                                  | I <sub>Soft_Start1,2</sub><br>_PU    | 21     | 27   | 34    | μA   | V <sub>Soft_Start1,2</sub> = 1 V;                                                              | P_6.4.58      |

| Soft Start1,2 pull down currents                                | I <sub>Soft_Start1,2</sub>           | 2.1    | 2.7  | 3.4   | μΑ   | V <sub>Soft_Start1,2</sub> = 1 V;                                                              | P_6.4.59      |

## **Regulator Description**

#### Table 6EC Regulator (cont'd)

$V_{IN}$  = 8 V to 36 V,  $T_{J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                                                      | Symbol                                           | Values |      |      | Unit | Note or                                                                      | Number   |

|----------------------------------------------------------------|--------------------------------------------------|--------|------|------|------|------------------------------------------------------------------------------|----------|

|                                                                |                                                  | Min.   | Тур. | Max. |      | Test Condition                                                               |          |

| Soft Start1,2 Latch-OFF<br>Thresholds                          | V <sub>Soft_Start1</sub> ,<br>2_LOFF             | 1.65   | 1.75 | 1.85 | V    | -                                                                            | P_6.4.60 |

| Soft Start1,2 Reset Thresholds                                 | V <sub>Soft_Start1,</sub><br>2_RESET             | 0.1    | 0.2  | 0.3  | V    | -                                                                            | P_6.4.61 |

| Soft Start1,2 Voltage during regulation                        | V <sub>Soft_Start_r</sub>                        | 1.9    | 2    | 2.1  | V    | <sup>1)</sup> No Faults                                                      | P_6.9.3  |

| Oscillator                                                     |                                                  |        |      |      |      |                                                                              |          |

| Switching Frequency                                            | f <sub>SW</sub>                                  | 285    | 300  | 315  | kHz  | $T_j = 25^{\circ}C;$<br>$R_{FREQ} = 37.4 \text{ k}\Omega;$<br>ENSPREAD = LOW | P_6.4.23 |

| SYNC Frequency                                                 | f <sub>sync</sub>                                | 200    | -    | 700  | kHz  | -                                                                            | P_6.4.24 |

| SYNC<br>Turn On Threshold                                      | V <sub>SYNC,ON</sub>                             | 2      | -    | -    | V    | -                                                                            | P_6.4.25 |

| SYNC<br>Turn Off Threshold                                     | V <sub>SYNC,OFF</sub>                            | -      | -    | 0.8  | V    | -                                                                            | P_6.4.26 |

| SYNC<br>High Input Current                                     | I <sub>SYNC,H</sub>                              | 15     | 30   | 45   | μA   | $V_{\rm SYNC}$ = 2.0 V;                                                      | P_6.4.62 |

| SYNC<br>Low Input Current                                      | I <sub>SYNC,L</sub>                              | 6      | 12   | 18   | μA   | $V_{\rm SYNC} = 0.8 \rm V;$                                                  | P_6.4.63 |

| Gate Driver for external Switc                                 | h                                                |        |      |      |      |                                                                              |          |

| Gate Driver undervoltage<br>threshold VBST1,2-<br>VSWN1,2_UVth | V <sub>BST1,2</sub> -<br>V <sub>SWN1,2_UVt</sub> | 3.4    | -    | 4    | V    | V <sub>BST1,2</sub> - V <sub>SWN1,2</sub><br>decreasing;                     | P_6.4.64 |

| HSGD1,2 NMOS driver on-state resistance (Gate Pull Up)         | R <sub>DS(ON_PU)</sub>                           | 1.4    | 2.3  | 3.7  | Ω    | $V_{BST1,2} - V_{SWN1,2} = 5 V;$<br>$I_{source} = 100 \text{ mA};$           | P_6.4.28 |

| HSGD1,2 NMOS driver on-state resistance (Gate Pull Down)       | R <sub>DS(ON_PD)</sub>                           | 0.6    | 1.2  | 2.2  | Ω    | $V_{BST1,2} - V_{SWN1,2} = 5 V;$<br>$I_{sink} = 100 \text{ mA};$             | P_6.4.29 |

| LSGD1,2 NMOS driver on-state resistance (Gate Pull Up)         | R <sub>DS(ON_PU)</sub>                           | 1.4    | 2.3  | 3.7  | Ω    | V <sub>IVCC_EXT</sub> = 5 V;<br>I <sub>source</sub> = 100 mA;                | P_6.4.30 |

| LSGD1,2 NMOS driver on-state resistance (Gate Pull Down)       | R <sub>DS(ON_PD)L</sub>                          | 0.4    | 1.2  | 1.8  | Ω    | $V_{\rm IVCC\_EXT}$ = 5 V;<br>$I_{\rm sink}$ = 100 mA;                       | P_6.4.31 |

| HSGD1,2 Gate Driver peak                                       | I <sub>HSGD1,2_SR</sub>                          | 380    | -    | -    | mA   | 1)                                                                           | P_6.4.32 |

| sourcing current                                               | C                                                |        |      |      |      | $V_{HSGD1,2} - V_{SWN1,2} = 1 V$<br>to 4 V;                                  |          |

| HSCD1 2 Cata Driver peak                                       | 1                                                | 410    |      |      | m^   | $V_{BST1,2} - V_{SWN1,2} = 5 V$                                              | D 6 4 22 |

| HSGD1,2 Gate Driver peak sinking current                       | I <sub>HSGD1,2_SN</sub><br>K                     | 410    | -    | -    | mA   | $V_{\text{HSGD1,2}} - V_{\text{SWN1,2}} = 4 \text{ V}$<br>to 1 V;            | P_6.4.33 |

|                                                                |                                                  |        |      |      |      | $V_{BST1,2} - V_{SWN1,2} = 5 V$                                              |          |

#### **Regulator Description**

#### Table 6EC Regulator (cont'd)

$V_{IN}$  = 8 V to 36 V,  $T_{J}$  = -40°C to +150°C, all voltages with respect to AGND (unless otherwise specified)

| Parameter                    | Symbol                   | Values |      |      | Unit | Note or                                                        | Number   |

|------------------------------|--------------------------|--------|------|------|------|----------------------------------------------------------------|----------|

|                              |                          | Min.   | Тур. | Max. |      | Test Condition                                                 |          |

| LSGD1,2 Gate Driver peak     | I <sub>LSGD1,2_SRC</sub> | 370    | -    | -    | mA   | 1)                                                             | P_6.4.34 |

| sourcing current             |                          |        |      |      |      | $V_{LSGD1,2} = 1 V \text{ to } 4 V;$                           |          |

|                              |                          |        |      |      |      | $V_{LSGD1,2} = 1 V \text{ to } 4 V;$<br>$V_{IVCC\_EXT} = 5 V;$ |          |

| LSGD1,2 Gate Driver peak     | I <sub>LSGD1,2_SN</sub>  | 550    | -    | _    | mA   | 1)                                                             | P_6.4.35 |

| sinking current              | К                        |        |      |      |      | $V_{LSGD1,2} = 4 V \text{ to } 1 V;$                           |          |

|                              |                          |        |      |      |      | $V_{IVCC\_EXT} = 5 V;$                                         |          |

| LSGD1,2 OFF to HSGD ON delay | t <sub>LSOFF-</sub>      | 15     | 30   | 40   | ns   | 1)                                                             | P_6.4.36 |

|                              | HSON_delay               |        |      |      |      |                                                                |          |

| HSGD1,2 OFF to LSGD ON delay | t <sub>HSOFF-</sub>      | 35     | 65   | 95   | ns   | 1)                                                             | P_6.4.37 |

|                              | LSON_delay               |        |      |      |      |                                                                |          |

1) Not subject to production test, specified by design