Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **TLE7184F**

System IC for B6 motor drives

# **Data Sheet**

Rev. 1.2, 2016-01-28

**Automotive Power**

### **Table of Contents**

# **Table of Contents**

|                                              | Table of Contents                                                                                                                                                                                                         | . 2                  |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1                                            | Overview                                                                                                                                                                                                                  | . 4                  |

| 2                                            | Block Diagram                                                                                                                                                                                                             | . 5                  |

| <b>3</b><br>3.1<br>3.2                       | Pin Configuration                                                                                                                                                                                                         | . 6                  |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4         | General Product Characteristics Absolute Maximum Ratings Functional Range Thermal Resistance Default State of Inputs                                                                                                      | . 9<br>10<br>11      |

| 5<br>5.1<br>5.2<br>5.3<br>5.4<br>5.5         | MOSFET Driver Inputs and Dead Time Output Stages Bootstrap Principle Currents at SH pins Electrical Characteristics                                                                                                       | 12<br>13<br>13<br>13 |

| <b>6</b><br>6.1                              | Shunt Signal Conditioning                                                                                                                                                                                                 |                      |

| <b>7</b><br>7.1                              | 5 V Low Drop Voltage Regulator                                                                                                                                                                                            |                      |

| <b>8</b><br>8.1<br>8.2<br>8.3<br>8.4         | Interface, VDH Switch and INH Digital Output  PWM Interface (IFMA)  VDHS Switch  Digital Output INHD  Electrical Characteristics                                                                                          | 21<br>22<br>22       |

| 9.1<br>9.2<br>9.2.1<br>9.2.2<br>9.2.3        | Description of Modes, Protection and Diagnostic Functions  Description of modes  Protection and Diagnosis Functions  Over Temperature Shut Down (OTSD)  Over Temperature Prewarning (OTPW)  Analog Temperature Monitoring | 24<br>27<br>27<br>27 |

| 9.2.4<br>9.2.5<br>9.2.6<br>9.2.7             | VS Under Voltage Lockout (VS_UVLO)  VDD Under Voltage Diagnosis (VDD_UVD)  VDD Under Voltage Shut Down (VDD_UVSD)  VREG Under Voltage Diagnosis (VREG_UVD)                                                                | 28<br>28<br>28<br>28 |

| 9.2.8<br>9.2.9<br>9.2.10<br>9.2.11<br>9.2.12 | VREG Under Voltage Shut Down (VREG_UVSD)  IOV and VDH Over Voltage Shut Down (IOV_OVSD, VDH_OVSD)  Dead Time and Shoot Through Protection  Short Circuit Protection (SCP)  SCDL Pin Open Detection (SCDL_open)            | 29<br>29<br>30       |

| 9.2.12<br>9.2.13<br>9.2.14<br>9.2.15<br>9.3  | Over Current Shut Down (OCSD)  VDD Current Limitation  Passive Gxx Clamping  ERR Pin                                                                                                                                      | 30<br>30<br>30       |

2

### **TLE7184F**

| Table of C | ontents |

|------------|---------|

|------------|---------|

| 9.4 | Electrical Characteristics | 32 |

|-----|----------------------------|----|

| 10  | Application Description    | 35 |

| 11  | Package Outlines           | 36 |

| 12  | Revision History           | 37 |

### System IC for B6 motor drives

**TLE7184F**

### 1 Overview

#### **Features**

- Drives 6 N-Channel Power MOSFETs

- Integrated 5V Vreg-Controller to power μC

- · Integrated switch for VDH voltage

- Separate control input for each MOSFET

- Adjustable dead time

- · Shoot through protection

- Analog adjustable Short Circuit Protection levels

- · Low quiescent current mode

- · 1 bit diagnosis ERR

- Over Temperature shut down and analog temperature output

- · Over Temperature pre-warning

- · Under Voltage shut down

- · Adjustable Over Voltage shut down

- Current sense OpAmp

- Over current shut down based on Current sense OpAmp, fixed shut down level

- 0 ...94% duty cycle at 25 kHz PWM frequency

- Green Product (RoHS compliant)

- AEC Qualified

PG-VQFN-48

### **Description**

The TLE7184F is a system IC for Brushless Motor Control. It incorporates a voltage supply for a  $\mu$ C, a bridge driver for a B6 configuration, an application typical PWM interface and some other smaller features. Target is to reduce the number of discrete components in typical BLDC automotive applications and give enough flexibility for custom specific adaptations.

It works with 3-phase motors and brush DC motors. Its exposed pad package allows the usage even at high ambient temperatures.

| Туре     | Package    | Marking  |

|----------|------------|----------|

| TLE7184F | PG-VQFN-48 | TLE7184F |

Data Sheet 4 Rev. 1.2, 2016-01-28

**Block Diagram**

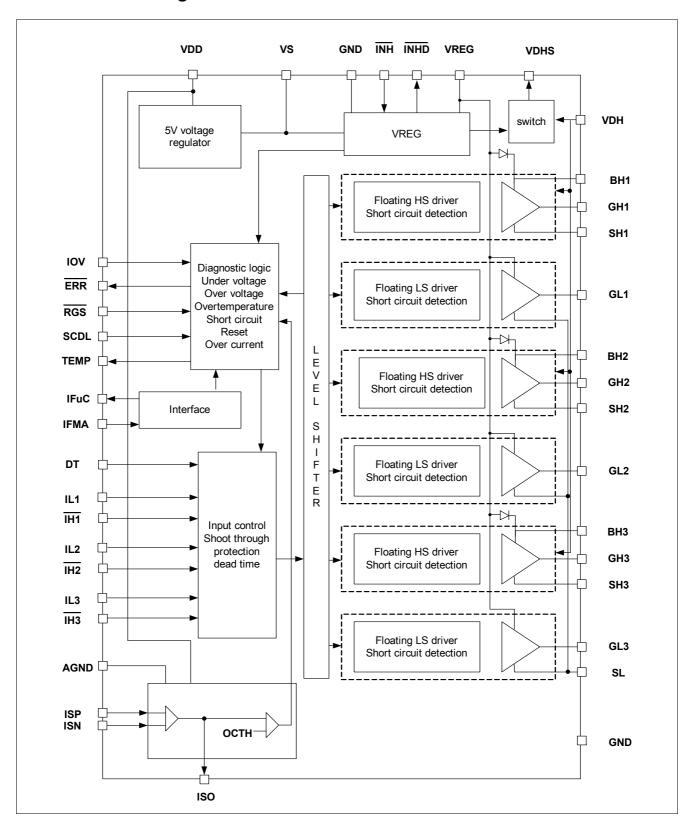

# 2 Block Diagram

Figure 1 Block Diagram

**Pin Configuration**

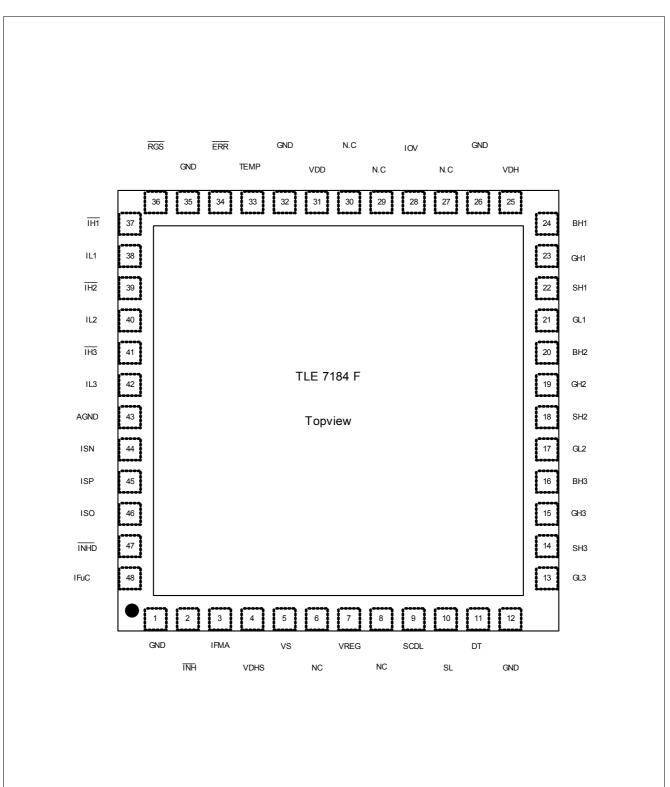

# 3 Pin Configuration

### 3.1 Pin Assignment TLE7184F

Figure 2 Pin Configuration

**Pin Configuration**

### 3.2 Pin Definitions and Functions

| Pin | Symbol | Function                                                                                       |

|-----|--------|------------------------------------------------------------------------------------------------|

| 5   | VS     | Supply Pin                                                                                     |

| 7   | VREG   | Output of supply for driver output stages - connect to capacitor                               |

| 31  | VDD    | Output of 5V supply for μC - connect to capacitor                                              |

| 2   | ĪNH    | Input pin wake up the complete system IC                                                       |

| 47  | ĪNHD   | Digital output 5V for INH state (high when INH is high)                                        |

| 4   | VDHS   | Switched output of VDH voltage; switch open in sleep mode                                      |

| 33  | TEMP   | Output pin for analog temperature signal                                                       |

| 36  | RGS    | Reset and Go-to-Sleep input pin for reset of error registers, set HIGH to avoid to go-to-sleep |

| 38  | IL1    | Input for low side switch 1 (active high)                                                      |

| 37  | ĪH1    | Input for high side switch 1 (active low)                                                      |

| 40  | IL2    | Input for low side switch 2 (active high)                                                      |

| 39  | ĪH2    | Input for high side switch 2 (active low)                                                      |

| 42  | IL3    | Input for low side switch 3(active high)                                                       |

| 41  | ĪH3    | Input for high side switch 3(active low)                                                       |

| 11  | DT     | Input pin for adjustable dead time function, connect to GND via resistor                       |

| 9   | SCDL   | Analog input pin for adjustable Short Circuit Detection function, connect to voltage divider   |

| 28  | IOV    | Input pin for Over Voltage detection.                                                          |

| 34  | ERR    | Open drain error output                                                                        |

| 25  | VDH    | Voltage input common drain high side for short circuit detection                               |

| 24  | BH1    | Pin for + terminal of the bootstrap capacitor of phase 1                                       |

| 23  | GH1    | Output pin for gate of high side MOSFET 1                                                      |

| 22  | SH1    | Pin for source connection of high side MOSFET 1                                                |

| 21  | GL1    | Output pin for gate of low side MOSFET 1                                                       |

| 20  | BH2    | Pin for + terminal of the bootstrap capacitor of phase 2                                       |

| 19  | GH2    | Output pin for gate of high side MOSFET 2                                                      |

| 18  | SH2    | Pin for source connection of high side MOSFET 2                                                |

| 17  | GL2    | Output pin for gate of low side MOSFET 2                                                       |

| 16  | ВН3    | Pin for + terminal of the bootstrap capacitor of phase 3                                       |

| 15  | GH3    | Output pin for gate of high side MOSFET 3                                                      |

| 14  | SH3    | Pin for source connection of high side MOSFET 3                                                |

| 13  | GL3    | Output pin for gate of low side MOSFET 3                                                       |

| 10  | SL     | Pin for common source connection of low side MOSFETs                                           |

| 44  | ISN    | Input for OpAmp - terminal                                                                     |

| 45  | ISP    | Input for OpAmp + terminal                                                                     |

| 46  | ISO    | Output of OpAmp                                                                                |

| 43  | AGND   | Analog GND for Opamp and analog temperature output                                             |

| 3   | IFMA   | Interface to master ECU (used for wake up)                                                     |

| 48  | IFuC   | Interface to µC                                                                                |

### **Pin Configuration**

| Pin | Symbol | Function       |

|-----|--------|----------------|

| 1   | GND    | Ground pin     |

| 12  | GND    | Ground pin     |

| 26  | GND    | Ground pin     |

| 32  | GND    | Ground pin     |

| 35  | GND    | Ground pin     |

| 6   | NC     | connect to GND |

| 8   | NC     | connect to GND |

| 27  | NC     | connect to GND |

| 29  | NC     | connect to GND |

| 30  | NC     | connect to GND |

Exposed pad to be connected to GND

**General Product Characteristics**

### 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

### Absolute Maximum Ratings 1)

$T_{\rm j}$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                                                  | Symbol            | Lin  | nit Values | Unit        | Conditions                                                    |

|----------|----------------------------------------------------------------------------|-------------------|------|------------|-------------|---------------------------------------------------------------|

|          |                                                                            |                   | Min. | Max.       |             |                                                               |

| Voltages | S                                                                          | +                 | -    | +          | <del></del> |                                                               |

| 4.1.1    | Voltage range at VS, IFMA, INH, IOV                                        | $V_{ m VS1}$      | -0.3 | 45         | V           | _                                                             |

| 4.1.2    | Voltage range at IFMA, INH                                                 | $V_{IFMA}$        | -6.0 | 45         | V           | $R >= 10k\Omega$                                              |

| 4.1.3    | Voltage range at VS                                                        | $V_{ m VS2}$      | -3.0 | 45         | V           | $R_{VS} >= 4.7\Omega;$ 60s, 5x;                               |

| 4.1.4    | Voltage range at VS                                                        | $V_{ m VS3}$      | -3.0 | 45         | V           | $R_{VS} >= 2.0\Omega;;$ 200ms, 5x;                            |

| 4.1.5    | Voltage range at VREG output                                               | $V_{VREG}$        | -0.3 | 15         | V           |                                                               |

| 4.1.6    | Voltage range at VDH, VDHS                                                 | $V_{VDHx}$        | -0.3 | 55         | V           | _                                                             |

| 4.1.7    | Voltage range at VDH                                                       | $V_{VDH1}$        | -3.0 | 55         | V           | With $R_{VDH}$<br>>=10 $\Omega$ ; 60s, 5x;<br>$T_{i}$ <=150°C |

| 4.1.8    | Voltage range at IHx, ILx, RGS, ERR, IFuC, TEMP, DT, VDD, ISO, INHD, SCDL, | $V_{DP}$          | -0.3 | 6          | V           | -                                                             |

| 4.1.9    | Voltage range at ISP, ISN                                                  | $V_{OPI}$         | -5.0 | 5.0        | V           | _                                                             |

| 4.1.10   | Voltage difference between ISP and ISN                                     | $V_{OPD}$         | -5.0 | 5.0        | V           |                                                               |

| 4.1.11   | Voltage range at BHx                                                       | $V_{BH}$          | -0.3 | 55         | V           | _                                                             |

| 4.1.12   | Voltage range at GHx                                                       | $V_{GH}$          | -0.3 | 55         | V           | _                                                             |

| 4.1.13   | Voltage range at GHx                                                       | $V_{GHP}$         | -7.0 | 55         | V           | $t_{\rm P}$ < 1µs; $f$ =50kHz                                 |

| 4.1.14   | Voltage range at SHx                                                       | $V_{SH}$          | -2.0 | 45         | V           | _                                                             |

| 4.1.15   | Voltage range at SHx                                                       | $V_{SHP}$         | -7.0 | 45         | V           | $t_{\rm P}$ < 1µs; $f$ =50kHz                                 |

| 4.1.16   | Voltage range at GLx                                                       | $V_{GL}$          | -0.3 | 18         | V           | _                                                             |

| 4.1.17   | Voltage range at GLx                                                       | $V_{GLP}$         | -7.0 | 18         | V           | $t_{\rm P}$ < 0.5µs;<br>f=50kHz                               |

| 4.1.18   | Voltage range at SL                                                        | $V_{\mathrm{SL}}$ | -0.3 | 5.0        | V           | _                                                             |

| 4.1.19   | Voltage range at SL                                                        | $V_{SLP}$         | -7.0 | 5.0        | V           | $t_{\rm P}$ < 0.5µs;<br>f=50kHz                               |

| 4.1.20   | Voltage difference Gxx-Sxx                                                 | $V_{GS}$          | -0.3 | 15         | V           | _                                                             |

| 4.1.21   | Voltage difference BHx-SHx                                                 | $V_{BS}$          | -0.3 | 15         | V           | _                                                             |

| 4.1.22   | Minimum bootstrap capacitor C <sub>BS</sub>                                | $C_{BS}$          | 330  | _          | nF          | -10% tolerance                                                |

| 4.1.23   | Minimum buffer capacitor C <sub>VREG</sub>                                 | $C_{VREG}$        | 1    | _          | μF          | allowed                                                       |

| Tempera  | atures                                                                     |                   |      |            |             |                                                               |

| 4.1.24   | Junction temperature                                                       | $T_{j}$           | -40  | 150        | °C          | _                                                             |

| 4.1.25   | Storage temperature                                                        | $T_{stg}$         | -55  | 150        | °C          | _                                                             |

#### **General Product Characteristics**

### Absolute Maximum Ratings (cont'd)1)

$T_{\rm j}$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                      | Symbol         | Lim  | nit Values | Unit     | Conditions |

|--------|--------------------------------|----------------|------|------------|----------|------------|

|        |                                |                | Min. | Max.       |          |            |

| 4.1.26 | Case temperature <sup>2)</sup> | $T_{\sf Case}$ | _    | 145        | °C       | _          |

| ESD Su | sceptibility                   | <u> </u>       |      | <u>'</u>   | <u> </u> | -          |

| 4.1.27 | ESD Resistivity <sup>3)</sup>  | $V_{ESD}$      | -2   | +2         | kV       | _          |

| 4.1.28 | CDM                            | $V_{CDM}$      | _    | 500        | V        | _          |

- 1) Not subject to production test, specified by design.

- 2) Calculation based on Timax, RthJC and the assumption of 1W power dissipation

- 3) ESD susceptibility HBM according to EIA/JESD 22-A 114B

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 4.2 Functional Range

| Pos.  | Parameter                                         | Symbol               | Li   | mit Values | Unit | Conditions                                                                       |

|-------|---------------------------------------------------|----------------------|------|------------|------|----------------------------------------------------------------------------------|

|       |                                                   |                      | Min. | Max.       |      |                                                                                  |

| 4.2.1 | Supply voltage at VS                              | $V_{ m VS}$          | 6.0  | 45         | V    | below 7V reduced functionality <sup>1) 2)</sup>                                  |

| 4.2.2 | Quiescent current $(I_{VS} + I_{VDH} + I_{IFMA})$ | $I_{Q}$              | _    | 50         | μΑ   | $V_{\rm S}$ <16V;<br>sleep mode<br>$V_{\rm VS}$ = $V_{\rm VDH}$ = $V_{\rm IFMA}$ |

| 4.2.3 | Supply current at VS (device enabled)             | $I_{\mathrm{VS}(0)}$ | _    | 19         | mA   | $V_{\rm s}$ =818V;<br>no load <sup>3)</sup> ;<br>$f_{\rm PWM}$ =25kHz;           |

| 4.2.4 | Duty cycle HS                                     | $D_{HS}$             | 0    | 94         | %    | $f_{\text{PWM}}$ =25kHz;                                                         |

| 4.2.5 | Duty cycle LS                                     | $D_{LS}$             | 0    | 100        | %    | continuous operation                                                             |

| 4.2.6 | Junction temperature                              | $T_{J}$              | -40  | 150        | °C   | _                                                                                |

- 1) MOS driver output deactivated and ERROR pin set to low if VREG is lower UVVR

- 2) MOS driver output stage will operate at Vs=6.7V with 5mA load current at VREG

- 3) no load at VDD, ERR, ISO, IFµC, VDHS, GXX, TEMP, DT

The limitations in the PWM frequency are given by thermal constraints and limitations in the duty cycle (charging time of bootstrap capacitor).

All maximum ratings have to be considered

All basic functions will work between  $T_J$ =150°C and Over Temperature shut down. In this temperature range, the parameters might leave the specified range.

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### **General Product Characteristics**

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                         | Symbol     |      | Limit Val | ues  | Unit | Conditions |

|-------|-----------------------------------|------------|------|-----------|------|------|------------|

|       |                                   |            | Min. | Тур.      | Max. |      |            |

| 4.3.1 | Junction to Case <sup>1)</sup>    | $R_{thJC}$ | _    | _         | 5    | K/W  | _          |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$ | _    | 29        | _    | K/W  | 2)         |

<sup>1)</sup> Not subject to production test, specified by design.

### 4.4 Default State of Inputs

Table 1 Default State of Inputs

| Characteristic                                                    | State          | Remark                                               |

|-------------------------------------------------------------------|----------------|------------------------------------------------------|

| Default state of ILx (if ILx left open -pull down)                | Low            | Low side MOSFETs off                                 |

| Default state of IHx (if IHx left open - pull up)                 | High           | High side MOSFETs off                                |

| Default state of RGS (if RGS left open - pull down)               | Low            | Error signal is reset and the TLE7184F goes to sleep |

| Default state of INH (if INH left open - pull down)               | Low            | no wake up by INH                                    |

| Default state of SCDL (if SCDL left open - pull up)               | High           | Error signal is set; all MOSFETs switched off        |

| Default state of IFMA (if IFMA left open - pull up) <sup>1)</sup> | High           | no wake up by IFMA                                   |

| Default state of IOV (if IOV left open - pull down)               | Low            | no Over Voltage detection by IOV                     |

| Default state of DT (if DT left open)                             | max. dead time | max. dead time                                       |

<sup>1)</sup> external capacitance < 25pF

<sup>2)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 $\mu$ m Cu, 2 x 35 $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

### 5 MOSFET Driver

### 5.1 Inputs and Dead Time

There are 6 independent control inputs to control the 6 MOSFETs individually. <u>However</u>, the control inputs for the High Side MOSFETs IHx are inverted. Hence, the control inputs for High Side IHx and Low Side MOSFETs ILx of the same half bridge can be tight together to control one half bridge by one control signal. To avoid shoot through currents within the half bridges, a dead time is provided by the TLE7184F.

For more details about the dead time please see Chapter 9.2.10

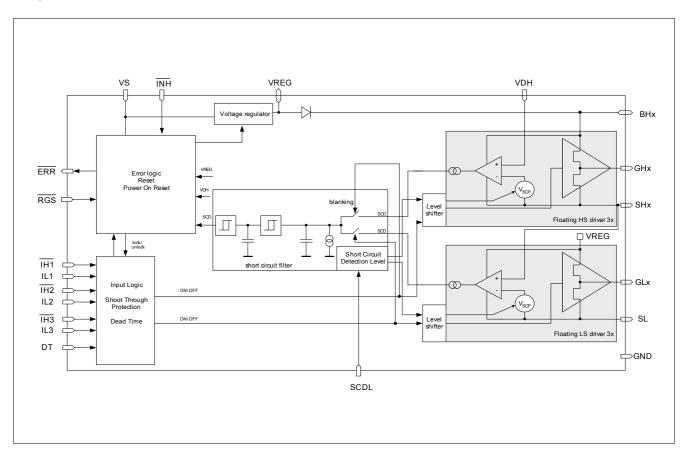

### 5.2 Output Stages

The 3 low side and 3 high side powerful push-pull output stages of the TLE7184F are all floating blocks.

All 6 output stages have the same output power and thanks to the bootstrap principle used, all MOSFETs can be switched up to high frequencies.

Each output stage has its own short circuit detection block. For more details about short circuit detection see Chapter 9.2.11.1)

Figure 3 Block Diagram of Driver Stages including Short Circuit Detection

Data Sheet 12 Rev. 1.2, 2016-01-28

The high side outputs are not designed to be used for low side MOSFETs; the low side outputs are not designed to be used for high side MOSFETs

### 5.3 Bootstrap Principle

The TLE7184F provides a bootstrap based supply for its high side output stages. The benefit of this principle is a fast switching of the high side switches - supporting active freewheeling in high side.

The bootstrap capacitors are charged by switching on the external low side MOSFETs connecting the bootstrap capacitor to GND. Under this condition the bootstrap capacitor will be charged from the VREG capacitor. If the low side MOSFET is switched off and the high side MOSFET is switched on, the bootstrap capacitor will float together with the SHx voltage to the supply voltage of the bridge. Under this condition the supply current of the high side output stage will discharge the bootstrap capacitor. This current is specified. The size of the capacitor together with this current will determine how long the high side MOSFET can be kept on without recharging the bootstrap capacitor.

When all external MOSFETs are switched off, the SHx voltage can be undefined. Under this condition, the bootstrap capacitors can be discharged, dependent on the SHx voltage.

### 5.4 Currents at SH pins

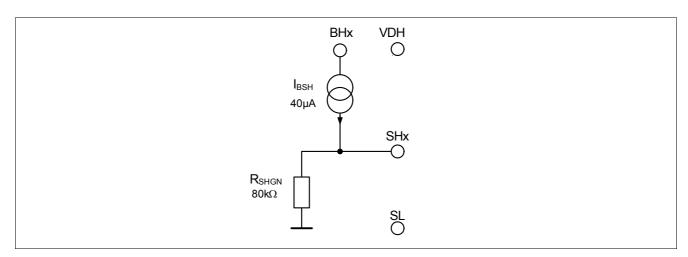

The currents at the SH pins can be used for diagnostic purposes to check the health state of the power stage. The simplified structure related to the SH currents the TLE7184F is described by **Figure 4**.

Figure 4 Block Diagram of SHx pin configuration

#### 5.5 Electrical Characteristics

#### **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 33 V,  $T_{\rm j}$  = -40 °C to +150 °C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Pos.   | Parameter                            | Symbol      | Limit Values |      |          | Unit | Conditions |

|--------|--------------------------------------|-------------|--------------|------|----------|------|------------|

|        |                                      |             | Min.         | Тур. | Max.     |      |            |

| Inputs |                                      |             | 1            | +    | <u> </u> |      |            |

| 5.5.1  | Low level input voltage of ILx; IHx  | $V_{LLL}$   | _            | _    | 1.6      | V    | _          |

| 5.5.2  | High level input voltage of ILx; IHx | $V_{I\_HL}$ | 2.8          | _    | _        | V    | _          |

| 5.5.3  | Input hysteresis of IHx; ILx2)       | $d_{VI}$    | 100          | _    | _        | mV   | _          |

| 5.5.4  | IHx pull-up resistors to VDD         | $R_{IH}$    | 28.5         | _    | 76.5     | kΩ   | _          |

| 5.5.5  | ILx pull-down resistors to GND       | $R_{IL}$    | 178.5        | _    | 564      | kΩ   | _          |

### **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 33 V,  $T_{\rm j}$  = -40 °C to +150 °C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Pos.   | Parameter                                               | Symbol         | L                      | imit Val | ues        | Unit | Conditions                                                                                                                   |

|--------|---------------------------------------------------------|----------------|------------------------|----------|------------|------|------------------------------------------------------------------------------------------------------------------------------|

|        |                                                         |                | Min.                   | Тур.     | Max.       |      |                                                                                                                              |

| MOSFE  | T driver output                                         |                |                        |          |            |      |                                                                                                                              |

| 5.5.6  | Output source resistance                                | $R_{Sou}$      | 2                      | _        | 13.5       | Ω    | $I_{load}$ =20mA                                                                                                             |

| 5.5.7  | Output sink resistance                                  | $R_{Sink}$     | 2                      | _        | 9          | Ω    | $I_{load}$ =20mA                                                                                                             |

| 5.5.8  | High level output voltage Gxx vs. Sxx                   | $V_{Gxx1}$     | _                      | 11       | 14         | V    | $13.5V <=V_{\rm VS}<=45{\rm V}^3, \\ V_{\rm IOV}<=V_{\rm OVIOV}, \\ V_{\rm VDH}<=V_{\rm OVVDH} \\ I_{\rm load}=37.5{\rm mA}$ |

| 5.5.9  | High level output voltage GHx vs. SHx <sup>2)</sup>     | $V_{Gxx2}$     | 6                      | _        | _          | V    | $V_{ m Vs}$ =8V, $C_{ m load}$ =20nF, dc=95%; $f_{ m PWM}$ =20kHz                                                            |

| 5.5.10 | High level output voltage GHx vs. SHx <sup>2)4)</sup>   | $V_{Gxx3}$     | $6 + V_{\text{diode}}$ | _        | _          | V    | $V_{ m Vs}$ =8V, $C_{ m load}$ =20nF, dc=95%; $f_{ m PWM}$ =20kHz; passive freewheeling                                      |

| 5.5.11 | High level output voltage GLx vs. GND                   | $V_{Gxx4}$     | 6.7                    | -        | _          | V    | $V_{ m VS}$ =8V, $C_{ m load}$ =20nF, dc=95%; $f_{ m PWM}$ =20kHz;                                                           |

| 5.5.12 | Rise time<br>$T_{\rm j}$ = -40°C<br>$T_{\rm j}$ = 150°C | $t_{\sf rise}$ | 100<br>150             |          | 230<br>350 | ns   | $C_{ m Load}$ =11nF; $R_{ m Load}$ =1 $\Omega$ $V_{ m VS}$ =7 $V$                                                            |

| 5.5.13 | Fall time $T_{\rm j}$ = -40°C $T_{\rm i}$ = 150°C       | $t_{fall}$     | 80<br>150              | _        | 210<br>290 | ns   | 20-80%                                                                                                                       |

| 5.5.14 | High level output voltage (in passive clamping)         | $V_{GUV}$      | _                      | -        | 1.2        | V    | sleep mode or<br>VS_UVLO <sup>2) 5)</sup>                                                                                    |

| 5.5.15 | Pull-down resistor at BHx to GND                        | $R_{BHUV}$     | _                      | -        | 80         | kΩ   |                                                                                                                              |

| 5.5.16 | Pull-down resistor at VREG to GND                       | $R_{VRUV}$     | _                      | -        | 30         | kΩ   |                                                                                                                              |

| 5.5.17 | Bias current into BHx                                   | $I_{BH}$       | -                      | -        | 150        | μΑ   | $V_{\rm BHx}$ - $V_{\rm SHx}$ =513V; no switching                                                                            |

| 5.5.18 | Current between BHx and SHx                             | $I_{BSH}$      | 15                     | 40       | 60         | μΑ   | $V_{\mathrm{BHx}}$ - $V_{\mathrm{SHx}}$ =513V;<br>$V_{\mathrm{SHX}}$ = GND                                                   |

| 5.5.19 | Resistor between SHx and GND                            | $R_{SHGN}$     | 48                     | 80       | 112        | kΩ   |                                                                                                                              |

| 5.5.20 | Bias current out of SL                                  | $I_{SL}$       | -                      | _        | 2          | mA   | $0V <= VSH <= VS+1$ V; no switching; $V_{CBS} > 5V$                                                                          |

### **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 33 V,  $T_{\rm j}$  = -40 °C to +150 °C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Pos.   | Parameter                                                                  | Symbol          | I    | Limit Val | ues  | Unit     | Conditions                                                      |

|--------|----------------------------------------------------------------------------|-----------------|------|-----------|------|----------|-----------------------------------------------------------------|

|        |                                                                            |                 | Min. | Тур.      | Max. |          |                                                                 |

| 5.5.21 | Input propagation time (low on)                                            | $t_{P(ILN)}$    | 50   | _         | 200  | ns       | $C_{Load}$ =11nF;                                               |

| 5.5.22 | Input propagation time (low off)                                           | $t_{P(ILF)}$    | 50   | _         | 200  | ns       | $R_{Load}$ =1 $\Omega$                                          |

| 5.5.23 | Input propagation time (high on)                                           | $t_{P(IHN)}$    | 50   | _         | 200  | ns       |                                                                 |

| 5.5.24 | Input propagation time (high off)                                          | $t_{P(IHF)}$    | 50   | _         | 200  | ns       |                                                                 |

| 5.5.25 | Absolute input propagation time difference between above propagation times | $t_{P(diff)}$   | -    | -         | 100  | ns       |                                                                 |

| VREG   | 1                                                                          |                 |      |           |      | <u> </u> |                                                                 |

| 5.5.26 | VREG output voltage                                                        | $V_{VREG}$      | 11   | 12.5      | 14   | V        | $V_{\rm VS}$ >= 13,5V; $I_{\rm load}$ =37,5mA                   |

| 5.5.27 | VREG over current limitation                                               | $I_{VREGOCL}$   | 100  | _         | 500  | mA       | no activation of error; $V_{\rm VREG} > V_{\rm VRSD}$           |

| 5.5.28 | Voltage drop between Vs and VREG                                           | $V_{ m VsVREG}$ | -    | -         | 0.5  | V        | $V_{\rm VS}$ >= 7V;<br>$I_{\rm load}$ =37,5mA;<br>Ron operation |

<sup>1)</sup>  $R_{\text{Load}}$  and  $C_{\text{Load}}$  in series

<sup>2)</sup> Not subject to production test; specified by design

<sup>3)</sup> Values above 33V not subjected to production test; specified by design

<sup>4)</sup>  $V_{\mathrm{diode}}$  is the bulk diode of the external low side MOSFET

<sup>5)</sup> see Chapter 9.2.15

**Shunt Signal Conditioning**

### 6 Shunt Signal Conditioning

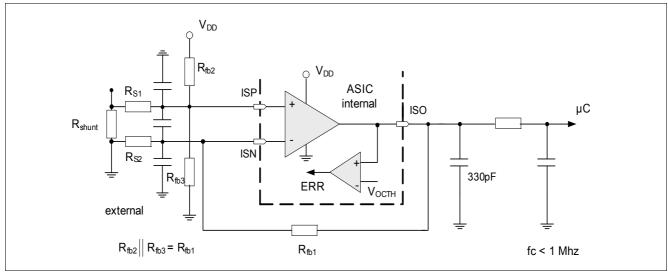

The TLE7184F incorporates a fast and precise operational amplifier for conditioning and amplification of the current sense shunt signal. The gain of the OpAmp is adjustable by external resistors within a range higher than 5. The usage of higher gains in the application might be limited by required settling time and band width.

It is recommended to apply a small offset to the OpAmp, to avoid operation close to the lower rail at low currents. The output of the OpAmp ISO is not short-circuit proof.

In addition to the integrated operational amplifier, the TLE7184F incorporates a comparator to detect over current situations. The output voltage  $V_{\rm ISO}$  is compared to a reference voltage  $V_{\rm OCTH}$  close to the upper rail of the 5V OpAmp supply (VDD). If  $V_{\rm ISO}$  reaches this level an error is set.

Figure 5 Shunt Signal Conditioning Block Diagram and Over Current Limitation

Over current shut down see Chapter 9.2.13.

### 6.1 Electrical Characteristics

#### **Electrical Characteristics - Current sense signal conditioning**

$V_{\rm S}$  = 6.0 to 33 V,  $T_{\rm j}$  = -40 °C to +150 °C, gain = 5 to 75, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Pos.  | Parameter                                                                | Symbol          | Limit Values |      |      | Unit | Conditions                                                          |

|-------|--------------------------------------------------------------------------|-----------------|--------------|------|------|------|---------------------------------------------------------------------|

|       |                                                                          |                 | Min.         | Тур. | Max. |      |                                                                     |

| 6.1.1 | Series resistors                                                         | $R_{S}$         | 100          | 500  | 1000 | Ω    | _                                                                   |

| 6.1.2 | Feedback resistor                                                        | $R_{fb}$        | 2000         | 7500 | _    | Ω    | _                                                                   |

| 6.1.3 | Resistor ratio (gain ratio), max. gain limited by settling time          | $R_{\rm fb/RS}$ | 5            | _    | _    | _    | $R_{\rm L}$ >3k $\Omega$                                            |

| 6.1.4 | Input differential voltage (ISP - ISN)                                   | $V_{IDR}$       | -800         | _    | 800  | mV   | _                                                                   |

| 6.1.5 | Input voltage (Both Inputs - GND) (ISP - GND) or (ISN -GND)              | $V_{LL}$        | -800         | _    | 2000 | mV   | -                                                                   |

| 6.1.6 | Input offset voltage of the I-DC link OpAmp, including temperature drift | $V_{IO}$        | _            | _    | +/-2 | mV   | $R_{\rm S}$ =500 $\Omega$ ; $V_{\rm CM}$ =0V; $V_{\rm ISO}$ =1.65V; |

| 6.1.7 | Input bias current (ISN,ISP to GND)                                      | $I_{IB}$        | -300         | _    | -    | μΑ   | $V_{\rm CM}$ =0V; $V_{\rm ISO}$ =open                               |

### **Shunt Signal Conditioning**

### Electrical Characteristics - Current sense signal conditioning (cont'd)

$V_{\rm S}$  = 6.0 to 33 V,  $T_{\rm j}$  = -40 °C to +150 °C, gain = 5 to 75, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)<sup>1)</sup>

| Pos.   | Parameter                                                                                                       | Symbol            | L                         | ₋imit Val      | ues       | Unit | Conditions                                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------------------|-------------------|---------------------------|----------------|-----------|------|------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                 |                   | Min.                      | Тур.           | Max.      |      |                                                                                                                  |

| 6.1.8  | High level output voltage of ISO                                                                                | $V_{OH}$          | V <sub>VDD</sub> -<br>0.2 | -              | $V_{VDD}$ | V    | $I_{\rm O}$ =-3mA                                                                                                |

| 6.1.9  | Low level output voltage of ISO                                                                                 | $V_{OL}$          | -0.1                      | _              | 0.2       | V    | $I_{\rm O}$ =3mA                                                                                                 |

| 6.1.10 | Guaranteed output current capability                                                                            | $I_{GOC}$         | 5                         | -              | _         | mA   | _                                                                                                                |

| 6.1.11 | Differential input resistance <sup>2)</sup>                                                                     | $R_{I}$           | 100                       | _              | _         | kΩ   | _                                                                                                                |

| 6.1.12 | Common mode input capacitance <sup>2)</sup>                                                                     | $C_{CM}$          | -                         | _              | 10        | pF   | 10kHz                                                                                                            |

| 6.1.13 | Common mode rejection ratio at DC CMRR = 20*Log((Vout_diff/Vin_diff) * (Vin_CM/Vout_CM))                        | $C_{MRR}$         | 80                        | 100            | _         | dB   | _                                                                                                                |

| 6.1.14 | Common mode suppression <sup>3)2)</sup> with CMS = 20*Log(Vout_CM/Vin_CM) Freq =100kHz Freq = 1MHz Freq = 10MHz | $C_{MS}$          | -                         | 62<br>43<br>33 | _         | dB   | $V_{\rm IN}$ =360mV*<br>sin(2*π*freq*t);<br>$R_{\rm s}$ =500Ω; $R_{\rm fb}$ =7500Ω                               |

| 6.1.15 | Slew rate                                                                                                       | $d_{V/dt}$        | _                         | 10             | _         | V/µs | Gain>= 5;<br>$R_L$ =1.0k $\Omega$ ; $C_L$ =500pF                                                                 |

| 6.1.16 | Large signal open loop voltage gain (DC)                                                                        | $A_{OL}$          | 80                        | 100            | _         | dB   | -                                                                                                                |

| 6.1.17 | Unity gain bandwidth                                                                                            | $G_{BW}$          | 10                        | 20             | _         | MHz  | $R_{\rm L}$ =1k $\Omega$ ; $C_{\rm L}$ =100pF                                                                    |

| 6.1.18 | Phase margin <sup>2)</sup>                                                                                      | $F_{M}$           | _                         | 50             | _         | 0    | Gain>= 5;<br>$R_L$ =1k $\Omega$ ; $C_L$ =100pF                                                                   |

| 6.1.19 | Gain margin <sup>2)</sup>                                                                                       | $A_M$             | _                         | 12             | _         | dB   | $R_L$ =1k $\Omega$ ; $C_L$ =100pF                                                                                |

| 6.1.20 | Bandwidth                                                                                                       | $B_{WG}$          | 1.6                       | -              | -         | MHz  | Gain=15; $R_{\rm L}$ =1k $\Omega$ ; $C_{\rm L}$ =500pF; $R_{\rm s}$ =500 $\Omega$                                |

| 6.1.21 | Output settle time to 98% $R_{\rm fb}/R_{\rm S}$ =15 $R_{\rm fb}/R_{\rm S}$ =75                                 | t <sub>set1</sub> | -                         | 1<br>4.6       | 1.8       | μs   | $R_{\rm L}$ =1k $\Omega$ ;<br>$C_{\rm L}$ =500pF;<br>0.3< $V_{\rm ISO}$ < VDD-0.3V;<br>$R_{\rm s}$ =500 $\Omega$ |

<sup>1)</sup> A minimum capacitance of 100pF is needed at the output of the OpAmp (parasitic or real capacitor);  $R_L$  is the total load resistance including the feedback network; In the application it is not recommended to apply a resistor from the output ISO to GND directly in addition to the feedback network.

<sup>2)</sup> Not subject to production test; specified by design

<sup>3)</sup> Without considering any offsets such as input offset voltage, internal mismatch and assuming no tolerance error in external resistors.

5 V Low Drop Voltage Regulator

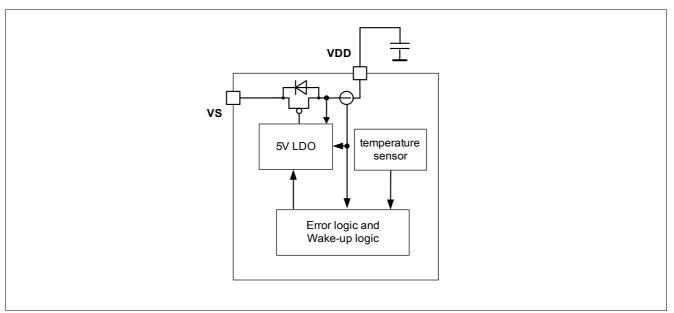

### 7 5 V Low Drop Voltage Regulator

The TLE7184F incorporates a 5V LDO for  $\mu$ C supply. The voltage regulator is protected against Over Temperature by the central temperature sensor (see **Chapter 9.2.1** and **Chapter 9.2.2**). It has an integrated current limitation and Under Voltage detection.

Parameters for Under Voltage detection see Chapter 9.2.5.

Figure 6 Block diagram of 5V LDO

### 7.1 Electrical Characteristics

### **Electrical Characteristics - Current sense signal conditioning**

$V_{\rm S}$  = 6.0 to 45 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                   | Symbol    | L    | Limit Values |      | Unit | Conditions                                                                                                |

|-------|---------------------------------------------|-----------|------|--------------|------|------|-----------------------------------------------------------------------------------------------------------|

|       |                                             |           | Min. | Тур.         | Max. |      |                                                                                                           |

| 7.1.1 | Output voltage                              | $V_{DD1}$ | 4.85 | -            | 5.25 | V    | $2\text{mA} <= I_{\text{load}} <= 70\text{mA};$ $C_{\text{load}} = 122\text{uF}^{1)}$                     |

| 7.1.2 | Output voltage                              | $V_{DD2}$ | 4.90 | _            | 5.20 | V    | 5mA <= $I_{load}$ <=25mA;<br>$C_{load}$ = 122uF <sup>1)</sup>                                             |

| 7.1.3 | LDO over current limitation                 | $I_{OCL}$ | 130  | _            | 270  | mA   | no activation of error by current limitation                                                              |

| 7.1.4 | Load regulation                             | $D_{VDD}$ | _    | 50           | 100  | mV   | $\begin{array}{c} l_{\rm oad} \ {\rm step} \ 020 {\rm mA}; \\ C_{\rm VDD} {\rm =} 1 {\rm uF} \end{array}$ |

| 7.1.5 | Power supply ripple rejection <sup>2)</sup> | $P_{SRR}$ | 50   | _            | -    | dB   | 100Hz sine wave;<br>$0.5V_{pp}$<br>$V_{VS}$ >=7V                                                          |

| 7.1.6 | Power supply ripple rejection <sup>2)</sup> | $P_{SRR}$ | _    | 31           | -    | dB   | 100Hz sine wave; $0.5V_{pp}$ $6V <= V_{VS} < 7V$                                                          |

<sup>1)</sup> ceramic C with 100nF with ESR<0.1 $\Omega$  in parallel

### **5 V Low Drop Voltage Regulator**

### 2) Not subject to production test; specified by design

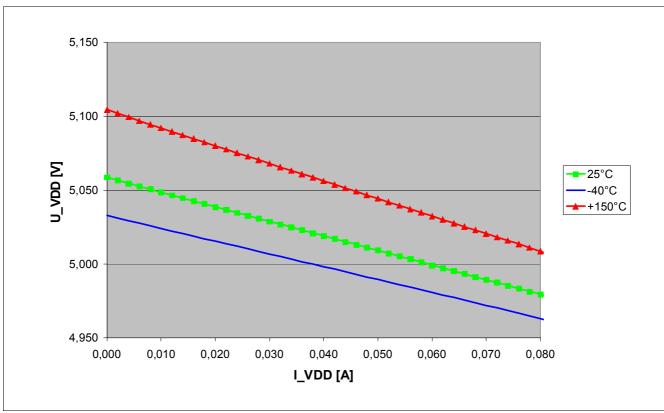

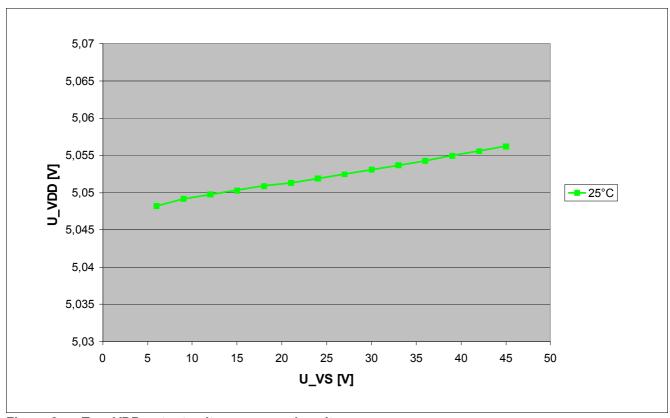

Figure 7 Typ. VDD output voltage vs. load current

### **5 V Low Drop Voltage Regulator**

Figure 8 Typ. VDD output voltage vs. supply voltage

Interface, VDH Switch and INH Digital Output

## 8 Interface, VDH Switch and INH Digital Output

### 8.1 PWM Interface (IFMA)

The TLE7184F has an integrated interface supporting the typical PWM interface between a remote master ECU and the  $\mu$ C. The link to the external master ECU is a single wire communication based on the battery voltage and running typ. with about 10 to 400 Hz. The information is encoded in the duty cycle of the signal.

This communication line requires a signal conditioning to connect to the on board µC.

The integrated circuit supports the incoming data path.

The outgoing data path is formed by external components

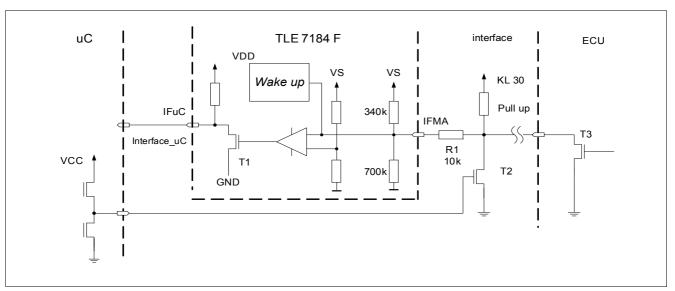

Figure 9 Structure PWM Interface

The integrated circuitry is described in Figure 9.

The main task of this interface is level shifting and protection of the µC.

The IFuC signal is following the IFMA signal, passing the duty cycle information from IFMA to the IFuC.

The  $\mu$ C port is used as input and is listening to the IFuC signal. The voltage at IFMA is monitored. If IFMA is low the IFuC open drain output is switched on - forcing the IFuC signal to low.

If IFMA is high, the IFuC open drain output is deactivated and the IFuC signal is pulled to high by the internal pull-up resistor.

The IFMA input is used as well for wake-up. See Chapter 9.1

#### Influence of serial resistor at IFMA pin

As shown in **Figure 9** a 10k resistor R1 is recommended to protect the IFMA pin against negative voltage levels coming from the interface signal. The integrated pull down and pull up resistors at the IFMA pin form a voltage divider together with the resistor R1. This will influence the resulting switching level of the IFMA interface in the application compared to the levels specified directly at the IFMA pin.

In this datasheet an additional parameter is provided to calculate the influence of the 10k resistor. The specified IFMA input current divided by Vs allows to calculate the drop over R1 with the following formula:

$$Voltage\_drop\_over\_R1 = \frac{I_{IFMA}}{V_{VS}} * V_{VS} * R1$$

### Interface, VDH Switch and INH Digital Output

#### 8.2 VDHS Switch

The System IC has an integrated switch connecting the VDH pin to the VDHS pin. This allows to place an external voltage divider for VDH voltage monitoring at the VDHS pin and to disconnect this voltage divider from VDH during sleep mode to assure low current consumption. The VDHS switch is only deactivated when the VDD regulator is switched off.

### 8.3 Digital Output INHD

The System IC provides a digital output  $\overline{\text{INHD}}$  showing the logic state of  $\overline{\text{INH}}$  (e.g. KL15) after a complete wake-up of the driver (approx. 1ms). The input levels of  $\overline{\text{INH}}$  for the  $\overline{\text{INHD}}$  output are defined separately from the levels for wake-up. Voltage levels for  $\overline{\text{INH}}$  wake-up function please see **Chapter 9.4** section Wake-up and go-to-sleep. The output stage consists of an integrated low side switch with a pull-up resistor to VDD.

### 8.4 Electrical Characteristics

#### **Electrical Characteristics - Protection and diagnostic functions**

$V_{\rm S}$  = 6.0 to 20V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.     | Parameter                                                                                                  | Symbol            | Limit Values |      |                | Unit     | Conditions                                                          |

|----------|------------------------------------------------------------------------------------------------------------|-------------------|--------------|------|----------------|----------|---------------------------------------------------------------------|

|          |                                                                                                            |                   | Min.         | Тур. | Max.           |          |                                                                     |

| Interfac | ce - static parameters                                                                                     | 1                 |              |      | <del>-  </del> | <u> </u> |                                                                     |

| 8.4.1    | IFMA input voltage high level (for IFµC high)                                                              | $V_{IMHL}$        | 59           | _    | _              | %        | of $V_{\rm VS}$ ; IC not in Sleep Mode                              |

| 8.4.2    | IFMA input voltage low level (for IFµC low)                                                                | $V_{IMLL}$        | -            | _    | 46             | %        | of $V_{\rm VS}$ ; IC not in Sleep Mode;                             |

| 8.4.3    | IFMA input hysteresis (for IFµC)                                                                           | $V_{IMhy}$        | 0.5          | _    | 9              | %        | of $V_{\rm VS}$ ; IC not in Sleep Mode                              |

| 8.4.4    | IFMA wake up voltage high level = $V_{\text{S}}$ - $V_{\text{IFMA}}$                                       | $V_{IMWH}$        | 2            | _    | 4              | V        | valid in Sleep Mode                                                 |

| 8.4.5    | IFMA low time to guarantee wake-<br>up                                                                     | $t_{IFlow}$       | 100          | _    | _              | μs       | V <sub>VS</sub> =720V                                               |

| 8.4.6    | IFMA internal pull-up resistor to $V_{\mathrm{S}}$                                                         | $R_{IMu}$         | 210          | 340  | 495            | kΩ       | _                                                                   |

| 8.4.7    | IFMA internal pull-down resistor to GND                                                                    | $R_{IMd}$         | 420          | 700  | 980            | kΩ       | not active in Sleep<br>Mode                                         |

| 8.4.8    | IFMA input current related to VS $V_{\rm IFMA}$ = 59% of $V_{\rm VS}$ $V_{\rm IFMA}$ = 46% of $V_{\rm VS}$ | $I_{IFMA}/V_{VS}$ | -2.0<br>-3.0 | _    | +2.0<br>+1.0   | μA/V     | _                                                                   |

| 8.4.9    | IFμC output low voltage                                                                                    | $V_{luLL}$        | _            | _    | 0.5            | V        | no external load                                                    |

| 8.4.10   | IF $\mu$ C internal pull-up resistor to $V_{\rm DD}$                                                       |                   | 8.5          | _    | 23             | kΩ       | _                                                                   |

| Interfac | ce - dynamic parameters                                                                                    |                   | 1            |      |                |          |                                                                     |

| 8.4.11   | IFμC duty cycle                                                                                            | $d_{lu}$          | 0            | _    | 100            | %        | _                                                                   |

| 8.4.12   | Propagation time rising edge IFμC                                                                          | $t_{PRE}$         | -            | -    | 6              | μs       | Including rise time to 80% of $V_{\rm VDD}$ ; $C_{\rm load}$ =100pF |

| 8.4.13   | Propagation time falling edge IFμC                                                                         | $t_{PFE}$         | _            | _    | 5              | μs       | Including fall time to 20% of $V_{\rm VDD}$ ; $C_{\rm load}$ =100pF |

### Interface, VDH Switch and INH Digital Output

### **Electrical Characteristics - Protection and diagnostic functions** (cont'd)

$V_{\rm S}$  = 6.0 to 20V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                             | Symbol      |      | Limit Val | ues      | Unit | Conditions         |

|--------|-----------------------------------------------------------------------|-------------|------|-----------|----------|------|--------------------|

|        |                                                                       |             | Min. | Тур.      | Max.     |      |                    |

| 8.4.14 | Deviation between rising and falling IFµC                             | $t_{PD}$    | -    | _         | 4        | μs   | $C_{load} = 100pF$ |

| VDH sv | vitch                                                                 | +           |      | +         |          |      | -                  |

| 8.4.15 | Ron VDH switch                                                        | $R_{VDH}$   | _    | _         | 150      | Ω    | Load current = 1mA |

| INHD d | igital output                                                         |             | U    | - 1       | <u> </u> |      |                    |

| 8.4.16 | Low level input voltage INH (for INHD=low)                            | $V_{INHDL}$ | _    | _         | 1.5      | V    | _                  |

| 8.4.17 | High level input voltage INH (for INHD=high)                          | $V_{INHDH}$ | 2.2  | _         | _        | V    | -                  |

| 8.4.18 | Input hysteresis of INH for INHD <sup>1)</sup>                        | $d_{VINHD}$ | 100  | _         | _        | mV   | _                  |

| 8.4.19 | INHD low level output voltage                                         | $V_{INHD}$  | _    | _         | 0.5      | V    | no external load   |

| 8.4.20 | $\overline{\text{INHD}}$ Internal pull-up resistor to $V_{\text{DD}}$ | $R_{INHD}$  | 42.5 | _         | 115      | kΩ   | _                  |

<sup>1)</sup> Not subject to production test; specified by design

**Description of Modes, Protection and Diagnostic Functions**

### 9 Description of Modes, Protection and Diagnostic Functions

### 9.1 Description of modes

The operation of TLE7184F can be described by different operation modes

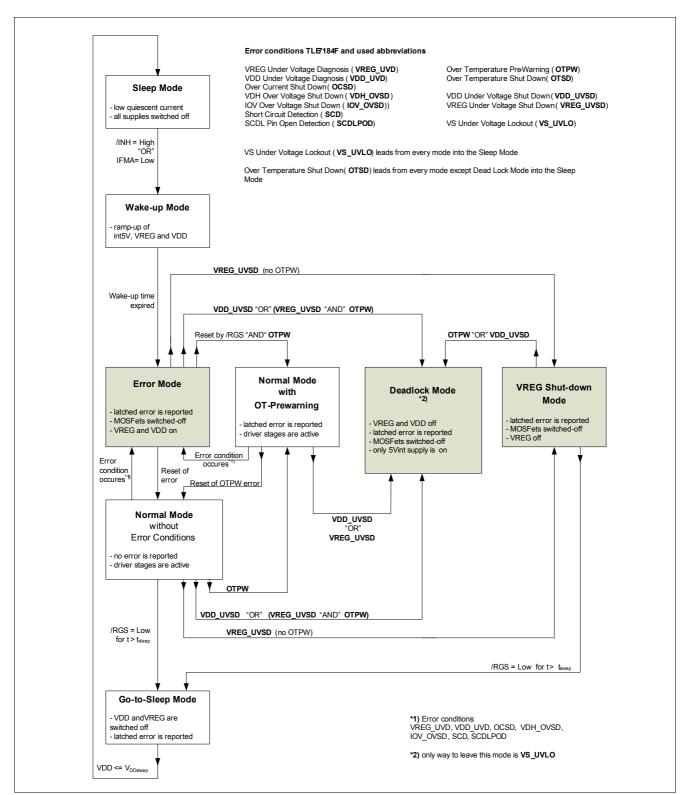

Figure 10 State diagram TLE7184F

### **Description of Modes, Protection and Diagnostic Functions**

#### Sleep Mode:

The sleep mode is entered if the device is in the Go-to-sleep Mode and the VDD voltage is lower than  $V_{\rm DDsleep}$ . The complete chip is deactivated beside the wake-up function (see Wake-up Mode). This mode is designed for lowest current consumption from the power net of the car. The passive clamping is active. For details see the description of passive clamping, see **Chapter 9.2.15**.

The only way to leave the Sleep Mode is to go to the Wake-up Mode.

#### Wake-up Mode:

The TLE7184F wakes up if  $\overline{\rm INH}$  (=KL15) is high or if IFMA is low and  $V_{\rm VS}$  is higher than  $V_{\rm VSLO}$ .

In this mode all supplies are ramping up. As soon as the internal 5V is available, a so called wake-up timer starts to run. If the IC reaches this state, the wake-up will continue even if the wake-up signals at  $\overline{\text{INH}}$  or IFMA disappear. The PWM interface (IFMA) is active as soon as the VDD voltage is sufficiently high. During this time it is expected that the supplies are powered up and the  $\mu$ C sets the  $\overline{\text{RGS}}$  to high. All external MOSFETs are switched off actively or passively. When the wake up timer is expired the IC goes into the Error mode.

In this mode all errors will be ignored beside Over Temperature Shut Down or  $V_S$  Under Voltage Lockout.

#### **Error Mode**

The Error Mode can be reached in 3 different ways:

- 1. The device is in Wake-up Mode and the wake up timer expires

- The device is in Normal Mode and one or more of the following errors occur: VREG Under Voltage Shut Down, VDD Under Voltage Shut Down, Over Current Shut Down, VDH Over Voltage Shut Down, IOV Over Voltage Shut Down, Short Circuit Detection or SCDL Open Detection.

- The device is in Normal Mode with OT-Prewarning and one or more of the following errors occur: VREG Under Voltage Shut Down, VDD Under Voltage Shut Down, Over Current Shut Down, VDH Over Voltage Shut Down, IOV Over Voltage Shut Down, Short Circuit Detection or SCDL Open Detection.

In this mode an Error is set at the ERROR Pin and all external MOSFETs are actively switched off as long as the bootstrap voltages allows it. The interface is active. VDHS switch is on and the current sense functions are working. VDD and VREG are active. Passive clamping is not active.

The Error mode can be left in the following ways:

- 1. If no error is present, the IC can be sent to Normal Mode by a reset with the RGS pin.

- 2. If a VREG Under Voltage Shut Down occurs and no Over Temperature Prewarning is present, the device will go to VREG Shut-down Mode.

- 3. If VDD Under Voltage Shut Down occurs or a VREG Under Voltage Shut Down together with a Over Temperature Prewarning occurs, the device will go into Deadlock Mode.

- 4. If Over Temperature Prewarning is present, the IC can be sent to Normal Mode with OT-Prewarning by a reset with the RGS pin.

### **Normal Mode**

The Normal Mode can be reached in two different ways:

- 1. The device is in Error Mode, no error is present and a reset is performed by the RGS pin.

- 2. The device is in Normal Mode with OT-Prewarning, the chip temperature is below the OT-Prewarning level and a reset is performed by the  $\overline{\text{RGS}}$  pin.

In the Normal Mode all functions are active and available with the regular limitations of the bootstrap principle. The gate drive output stages can be controlled with the input pins.

The Normal Mode can be left in 5 ways:

- 1. The devices goes to the Go-To-Sleep Mode by setting  $\overline{\text{RGS}}$  to low for a time longer than  $t_{\text{sleep}}$ .

- 2. If a Over Temperature Prewarning occurs the device goes into the Normal Mode with OT-Prewarning.

Data Sheet 25 Rev. 1.2, 2016-01-28